Академический Документы

Профессиональный Документы

Культура Документы

Design of A Digital Cdma Receiver: I. Vijay Kumar M.B.Srinivas

Загружено:

Madhu Krishna KarthanОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Design of A Digital Cdma Receiver: I. Vijay Kumar M.B.Srinivas

Загружено:

Madhu Krishna KarthanАвторское право:

Доступные форматы

DESIGN OF A DIGITAL CDMA RECEIVER

I. Vijay Kumar

VLSI and Embedded Systems Research Center

International Institute of Information Technology, Hyderabad

India 500019

Tel: +91-40-3001969

Fax: +91-40-3001413

Email: vijaykumar@gdit.iiit.net

Abstract-In this work, an attempt has been made to design a

Digital Signal Code Division Multiple Accesses Receiver using

VHDL [1] [2] and synthesize using Mentor Graphics tools. The

receiver is designed for a maximum of three users as per the

design specification given for the contest. The novelty of this

design is that it uses four independent processes to achieve the

concurrent operation for the entire functionality. The simulation

and synthesis are carried out using Mentor Graphics FPGA

tools and an optimized circuit in terms of area and timing is

brought out.

1. INTRODUCTION

The enhancement in performance obtained from a DSSpread-Spectrum signal through the processing gain, and the

coding gain can be used to enable many DS spread spectrum

signals to occupy the same channel bandwidth provided that

each signal has its own pseudorandom (signature) sequence.

Thus, it is possible to have several users transmit messages

simultaneously over the same channel bandwidth. This type

of digital communication in which transmission/reception has

its own distinct signature code for transmitting over a

common channel is called CDMA. A receiver, which uses

CDMA technology as per the specifications, is designed

using VHDL and results are obtained for the simulation and

logic synthesis.

2. SYSTEM FUNCTIONALITY

The system uses the data (signals) sent by the transmitter,

whose characteristics are already known. The transmitter

receives 3 digit inputs and mixes them to generate one output

using CDMA technique. The receiver receives the mixture

and decodes the signal and extracts one preferable datum. A

perfect synchronization clock for both the transmitter and the

receiver is assumed. CDMA does the data extraction using

Pseudo Noise code (PN code), which is a sequence of

randomly appearing ones and zeros, but the appearing

frequency of both ones and zeros are almost the same. The

PN code of 127 bits is used for the inner product calculation,

which is also called convolution or matched filtering.

M.B.Srinivas

VLSI and Embedded Systems Research Center

International Institute of Information Technology, Hyderabad,

India 500019

Tel: +91-40-3001969

Fax: +91-40-3001413

Email: srinivas@iiit.net

The PN code generation Module (Process): - The PN codes are

generated in this module using the linear shift back registers.

These codes are generated on the raising clock edge and on

receiving the SYNCIN signal, which is activated by the

SYNCOUT signal of the transmitter. After a period of 127

clock cycles, the process waits for the next SYNCIN signal

for the PN code regeneration. Thus it keeps in synchronous

with the transmitter data. If the design requires a change in

PN code, a different design can be modeled for the PN

generation without effecting the other processor blocks, a

consequence of using independent processes.

Counter Module: - The Counter module (Process) starts the

counter with the start of SYNCIN signal and for further

regeneration it depends upon the next SYNCIN signal thus

keeping track of the input signals.

Synchronous Signal Generation Module: - This module keeps

track of the SYNCIN signal (SYNCOUT signal from the

transmitter) and gives stimuli for all other modules for

functioning for a period of 127 cycles after which all other

processes wait for the next stimuli. This process is

independent in nature.

Receiver Output Module: -The function of this Module

(process) is to process on the RVIN data upon receiving

stimuli from the Sync signal. The PN code is convolved with

the received data and after a period of 127 cycles the output

(DOUT) is assigned a value according to the channel output

requirement and the VALID signal is made high. The

processing of the data is done for the three channels and one

of the values is assigned according to the channel selection. If

the number of users is increased, then new PN code

3. RECEIVER DESIGN

The receiver design is divided into four different modules,

viz., the PN code generation module, counter module,

synchronous signal generation module and receiver output

module, as shown in Fig. 1, and are designed using process

statements. A synchronous clock is applied to all the modules

while the RESET signal initializes all the values. A brief

explanation of various modules is given below.

Fig-1 System Architecture

generators can be introduced and respective channel

processing for the channel data can be achieved easily with

small changes in code. Here the novelty lies in the ease with

which new channels can be added.

The technique used in the present design is simple. The entire

design is divided into four different process statements and

each is run concurrently thus making four different modules

work in tandem. The Simulation was carried out using

ModelSim simulator (Mentor Tools). Accuracy of the results

was verified by applying data out of the transmitter to the

receiver. Figure 2 and Fig-3 show the start and end of the

simulation for the transmitters input of (data-in) 000. The

valid signal is high after 127 clock cycles and the data-out is

0, thus verifying the design. The synthesized RTL and

technology schematics are shown in the Fig-4 and Fig-5

respectively.

***********************************************

Device Utilization for 2s15cs144 ( XILINX SPARTAN2)

***********************************************

Resource

Used Avail

Utilization

---------------------------------------------------------------------IOs

9

86

10.47%

Function Generators

291

384

75.78%

CLB Slices

146

192

76.04%

Dffs or Latches

128

672

19.05%

-----------------------------------------------------------------------

Fig-4 RTL Schematic

Fig-2 Simulation start point

Fig-5 Technology Schematic

9. RESULTS AND CONCLUSIONS

The results, as shown in Figs. 2 and 3, show that the design

meets the specifications given. The design has been

implemented on Xilinxs Spartan-2 series FPGA with good

utilization as indicated by the results. The dynamic power

consumption has been estimated to be 1.35 W.

Fig-3 Simulation end point

8. SYNTHESIS

Vdd = 2.5 V, Maximum clock frequency = 77.2 MHz

DYNAMIC POWER CONSUMTION =1.35W (approximately)

10. REFERENCES

[1]

Perry Digital Design using VHDL '

[2]

Heinkel : VHDL Reference

Вам также может понравиться

- GlmifeДокумент3 страницыGlmifeAndrea FasatoОценок пока нет

- Global Wireless e - Voteing SystemДокумент27 страницGlobal Wireless e - Voteing SystemLaxmi KanthОценок пока нет

- Calls and MoUДокумент7 страницCalls and MoUAnuj RawatОценок пока нет

- Vol4 No2 Electronics 1Документ6 страницVol4 No2 Electronics 1shastryОценок пока нет

- M2M Communication Based Wireless SCADA For Real-Time Industrial AutomationДокумент3 страницыM2M Communication Based Wireless SCADA For Real-Time Industrial AutomationAutoyearОценок пока нет

- Design of The Data Acquisition System Based On STM32: Information Technology and Quantitative Management (ITQM2013)Документ7 страницDesign of The Data Acquisition System Based On STM32: Information Technology and Quantitative Management (ITQM2013)Josue Manuel Pareja ContrerasОценок пока нет

- Tp1 Report: Code-Division Multiple Access (CDMA)Документ6 страницTp1 Report: Code-Division Multiple Access (CDMA)Boulanouar RBIHОценок пока нет

- Experiment No: 04: AJEENKYA DY Patil School of Engineering Department of Electronics & Telecommunication EngineeringДокумент8 страницExperiment No: 04: AJEENKYA DY Patil School of Engineering Department of Electronics & Telecommunication EngineeringmanashОценок пока нет

- Iii B.Tech Ii Sem Eie (R18) : Unit - VДокумент62 страницыIii B.Tech Ii Sem Eie (R18) : Unit - VSrinivas PapaniОценок пока нет

- Introduction of Industry: Company ProfileДокумент38 страницIntroduction of Industry: Company ProfileRahul SinghОценок пока нет

- Development of Coalmine Safety System Using Wireless Sensor NetworkДокумент10 страницDevelopment of Coalmine Safety System Using Wireless Sensor Networkchinu07416Оценок пока нет

- Distributed Control SystemsДокумент24 страницыDistributed Control SystemsPraveen Madhusoodhanan100% (1)

- Wireless Polling Method Using RFДокумент101 страницаWireless Polling Method Using RFSravani SravzОценок пока нет

- PCI6221Документ7 страницPCI6221rajasekarkprОценок пока нет

- Real Time Clock Using Fpga: B. E. III, Semester - 5 (Electronics Branch) SubjectДокумент9 страницReal Time Clock Using Fpga: B. E. III, Semester - 5 (Electronics Branch) SubjectJay JataniyaОценок пока нет

- 2 MarkДокумент15 страниц2 MarkGowthamanОценок пока нет

- 11.wireless FullДокумент6 страниц11.wireless FullTJPRC PublicationsОценок пока нет

- Chapter 2 Literature ReviewДокумент15 страницChapter 2 Literature ReviewsaiОценок пока нет

- Using OCC For Full Scan Design PDFДокумент6 страницUsing OCC For Full Scan Design PDFUmesh ParasharОценок пока нет

- DSP SmartДокумент91 страницаDSP SmartNishanth NissanОценок пока нет

- D.Sai Dutt: Phone No: - 09030772232. Location: - Hyderabad Professional SkillsДокумент4 страницыD.Sai Dutt: Phone No: - 09030772232. Location: - Hyderabad Professional SkillsReshma VlsiОценок пока нет

- Rajarathinam ResumeДокумент5 страницRajarathinam ResumeManickavel SmsОценок пока нет

- Design of The Data Acquisition System Based On STM32: Information Technology and Quantitative Management (ITQM2013)Документ7 страницDesign of The Data Acquisition System Based On STM32: Information Technology and Quantitative Management (ITQM2013)Nguyễn Trọng TuyếnОценок пока нет

- K L With Advanced Encryption Standard (AES) Receiver/DecoderДокумент8 страницK L With Advanced Encryption Standard (AES) Receiver/DecoderbilarodrigoОценок пока нет

- Design of A GSM Based Electronic Voting Machine With Voter TrackingДокумент4 страницыDesign of A GSM Based Electronic Voting Machine With Voter TrackingsolomonfikadieОценок пока нет

- Troubleshoot Media Forking From Cisco IP Phone To Media SenseДокумент17 страницTroubleshoot Media Forking From Cisco IP Phone To Media Sensesumit rustagiОценок пока нет

- Office Security SystemДокумент6 страницOffice Security SystemIJMERОценок пока нет

- Implementing V32bis Viterbi Decoding On TheTMS320C62xx DSPДокумент46 страницImplementing V32bis Viterbi Decoding On TheTMS320C62xx DSPnguyenhuuduc_bgОценок пока нет

- E Brains DetailsДокумент4 страницыE Brains DetailsJyoti HaveliyaОценок пока нет

- Midterm Report Format PDFДокумент25 страницMidterm Report Format PDFLucy HeartfilliaОценок пока нет

- m2x3c I500c en M C Manual GBДокумент88 страницm2x3c I500c en M C Manual GBdinakaran2020Оценок пока нет

- Report On Practical Training at CДокумент48 страницReport On Practical Training at CJyoti SharmaОценок пока нет

- 8 Bit Risc Processor PresentationДокумент36 страниц8 Bit Risc Processor PresentationSantanu KumarОценок пока нет

- PLC ScadaДокумент30 страницPLC ScadaNeeraj Mishra100% (1)

- Vlsi Lab QuestionsДокумент7 страницVlsi Lab QuestionsRakesh MudigondaОценок пока нет

- Design and Simulation of Digital Down Converter Based On System GeneratorДокумент3 страницыDesign and Simulation of Digital Down Converter Based On System GeneratorMayerly MayorgaОценок пока нет

- Rapid Prototyping of Control Systems Using Embedded Target For TI C2000 DSPДокумент5 страницRapid Prototyping of Control Systems Using Embedded Target For TI C2000 DSPLeroy Lionel SonfackОценок пока нет

- Distributed Control Systems: Emad Ali Chemical Engineering Department King SAUD UniversityДокумент24 страницыDistributed Control Systems: Emad Ali Chemical Engineering Department King SAUD UniversitynaeemfaysalОценок пока нет

- 5+years1apr2015sai DuttДокумент4 страницы5+years1apr2015sai DuttReshma VlsiОценок пока нет

- MCC Expt 2 CSMAДокумент5 страницMCC Expt 2 CSMAAlkaОценок пока нет

- Data Acquisition System For A Formula SAE Race CarДокумент43 страницыData Acquisition System For A Formula SAE Race CarRodrigo Bob100% (1)

- Paper To Be SubmitedДокумент5 страницPaper To Be SubmitedAl Beruni TomalОценок пока нет

- Summer Training ProjectДокумент18 страницSummer Training ProjectTarun Chugh100% (1)

- dsPic33FJ256MC710 (Gluonpilot)Документ340 страницdsPic33FJ256MC710 (Gluonpilot)Rosana FariaОценок пока нет

- Activity 03Документ14 страницActivity 03SasukeОценок пока нет

- FreyrSCADA IEC 60870 5 104 Server Simulator User ManualДокумент33 страницыFreyrSCADA IEC 60870 5 104 Server Simulator User ManualHoang Tran DinhОценок пока нет

- Bachelor of Technology in Electronics & Communication: Synopsis ONДокумент26 страницBachelor of Technology in Electronics & Communication: Synopsis ONKapil YadavОценок пока нет

- A Novel High Performance Implemance and Design of 64 Bit MAC Unit& Their Delay ComparisionДокумент17 страницA Novel High Performance Implemance and Design of 64 Bit MAC Unit& Their Delay ComparisionAmarenderОценок пока нет

- Wireless Automobile Monitoring SystemДокумент48 страницWireless Automobile Monitoring SystemVaibhav TiwariОценок пока нет

- Multiclick: A Fast, Easy and Reliable Solution For Installing Power Metering SystemsДокумент14 страницMulticlick: A Fast, Easy and Reliable Solution For Installing Power Metering SystemsÁlvaroAnabalónSalamancaОценок пока нет

- DsPIC256GP710A DatasheetДокумент350 страницDsPIC256GP710A Datasheetmadmadovi1Оценок пока нет

- C - DOT Exchange Control Department of Telematics (C-DOT) Exchange Was DesignedДокумент11 страницC - DOT Exchange Control Department of Telematics (C-DOT) Exchange Was Designedkhadarbasha.n nОценок пока нет

- GSM Based Display SynopsisДокумент17 страницGSM Based Display SynopsisPooja SharmaОценок пока нет

- RFID Based Security System (AT89S52 + RFID)Документ18 страницRFID Based Security System (AT89S52 + RFID)Prathamesh JadhavОценок пока нет

- The Design of SVPWM Waveform Generator Based On CPLD - DSP: Software EngineeringДокумент7 страницThe Design of SVPWM Waveform Generator Based On CPLD - DSP: Software EngineeringAshagre MekuriaОценок пока нет

- Unit 5Документ91 страницаUnit 5eie.vgnt2023Оценок пока нет

- 1250 Alcohol Detection With Vehicle ControllingДокумент6 страниц1250 Alcohol Detection With Vehicle ControllingSunil BerwalОценок пока нет

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkОт EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkОценок пока нет

- Geometrical Interpretation of Dilution of Precision DOPДокумент2 страницыGeometrical Interpretation of Dilution of Precision DOPMadhu Krishna KarthanОценок пока нет

- 320 Lecture 33Документ8 страниц320 Lecture 33Madhu Krishna KarthanОценок пока нет

- Tuned AmplifiersДокумент9 страницTuned AmplifiersMadhu Krishna KarthanОценок пока нет

- 3.a) Draw The Circuit of RC Phase-Shift Osci: Using Op-Amps. (8+7)Документ1 страница3.a) Draw The Circuit of RC Phase-Shift Osci: Using Op-Amps. (8+7)Madhu Krishna KarthanОценок пока нет

- Cascaded (CE-CC) AmplifierДокумент6 страницCascaded (CE-CC) AmplifierMadhu Krishna KarthanОценок пока нет

- Satellite Communications A: Access Schemes in Satellite Networks - Professor Barry G EvansДокумент46 страницSatellite Communications A: Access Schemes in Satellite Networks - Professor Barry G EvansMadhu Krishna KarthanОценок пока нет

- 3.5 CMOS/TTL Interfacing: V V V VДокумент2 страницы3.5 CMOS/TTL Interfacing: V V V VMadhu Krishna KarthanОценок пока нет

- Simulation of Wireless Comm. Sys Using MATLABДокумент57 страницSimulation of Wireless Comm. Sys Using MATLABPriyamvada VermaОценок пока нет

- Operational Amplifier - Wikipedia, The Free EncyclopediaДокумент24 страницыOperational Amplifier - Wikipedia, The Free EncyclopediaMadhu Krishna KarthanОценок пока нет

- Electronic Communication Systems - G. Kennedy and B. DavisДокумент54 страницыElectronic Communication Systems - G. Kennedy and B. DavisMadhu Krishna Karthan75% (4)

- Rinex FormatДокумент20 страницRinex FormatMadhu Krishna KarthanОценок пока нет

- TB6500 ManualДокумент11 страницTB6500 ManualEnrique BautistaОценок пока нет

- Table of Contents For Computer Architecture: A Minimalist PerspectiveДокумент6 страницTable of Contents For Computer Architecture: A Minimalist PerspectiveWilliam GilreathОценок пока нет

- 9000-41034-0100600 - Data Sheet - enДокумент2 страницы9000-41034-0100600 - Data Sheet - endAvId rObLeSОценок пока нет

- Quadro Mobile Line Card n18 11x8.5 r4 HRДокумент1 страницаQuadro Mobile Line Card n18 11x8.5 r4 HREka S. PaongananОценок пока нет

- HUAWEI - SD-WAN SolutionДокумент235 страницHUAWEI - SD-WAN Solutionbuafac10Оценок пока нет

- Advanced Computer Architectures: 17CS72 (As Per CBCS Scheme)Документ31 страницаAdvanced Computer Architectures: 17CS72 (As Per CBCS Scheme)Aasim InamdarОценок пока нет

- Online Consumer Complaint Filing: E-Filing of Complaints at Consumer Forums of IndiaДокумент13 страницOnline Consumer Complaint Filing: E-Filing of Complaints at Consumer Forums of IndiaLAVANYA SAMPATHОценок пока нет

- Es ZC424 Course HandoutДокумент13 страницEs ZC424 Course HandoutJAYAKRISHNAN.K.RОценок пока нет

- Equity Sentry ManualДокумент3 страницыEquity Sentry ManualSheBrowniesОценок пока нет

- Fuerte, Danielle Angela 06-17 Vlog (G) Ing Sino Ka Man, On Vlogs and Created Filipino IdentitiesДокумент83 страницыFuerte, Danielle Angela 06-17 Vlog (G) Ing Sino Ka Man, On Vlogs and Created Filipino IdentitiesSherren NalaОценок пока нет

- Coupling and CohesionДокумент2 страницыCoupling and CohesionDebadatta GadanayakОценок пока нет

- CRT Learning Module: Course Code Course Title No. of Hours Module TitleДокумент16 страницCRT Learning Module: Course Code Course Title No. of Hours Module TitleEiszel CadacioОценок пока нет

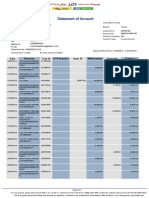

- Statement of Account: Date Tran Id Remarks UTR Number Instr. ID Withdrawals Deposits BalanceДокумент8 страницStatement of Account: Date Tran Id Remarks UTR Number Instr. ID Withdrawals Deposits Balancedinesh namdeoОценок пока нет

- A320LEAP1A-B12-0008.5 Cont&Ind R1 220517Документ78 страницA320LEAP1A-B12-0008.5 Cont&Ind R1 220517simsimsomОценок пока нет

- CH 5 NOTES - Data Organization and Descriptive StatisticsДокумент32 страницыCH 5 NOTES - Data Organization and Descriptive StatisticsMila SmithОценок пока нет

- FM 4-02 Preventive Medical ServiceДокумент195 страницFM 4-02 Preventive Medical ServiceMark Cheney100% (2)

- Victor Chironda CV 2019Документ4 страницыVictor Chironda CV 2019Alex LebedevОценок пока нет

- Payment Notification FNBДокумент1 страницаPayment Notification FNBChequeОценок пока нет

- Axioms Activity (Games) PDFДокумент3 страницыAxioms Activity (Games) PDFKristopher TreyОценок пока нет

- Practice Test A1Документ7 страницPractice Test A1Khang Nguyen TienОценок пока нет

- ACESYS V8.0 - User Manual - AlternateДокумент12 страницACESYS V8.0 - User Manual - AlternateMohamed AdelОценок пока нет

- (PPT) Digital Electronics 2 For StudentsДокумент6 страниц(PPT) Digital Electronics 2 For StudentsJONNA ACABOОценок пока нет

- Cisco - Aci - White Paper c11 740861Документ67 страницCisco - Aci - White Paper c11 740861PrasannaОценок пока нет

- R-Net System R-Net System: Multi-Rehab Powerchair Control SystemДокумент4 страницыR-Net System R-Net System: Multi-Rehab Powerchair Control SystemMikel VillanuevaОценок пока нет

- BSNL Summer Traning ReportДокумент39 страницBSNL Summer Traning ReportMohd MunzirОценок пока нет

- Engine Control Unit Type ECU 4/G: MTU/DDC Series 4000 Genset ApplicationsДокумент62 страницыEngine Control Unit Type ECU 4/G: MTU/DDC Series 4000 Genset ApplicationsGeorge Barsoum100% (3)

- VoyeurismДокумент9 страницVoyeurismsaurabhosaurus100% (1)

- CP4P Week3 Course Preview ActivityДокумент4 страницыCP4P Week3 Course Preview ActivityPresiОценок пока нет

- Republic of The Philippines Sangguniang Panlungsod City of Baguio SOFAD SESSION, 09 OCTOBER 2017, 2:00 P.M. Session Nr. 1Документ3 страницыRepublic of The Philippines Sangguniang Panlungsod City of Baguio SOFAD SESSION, 09 OCTOBER 2017, 2:00 P.M. Session Nr. 1rainОценок пока нет

- An Introduction To MQTT For Complete BeginnersДокумент22 страницыAn Introduction To MQTT For Complete BeginnerskarchecovОценок пока нет