Академический Документы

Профессиональный Документы

Культура Документы

Part01 COURS Systèmes Numeriques 2014 2015

Загружено:

juhanАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Part01 COURS Systèmes Numeriques 2014 2015

Загружено:

juhanАвторское право:

Доступные форматы

R.

YAHIAOUI

UFR Sciences et Techniques Besanon

Licence EEA 3me Anne

Systmes Numriques

Cours

TD

TP

22h

18h

20h

M. Rda YAHIAOUI

R. YAHIAOUI

Panorama des types de circuits logiques

FPGA : Field Programmable Gate Array rseau de portes programmables in-situ

2

CPLD : Complex Programmable Logic Device

R. YAHIAOUI

UFR Sciences et Techniques Besanon

Licence EEA 3me Anne

Systmes Numriques

Cours

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Introduction

Actuellement les Objets Techniques (O.T.) utilisent de plus en plus la logique

programme (P, Mmoires, C, ...). Ces structures ont besoin de s'interfacer

entre elles. Elles utilisent gnralement pour raliser ces interfaces des fonctions

base de fonctions logiques lmentaires, compteurs, registres , .... Le nombre

de circuits ncessaires pour remplir ces fonctions peut devenir trs vite

important.

Pour diminuer les cots de fabrication, de dveloppement et de maintenance, les

fabricants de circuits intgrs ont donn naissance aux Circuits Logique

Programmable ou encore P.L.D. (Programmable Logic Device)

Ces circuits sont capables pour un O.T. de raliser plusieurs fonctions logiques

dans un seul circuit. Si ces fonctions taient ralises base circuits de logique

classique, il en faudrait plusieurs circuits.

Un autre avantage,

avantage l'volution des fonctions d'un l'O.T. s'effectue par

programmation compare une solution classique o il faut refaire un circuit

imprim si on veut modifier le fonctionnement.

4

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Classification

Les constructeurs de P.L.D. se livrent entre eux une guerre commerciale et sur

les appellations, ce qui explique la difficult tablir la classification des P.L.D.

La plus ancienne et la plus connue est certainement la famille des P.A.L. Le nom a

t donn par la socit M.M.I (Fusion depuis avec A.M.D.), c'est une appellation

dpose, comme Walkman pour Sony ou Rfrigrateur pour Frigidaire.

* P.A.L. signifie Programmable Array Logic, c'est dire rseau logique

programmable. La programmation de ces circuits s'effectue par destruction de

fusibles. Une fois programms on ne peut plus les effacer. On distingue deux

sous familles:

-Les P.A.L. combinatoires ou P.A.L. simples. Ils sont constitus

de fonctions de logique combinatoire.

- Les P.A.L. registres ou F.P.L.S. Field Programmable Logic

Squencer pour squenceur logique programmable. Ils sont

constitus de logique combinatoire et squentielle (Registre).

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Classification (suite)

Les P.A.L. effaables: E.P.L.D.

Les E.P.L.D. Ce qui signifie Erasable Programmable Logic Device,

evice c'est dire

circuit logique programmable et effasable et qui sont aux P.A.L. ce que sont les

U.V.P.R.OM. aux P.R.O.M. Les E.P.L.D. peuvent tre effacs par U.V. ou

lectriquement. Ils sont encore appels P.A.L. CMOS.

Les G.A.L.

Les G.A.L. Ce qui signifie Generic Array Logic ou encore rseau logique

gnrique ce qui veut dire pas grand chose mais qui sont aux P.A.L. ce que sont

les E.E.P.R.O.M aux P.R.O.M. Le nom de G.A.L. a t dpos par LATTICE

SEMICONDUCTOR. Leur fonctionnement est identique aux P.A.L. CMOS, ils sont

programmables et effaables lectriquement.

6

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

* Les C.P.L.D.

Classification (suite)

Les C.P.L.D. Ce qui signifie Complex Programmable Logic Device.

evice Ces circuits

sont composs de plusieurs P.A.L.s lmentaires (Par exemple lquivalent de

P.A.L.s 22V10) relis entre-eux par une zone dinterconnexion. Grce cette

architecture, ils permettent datteindre des vitesses de fonctionnement leves

(plusieurs centaine de Mhz).

* Les L.C.A. & F.P.G.A. anti-fusible.

-Les L.C.A. Ce qui signifie Logic Cell Array ou encore rseau de cellules logiques.

Ces circuits sont composs de blocs logiques lmentaires de 2000 10000

portes que l'utilisateur peut interconnecter.

- Les F.P.G.A. anti fusibles sont identiques aux L.C.A sauf qu'ils permettent une

plus grande intgration de portes et ils ne sont pas effaables lectriquement. Le

nom anti-fusible vient de la programmation des connexions qui s'effectue par

fermeture de circuits, compar aux fusibles o l'on ouvre les circuits.

Remarque : Les composants programmables proposs par ALTERA sont de type EEPROM et SRAM.

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Structure de base

La plupart des PLDs suivent la structure suivante :

Un ensemble doprateurs ET sur lesquels viennent se connecter les variables dentre et

leurs complments.

Un ensemble doprateurs OU sur lesquels les sorties des oprateurs ET sont

connectes.

Une ventuelle structure de sortie (Portes inverseuses, logique 3 tats, registres...).

Les deux premiers ensembles forment chacun ce quon appelle une matrice. Les

interconnexions de ces matrices doivent tre programmables. Cest la raison pour laquelle elles

sont assures par des fusibles qui sont grills lors de la programmation.

symbolisation des portes logiques pour les

PLDs

Lorsquun PLD est vierge

connexions sont assures.

toutes

les

8

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Structure de base

En rsum

D'un point de vue fonctionnel un P.A.L.

P.A.L est constitu d'une zone d'entre de fusibles ou

matrice de programmation et une structure de sortie non programmable dterminant le type de

circuit voir schma ci-dessous.

Tout P.A.L. est constitu :

- D'entres (Input): I1 In avec 8<n<22.

- De sorties (Output) Ou dentres / sorties (I/O)

de type Totem Ple ou Trois Etats :

O1 On ou IO1 IOn (2<n<15).

On peut galement trouver:

- Une entre d'horloge (Clock): Clk ou Clock.

- Une entre de validation des sorties trois

tats: OE (Output Enable) ou Enable.

- Une entre de remise zro des registres:

RESET.

9

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Structure de base dun P.L.D

Symbolisation normalise

Un exemple de ce type de structure

est prsent ici :

On peut remarquer que la reprsentation

dune telle structure est complexe alors que le

nombre de portes intgres est peu

important.

10

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Structure de base dun P.L.D

Les constructeurs ont donc trs

rapidement adopts un autre type de

reprsentation rendant les schmas

beaucoup plus lisibles.

On remarquera que la norme adopte

est amricaine (normal, la plupart des

constructeurs sont amricains).

Un exemple de cette reprsentation est

donn ici:

Cette figure reprsente la structure interne

dun PLD ayant ses fusibles intacts. Les

quations logiques de Q0 et Q1 sont :

Q0 = Q1 = a./b./a.b + a./b./a.b + a./b./a.b + Structure de base avec les normes des

constructeurs

a./b./a.b = 0

11

Somme des Termes produits

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Structure de base dun P.L.D

Si on veut obtenir les fonctions Q0 = a./b + /a.b et Q1 = /a./b + a.b , on grillera des

fusibles de faon obtenir le schma suivant :

PLD programm

12

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Exercices

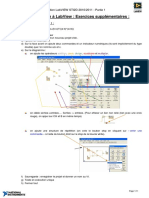

Implanter les quations suivantes dans le PAL 22V10 ci-dessous.

F = /a.b + /c./b./a + c.b

G = /a + /b

On marque d'une croix les fusibles

laisss intact.

Prciser comment sont les fusibles d'un

terme produit non utilis. Il faut en effet que

le terme produit correspondant n'influence

pas la sortie. Le terme est donc annul en

configurant les fusibles de la bonne

manire.

13

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Exercices

Implanter les quations suivantes dans le PAL 22V10 ci-dessous.

F = /a.b + /c./b./a + c.b

G = /a + /b

Prciser comment sont les fusibles d'un

terme produit non utilis. Il faut en effet que

le terme produit correspondant n'influence

pas la sortie. Le terme est donc annul en

configurant les fusibles de la bonne

manire.

Un terme produit non utilis est

neutralis en ralisant le calcul

de la valeur logique 0, quelque

soit la valeur sur son entre.

14

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Exercices

Implanter les quations suivantes dans le

PAL suivant :

F = /e + a.d + /g.a./d + h.e./a

H = a./d./c.e + /g.d.c

La validation du PAL est ralise par une

quation

Enable F = a.d

Enable H = c.h

Prciser comment sont grs les termes

produits non utiliss.

15

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Les diffrentes structures

Dans l'exemple du cours et les deux exercices prcdent, la programmation tait

facilement ralisable, ce n'est pas toujours le cas. C'est pourquoi il existe un

grand nombre de P.A.L. utilisant des structures de sorties diffrentes. On peut

distinguer trois types de structures de base:

- Combinatoire. - Squentielle. - Versatile.

1. Combinatoire: Il existe trois types:

- H -> (High) Porte ET suivit d'une Porte OU. Sortie active l'tat haut.

- L -> (Low) Porte ET suivit d'une Porte NON OU. Sortie active l'tat bas.

- C -> (Combine) programmable en type H ou L.

16

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Les diffrentes structures

2. Squentielle: Il existe trois types:

- R -> (Register): Registre.

Registre Ces circuits sont composs de bascule D. Les sorties

des bascules sont de type trois tats contrles par un signal de validation

Enable ou OE, et une horloge est commune toutes les bascules (clock).

- X -> (Register Or Exclusif): Ou Exclusif et Registre.

17

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Les diffrentes structures

2. Squentielle (suite):

-RA -> (Register Asynchron):

Registre asynchrone.

Les structures de sorties sont

beaucoup plus volues par

rapport aux autres P.A.L., elles se

rapprochent des P.A.L. de type

versatile.

Elles peuvent prendre quatre

configurations

suivant

les

valeurs de AP et AR.

18

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Les diffrentes structures

3. Les versatiles V:

Ce type de structure reprsente les

P.A.L. les plus volues, car les

structures de sorties dite versatile

proposent quatre configurations

possibles suivant les valeurs de S0

et S1.

Ce qui donne:

19

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Exemple de P.A.L

Le plus clbre des circuits

versatile est certainement le P.A.L.

22V10 de chez AMD. Il permet

d'muler pratiquement tout les

autres types de P.A.L. et dispose

d'un circuit de remise zro des

registres la mise sous tension du

circuit.

Schma interne dun PAL

22V10 : ( GAL22V10 Lattice

Semiconductor).

20

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Les rfrences des P.A.L.

Les constructeurs de P.A.L. ont standardis le marquage des P.A.L.

Chez AMD:

Chez TEXAS INSTRUMENTS:

21

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Remarques :

Les rfrences des P.A.L.

Le nombre dentres varie entre 8 et 22.

Le nombre de sorties varie entre 2 et 15.

La puissance est indique par une lettre code.

La vitesse indique le temps de propagation en nS.

Les versions versatiles ont une cellule de sortie programmable permettant dobtenir

nimporte quel autre type de structure de sortie (L, H, R ...).

Les versions CMOS (CE) sont effaables lectriquement. Les fusibles sont remplacs

par des transistors de type MOS FET. Ce ne sont ni plus ni moins que des GALs .

Un circuit P.A.L. peut tre dupliqu comme une EPROM, pour le protger les

constructeurs ont ajout un bit dit de scurit. Si ce bit est programm alors le

22

circuit ne peut plus tre relu.

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables (P.L.D.)

Les rfrences des P.A.L. Exemples:

PAL 16 L 8 H 15 PC : 16 entres maximum, L: Structure de sortie : Combinatoire

active Bas,

Bas 8 sorties maximum, H: Consommation : puissance, 15: Vitesse : 15 nS,

PC:

PC Type de botier : DIL plastique civile

23

Systmes Numriques

R. YAHIAOUI

Les G.A.L (Generic Array Logic).

Linconvnient majeur des PALs est quils ne sont programmables quune seule fois. Ceci

impose un gaspillage important de ces circuits lorsquon veut dvelopper un nouveau produit.

La firme LATTICE a donc pens, il y a un peu plus de 10 ans, remplacer les fusibles

irrversibles des PALs par des transistors MOS FET pouvant tre rgnrs.

rgnrs Ceci a donc

donn naissance aux GALs que lon pourrait traduire par Rseau logique Gnrique .

Ces circuits peuvent donc tre reprogramms volont sans pour autant avoir une dure de

vie restreinte. On peut aussi noter que dans leur structure interne les GALs sont constitus

de transistor CMOS alors que les PALs classiques sont constitus de transistors bipolaires.

La consommation des GALs est donc beaucoup plus faible.

faible Depuis dautres constructeurs

fabriquent ce type de produit en les appelant PAL CMOS .

Par soucis de remplacer les PALs, LATTICE a quip la plupart de ses GALs de macrocellules programmables permettant dmuler nimporte quel PAL. Ces structures de sortie

sont donc du type Versatile (V).

EMULER : Se dit d'un systme pouvant fonctionner comme un autre systme travers des

fonctions pour lesquelles il n'avait pas t prvu l'origine, sorte de compatibilit a posteriori.

24

Systmes Numriques

R. YAHIAOUI

Les G.A.L (Generic Array Logic).

Protection Contre la Duplication

Comme pour les PAL, les GAL sont dots dun bit de scurit qui peut tre activ lors de

la programmation empchant ainsi toute lecture du contenu du circuit.

circuit Ce bit est remis

zro seulement en effaant compltement le GAL.

Il est aussi constitu dun ensemble de huit octets, appel signature lectronique,

pouvant contenir des informations diverses sur le produit.

Rfrence des GAL

Le nombre de types de GAL est de 8.

8 Les deux 2 derniers-ns prsentent une structure

plus particulire. Les six plus anciens sont diffrencis par leurs nombres dentres et

de sorties. Ils possdent une structure de sortie soit du type Versatile soit du type

Registre asynchrone .

25

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables Complexes(Les C.P.L.D)

Les CPLDs pour (Complex Programmable Logic Device) ont une capacit en

nombre de portes et en possibilits de configuration trs suprieure celle des

PALs. Leurs architectures sont bases sur celles des PALS. Un CPLD cest

lquivalent de plusieurs PALs mis dans le mme circuit associ une zone

dinterconnexion. Le nombres de portes peut varier entre 100 et 100 000 portes

logiques et entre 16 et 1000 bascules voir plus.

Structure gnrale dun CPLD.

26

Systmes Numriques

R. YAHIAOUI

Les Circuits Logiques Programmables Complexes(Les C.P.L.D)

PIA (Programmable Interconnect Array)

27

Systmes Numriques

R. YAHIAOUI

LES F.P.G.A.s (Fields Programmable Gate Array).

Introduction:

les FPGAs la diffrence des CPLDs sont assimilables des A.S.I.C. (Application Specific Integrated

Circuit) programmables par lutilisateur.

La puissance de ces circuits est telle quils peuvent tre composs de plusieurs milliers voire millions de

portes logiques et de bascules. Les dernires gnrations de FPGA intgrent mme de la mmoire vive

(RAM). Les deux plus grands constructeurs de FPGA sont XILINX et ALTERA.

28

Systmes Numriques

R. YAHIAOUI

LES F.P.G.A.s (Fields Programmable Gate Array).

Architectures:

Row-based architecture

consiste en une alternance de

ranges de modules logiques

programmables et de pistes

d'interconnexion.

Sea of gates architecture ou mer

de transistors (portes).

29

Systmes Numriques

R. YAHIAOUI

LES F.P.G.A.s (Fields Programmable Gate Array).

30

Systmes Numriques

R. YAHIAOUI

LES F.P.G.A.s (Fields Programmable Gate Array).

lments logiques

LE

Cellules I/O

Interconnexions :

Fusibles, antifusibles,

EEPROM, RAM

Structure CPLD

(Complex Programmable Logic Device)

Structure FPGA

(Field Programmable Gate Array)

31

Fabricants : Xilinx, Altera, Atmel, Cypress, Quicklogic, Actel

R. YAHIAOUI

UFR Sciences et Techniques Besanon

Licence EEA 3me Anne

Le VHDL plus en dtails

Cours

32

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Pourquoi avoir cr un langage de description de structures lectroniques (H.D.L.

Hardware Description language) VHDL ?

Labrviation VHDL signifie VHSIC Hardware Description Language (VHSIC :

Very

High Speed Integrated Circuit). Ce langage a t crit dans les annes 70 pour

raliser la simulation de circuits lectroniques. On la ensuite tendu en lui rajoutant

des extensions pour permettre la conception (synthse) de circuits logiques

programmables (P.L.D. Programmable Logic Device).

Auparavant pour dcrire le fonctionnement dun circuit lectronique programmable

les techniciens et les ingnieurs utilisaient des langages de bas niveau (ABEL,

PALASM, ORCAD/PLD,..) ou plus simplement un outil de saisie de schmas.

Actuellement la densit de fonctions logiques (portes et bascules) intgre dans

les PLDs est telle (plusieurs milliers de portes voire millions de portes) quil

nest plus possible dutiliser les outils dhier pour dvelopper les circuits

daujourdhui.

33

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les socits de dveloppement et les ingnieurs ont voulu saffranchir des

contraintes technologiques des circuits. Ils ont donc cr des langages dits de haut

niveau savoir VHDL et VERILOG. Ces deux langages font abstraction des

contraintes technologies des circuits PLDs.

Ils permettent au code crit dtre portable, cest dire quune description crite

pour un circuit peut tre facilement utilise pour un autre circuit.

Il faut avoir lesprit que ces langages dits de haut niveau permettent de matrialiser

les structures lectroniques dun circuit.

En effet les instructions crites dans ces langages se traduisent par une

configuration logique de portes et de bascules qui est intgre lintrieur des

circuits PLDs. Cest pour cela quon prfre parler de description VHDL ou

VERILOG que de langage.

34

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Relation entre une description VHDL et les circuits logiques

programmables.

Limplantation dune ou de plusieurs descriptions

VHDL dans un PLD va dpendre de laffectation

que lon fera des broches dentres / sorties et des

structures

de

base

du

circuit

logique

programmable.

Lors de la phase de synthse chaque bloc sera

matrialis par des portes et/ou des bascules. La

phase suivante sera dimplanter les portes et les

bascules lintrieur du circuit logique.

Schma fonctionnel dimplantation de

descriptions VHDL dans un circuit logique

programmable.

Cette tche sera ralise par le logiciel placement/routage ( Fitter ), au cours de

laquelle les entres et sorties seront affectes des numros de broches.

On peut remarquer sur le schma la fonction particulire du bloc VHDL N5. En effet

dans la description fonctionnelle dun PLD on a souvent besoin dune fonction qui sert

cadencer le fonctionnement de lensemble, celle-ci est trs souvent ralise par une

machine dtats synchronise par une horloge.

horloge

35

Systmes Numriques

R. YAHIAOUI

Organisation

fonctionnelle de

dveloppement dun

PLD.

36

Systmes Numriques

R. YAHIAOUI

Structure dune description VHDL simple.

Une

description

VHDL

est

compose

de

2

parties

indissociables savoir :

-Lentit (ENTITY), elle dfinit

les entres et sorties.

- Larchitecture

(ARCHITECTURE), elle contient

les instructions VHDL

permettant de raliser le

fonctionnement attendu.

Un dcodeur 1 parmi 4.

37

Systmes Numriques

R. YAHIAOUI

Structure dune description VHDL simple.

1) Dclaration des bibliothques.

Toute description VHDL utilise pour la synthse a besoin de bibliothques.

LIEEE (Institut of Electrical and Electronics Engineers) les a normalises et plus

particulirement la bibliothque IEEE1164. Elles contiennent les dfinitions des

types de signaux lectroniques, des fonctions et sous programmes permettant de

raliser des oprations arithmtiques et logiques,...

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.numeric_std.all;

Use ieee.std_logic_unsigned.all;

-- cette dernire bibliothque est souvent utilise pour lcriture de compteurs

La directive Use permet de slectionner les bibliothques utiliser.

38

Systmes Numriques

R. YAHIAOUI

Structure dune description VHDL simple.

2) Dclaration de lentit et des entres / sorties (I/O).

39

Systmes Numriques

R. YAHIAOUI

Structure dune description VHDL simple.

2) Dclaration de lentit et des entres / sorties (I/O).

2.1) Le NOM_DU_SIGNAL.

Il est compos de caractres, le premier caractre doit tre une lettre, sa longueur est

quelconque, mais elle ne doit pas dpasser une ligne de code. VHDL nest pas

sensible la casse , cest dire quil ne fait pas la distinction entre les majuscules

et les minuscules.

2.2) Le SENS du signal.

- in : pour un signal en entre.

- out : pour un signal en sortie.

- inout : pour un signal en entre sortie

- buffer : pour un signal en sortie mais utilis comme entre dans la description.

2.3) Le TYPE.

Le TYPE utilis pour les signaux dentres / sorties est :

- le std_logic pour un signal.

40

- le std_logic_vector pour un bus compos de plusieurs signaux.

Systmes Numriques

R. YAHIAOUI

Structure dune description VHDL simple.

3) Dclaration de larchitecture correspondante lentit : description du

fonctionnement.

fonctionnement

Larchitecture dcrit le fonctionnement souhait pour un circuit ou une partie du circuit.

En effet le fonctionnement dun circuit est gnralement dcrit par plusieurs modules

VHDL. Il faut comprendre par module le couple ENTITE/ARCHITECTURE. Dans le

cas de simples PLDs on trouve souvent un seul module.

Larchitecture tablit travers les instructions les relations entre les entres et les

sorties. On peut avoir un fonctionnement purement combinatoire, squentiel voire les

deux squentiel et combinatoire.

41

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Rsum:

En VHDL, une structure logique est dcrite l'aide d'une entit et d'une

architecture de la faon suivante:

42

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Exemple:

43

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Exemple:

44

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Exemples de

Dclaration de larchitecture

45

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Description comportementale et structurelle

Il existe deux faons distinctes de dcrire une structure. L'une dite comportementale

et l'autre structurelle.

structurelle

Description comportementale

Dans ce type de

description, le

comportement de la

structure est directement

inscrit dans l'architecture

l'aide d'instructions

squentielles ou sous

forme de flow de

donnes.

46

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Description comportementale et structurelle

Description Structurelle

47

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Description comportementale et structurelle

Description Structurelle

48

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

Quest ce que le mode concurrent ? Pour une description VHDL toutes les

instructions sont values et affectent les signaux de sortie en mme temps.

Lordre dans lequel elles sont crites na aucune importance. En effet la description

gnre des structures lectroniques, cest la grande diffrence entre une description

VHDL et un langage informatique classique.

Dans un systme microprocesseur, les instructions sont excutes les unes la suite

des autres.

Avec VHDL il faut essayer de penser la structure qui va tre gnre par le

synthtiseur pour crire une bonne description, cela nest pas toujours vident.

49

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

Pour le dcodeur 1 parmi 4 au transparent 98, lordre dans lequel seront crites les

instructions na aucune importance.

Linstruction dfinissant ltat de D0

t dplace la troisime ligne, la

synthse de cette architecture est

quivalente la premire.

50

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

1.a) Laffectation simple : <=

1) Les oprateurs.

51

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

1.a) Laffectation simple : <=

52

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

1.b) Oprateur de concatnation : &.

Cet oprateur permet de joindre des signaux entre eux .

53

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

1.c) Oprateurs logiques.

54

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

1.d) Oprateurs arithmtiques.

55

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

1.e) Oprateurs relationnels.

56

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

2) Les instructions du mode concurrent .

2.a) Affectation conditionnelle :

57

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

2) Les instructions du mode concurrent .

2.a) Affectation conditionnelle :

58

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

2) Les instructions du mode concurrent .

2.b) Affectation slective :

Cette instruction permet daffecter diffrentes valeurs un signal, selon les valeurs

prises par un signal dit de slection.

59

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

2) Les instructions du mode concurrent .

2.b) Affectation slective :

60

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

2) Les instructions du mode concurrent .

2.b) Affectation slective :

61

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

2) Les instructions du mode concurrent .

2.b) Affectation slective :

62

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions de base (mode concurrent ), logique combinatoire.

2) Les instructions du mode concurrent .

2.b) Affectation slective :

63

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions du mode squentiel

1) Dfinition dun PROCESS.

64

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions du mode squentiel

2) Les deux principales structures utilises dans un process.

65

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions du mode squentiel

3) Exemple de Process

Commentaires

-Seul le signal CLK fait partie de la liste de

sensibilit. Daprs les rgles de fonctionnement

nonces prcdemment, seul un changement dtat

du signal CLK va dclencher le process et par

consquent valuer les instructions de celui-ci.

-Linstruction if (CLK'event and CLK='1') then permet

de dtecter un front montant du signal CLK. La

dtection de front est ralise par lattribut event

appliqu lhorloge CLK. Si on veut un

dclenchement sur un front descendant, il faut

crire linstruction suivante : if (CLK'event and

CLK='0').

-Les bibliothques IEEE possdent deux instructions

permettant de dtecter les fronts montants )

rising_edge(CLK)

ou

descendants

falling_edge(CLK).

- Si la condition est remplie alors le signal de sortie S

sera affect avec la valeur du signal dentre D. 66

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions du mode squentiel

4) Les compteurs :

Ils sont trs utiliss dans les descriptions VHDL. Lcriture dun compteur peut tre

trs simple comme trs complique. Ils font appels aux process.

4.1) Compteur simple :

67

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions du mode squentiel

68

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions du mode squentiel

69

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions du mode squentiel

4.2) Compteur mise un SET et mise zro RESET :

70

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les instructions du mode squentiel

4.3) Compteur / Dcompteur entre de prchargement :

Remarque : La mise zro des sorties du compteur

passe par linstruction : CMP <= "0000";

une autre faon dcrire cette instruction est :

CMP <= (others => 0) ;

Cette dernire est trs utilise dans les descriptions

car elle permet de saffranchir de la taille du bus. En

effet others=>0 correspond mettre tous les bits

du bus zro quelque soit le nombre de bits du bus.

De la mme faon on peut crire others=>1 pour

mettre tous les bits un.

71

Systmes Numriques

R. YAHIAOUI

Introduction la Synthse logique - VHDL

Les composants programmables proposs par ALTERA sont de type

EEPROM et SRAM.

ALGORITHME DE PROGRAMMATION

1) Ecriture du fichier VHDL

2) Compilation (analyse syntaxique)

Si il y a une erreur elle est indique et parfois explique.

Correction et compilation jusqu limination de toutes les erreurs

3) Simulation fonctionnelle

Si les signaux obtenus ne correspondent pas ceux esprs

Revoir lanalyse du problme

4) Choix du composant et affectation des broches

5) Compilation et fitter (le logiciel intgre le fichier compil dans le composant)

Si le fittage choue (composant trop petit , affectation des broches trop

contraignante)

Changer de composant. Revoir le fichier VHDL (analyse)

6) Simulation tenant compte des temps de propagation

Si les signaux obtenus ne correspondent pas ceux esprs

Changer de composant. Revoir le fichier VHDL (analyse)

7) Programmation du composant (transfre du fichier de configuration par un cble entre le

PC et la carte)

72

R. YAHIAOUI

THE END

73

Вам также может понравиться

- A. Premier Cas: Ve2 Ve1Документ2 страницыA. Premier Cas: Ve2 Ve1BOURAS Ihabe - بوراس إيهابОценок пока нет

- TD Fpga Cs 2015Документ5 страницTD Fpga Cs 2015hakim100% (1)

- Cours410 Document Synthã SeДокумент148 страницCours410 Document Synthã Seferiel aissiОценок пока нет

- Cours4 OracleSQL DMLДокумент13 страницCours4 OracleSQL DMLNheb Naares Nheb NaareesОценок пока нет

- Ct-1plan de ProtectionДокумент32 страницыCt-1plan de ProtectionKDA100% (1)

- Atelier Photo: Cours 2Документ18 страницAtelier Photo: Cours 2المحرر التربوي ميلود حاجبОценок пока нет

- Capteur de Température, (Bac STL Physique de Laboratoire 2009)Документ7 страницCapteur de Température, (Bac STL Physique de Laboratoire 2009)Imen HammoudaОценок пока нет

- MANUEL DE RÉFÉRENCE VAL3. Version 7Документ192 страницыMANUEL DE RÉFÉRENCE VAL3. Version 7Vincent PateloupОценок пока нет

- Zelio Time - RE9RA11MW7Документ8 страницZelio Time - RE9RA11MW7Dominique KomeyОценок пока нет

- ServomoteurДокумент2 страницыServomoteurAbouZakariaОценок пока нет

- Rapport de Stage CCA 2014Документ36 страницRapport de Stage CCA 2014ThourayaAouledMessaoud100% (11)

- Exercice S 1Документ5 страницExercice S 1gamalОценок пока нет

- TP 1Документ9 страницTP 1Ygb RedaОценок пока нет

- Béton ArmeeДокумент8 страницBéton ArmeeMarwenОценок пока нет

- Les Systèmes de Répartition Aérienne, La Troisième PartieДокумент6 страницLes Systèmes de Répartition Aérienne, La Troisième Partieهانى خيرОценок пока нет

- Comment Doubler Votre Drague PDFДокумент2 страницыComment Doubler Votre Drague PDFIvan50% (2)

- Chapitre 1Документ9 страницChapitre 1Tiavina SafidyОценок пока нет

- Exercice Electricite 2-16 PDFДокумент1 страницаExercice Electricite 2-16 PDFRabieZedОценок пока нет

- Matrices Emu8086Документ14 страницMatrices Emu8086Angel LigthОценок пока нет

- SallenДокумент1 страницаSallenAbderrahmane SmaaliОценок пока нет

- TD 3 - Corrigé - MicrocontrôleurДокумент9 страницTD 3 - Corrigé - MicrocontrôleurMontassar ZaraiОценок пока нет

- HarmoniqueДокумент17 страницHarmoniqueDJAMEL EDDINE FEKIRОценок пока нет

- C Telefono Universal VEOV0421Документ2 страницыC Telefono Universal VEOV0421Jose TorresОценок пока нет

- Master Electronique Energie Electrique Automatique Parcours AutomatiqueДокумент5 страницMaster Electronique Energie Electrique Automatique Parcours AutomatiqueTarak BenslimaneОценок пока нет

- Exercices SujetДокумент11 страницExercices SujetLycée Menzel HayetОценок пока нет

- Electronique de Puissance Avancée 2016-2017Документ26 страницElectronique de Puissance Avancée 2016-2017SADOKОценок пока нет

- Electronique de Puissance TLe F3, 2023-2024Документ3 страницыElectronique de Puissance TLe F3, 2023-2024Maxim MeliОценок пока нет

- Le Blog de Maia (FR)Документ10 страницLe Blog de Maia (FR)sofiaОценок пока нет

- Presentation KdenliveДокумент50 страницPresentation KdenlivepinonvОценок пока нет