Академический Документы

Профессиональный Документы

Культура Документы

White Paper: Selecting The Correct High Speed Transceiver Solution

Загружено:

knowhim26002Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

White Paper: Selecting The Correct High Speed Transceiver Solution

Загружено:

knowhim26002Авторское право:

Доступные форматы

White Paper

Selecting the Correct High Speed

Transceiver Solution

Introduction

Many standards and protocols are now using high speed transceivers (SERDES) as part of their physical

interface. The protocols cover a spectrum of applications including communications, computer, industrial

and storage, where there is a need to move large quantities of data between chips or across backplanes, but

traditional parallel bus interfaces can no longer be relied upon. One technology emerging to support many

of these applications is the FPGA architecture with embedded High Speed 3.125 Gbps transceivers. This

allows the user to develop a full system of chip solutions by providing both a physical layer

implementation and the logic to provide full hardware support for the rest of the application. These devices

also provide all of the historical benefits of FPGA architecture including flexibility, ease of use and quick

time to market, all qualities required as these new protocols emerge.

A number of solutions now exist in the market, including Application Specific Standard Product (ASSP),

Application Specific Integrated Circuits (ASIC) and FPGA with Embedded high speed transceivers. This

paper outlines some of the considerations when selecting among these products.

ASSP for high speed design

Traditionally High Speed Interfacing has been implemented using ASSP devices. ASSP solutions tend to

require multiple chips to provide the solution. This is partly due to the rate at which the technology grew,

and partly because the transceiver requires different process technology compared to the rest of the system.

Initially the system is very modular; for example, a SERDES solution would consist of a separate

transceiver, a Serializer/Deserializer and an encoder/decoder. However more recently these have been

merged into a single chip solution.

While it is common to integrate transceivers into higher layer ICs, the challenge remains for many ASSP

vendors to define and design a chip that can support multiple protocols or applications. This is a

challenging task since in most cases standards and market dynamics are in a constant state of flux. Today,

some separation is still necessary because it is not possible to generate a one fits all protocol ASSP

product, so it is often more cost effective to make a generic product which covers a number of

applications. ASSPs reliance on multiple devices to provide a solution has a number of disadvantages to

the high speed designer

Interoperability Connectivity between ASSPs is generally parallelized for chip to chip transfer. In

order to maintain the data rate, parallel interfaces must continue to run at (relatively)

high speeds, support double data rates (data on both edges of the clock) and support

wide bus widths. High speed parallel busses are extremely susceptible to skew

between signal, noise and crosstalk, causing difficult layout conditions. These issues

are greatly reduced by single chip solutions much of the data processing can occur in

the same device as the transceiver, reducing the number of chip to chip connections.

A good transceiver based solution will also provide a balanced parallel interface

with additional circuitry to overcome skew and signal integrity issues.

September 2003, ver. 1.0

WP-HGSPDTRNS-1.0

Selecting the Correct High Speed Transceiver Solution

Power

PCB layout

Altera Corporation

Multiple ASSP solutions have a greater power budget than a single chip solution.

Firstly there is the issue of each device requiring its own core supply and secondly

the parallel bus interfaces between ASSPs require additional power to be able to

drive signals between chips. Both these issues can be significantly reduced by a

single chip solution.

Multiple chip solutions require a more a complex layout. Firstly there is the issue of

PCB real estate, where a single chip will require less room than multiple chip

solutions, particularly when considering passives required for decoupling and signal

integrity. Secondly, layout is complicated by the high speed, wide parallel (source

synchronous busses) which must be carefully laid to avoid skew, noise and crosstalk.

ASSPs on the whole can provide a reasonable solution, particularly where the channel requirement is low.

They are also ideal at the higher end of the market, where they can use dedicated processes to generate

devices to reach higher data rates and better jitter requirements. However, many applications require the

ASSP to interface to either an ASIC or FPGA for data processing, so as mainstream ASIC or FPGA

embraces the transceiver architecture, it makes sense for engineers to use these solutions to overcome the

issues highlighted above.

ASIC for high speed design

ASIC has generally been viewed as a good single chip solution for high speed design. ASIC allows the

user to fully customize the design to meet their application needs, overcoming issues such as channel

limitations and it enables the user to add functionality around the transceiver for a particular application or

protocol. ASIC enables the user to develop a full data path solution in a single chip, reducing the number

of external busses between devices and removing some of the interoperability issues associated with

interconnectivity.

However there are a number of new trends emerging which will make only the highest volume solutions

viable for ASIC design.

Cost and Time The cost and time to market issues of ASIC issues are heavily documented,

particularly the design costs and design/verification time needed for low geometry

process technologies such as a 0.13um all layer copper technology. Transceiver

integrated ASIC devices require leading edge technology to enable the transceivers

to operate at high speed. Therefore the ASIC designer has little alternative but to

accept high NREs charges and long development and high verification times if they

are to implement design in ASIC.

Embedding transceivers into a digital domain is complex and often causes

significant design issues, particularly when preventing noise and jitter from crossing

between the transceiver and the logic domains. It is also difficult to select the correct

transceiver characteristics to meet the environment in which the device is likely to be

used. These issues invariably lead to multiple iterations of the silicon, massively

increasing the development costs. Modeling software is now available to overcome

some these issues, but it is extremely expensive, time consuming and requires

leading edge hardware to run and operate successfully.

Altera Corporation

Flexibility

Selecting the Correct High Speed Transceiver Solution

Many new protocols are now adopting high speed transceiver technology as a

standard interface technology. Many of the protocols are still standardizing so it is

possible that some may merge or disappear. It is therefore important that the device

technology used to support new protocols is flexible enough to cope to with design

issues or changes in order to extend the life of a product. ASIC is traditionally

inflexible and often needs to go through a difficult redesign process to cope with a

modification.

FPGA for high speed design

The integration of transceivers with FPGA architectures provides the user with many of the benefits of the

ASIC solution, but with the flexibility required to overcome changes in protocols or modifications required

in design. The FPGA solution provides a single chip solution and therefore overcome many of the

interoperability, layout and power requirements of multiple chip solutions. The transceivers supplied with

FPGA are also flexible, allowing them to operate in a number of different system environments helping to

overcome signal integrity issues. This flexible approach allows the same card to be used in a number of

different systems and applications.

The transceiver within the FPGA architecture can be viewed as partial ASSPs. Engineering effort

provided by the FPGA manufacturer reduces the effort required to design and verify the data path between

the FPGA and the transceiver. The transceiver are also designed and tested to work to a specific criteria

and to support specific protocols. These steps reduce the designers characterization and test workload,

during the compliance phase of the development and further reduce the time to market beyond the

traditional advantages offered by FPGAs.

In applications where the data rate exceeds the FPGA transceiver speed, or protocols where the data

throughput is higher than the bandwidth of FPGA, then it is possible that an ASSP or even an ASIC will

provide a better solution. However in these applications transceiver based FPGAs will still play a part in

the overall system design, and will interoperate with the other components in the system to provide a

complete solution.

Considerations when choosing a transceiver

Transceiver selection is fundamental to the whole system design, so decisions are made on performance

rather than brand loyalty or the type of design tool used on the previous design. The selection can be as

important as which Processor or DSP is to be used in the system, so the selection process often starts early

in the design phase and is carried out with a great deal of care.

Generally, system architects analyze the performance of the transceiver before making final decisions.

There are many criteria for the transceiver to meet during this selection phase, but the compliance to the

specification and its immunity to adverse conditions such as susceptibility to jitter and noise, or its ability

to drive along the transmission medium are key.

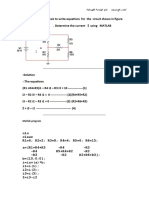

The empirical measurement of the transceiver performance is the eye diagram. This is a measurement of

the transceiver waveform pattern built up over a number of cycles and superimposed.

Selecting the Correct High Speed Transceiver Solution

Altera Corporation

Figure 1. Stratix GX transceiver eye diagram @ 3.125Gbps

The eye pattern can be used to show conformance to a particular specification by the use of an eye mask. If

the waveform does not cross the mask then it is seen to conform to the specification for jitter, noise and

amplitude. If the eye crosses the mask then it does not conform.

The Transceivers in the Stratix GX architecture are seen to have a superior eye quality. Figure 1 shows a

3.125Gbps eye diagram with 0% pre-emphasis and a VOD of 1000mV

While the transceiver performance is extremely important to the decision making process, there are also a

number of other considerations which need to be made when selecting the correct device. The following

section discusses some of these features.

Power

Power consumption is one major issue in virtually all applications, but particularly in a chassis based

systems, is power consumption. The fast switching requirements of the transceiver makes them inherently

power hungry, leading to a high power requirement. Power issues are prevalent in all transceiver solutions

including ASSP and ASIC because the issue is related to the analog portion of the transceiver rather than

the logic portion of the device.

Power consumption is a particular concern in chassis or backplane applications, where space is restricted

so power or heat problems must be kept under control for devices to stay within operating range. The costs

to implement adequate power management can be high. The techniques include:

4

Altera Corporation

Selecting the Correct High Speed Transceiver Solution

Heat sinks -which can greatly increase production costs.

Expensive chassis design involving custom metalwork.

Additional air flow involving the use of expensive fans. Additional cost introduced through additional

maintenance once the systems are installed.

Higher performance power supplies leading to extra component cost.

Stratix GX devices were designed with a low power PCML buffer to overcome some of the power

problems within the transceiver. Each Quad (block of 4 Transceivers which can be aligned to produce a

10Gbps interface) requires 475 mW to operate at 3.125 Gbps across 40 of FR4 fabric. A single channel

requires 175 mW per channel but that includes the overhead for all of the PMA section of the Quad.

Additional channels require only 100mW. Stratix GX transceivers provide further power savings by

allowing the transmitter or receiver to be disabled on a channel by channel basis. All these features have a

considerable power saving when compared to other FPGA solutions and many ASIC/ASSP solutions, thus

reducing overall system cost.

Signal Integrity

FPGA with embedded transceiver are ideal for inter chip communications, whether across a backplane or

for direct communication on a single card. Serial transceivers may be used to simplify a system by

replacing a high speed parallel bus. At high speed, parallel busses can suffer from skew and crosstalk,

making layout more complex. As the data rate increases the parallel bus width must increase to meet the

data requirement and the problem worsens. In this case serial transceivers are extremely useful and provide

the following advantages:

Simpler board layout.

Fewer components.

Fewer PCB layer.

However the properties of high speed signaling, or moreover the edge speeds, mean that transmission line

effects can make layout difficult. FR4 laminate material is widely used for PCB designs because it is

generally a good conductive material and is cost effective.

Unfortunately, at high data rates the copper tracking on the material suffers from the skin effect, where

high frequency signal trend to travel on the surface of the track, reducing the conductive area and

increasing the signal attenuation.

A larger problem is caused by dielectric loss, which like skin effect causes the PCB material to act as a low

pass filter and further attenuate the high frequency components from the signal. FR4 PCB material is

particularly susceptible to dielectric loss and has a high dielectric tangent tan(). Users can switch to an

alternative PCB material such as GETEK which has a lower tan(), or in other words is less lossy, but

comes at additional costs.

Stratix GX includes extra functionality within the receiver to help overcome these issues, making design

layout simpler and allowing the continued use of FR4 PCB fabric. More information on board layout can

be found in the Stratix GX board layout Guidelines.

Selecting the Correct High Speed Transceiver Solution

Altera Corporation

Programmable Drive Strength

Transmission line losses can be overcome by increasing the drive strength of the differential pair to boost

the signal seen by the receiver. The Stratix GX architecture allows the designer to select drive strength

between 4mA and 16mA. The actual Vod setting is determined by the termination resistor value.

Pre-emphasis

Issues associated with signal loss cannot always be solved by boosting the signal, as this will also boost

any noise or jitter on the line and will result in greater power consumption. One solution is to use signal

pre-emphasis, which effectively boosts the high frequency component of the transmitted signal by

emphasizing the first data symbol after any signal transition.

Stratix GX provides programmable transmission pre-emphasis, allowing the user to select the level,

depending on transmission medium and drive length. Figure 2a and 2b show the effect of 800mV signal

with pre-emphasis at the transmitter (0) and at the receiver (20) operating at 3.125 Gbps.

Figure 2a.

Figure 2b.

Receiver Equalization

Pre-emphasis is an useful tool in ovecoming transmission losses, but it can lead to greater power

requirements, produce more Electro-Magnetic Interference (EMI) and make the system more suceptable to

crosstalk. An alternative and more effective solution is to use Receive equalization. In many applications it

is possible to overcome the losses just by using Equalization and see better Bit Error performance . The

receiver equalization provides circuitry boosts the high frequency components of the signal at the receiver

end to compensate for the transmission losses, while leaving the low frequency components untouched.

Stratix GX is unique as it is the only FPGA solution to offer Receiver equalization. This enables Stratix

GX to interoperate with both ASIC and ASSP solutions over longer distances and in extremely poor

operating conditions, where other solutions may fail. Stratix GX allows the user to configure the equalizer

to operate at different track lengths. This ensures the system can be configured for its optimum

performance. Figure 3 shows the SPICE simulated results of equalization. Figure 3a shows a simulated eye

diagram into the receiver. Figure 3b shows the same signal after it has passed through receiver

equalization.

Under certain operating conditions such as legacy systems not designed to support high speed transceivers

or when interfacing to legacy devices, a combination of pre-emphasis and receiver equalization can

provide an effective solution, where a single function may not solve the problem.

6

Altera Corporation

Figure 3a SPICE simulated input to Equalizer

Selecting the Correct High Speed Transceiver Solution

Fig 3b SPICE Simulated output from Equalizer

An important factor when considering a backplane design is transceiver drive capability; this is particularly

an issue because the drive distance can be variable depending on backplane layout, number of slots in the

backplane and the overall location of the master and slave cards. Many devices offer a drive capability of

20 which on the first sight would seem adequate because backplane systems do not tend to exceed 19 in

length based on a typical 84HP chassis. However in reality, for a backplane that encompasses the whole of

a chassis, a card in slot one interfacing to a card in slot twenty could easily exceed 30, if you consider stub

lengths between the card and the backplane connector which are typically around 2 per card and the fact

that it is extremely unlikely the track on the backplane will take the most direct route, particularly if is end

to end.

The signal integrity feature in Stratix GX enables the device to operate over 40 of FR4 PCB fabric. This

allows Stratix GX to operate in the majority of backplane applications and conform to the form factor.

Hot socketing

An important aspect of system based design is hot socketing capability. Hot socketing capability within

High Speed Transceiver embedded FPGAs can be broken into two functions, Transceiver side and board

or FPGA side. Both are important aspects for in-system hot swap support.

The transceiver side describes the ability to add or remove a transceiver channel without damaging it and

without interrupting the other transceivers in the quad. This may, in the case of a line application, be a

number of channels connected via cables, where one cable is removed without detrimental effects to the

other channels. Alternatively in a backplane application, this could apply to a switch card connected to a

number of line cards. In this case a line card may be removed from the system without causing a data loss

between the switch card and the other line cards. Hot socketing capability is extremely important in many

applications, but particularly in telecom applications because it allows for system maintenance or upgrade

without any significant system down time.

FPGA hot socketing applies to the capability of the normal I/O to cope with the insertion or removal of the

device from a system or chassis. This is again important in for a line card in a system, because it provides

the ability to insert or remove a system or card from a backplane without damage and expect it to start up.

Stratix GX provides a solution for both transceiver and FPGA based hot socketing. Each transceiver is

immune to the effects of the other transceivers being connected or disconnected. In addition the transceiver

can be programmed to signal errors to the FPGA, such as a loss of lock signal from the Clock Recovery

Unit when a connection is lost. The FPGA I/O within Stratix GX is designed to operate in a mixed signal

environment and can tolerate any possible power up sequence. In effect this means that the Stratix GX I/O

can be driven before or during a power up sequence without damage. The FPGA I/O is also designed not to

7

Selecting the Correct High Speed Transceiver Solution

Altera Corporation

drive out during power up and prior to configuration, meaning a board can be inserted into a system

without interfering with its operation.

Self-Test

Self test of the transceiver and associated circuitry is an invaluable tool during the development and debug

phase of a project. It allows the designer to test operation without the need to interface to external systems

or devices. These techniques can also be used in the field for diagnosis. In order for self test to be useful, it

is important that is has the ability to generate and detect codes or patterns in the transceiver. Self test

modes must be flexible to enable test on different aspects of the transceiver.

Stratix GX provides a comprehensive self test solution. It provides the ability to perform both serial loop

and parallel loop testing. Serial loop back tests the blocks within the serial data path by looping back

between the output of the transmitter serializer and the receiver deserializer. Parallel loopback tests the

circuitry within the parallel portion of the transceiver, looping from the transmitter synchronizer FIFO,

through the 8b10b encoder and then back into the receiver FIFO via the 8b10b decoder, word aligner,

pattern detector and rate matcher. A further parallel mode allows the user to bypass the 8b10b circuitry.

Stratix GX also includes two different pattern generators:

1.

2.

BIST generator and detector can be used to verify the entire transceiver by transmitting and

receiving a set pattern via both serial and parallel loopback modes. The BIST generator can be

programmed to generate a number of different test codes depending on the application.

PRBS generator and detector are used to generate and verify a PRBS pattern through the

transceiver, supporting both serial and parallel modes. PRBS testing is particularly useful for

performing Bit Error Rate testing and the Stratix GX device can be configured to generate a BIST

flag if an error is recorded.

The self test modes enable full speed real time testing of the transceiver. In each case, test can be

independent of the FPGA fabric, enabling the user to determine the suitability of the product without the

need to generate the entire design.

Source Synchronous Support

Many applications cannot rely on high speed transceivers to support applications and will therefore require

some sort of high speed source synchronous (i.e. parallel) interface to provide data balance. Source

Synchronous I/O describes an interface where clock and data are transmitted separately. As a link layer

interface, Source Synchronous I/O can be used to move data from the transceiver into the rest of the system

for processing. It is therefore important that the source synchronous I/O can support a sufficiently high

data bandwidth to ensure the transceivers is permanently provisioned with data.

One example could be the SDH/SONET line card, where the line side of the interface would use high

speed transceivers to support a 10Gbps interface, supporting the OC-192 specification; the backplane side

of the interface could use an SPI4.2 as a bus interface across a backplane or interfacing to a network

processor.

Another example would be high speed protocol which does not offer support for a CDR based transceiver.

In this case, the interface will again be required to use a source synchronous interface.

Altera Corporation

Selecting the Correct High Speed Transceiver Solution

In either case, source synchronous design is made difficult because of skew between clock and data or

different data channels, making it difficult for the receiver to interpret the data and align it to the clock.

The Source Synchronous I/O elements provide by Stratix GX includes Design Phase Alignment (DPA)

circuitry to overcome these issues. DPA operates by replicating the receiver clock signal into phases and

then aligning the nearest clock phase to the incoming data. Once the data has been aligned to the clock it

passes through a deserialzer and can be byte aligned.

DPA enables the Source Synchronous interface on Stratix GX to operate at speeds up to 1Gbps. This

superior data rate allows a higher bandwidth support to the transceiver interface. It also allows parallel

standards such as SPI-4.2 and Parallel Rapid I/O to run at a higher data rate. This allows the interface to

both support higher data rates and support further overheads for error correction and encryption.

For more information on the advantages of Dynamic Phase alignment refer to the document Advantages

of the Embedded DPA Circuitry in Stratix GX Devices

Protocol Advantages

XAUI

One of the primary aims of the transceiver blocks within the Stratix GX architecture is to support the

XAUI protocol. XAUI specification describes the interface between the Physical Coding Sublayer and the

Media Access Controller for 10Gbit Ethernet standard. XAUI was conceived as an alternative to original

the XGMII parallel interface and has been widely adopted for various applications including 10Gigabit

Ethernet line cards, LAN to WAN bridges (SONET to Ethernet) and in particular as a protocol layer for

backplane and chip to chip applications.

The XAUI protocol utilizes many of the functions used by other emerging protocols and is therefore an

ideal base for a transceiver design. Stratix GX has embraced this protocol not only by meeting the

electrical and jitter specifications but also by adding dedicated circuitry into the transceiver to make design

implementation simpler. AN249 Implementing 10 Gigabit Ethernet XAUI in Stratix GX devices provides a

full overview on how to use Stratix GX for XAUI applications. However it is worth mentioning one key

feature supported by Stratix GX:

Channel Alignment

The XAUI protocol requires 4 channels of 3.125Gbps data to support 10Gbps Ethernet (including 8B10B

overhead). The XAUI protocol inserts a special alignment character (/A/) into the data to allow the receiver

to detect the data and realign it.

The Stratix GX transceivers are provided as Quad interfaces, where 4 transceivers are aligned together.

The Quads include dedicated alignment, routing and clocking circuitry to gain optimum performance and

reduce latency. The internal alignment circuitry improves the efficiency within the FPGA, by removing the

need to use external routing, which could interfere with both the transceiver performance and the general

logic placements. This is particularly important because the alignment circuitry needs to meet tight time

constraints in order to operate successfully

Selecting the Correct High Speed Transceiver Solution

Altera Corporation

SDH/SONET

The Stratix GX architecture is well suited to SDH/SONET protocol backplane applications. Whilst there is

no standard protocol to support SDH/SONET backplane applications, many of the building functions used

for line side applications can be implemented in backplane applications. Stratix GX transceiver technology

provides a number of functions to support SDH/SONET based protocols.

Pattern Detection

Data Path

Clocking

The Stratix GX transceiver includes a Pattern Detector to locate Frame

Characters in the data stream. The pattern detector searches for A1A2 or

A1A1A2A2 characters as specified in the OC standards. Once located, the

pattern detector flags the word aligner to align the data into the pre transmitted

data alignment. The dedicated circuitry prevents the need to use precious logic

in the FPGA

Often FPGA solutions designed to support 8b10b encoded data do not offer

flexibility in the data path back to the FPGA, should the encoder circuitry be

bypassed. This is particularly applicable for protocols using 8 or 16 bit data

because the transceiver may only be able to support the protocols by using

circuitry within the FPGA to realign the data onto the correct word boundaries.

Stratix GX has a flexible bus structure within the Transceiver which can provide

support for 8, 10, 16 and 20 bit data between the transceiver and the FPGA,

even when the 8b10b encoders are bypassed.

Stratix GX architecture provides flexible PLLs to support the high speed

transceiver operation. The PLLs are granular, allowing for a number of

different standards to be supported from a single clock source. This is

particularly useful in SDH/SONET applications where a single clock source can

be used to support clock rates between 622Mbps and 3.125Gbps.This will allow

the same card to be used in a number of different applications.

For more information on how Stratix GX can be utilized in SDH/SONET applications refer to the

document Using Stratix GX for SONET/SDH backplane white paper.

SPI 4.2

Primarily used in OC-192 systems, the SPI-4.2 standard interfaces cell and packet transfers at 10-Gbps

between physical (PHY) and link layer devices. Due to layout issues discussed earlier in this document,

SPI-4.2 utilizes source synchronous data transfer and is therefore restricted to around 800mbps using

conventional I/O standards. However by using the DPA feature in Stratix GX, the interface can support

data rates of 1Gbps.

Depending on the use of the interface in the application, the operational speed of SPI4.2 can vary. Though,

if the interface is used on the system side, it tends to operate at higher data rates. This ensures the data from

a network processor is constantly available at framer to ensure no idle packets in the transmission pipe. For

this reason, the latest 10Gbps network processors tend to support 1Gbps interfaces.

For more information about the advantages of Stratix GX for the SPI-4.2 protocol refer to the document

Advantages of the Embedded DPA Circuitry in Stratix GX Devices

10

Altera Corporation

Selecting the Correct High Speed Transceiver Solution

Conclusion

The demand for high speed transceivers is increasing as more applications need to support higher data

bandwidths. Many new protocols are springing up to meet these challenges. There is now a real need for

flexible transceiver architecture to meet these needs. By integrating high-speed serial transceiver into the

high-performance Stratix architecture, the Stratix GX family provides a total solution for many different

applications. Transceiver technology has been carefully implemented to provide full functionality, while

also providing the flexibility to support modifications as these new protocols merge and change. The

transceivers properties, coupled with its low power requirement make it ideally suited to not just

backplane but also chip to chip and other aspects of transceiver design.

Copyright 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions

Company, the stylized Altera logo, specific device designations, and all other words and logos

101 Innovation Drive

San Jose, CA 95134

(408) 544-7000

www.altera.com

that are identified as trademarks and/or service marks are, unless noted otherwise, the

trademarks and service marks of Altera Corporation in the U.S. and other countries.* All other

product or service names are the property of their respective holders. Altera products are

protected under numerous U.S. and foreign patents and pending applications, maskwork

rights, and copyrights. Altera warrants performance of its semiconductor products to current

specifications in accordance with Alteras standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no

responsibility or liability arising out of the application or use of any information, product, or

service described herein except as expressly agreed to in writing by Altera Corporation. Altera

customers are advised to obtain the latest version of device specifications before relying on

any published information and before placing orders for products or services.

11

Вам также может понравиться

- Intel Whitepaper - Intel® FPGAs and SoCs With Intel® FPGA AI Suite and OpenVINO Toolkit Drive Embedded/Edge AI/Machine Learning ApplicationsДокумент8 страницIntel Whitepaper - Intel® FPGAs and SoCs With Intel® FPGA AI Suite and OpenVINO Toolkit Drive Embedded/Edge AI/Machine Learning Applicationsknowhim26002Оценок пока нет

- White Paper: Compromises of Using A 10-Gbps Transceiver at Other Data RatesДокумент6 страницWhite Paper: Compromises of Using A 10-Gbps Transceiver at Other Data Ratesknowhim26002Оценок пока нет

- Intel Whitepaper - FPGA Adaptive Software Debug and Performance AnalysisДокумент7 страницIntel Whitepaper - FPGA Adaptive Software Debug and Performance Analysisknowhim26002Оценок пока нет

- FPGA ArchitectureДокумент14 страницFPGA ArchitectureN Pradyumna KumarОценок пока нет

- Altera Whitepaper - DDR & DDR2 SDRAM Controller Compiler FAQДокумент5 страницAltera Whitepaper - DDR & DDR2 SDRAM Controller Compiler FAQknowhim26002Оценок пока нет

- Altera Whitepaper - Benefits of Altera's High-Speed DDR2 SDRAM Memory Interface SolutionДокумент10 страницAltera Whitepaper - Benefits of Altera's High-Speed DDR2 SDRAM Memory Interface Solutionknowhim26002Оценок пока нет

- WP 01190 Real Time SocsДокумент22 страницыWP 01190 Real Time SocsHugo MarcondesОценок пока нет

- White Paper: Challenges in Manufacturing Reliable Lead-Free and RoHS-Compliant ComponentsДокумент11 страницWhite Paper: Challenges in Manufacturing Reliable Lead-Free and RoHS-Compliant Componentsknowhim26002Оценок пока нет

- Enhancing High-Speed TelecommunicationsДокумент5 страницEnhancing High-Speed Telecommunicationsknowhim26002Оценок пока нет

- Signal Integrity Comparisons Between Stratix II and Virtex-4 FPGAsДокумент10 страницSignal Integrity Comparisons Between Stratix II and Virtex-4 FPGAsknowhim26002Оценок пока нет

- Single-Resistor RSDS Solution For Cyclone II DevicesДокумент3 страницыSingle-Resistor RSDS Solution For Cyclone II Devicesknowhim26002Оценок пока нет

- Single-Resistor RSDS Solution For Cyclone II DevicesДокумент3 страницыSingle-Resistor RSDS Solution For Cyclone II Devicesknowhim26002Оценок пока нет

- Altera Voltage Regulator Selection For FPGAsДокумент8 страницAltera Voltage Regulator Selection For FPGAsknowhim26002Оценок пока нет

- Altera Leveraging The 40-Nm Process Node To Deliver The World's Most Advanced Custom Logic DevicesДокумент8 страницAltera Leveraging The 40-Nm Process Node To Deliver The World's Most Advanced Custom Logic Deviceskn65238859Оценок пока нет

- Bible in Basic English - New Testament - 3 JohnДокумент1 страницаBible in Basic English - New Testament - 3 Johnknowhim26002Оценок пока нет

- 1bible in Basic English - New Testament - 1 JohnДокумент5 страниц1bible in Basic English - New Testament - 1 Johnknowhim26002Оценок пока нет

- Bible in Basic English - New Testament - JudeДокумент2 страницыBible in Basic English - New Testament - Judeknowhim26002Оценок пока нет

- Altera 40-Nm FPGAs - Architecture and Performance ComparisonДокумент16 страницAltera 40-Nm FPGAs - Architecture and Performance Comparisonkn65238859Оценок пока нет

- Altera 40-Nm FPGA Power Management and AdvantagesДокумент15 страницAltera 40-Nm FPGA Power Management and Advantageskn65238859Оценок пока нет

- Bible in Basic English - New Testament - 2 JohnДокумент1 страницаBible in Basic English - New Testament - 2 Johnknowhim26002Оценок пока нет

- Bible in Basic English - New Testament - PhilemonДокумент2 страницыBible in Basic English - New Testament - Philemonknowhim26002Оценок пока нет

- Bible in Basic English - New Testament - 2 PeterДокумент4 страницыBible in Basic English - New Testament - 2 Peterknowhim26002Оценок пока нет

- Bible in Basic English - New Testament - 1 PeterДокумент6 страницBible in Basic English - New Testament - 1 Peterknowhim26002Оценок пока нет

- Bible in Basic English - New Testament - 2 TimothyДокумент5 страницBible in Basic English - New Testament - 2 Timothyknowhim26002Оценок пока нет

- Bible in Basic English - New Testament - 2 ThessaloniansДокумент3 страницыBible in Basic English - New Testament - 2 Thessaloniansknowhim26002Оценок пока нет

- Bible in Basic English - New Testament - TitusДокумент3 страницыBible in Basic English - New Testament - Titusknowhim26002Оценок пока нет

- Bible in Basic English - New Testament - 1 TimothyДокумент7 страницBible in Basic English - New Testament - 1 Timothyknowhim26002Оценок пока нет

- Bible in Basic English - New Testament - PhilippiansДокумент6 страницBible in Basic English - New Testament - Philippiansknowhim26002Оценок пока нет

- Bible in Basic English - Old Testament - MalachiДокумент5 страницBible in Basic English - Old Testament - Malachiknowhim26002Оценок пока нет

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- RUS - Long-Range Planning GuideДокумент43 страницыRUS - Long-Range Planning GuideClaud RichmondОценок пока нет

- Chengzhou WangДокумент159 страницChengzhou WangAnonymous n30qTRQPoIОценок пока нет

- R1 6Ω R4 4Ω R5 6Ω V1 10 VДокумент63 страницыR1 6Ω R4 4Ω R5 6Ω V1 10 Vď èОценок пока нет

- Data Sheet: CB-3-GDU-NF-13Документ2 страницыData Sheet: CB-3-GDU-NF-13rizkyОценок пока нет

- lm80 nt441 15 - CДокумент103 страницыlm80 nt441 15 - CAdhiezzz GamingОценок пока нет

- Emcp Specification: NCEPNA6M4-xxxxДокумент71 страницаEmcp Specification: NCEPNA6M4-xxxxPhone ShopОценок пока нет

- Neuron II Elgi CompressorДокумент42 страницыNeuron II Elgi CompressorOswaldo69% (16)

- Raptor Techn RevCA 704010EN WebДокумент194 страницыRaptor Techn RevCA 704010EN WebFranciscoОценок пока нет

- Absolute Sound Buyers Guide High End 2014Документ119 страницAbsolute Sound Buyers Guide High End 2014energiculОценок пока нет

- Bicmos TechnologyДокумент34 страницыBicmos TechnologyRahil Sharma100% (8)

- Automatic Generation Control in A Deregulated Power SystemДокумент6 страницAutomatic Generation Control in A Deregulated Power SystemamaytaОценок пока нет

- Design of A Cost Effective Micro Hydro Power Generation System Using The Discharge Water of The Central Steam Power PlantДокумент159 страницDesign of A Cost Effective Micro Hydro Power Generation System Using The Discharge Water of The Central Steam Power PlantNobel Engzen Du BermoyОценок пока нет

- Speed Control of DC Motor Using Mobile PhoneДокумент4 страницыSpeed Control of DC Motor Using Mobile PhonegowrishankarplОценок пока нет

- Fanucprofibusdp 04Документ279 страницFanucprofibusdp 04dfsfgОценок пока нет

- BOSS Slow Gear SG-1 Attack DelayДокумент1 страницаBOSS Slow Gear SG-1 Attack Delay大石 真義Оценок пока нет

- Avionics Unit 1Документ25 страницAvionics Unit 1Raahini IzanaОценок пока нет

- Seminar Report 2017 Vlsi Implementation of A Cost Efficient Near-Lossless Cfa Image Compressor For Wireless Capsule EndosДокумент31 страницаSeminar Report 2017 Vlsi Implementation of A Cost Efficient Near-Lossless Cfa Image Compressor For Wireless Capsule EndosAnanthu J VОценок пока нет

- MST 9001d Diesel Engine Ecu Test Rig Phs Instruction 1Документ13 страницMST 9001d Diesel Engine Ecu Test Rig Phs Instruction 1sk034jy081Оценок пока нет

- Intrerupatoare - Pagini de CatalogДокумент124 страницыIntrerupatoare - Pagini de CatalogClaudiu GheorgheОценок пока нет

- Disassembling System Unit Procedure and Safety PrecautionsДокумент28 страницDisassembling System Unit Procedure and Safety PrecautionsLourent Villy Conlu Casayuran100% (5)

- Samsung HP s4253 SpecsДокумент2 страницыSamsung HP s4253 SpecsKarina Esmeralda ZОценок пока нет

- SATIP-P-103-01 Rev 6Документ30 страницSATIP-P-103-01 Rev 6VISAKHОценок пока нет

- Technical Data UM202 - UM203Документ6 страницTechnical Data UM202 - UM203Anonymous 8rb48tZSОценок пока нет

- AD STICE CONNECT AD QFP44C-A02 AD QFP32B-A05 AD QFP64C-B02 To STICE-SYS001Документ10 страницAD STICE CONNECT AD QFP44C-A02 AD QFP32B-A05 AD QFP64C-B02 To STICE-SYS001Sebastian ChaileОценок пока нет

- Kamath Pole ZeroДокумент6 страницKamath Pole ZeroVenkatesh TatikondaОценок пока нет

- Chapter 9: 8086/8088 Hardware SpecificationsДокумент105 страницChapter 9: 8086/8088 Hardware Specificationssapna_eng4080Оценок пока нет

- Control Concepts Surge Protective Device Training ManualДокумент23 страницыControl Concepts Surge Protective Device Training ManualCatagña AnyОценок пока нет

- Digital Control of A Three Phase 4 Wire PWM Inverter For PVДокумент9 страницDigital Control of A Three Phase 4 Wire PWM Inverter For PV7788778887Оценок пока нет

- BTS Power Control R10Документ17 страницBTS Power Control R10Achmad SalsabilОценок пока нет

- Company Profile - RELAYS ENG.Документ92 страницыCompany Profile - RELAYS ENG.mОценок пока нет