Академический Документы

Профессиональный Документы

Культура Документы

Paper ADC

Загружено:

LJKarenИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Paper ADC

Загружено:

LJKarenАвторское право:

Доступные форматы

ESTUDIO DE CONVERSORES ADC Y DAC

Gabriel Ricardo Charry Villamagua

Karen Elizabeth Loaiza Jimnez

e-mail: gabrichav@yahoo.es

email: karencit_92@hotmail.com

Universidad Nacional de Loja

Loja, Ecuador

Abstract: La conversin A/D es un proceso de

cuantizacin de la cual una seal analgica es

representada por su equivalente en estados

binarios.

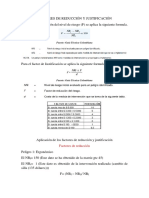

1.1 TIPOS DE CONVERTIDORES A/D.

Los convertidores A/D se pueden

bsicamente en los siguientes tipos:

clasificar

Palabras clave: ecuaciones en diferencias,

Laplace, Laurent, ROC (region of convergence).

1. INTRODUCCIN

Un conversor, (o convertidor) analgico-digital

(CAD), (o tambin ADC del ingls "Analog-toDigital Converter") es un dispositivo electrnico

capaz de convertir una entrada analgica de

voltaje en un valor binario, Se utiliza en equipos

electrnicos como computadora, grabadores de

sonido

y

de

vdeo,

y

equipos

de

telecomunicaciones. La seal analgica, que vara

de forma continua en el tiempo, se conecta a la

entrada del dispositivo y se somete a un muestreo

a una velocidad fija, obtenindose as una seal

digital a la salida del mismo.

Figura2. Tipos de convertidores A/D

Aunque no son los nicos, s son los ms tpicos.

Los que ms inters tienen por su aplicacin son

los marcados con asterisco (*).

1.1.1 APROXIMACIONES SUCESIVAS

En este circuito, se sustituye el contador por un

registro de aproximaciones sucesivas (RAS). La

idea de este circuito es lograr llegar al valor final,

sin tener que recorrer todos los anteriores. Para

ello, se pretende conocer en cada ciclo de reloj el

valor de un bit. En primer lugar el valor del bit ms

significativo Dn-1, despus el Dn-2 y as

sucesivamente.

El convertidor A/D es el nico elemento totalmente

indispensable en un sistema de adquisicin de

datos. Adems l por si slo puede constituir un

SAD. Generalmente suele ser el ms caro de

todos los elementos que constituyen el SAD

aunque, por supuesto, su precio depende de la

calidad de las prestaciones que se le pidan. Estas

sern: la exactitud, que depende de los errores

que se produzcan y de la resolucin (nmero de

bits), y la velocidad.

El mtodo consiste en colocar en primer lugar en el

registro el valor LHH...H. Si la VIN es superior a la

salida del D/A en ese caso, el amplificador lo

detectar dando saturacin positiva y un 1 en

salida. Por tanto para alcanzar el valor deseado

tendr que incrementar el bit de mayor peso, es

decir darle el valor H. Si por el contrario, el

amplificador hubiese dado a la salida un 0, el bit

estara en su valor correcto.

Figura1. Conversores A/D y D/C

Tras estos pasos el integrador comienza en cero y

como VIN es positivo, la salida del amplificador

estar en saturacin positiva. Con ello, a la salida

del comparador tendremos un 1 lgico, lo cual

permitir que la seal de reloj CLK alcance al

contador. A medida que se carga el condensador

aumenta el valor de salida del integrador VI. Esto

contina igual hasta que en un momento

determinado VIN es mayor o igual que VI lo que

hace que el comparador se sature negativamente,

y por tanto, VC = 0. En ese momento el resultado

de la puerta NAND es un uno lgico, con lo cual

impedimos que la seal CLK llegue al contador,

terminando as el proceso de conversin.

Figura3. Conversor A/D retroalimentado de Aproximaciones

Sucesivas.

Una vez conocido el valor de Dn-1 introducimos

como dato digital el siguiente: Dn-1 LHH...H y

comparamos la salida del D/A con VIN como se

hizo en el caso anterior. De esta manera

conseguimos saber tambin el valor de Dn-2.

Repitiendo este proceso en el tiempo conseguimos

obtener el valor buscado.

1.1.3 DOBLE RAMPA

La principal ventaja que presenta este dispositivo

frente a otros es que se necesita un ciclo de reloj

por cada bit. Por ello, para 12 bits slo son

necesarios 12 ciclos de reloj.

Figura5. Conversor A/D integrador de Doble Rampa.

1.1.2 SIMPLE RAMPA

Se hace la conversin en un slo paso.

Disponemos de un integrador y la tensin VIN

debe ser positiva (unipolar). Cuando SC=1,

entonces:

Los convertidores de este tipo son lentos: unas 3040 conversiones por segundo, es decir de 30-40

mseg lo cual permite que el oscilador es muy

sencillo del tipo RC.

Este convertidor es til ya que adems de tener

una dependencia baja de la salida con la entrada,

permite conseguir alta resolucin (24 bits o algo

ms). Sin embargo esta alta resolucin puede

presentar problemas de deriva o offset que se

resuelva mediante una tercera rampa (7109). Su

idea bsica es medir la deriva en la primera fase

poniendo la entrada a cero y aadiendo esta deriva

mediante un sumador en el resto del circuito. Se

aade, por tanto, un tiempo previo al primero que

es un ajuste de cero del A/D.

Se cierra el interruptor cortocircuitando el

condensador C, de manera que se descarga a

travs de la RON del interruptor.

Se resetea el contador colocndolo a cero.

La unidad de control permite que la seal de

reloj llegue al contador. Para ello coloca a 1 la

tercera entrada de la puerta AND.

Por otra parte, si VA<0 se necesitar que VREF

sea positiva.

Otra ventaja de este circuito es el bajo consumo

por estar fabricado en tecnologa CMOS. Son

tambin bastante inmunes al ruido sobre todo al de

alta frecuencia. Si, por ejemplo, se quiere convertir

una seal continua, si se observa sta

Figura4. Conversor A/D integrador de Simple Rampa.

detenidamente se ver que no tiene un nico valor

sino que oscila dentro de una banda de valores

(tiene ruido).

1.1.4 TENSIN-FRECUENCIA

En este tipo de convertidor se realiza una

conversin de la seal analgica de entrada a

frecuencia, midindose despus el valor de la

misma (antes la convertamos en tiempo). Este

circuito, por tanto, tendr dos partes bien distintas:

la primera convierte la seal a frecuencia y la

segunda mide esa frecuencia.

El convertidor completo ser:

Figura8. Conversor A/D Paralelo.

En donde, si el codificador tiene a la salida n

niveles, necesitamos 2n comparadores a la

entrada (para 8 bits se necesitan 256

comparadores). Las tensiones de referencia son

todos mltiplos de la tensin del LSB.

El funcionamiento de este comparador es simple:

todos aquellos comparadores en los que VIN sea

mayor que su tensin de referencia estar en

saturacin positiva mientras que los dems no. El

segundo nivel es un codificador que convierte las

2n entradas en n salidas.

Figura6. Conversor A/D integrador Tensin - Frecuencia.

La salida del contador ser la salida

convertidor. En el tiempo tendremos:

del

1.2 PARMETROS CARACTERSTICOS DE

LOS A/D

1.2.1 RESOLUCIN

Es el nmero de bits que posee la salida digital, se

mide en bits o en LSB. Los de aproximaciones

sucesivas son, como mucho, de 14 16 siendo lo

normal de 12 bits, aunque tambin los hay de 8

10. Con 8 bits resulta ser muy pobre el convertidor,

sin embargo si se busca bajo coste puede ser

adecuado. Para A/D discretos, no integrados, n=

10, 12 es lo ms corriente. En general podemos

decir que aquellos convertidores con n 12 bits se

consideran de alta resolucin.

Figura7. Contador.

Se trata de un circuito de bajo coste muy

interesante para el caso de aislamiento. Tambin

es interesante para el caso de transmisin de

informacin a larga distancia dado que la salida ya

se encuentra digitalizada y, por ejemplo, se puede

multiplexar varias de ellas a travs un multiplexor

digital.

1.1.5 CONVERTIDOR PARALELO

Se trata de un convertidor excepcionalmente

rpido pero muy complejo desde el punto de vista

del circuito. Su estructura tiene dos partes. En el

primer

nivel

aparecen

un

conjunto

de

comparadores

1.2.2 VELOCIDAD

En un A/D se pasa de dos magnitudes continuas V

y t a dos discretas. Al digitalizar, las tensiones se

convierten en A valores discretos, ya que la

resolucin no es infinita sino. La diferencia entre un

valor y el siguiente es el LSB, que se obtiene como

RANGO/2n.

Por otra parte al digitalizar la seal en el tiempo

tambin se discretiza. Se da la orden de comienzo

3

(SC, Start Conversion) y cuando se termina la

conversin el A/D da la seal de haber terminado

(EOC, End Of Conversion) y entre estas dos

seales transcurre un tiempo durante el cual se ha

realizado una conversin.

La medida que se digitaliza en cada instante no

ser, probablemente, el valor real de la seal, sino

el valor ms prximo dentro de la discretizacin de

V. Se produce, por tanto, un error de cuantizacin

que depende de n. Este error sera de 1 LSB o de

medio LSB como mximo dependiendo del mtodo

empleado. A medida que n sea mayor, menor ser

el error.

Figura9. Conversin Digital Analgica.

La estructura genrica de este tipo de conversores

es la que se ha indicado en la siguiente figura.

Igualmente se produce un error debido a la

discretizacin temporal. Cada instante de medida

ser ti = iT, siendo T la diferencia temporal entre

dos medidas.

La separacin temporal entre intervalos de

conversin T depender de la tecnologa del

convertidor, as podemos encontrar valores que

van desde 50ns a 50ms, como se aprecia tenemos

un factor de 106 entre ellos. Tambin influye la

separacin entre la toma de una medida y la toma

de la siguiente. De esta manera T lo podemos

hacer ms grande si nos interesa, pero no

disminuirlo por debajo de lo que el convertidor

pueda dar. En cualquier caso podemos decir que

leemos los datos con una separacin temporal T o

con una frecuencia F = 1/T, a la que se le da el

nombre de FRECUENCIA DE MUESTREO.

Figura10. Conversor D/A

2.2 TIPOS DE CONVERTIDORES D/A

2.2.1 REDES ESCALERA

Las redes escalera permiten reducir el rango de

valores de las resistencias. En la siguiente figura

se muestra un ejemplo, aunque este tipo de

circuitos ya que en la actualidad estn superados

por las redes R-2R.

2 CONVERSIN DIGITAL ANALGICA

(D/A)

2.1 INTRODUCCIN

Partimos de una seal digital D = dndn-1... d1 en

paralelo que responde a la codificacin binaria

natural y una referencia Xref (podra ser una tensin

o una corriente) y pretendemos obtener una seal

analgica x que vare de a saltos iguales a Xref /2n

entre 0 y (2n 1) Xref /2n = Xref (1 2-n), como se

muestra en la figura.

Figura11. Convertidor D/A. Redes Escalera.

2.2.2 MTODO DE LA RED ESCALERA R-2R

Dado un conversor D/A con salida en corriente,

como la red R-2R, cuya topologa final se

complementa con un conversor de I a V

implementado con un amplificador operacional, se

puede obtener una que responda al cdigo binario

desplazado (binary offset) agregando una rama

que aporte una corriente adicional como se indica

en la figura. El resultado es, entonces, bipolar.

Figura12. Convertidor D/A. Mtodo R-2R.

Figura13. Convertidor D/A. Exactitud.

2.2.3 CONVERSOR MULTIPLICATIVO

Los conversores integrados en los cuales Vref no

es fija sino que puede imponerse externamente se

denominan conversores multiplicativos.

2.3

ESPECIFICACIONES

CONVERSORES D/A

DE

2.3.3 ERROR DE ESCALA

Es el error que se obtiene a fondo de escala con

respecto al valor ideal. Se debe en general a

errores de ganancia, en la referencia o en la red

resistiva. Se expresa tambin en LSB a fondo de

escala. El error de escala ideal es 0 LSB.

LOS

Para una aplicacin efectiva de los conversores

digital-analgicos es preciso conocer y saber

interpretar las especificaciones de los mismos, ya

que ponen de manifiesto las limitaciones as como

las verdaderas prestaciones, que en muchos

casos difieren considerablemente de la idealidad.

A continuacin presentamos una descripcin de

las especificaciones ms importantes.

2.3.1 RESOLUCIN

Es la cantidad de bits o dgitos binarios que acepta

en su entrada. Tambin puede expresarse como el

porcentaje del valor nominal mximo (fondo de

escala). Ejemplo: un conversor de 10 bits tambin

puede tener su resolucin expresada como 1/210

0,0976 %. Observar que la resolucin por s sola

no indica nada respecto a la precisin del

conversor.

Figura14. Convertidor D/A. Error de Escala.

2.3.4 ERROR DE OFFSET

Es el valor de salida obtenido cuando la entrada es

nula. Se mide en porcentaje del mximo nominal o

en LSB. El valor ideal es 0 LSB.

2.3.5 NO LINEALIDAD

Indica la mxima separacin de la lnea recta que

resulta luego de eliminar los errores de escala y de

offset. El valor ideal es 0 LSB.

2.3.2 EXACTITUD

Es la mxima desviacin respecto a la lnea recta

que une el mnimo y el mximo valor ideales. Se

expresa en LSB (least significant bit), lo cual

significa que se usa el salto mnimo nominal como

unidad. Otra forma de expresarlo es en porcentaje

del valor mximo nominal. La exactitud ideal es 0

LSB. Es necesario tener en cuenta que esta

especificacin incluye todos los errores posibles

del conversor

2.3.6 NO LINEALIDAD DIFERENCIAL

Es la mxima diferencia entre un salto a la salida

debido a un cambio de 1 LSB y el salto ideal. Se

expresa como porcentaje del mximo nominal o en

LSB. El valor ideal es 0 LSB.

2.3.7 MONOTONA

Es la cualidad de generar valores analgicos

crecientes ante cdigos digitales de entrada

crecientes. A veces se especifica como aquella

resolucin en bits para la cual se puede garantizar

5

la monotona. Por ejemplo, un conversor podra

tener una resolucin de 8 bits pero una monotona

de 7 bits, en caso de que algunos saltos de 1 LSB

produzcan inversiones, pero que ningn salto del

segundo bit menos significativo produzca tales

inversiones. Idealmente, la monotona debe ser

igual a la resolucin. Lamonotona est

relacionada con la no linealidad. Una no linealidad

mayor de 0,5 LSB podra provocar una prdida

del carcter montono de la respuesta,

especialmente cuando en un cdigo el error es por

exceso y en el que le sigue es por defecto. Esta

situacin puede darse en el salto que se produce

en el punto medio de la escala (01...1 a 10...0).

que todas las llaves conducen (es decir que se

encienda la que corresponda al MSB antes de

apagarse las restantes), o viceversa. El resultado

es un pico de corriente corto (de uno u otro signo)

pero de gran amplitud. Este pico podra atenuarse

debido al slew-rate del amplificador de salida.

2.3.11 DERIVAS CON LA TEMPERATURA

Cada uno de los parmetros anteriores es

susceptible de cambiar con la temperatura, por

ejemplo el error de no linealidad o de fondo de

escala (error de escala). Se especifica en % del

fondo de escala nominal por C (% FS / C).

2.3.8 TIEMPO DE ESTABLECIMIENTO

Es el mximo tiempo transcurrido luego de un

cambio de cdigo de entrada arbitrario para

alcanzar el valor analgico correspondiente con un

error de a lo sumo 0,5 LSB. El tiempo de

establecimiento de un conversor D/A tiene dos

componentes: una debida al comportamiento

dinmico lineal y otra debido al slew-rate del

amplificador operacional (fenmeno no lineal). La

primera se debe a las capacidades parsitas en

paralelo con las llaves analgicas, que hacen que

la conmutacin entre un cdigo de entrada y otro

no sea instantnea. Sus caractersticas son

similares a las de cualquier transitorio, con una

aproximacin exponencial al valor final. La

componente debida al slew-rate del amplificador

se caracteriza por un crecimiento lineal con

pendiente fija, por lo cual cuanto mayor sea la

amplitud del salto (por ejemplo un cambio en la

entrada de 00...0 a 11...1) mayor ser el tiempo de

crecimiento. En general predomina el efecto del

slew-rate, salvo que se usen amplificadores de

muy alta velocidad.

2.3.12 DERIVA POR ENVEJECIMIENTO

El envejecimiento tambin altera los valores

especificados. Una de los ms importantes es la

deriva del error de escala debido al envejecimiento

de la Vref.

3. CONVERTIDOR ADC0808

El convertidor ADC0808 es un componente para la

adquisicin de datos, este circuito CMOS tiene un

convertidor analgico-digital de 8 bits, un

multiplexor de 8 canales y una lgica de control

que lo hace compatible con todos los

microprocesadores. Para la conversin utiliza el

mtodo de aproximaciones sucesivas. Este

dispositivo ofrece gran velocidad, gran exactitud,

mnima dependencia a la temperatura, excelente

repetitibilidad y un consumo mnimo de energa,

por lo tanto lo hace un dispositivo ideal en

aplicaciones de control y de automotores.

4

DESCRIPCIN

TCNICA

CONVERTIDOR ADC0808

2.3.9 SLEW-RATE

Mxima pendiente de la salida ante una

conmutacin del cdigo de entrada. Su efecto es

ms notorio en las transiciones grandes (o a fondo

de escala). En general, se debe no a la red R-2R

sino al amplificador que convierte corriente en

tensin.

DEL

A continuacin, daremos una descripcin sinttica

de un convertidor A/D presentado por varios

fabricantes; En nuestro caso tomaremos el chip de

Nacional Semiconductor, el cual presenta algunas

de estas caractersticas:

Tecnologa de fabricacin CMOS.

Conversor del tipo de aproximaciones

sucesivas.

Alimentacin nica normal Vcc = +5 Volt (mx.

6,5 V).

Bajo consumo (15 mW).

Tiempo de conversin tpico 100 s.

Salidas triestado memorizadas, compatible con

TTL.

2.3.10 SOBREPICO Y GLITCH

El sobrepico es el resultado de una respuesta

subamortiguada en el amplificador. El glitch es un

efecto similar a lo que en lgica se denomina

aleatorio, que consiste en que las llaves no

conmutan instantneamente ni simult- neamente.

As, en un DAC de 8 bits, al pasar del cdigo 127

al 128 en la entrada, podra haber un momento en

Multiplexor analgico de 8 canales de entrada.

Adaptacin a microprocesadores.

Resolucin 8 bits.

Errores de linealidad y desajuste total < 1/2

LSB (digito menos significativo).

El capacitor es una compensacin que permite

mejorar el tiempo de establecimiento. La

resistencia de realimentacin est integrada para

reducir las derivas trmicas.

Amplificador con ganancia controlada: Si el

conversor es de tipo multiplicativo puede utilizarse

la entrada de Vref como una entrada de seal, y

entonces la ganancia ser proporcional al dato

digital de entrada al conversor.

Este convertidor A/D, que es presentado en varios

encapsulados de CI monoltico, utiliza la tcnica de

conversin

de

aproximaciones

sucesivas

produciendo cdigos o palabras binarias de 8 bit

equivalentes a la magnitud de la entrada

analgica.

7. REFERENCIAS

5.

APLICACIONES

CONVERTIDORES A/D

DE

LOS

[1] Conversor ADC0808. [Seriada en lnea]. Disponible en:

http://www.forosdeelectronica.com/f23/funciona-adc080820781/. Consultado el 15 de junio del 2013.

[2] Convertidores A/D y D/A. [Seriada en lnea]. Disponible en

http://www.fceia.unr.edu.ar/enica3/da-ad.pdf. Consultado el

16 de junio del 2013.

[3] Tipos de convertidores A/D. [Seriada en lnea]. Disponible

en:

http://www.dte.us.es/ing_inf/ins_elec/temario/Tema%208.%

20Convertidores%20A-D.pdf. Consultado el 15 de junio del

2013.

[4] Aplicaciones de los convertidores. [Seriada en lnea].

Disponible en: http://www.fceia.unr.edu.ar/enica3/da-ad.pdf.

Consultado el 16 de junio del 2013.

Voltmetro Digital: Los voltmetros digitales

convierten los voltajes analgicos a su

representacin en cdigo BCD (decimal codificado

en binario), el cual se decodifica y se presenta la

informacin

a

travs

de

visualizadores,

normalmente de 7 segmentos.

Red de resistencias ponderadas: Es la

estructura ms simple que se puede dar. Como se

aprecia fcilmente se trata de un sumador con un

interruptor analgico en cada entrada de suma que

permite aadirla o no. Dependiendo de que el valor

de VREF sea positivo o negativo, obtendremos a

la salida una tensin - +. Cada bit del dato digital

actuar sobre un interruptor del circuito.

Generacin de seales: en esta aplicacin se

trata de obtener una seal de salida que siga un

patrn determinado. En cada posicin de la ROM

est guardado de forma digital un "pedazo" de la

seal de forma que con el contador se va a cada

una de las posiciones de la memoria que son

lanzados al D/A de forma secuencial generndose

la seal. Esta puede ser de cualquier tipo (seno,

de voz, etc). En el caso de la generacin de seal

de voz se le llama sintetizador de voz programada.

Tarjetas grficas de los ordenadores y como

elemento de control en aplicaciones de tipo

industrial, para elementos de control continuo.

6.

APLICACIONES

CONVERTIDORES D/A

DE

LOS

Potencimetro digital: Un conversor D/A

multiplicativo puede utilizarse como potencimetro

digital, el cual puede ser controlado desde un

microprocesador.

Вам также может понравиться

- Cad CdaДокумент14 страницCad CdaJesus Shop Hollister AbercrombieОценок пока нет

- Trabajo de La Unidad Iii - Chavezmissael - Itc - TVДокумент5 страницTrabajo de La Unidad Iii - Chavezmissael - Itc - TVNaydelin Marcelina Chavez EspinozaОценок пока нет

- Practica1.1 Alejandro Torres Torres PDSДокумент10 страницPractica1.1 Alejandro Torres Torres PDSAlejandro TorresОценок пока нет

- Lectura # 18A - Convertidor AD ResumenДокумент5 страницLectura # 18A - Convertidor AD ResumenErwin Guillermo Valdizón WinterОценок пока нет

- Convertidor Analogico Digital R2RДокумент7 страницConvertidor Analogico Digital R2RSergio Limck Plnckk100% (1)

- Labo Tele2 - FINALДокумент14 страницLabo Tele2 - FINALMauro G. Tarazona LévanoОценок пока нет

- Convertidores Analógico DigitalДокумент8 страницConvertidores Analógico DigitalEmmanuel Santiago HernandezОценок пока нет

- Circuito Analogico DigitalДокумент11 страницCircuito Analogico Digitalerik0688Оценок пока нет

- Convertidor DAДокумент34 страницыConvertidor DAEric Dueñas TrujilloОценок пока нет

- DAC ADC Comentarios 19 PDFДокумент5 страницDAC ADC Comentarios 19 PDFDaniJaime 17Оценок пока нет

- Convertidores Ad y DaДокумент18 страницConvertidores Ad y DaMaria MarquinaОценок пока нет

- CCS - 11 - Conversion A - DДокумент15 страницCCS - 11 - Conversion A - DHussein SaddamОценок пока нет

- Convertidores Analogicos Digitales y Digitales AnalogicosДокумент7 страницConvertidores Analogicos Digitales y Digitales AnalogicosCristian ChimboОценок пока нет

- 2.marco Teorico 2.0Документ15 страниц2.marco Teorico 2.0Jamil Carasas TerronesОценок пока нет

- Conversores AD DA y Sensor de HumedadДокумент31 страницаConversores AD DA y Sensor de HumedadJorgeKuschel0% (2)

- Conversor ADДокумент8 страницConversor ADJessy KathОценок пока нет

- Tarea 1 Arreglo R-2rДокумент7 страницTarea 1 Arreglo R-2rAndrés RNОценок пока нет

- INFORME FINAL Nº4 - Sistemas DigitalesДокумент21 страницаINFORME FINAL Nº4 - Sistemas DigitalesMARIO ALBERTO CCOYORI MENDOZAОценок пока нет

- Tipos de ADC PDFДокумент6 страницTipos de ADC PDFLinda CastilloОценок пока нет

- Trabajo de Investigación 3 ELA2Документ7 страницTrabajo de Investigación 3 ELA2Juan David Rodriguez BeltranОценок пока нет

- Conversión AnalógicaДокумент13 страницConversión AnalógicaMiguel Andres CastilloОценок пока нет

- Convertidor Analogico DigitalДокумент6 страницConvertidor Analogico DigitalCiberx angel “Ciberxangel”Оценок пока нет

- ADC Doble RampaДокумент5 страницADC Doble Rampagagafefawefaef100% (1)

- ConvertidoresДокумент13 страницConvertidoresGabriela Ortiz CuetoОценок пока нет

- Conversores AD DAДокумент6 страницConversores AD DAManuel HerreraОценок пока нет

- Telecomunicaciones 2Документ5 страницTelecomunicaciones 2David DraОценок пока нет

- Convertidor Convertidor Analógico Digital y Converidor de Digital A AnalogoДокумент11 страницConvertidor Convertidor Analógico Digital y Converidor de Digital A AnalogoSandra Milena Nuñez CuadrosОценок пока нет

- LABORATORIO ConversoresДокумент4 страницыLABORATORIO ConversoresAriel CadenaОценок пока нет

- Conversion de SeñalesДокумент6 страницConversion de SeñalesAlexander Velez0% (1)

- Laboratorio Tele2Документ5 страницLaboratorio Tele2Wilbert Amanca CordovaОценок пока нет

- Principios Electricos - Investigación Unidad 3Документ15 страницPrincipios Electricos - Investigación Unidad 3Adair NavarroОценок пока нет

- 34 Cad DacДокумент7 страниц34 Cad DacgerhonimОценок пока нет

- Convertidor Analogico DigitalДокумент5 страницConvertidor Analogico DigitalcarlosОценок пока нет

- Conversores A/DДокумент33 страницыConversores A/DMauricio Menay SuárezОценок пока нет

- Ad 03Документ7 страницAd 03Dany MárquezОценок пока нет

- Convertidores DAC y CAD PDFДокумент7 страницConvertidores DAC y CAD PDFskyworld99Оценок пока нет

- Investigacion DijitalesДокумент8 страницInvestigacion DijitalesGomez MarquezОценок пока нет

- Convertidores A/DДокумент8 страницConvertidores A/DFabianBañoОценок пока нет

- Informe DACДокумент9 страницInforme DACHenry PabonОценок пока нет

- Convertidoes Dac y AdcДокумент13 страницConvertidoes Dac y AdcAlejandro Garcilazo100% (1)

- 4.-Problemas Resueltos Sobre Ad y Da - SeminarioДокумент10 страниц4.-Problemas Resueltos Sobre Ad y Da - SeminarioCesar Mario Paredes MezaОценок пока нет

- Cap. 27Документ8 страницCap. 27Programa ClipОценок пока нет

- Actividad 4.1Документ6 страницActividad 4.1Dimas Ramirez PortasОценок пока нет

- PLC Tratamiento Señales AnalogasДокумент12 страницPLC Tratamiento Señales AnalogasJohan Andres Rodriguez CortesОценок пока нет

- Convertidores Adc y DacДокумент10 страницConvertidores Adc y Dacanju139221Оценок пока нет

- Conversores AD DAДокумент79 страницConversores AD DAalexh24Оценок пока нет

- Trabajo de Convertidores 1Документ17 страницTrabajo de Convertidores 1Andy Moncada MenaОценок пока нет

- Cuestionario 1 PDFДокумент16 страницCuestionario 1 PDFmarco leeОценок пока нет

- ML313 Unidad 9 Medidores DigitalesДокумент10 страницML313 Unidad 9 Medidores DigitalesErick Molina AlcarrazОценок пока нет

- ADCДокумент15 страницADCDiana Catalina JaimesОценок пока нет

- DAC y ADCДокумент22 страницыDAC y ADCfrankys200Оценок пока нет

- Conversor de Señal Digital A AnalógicaДокумент4 страницыConversor de Señal Digital A AnalógicaElliott GarciaОценок пока нет

- Armónicas en Sistemas Eléctricos IndustrialesОт EverandArmónicas en Sistemas Eléctricos IndustrialesРейтинг: 4.5 из 5 звезд4.5/5 (12)

- Corrección gamma: Mejora de la claridad visual en la visión por computadora: la técnica de corrección gammaОт EverandCorrección gamma: Mejora de la claridad visual en la visión por computadora: la técnica de corrección gammaОценок пока нет

- Prácticas de redes de datos e industrialesОт EverandPrácticas de redes de datos e industrialesРейтинг: 4 из 5 звезд4/5 (5)

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiОт EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiРейтинг: 5 из 5 звезд5/5 (1)

- Formato Pruebas FibraДокумент2 страницыFormato Pruebas FibraLJKarenОценок пока нет

- 200 Mandalas Orientacionandujar Listos para ImprimirДокумент200 страниц200 Mandalas Orientacionandujar Listos para ImprimirPsicYadiraMendizabal100% (4)

- Caso Psicosis PuerperalДокумент5 страницCaso Psicosis PuerperalLJKarenОценок пока нет

- EEAG - Escala DSM IV PDFДокумент7 страницEEAG - Escala DSM IV PDFcristhianibo777Оценок пока нет

- Explicación Acometidas EléctricasДокумент7 страницExplicación Acometidas EléctricasLJKarenОценок пока нет

- DocДокумент12 страницDocLJKarenОценок пока нет

- Formato Pruebas FibraДокумент1 страницаFormato Pruebas FibraLJKarenОценок пока нет

- Escala Depresión PostpartoДокумент2 страницыEscala Depresión PostpartoOliver AdipОценок пока нет

- HOJA de AUTORREGISTRO para La Reestructuracion CognitivaДокумент1 страницаHOJA de AUTORREGISTRO para La Reestructuracion CognitivaLJKaren81% (16)

- Modelo Prueba 1Документ5 страницModelo Prueba 1LJKarenОценок пока нет

- Funciones de La Familia DisfuncionalДокумент1 страницаFunciones de La Familia DisfuncionalLJKarenОценок пока нет

- Ejemplos de AutorregistrosДокумент3 страницыEjemplos de AutorregistrosLJKarenОценок пока нет

- Psicodinámia FamiliarДокумент1 страницаPsicodinámia FamiliarLJKarenОценок пока нет

- 6th Central Pay Commission Salary CalculatorДокумент15 страниц6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Seña y Sist (Paper Fourier)Документ7 страницSeña y Sist (Paper Fourier)LJKarenОценок пока нет

- Ejercicios 6.6Документ1 страницаEjercicios 6.6LJKarenОценок пока нет

- 16PFДокумент34 страницы16PFJose Jorge FontalvoОценок пока нет

- Cuest Sociales Actualizado JoseДокумент20 страницCuest Sociales Actualizado JoseLJKarenОценок пока нет

- Encuesta de Opinión y Escalas de ActitudДокумент2 страницыEncuesta de Opinión y Escalas de ActitudLJKarenОценок пока нет

- TablaДокумент9 страницTablaLJKarenОценок пока нет

- Deb.1 Consulta EntropíaДокумент1 страницаDeb.1 Consulta EntropíaLJKarenОценок пока нет

- Pens Amien ToДокумент2 страницыPens Amien ToLJKarenОценок пока нет

- Deber Transf de FourierДокумент2 страницыDeber Transf de FourierLJKarenОценок пока нет

- Evolución y ConductaДокумент2 страницыEvolución y ConductaLJKaren100% (1)

- Ficha de Observacion TSДокумент2 страницыFicha de Observacion TSLJKarenОценок пока нет

- Cuadro Sinóptico PsicologiaДокумент1 страницаCuadro Sinóptico PsicologiaLJKarenОценок пока нет

- Ficha SDДокумент1 страницаFicha SDLJKarenОценок пока нет

- BiografiasДокумент105 страницBiografiasLJKarenОценок пока нет

- Ficha de Observacion TSДокумент2 страницыFicha de Observacion TSLJKarenОценок пока нет

- PreguntasДокумент1 страницаPreguntasLJKarenОценок пока нет

- Exportacion de ServiciosДокумент74 страницыExportacion de ServiciosJesús Terry TerryОценок пока нет

- Iconos de AutoCAD y Sus FuncionesДокумент5 страницIconos de AutoCAD y Sus FuncionesJAVIERОценок пока нет

- ArgosДокумент45 страницArgosAsociación Española de AcuaristasОценок пока нет

- Rojas Bermudo, Candida SoniaДокумент15 страницRojas Bermudo, Candida SoniaEnrique Rojas BermudoОценок пока нет

- El Origen de La Cultura Africano-Americana PDFДокумент149 страницEl Origen de La Cultura Africano-Americana PDFtomasfeza5210100% (1)

- 1 PBДокумент9 страниц1 PBJorge Rodriguez MОценок пока нет

- Perfil Auxiliar de SoporteДокумент4 страницыPerfil Auxiliar de SoporteKokito GoОценок пока нет

- Formato InduccionДокумент24 страницыFormato InduccionHECTOR100% (1)

- Factores de Reducción y JustificaciónДокумент4 страницыFactores de Reducción y JustificaciónAlan Recalde100% (2)

- 04 1372062jiioozvywsДокумент36 страниц04 1372062jiioozvywsWILBERT ANTONY ROCHA VERAОценок пока нет

- Universidad Continental Escuela Académico Profesional de Ingeniería CivilДокумент10 страницUniversidad Continental Escuela Académico Profesional de Ingeniería CivilJAIME ADAN QUISPE CCALLISAYAОценок пока нет

- Ley 1381 2010 Protección de Lenguas NativasДокумент9 страницLey 1381 2010 Protección de Lenguas NativasNeila DiazОценок пока нет

- Normas IeeeДокумент2 страницыNormas IeeeJohanna GalanОценок пока нет

- Dispositivos de InformaciónДокумент2 страницыDispositivos de InformaciónBeltramo LucianoОценок пока нет

- Una Propuesta para El Formato de La Historia Clinica Homeopatica Ximena Rey 1 PDFДокумент80 страницUna Propuesta para El Formato de La Historia Clinica Homeopatica Ximena Rey 1 PDFFelimer Guarniz0% (1)

- Machote Dictamen Criminalistica DefinitivoДокумент3 страницыMachote Dictamen Criminalistica DefinitivoJuan M. Romero100% (1)

- GUIA2MATE4Документ167 страницGUIA2MATE4Angel BGОценок пока нет

- Informe de Laboratorio Numero 1Документ9 страницInforme de Laboratorio Numero 1Edwin Edu CutireОценок пока нет

- Cuaderno de Trabajo V InformaticaДокумент69 страницCuaderno de Trabajo V InformaticaLuis Enrique Escalante Montejo100% (1)

- Tesis PDFДокумент154 страницыTesis PDFIdlsndoОценок пока нет

- Secuencia de GeometrìaДокумент8 страницSecuencia de GeometrìaNOELIA100% (1)

- Línea de Tempo Del Orígenes y Evolución de La Teoría General de SistemasДокумент7 страницLínea de Tempo Del Orígenes y Evolución de La Teoría General de Sistemasnaivi sanchezОценок пока нет

- Ensayo - Masculinidad, Razas, Roles Sexuales Luis GarciaДокумент1 страницаEnsayo - Masculinidad, Razas, Roles Sexuales Luis GarciaMaricusaОценок пока нет

- PRACTICA 8 Destilacion Por Arrastre de Vapor-1Документ9 страницPRACTICA 8 Destilacion Por Arrastre de Vapor-1Dyann Sotéz Gómez100% (1)

- Nirvana - Nevermind (Guitar Songbook)Документ3 страницыNirvana - Nevermind (Guitar Songbook)Stone age0% (2)

- Serie S de TiempoДокумент12 страницSerie S de TiempoPerales Rios JosueОценок пока нет

- Fisica 1bgu 3bloqueДокумент17 страницFisica 1bgu 3bloqueJavier MartínezОценок пока нет

- Fichas de Razonamiento Verbal COM-3S-2016Документ57 страницFichas de Razonamiento Verbal COM-3S-2016Marco Montalban Sayago100% (3)

- 16-22 El Imperialismo Europeo Del Siglo XIX XXДокумент12 страниц16-22 El Imperialismo Europeo Del Siglo XIX XXPaulina Constanza Aravena Cortés100% (1)

- Bonitos Mandalas para NiñosДокумент5 страницBonitos Mandalas para Niñosvale paezОценок пока нет