Академический Документы

Профессиональный Документы

Культура Документы

Vlsi Abstract

Загружено:

ALEX SAGARАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Vlsi Abstract

Загружено:

ALEX SAGARАвторское право:

Доступные форматы

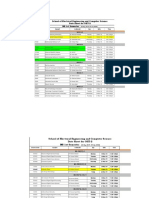

Hades InfoTech Pvt.

Ltd

IEEE VLSI ABSTRACT 2013-14

HARDWARE IMPLEMENTATION

HVL01

A Current Consumption Measurement Approach for FPGA-Based

Embedded Systems

Abstract:

An approach for field programmable gate array (FPGA) based embedded system

dynamic current consumption measurement is presented in the paper. The measurement

method is based on current conversion to time interval. The time interval is then

measured using timer implemented in FPGA. Measurement uncertainty budget analysis is

performed. It reveals key components and their parameters mostly affecting current

measurement uncertainty. System architecture for incorporating measurement setup to the

standard FPGA development flow is suggested.

HVL02

Design of a Real-Time FPGA-Based Data Acquisition Architecture for

the LabPET

Abstract:

The LabPET II detector block was designed to achieve submillimeter spatial

resolution in small animal PET imaging. Each detection block consists of two arrays of

4$, times,$ 8 avalanche photodiodes (APD) individually coupled to an 8$, times,$8

scintillator array, to form 64 independent detectors with parallel readout channels. This

new detection block entails an eightfold increase in pixel density compared to the

LabPET I. A 64-channel mixed-signal application-specific integrated circuit (ASIC) was

designed to extract relevant PET data in real time from the LabPET II detection blocks.

In order to interface the ASICs forming the PET camera with the storage units, a realtime FPGA-based digital data acquisition (DAQ) system was designed. The DAQ system

allows event harvesting, processing and transmission to a host computer for data storage

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

Page |1

Hades InfoTech Pvt. Ltd

as well as system programming and calibration. Real-time event processing embedded in

the DAQ includes time trigger, energy computation using a time-over-threshold (TOT)

conversion scheme, timing corrections, and event sorting trees. In the standard DAQ

mode, a real-time coincidence engine analyzes events and only keeps relevant

information to minimize data throughput and post-acquisition data processing. The

architecture consists of three FPGA-based electronic layers wired through gigabit links: a

Front-End layer extracts time and energy along with the pixel address, a custom Hub

layer chronologically sorts incoming events, and a Coincidence engine matches

coincident events and computes an estimate of the random events rate. Every FPGA in

the different layers is accessible through an Ethernet link. The real-time digital

architecture sustains the required throughput of $sim $111 million events/s for a $sim

{hbox{37thinspace000}}$-channel scanner configuration.

HVL03

Project-Based Learning in Embedded Systems Education Using an

FPGA Platform

Abstract:

With embedded systems becoming ubiquitous, there is a growing need to teach

and train engineers to be well-versed in their design and development. The

multidisciplinary nature of such systems makes it challenging to give students exposure

to and experience in all their facets. This paper proposes a generic architecture,

containing multiple processors, that allows easy integration of custom and/or predefined

peripherals. The architecture allows students to explore both the hardware and software

issues associated with real-time and embedded systems. Furthermore, the architecture can

be extended to train students in advanced concepts in embedded multiprocessor systems.

This generic architecture has been used for two courses at the National University of

Singaporeone on real-time embedded systems and the other emphasizing the hardware

aspects of embedded systems. The project in the real-time embedded systems course has

students develop a five-a-side soccer system on multiple field-programmable gate array

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

Page |2

Hades InfoTech Pvt. Ltd

(FPGA) boards using embedded processors. In the embedded hardware design course

project, students use an embedded processor-based system to perform decryption of a

block encrypted image, accelerated through a custom co-processor. The use of displays

gives students a visual/interactive experience and a sense of accomplishment, while

reinforcing the theoretical concepts. Both qualitative and quantitative assessment results

are presented, showing how students perceived these projects and met the learning

objectives.

HVL04

A Reliable and Cost-Effective Sand Monitoring System on the Field

Programmable Gate Array

Abstract:

Sand monitoring gives the benefits of avoiding equipment erosion and production

failure in the oil industry. This paper presents the design and implementation of a reliable

and cost-effective sand monitoring system for measuring sand production in gas and oil

flows in real time. The designed monitoring system involves two acoustic emission (AE)

sensors and one Doppler sensor for gauging the sand impaction and the velocity of sand

particles in a nonintrusive manner, respectively. It is implemented on a field

programmable gate array (FPGA) as a prototype for real-time data acquisition and

processing, and evaluated using a testbed pump skid available in our laboratory. Relying

on a low-cost FPGA board to integrate all acquisition and processing functionality, our

monitoring system can measure the sand production amount on-the-fly reliably with high

accuracy, according to our experimental evaluation. It is likely to achieve better accuracy

than one without the Doppler sensor. The proposed monitoring system is affordable for

wide deployment, given its high accuracy, good resilience to surrounding noise, and low

cost (when compared with commercially available systems whose price tags can be some

tenfold higher).

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

Page |3

Hades InfoTech Pvt. Ltd

HVL05

Simple Closed Loop DC Speed Control System On FPGA Platform for

VHDL Beginner

Abstract:

Students develop interest to understand the theory around a project that fascinates

them. The motivation of this paper has been to devise a model for teaching VHDL

language to embedded students. The teaching model is based on a practical example of a

simple DC Motor control application conducted in the lab session. A series of Lab

modules from basic digital logics leading gradually to a closed loop DC motor speed

control is presented as lab experiments to maintain the interest of first time learner of

VHDL language. The theory of VHDL language construction is covered separately by

way of classroom lectures but in conjunction with the Lab practice sessions.

HVL06

FPGA Based Real Time Systems For Position Tracking

Abstract:

Position tracking systems supported with RISS and gyroscopes are found to be

better solutions in the places where GPS is unemployable or in the places where GPS

cannot work. Generally systems that are based on GPS for position tracking, face a lot of

problems in the areas where line of sight is hard to achieve i.e. GPS denied environment,

like dense terrestrial areas, subways, tunnels and hidden places. This system provides

continuous and highly reliable position tracking by synchronising real time stimulus

obtained from the sensors and the actual GPS values. The core processor of the system is

built on an FPGA which is used in the system kernel. The key factor for using FPGA in

the system is its customisable core and its flexibility to interface with the sensors. The

core employees the Hybrid Kalman filter for estimating the displacement and position. In

this system we integrate the 3D-RISS with GPS to achieve a Reliable and uninterrupted

Position Tracking. In these systems the processor estimates the posit on of the object

based on the four inputs taken from the RISS and the Odometer, they are Velocity,

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

Page |4

Hades InfoTech Pvt. Ltd

acceleration, orientation and position. Here the system integrates the offline Inertial data (

i.e. while the GPS is unavailable) with that of actual GPS data. The system starts to

compute the position and velocity using the initial data provided by the GPS at the instant

it was lost. This kind of position tracking systems used in various kinds of moving

objects like Aircrafts, Guided missiles, Land Rovers, and Marine navigations.

HVL07

FPGA based Real Time 3D-RISS / GPS Integrated System for Position

Tracking

Abstract:

Navigation algorithms integrating measurements from multi-sensor systems

overcome the problems that arise from using GPS navigation systems in standalone

mode. Algorithms which integrate the data from 2D low-cost reduced inertial sensor

system (RISS), consisting of a gyroscope and an odometer or wheel encoders, along with

a GPS receiver via a Kalman filter has proved to be worthy in providing a consistent and

more reliable navigation solution compared to standalone GPS receivers. It has been also

shown to be beneficial, especially in GPS-denied environments such as urban canyons

and tunnels. The main objective of this paper is to narrow the idea-to-implementation gap

that follows the algorithm development by realizing a low-cost real-time embedded

navigation system capable of computing the data-fused positioning solution. The role of

the developed system is to synchronize the measurements from the three sensors, relative

to the pulse per second signal generated from the GPS, after which the navigation

algorithm is applied to the synchronized measurements to compute the navigation

solution in real-time. Employing a customizable soft-core processor on an FPGA in the

kernel of the navigation system, provided the flexibility for communicating with the

various sensors and the computation capability required by the Kalman filter integration

algorithm.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

Page |5

Hades InfoTech Pvt. Ltd

HVL08

FPGA based Braille to text & speech for blind persons

Abstract:

Blind people are an integral part of the society. However, their disabilities have

made them to have less access to computers, the Internet, and high quality educational

software than the people with clear vision. Consequently, they have not been able to

improve on their own knowledge, and have significant influenc e and impact on the

economic, commercial, and educational ventures in the society. One way to narrow this

widening gap and see a reversal of this trend is to develop a system, within their

economic reach, and whi ch will empower them to communicate freely and widely using

the Internet or any other information infrastructure. Over time, the Braille system has

been used by the visually impaired for communication and contact with the outside

world. This paper presents the implementation of Braille to Text/Speech Converter on

FPGA Spartan3 kit. The actual Braille language is converted into English language in

normal domain. The input is given through braille keypad which consists of diff erent

combinations of cells. This input goes to the FPGA Spartan3 Kit. According to the

combinations given, FPGA converts the input into corresponding english text through the

decoding logic in VHDL language. After decoding, the corresponding alphabet is

converted to speech through algorithm. Also it is displayed on the LCD by interfacing the

LCD to the Spartan3 kit.

HVL09

Implementation of FPGA based PID Controller for DC Motor Speed

Control System

Abstract:

In this paper, the implementation of software module using VHDL for Xilinx

FPGA (XC3S400) based PID controller for DC motor speed control system is presented.

The tools used for building and testing the software modules are Xilinx ISE 9.2i and

ModelSim XE III 6.3c. Before verifying the design on FPGA the complete design is

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

Page |6

Hades InfoTech Pvt. Ltd

simulated using Modelsim Simulation tool. A test bench is written where, the set speed

can be changed for the motor. It is observed that the motor speed gradually changes to the

set speed and locks to the set speed.

HVL010

Implementation of Hamming code using VLSI

Abstract:

This paper tries to explain the implementation of hamming code using VLSI. In

the present world the field of communication has got many applications, and in every

field the data is encoded at the transmitter and transferred on a communication channel

and received at the receiver after it is decoded. During the transmission of data it might

get corrupted because of some noise on the channel. So it is necessary for the receiver to

have some function which can detect the error in the received data. Hamming code is one

of such forward error correcting code which has got many applications. In this paper the

algorithm for hamming code is discussed and then implementation of it in verilog is done

to get the results. Hamming code is an improvement over parity check method. Here a

code is implemented in verilog in which 4-bit of information data is transmitted with 3redundancy bits. In order to find the value of these redundancy bits a code is written in

verilog which will be simulated in Xillinx 9.1 software. The r sult of simulation and test

bench waveforms are also shown.

HVL011

FPGA Based Critical Patient Health Monitoring Using Fuzzy Neural

Network

Abstract:

We have designed FPGA based system and trained a fuzzy neural network for

early diagnosis of a patient. The system employs a fuzzy interface cascaded with a feedforward neural network in order to obtain an optimum decision regarding the future

pathology physiological state of a patient,. The neurons that are considered in the

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

Page |7

Hades InfoTech Pvt. Ltd

proposed network are devoid of self-connections instead of commonly used selfconnected neurons. The system has been trained and tested with renal data of patients

taken at 10 days interval of time. Applying the methodology, the chance of forecasting of

critical renal condition of a patient has been predicted accurately, 30 days ahead of

actually attaining the critical condition. The system has also been tested for pathology

physiological state prediction of patients at multiple time steps ahead and the prediction

at the next instant of time stands out to be the most accurate. The fuzzy interface

discussed here performs fuzzification of patient data. The data from the patient such as h

ight or weight data cannot always be trusted as they are subjected to the quality and

accuracy of measuring units and the skill of the technician. Moreover, based on a single

data, it would be highly uncertain to make an accurate decision about the future

physiological state of the patient. So the patient data have been fuzzified with the

objective of transformation of periodic measures into likelihoods that the body mass

index, blood glucose, urea, creatinine, systolic and diastolic blood pressure of the patient

is high, low or moderate.

HVL012

VIDEO acquisition through I2C using VHDL

Abstract:

With I2C implementation of video acquisition system, devices can communicate

with each other very speedily than with any other communication protocol. The main

purpose of this technique is not only to communicate the devices but keep in touch with

every operation which can be performing by with the help of this protocol. I2c just uses

two lines for data communication making it lightweight, economical, and omnipresent.

The design is use in acquisition system to make overall system more efficient and

accurate, with the use of I2C data transmit rate get also increased.OV7620 single-chip

CMOS VGA colour digital camera is used in the design using VHDL and FPGA.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

Page |8

Hades InfoTech Pvt. Ltd

HVL013

FPGA and GSM Implementation of Advanced Home

Security System

Abstract:

Home and industrial security today needs to make use of the latest technological

components. In this paper I going to present the design and implementation of a remote

and sensing, control and home security system based on GSM (Global System for

Mobile) . This system offers a complete, low cost, powerful and user friendly way of 24

hours of real time monitoring and remote control of a home and industrial security. The

system works as a remote sensing for the electrical appliances at home to check whether

it is on or off, at the same time the user can control the electrical appliances at home by

sending SMS ( Short Messaging Service) message to the system, for example turning on t

he AC before returning home. In case of fire/security the chip will receive signals from

the different sensors in the monitoring place and acts according to the received signal by

sending an SMS message to users Mobile Phone, it also works as automatic and

immediate reporting to the user in case of emergency for home security, as ell as

immediate and automatic reporting to the fire brigade and police station according to

activated sensor to decrease the time required for tacking action.The design has been

described using VHDL (VHSIC Hardware Description Language) and implemented in

hardware using FPGA (Field Programmable Gate Array).

HVL014

FPGA Implementation of Picoblaze based Embedded System for

Monitoring Applications

Abstract:

PicoBlaze is an 8-bit soft core microprocessor developed by Xilinx that can be

synthesized in some FPGA families. This paper presents a set of peripherals that have

been developed to interface with PicoBlaze: VGA control, serial communication, PS/2

keyboard port and LCD control. To demonstrate its capabilities, the system has been

implemented in a FPGA board and some typical control and monitoring systems have

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

Page |9

Hades InfoTech Pvt. Ltd

been developed. The design approach of the peripherals and details of the integration of

the systems are explained.

HVL015

Design and Development of FPGA Based Data Acquisition System for

Process Automation

Abstract:

This paper presents a novel approach to the design of data acquisition system for

process applications. The core heart of the proposed system is Field Programmable Gate

Array (FPGA) which is configured and programmed to acquire a maximum of 16 MB

real time data. For the real time validation of the designed system, a process plant with

three parameters i.e. pressure, temperature and level is considered. Real time data from

the process is acquired using suitable temperature, pressure and level sensors. Signal

conditioners are designed for each sensor and are tested in real time. Designed FPGA

based data acquisition system along with corresponding signal conditioners is validated

in real-time by running the process and comparing the same with the corresponding

references. The data acquired in real time compares well with the references.

HVL016

Intelligent Car Parking Management System On FPGA

Abstract:

Car parking has become an immense issue, especially in big cities. There are two

main reasons: Firstly, the growth in population, secondly, the security. Moreover, the car

theft has become an evil art haunting drivers. In this paper, we provide an interface and a

software/ hardware module for Intelligent Car Park Management System (ICPMS). The

ICPMS will provide an extensive management for vehicles including parking facilities

and security. The ICPMS is validated using a test case scenario and extensive

experimentation proves the feasibility of the approach.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 10

Hades InfoTech Pvt. Ltd

HVL017

FPGA Based Implementation of Flat Panel Display Controller with DVI

Interface

Abstract:

Digital displays are a fast-growing market comprising LCD, plasma, and rear

projection television technologies as well as smaller displays for mobile handsets and

automobiles, in addition to many other applications. Digital image processing enhances

the overall viewing aesthetics of the displayed image and can differentiate our product.

This paper deals about the design and development of Flat panel display controller design

using Xilinx Spartan-3AN Development board and intended for display panel

applications to assist in developing products for this market. The display solution FPGA

consists of a DVI Input interface, colour temperature correction, precise gamma

correction, an image dithering engine, and Low- Voltage Differential Signaling (LVDS)

Transmit (TX) output interface.

HVL018

Design Of FPGA Based PWM Solar Power Inverter For Livelihood

Generation In Rural

Abstract:

The paper presents development of a utility interface solar power converter

(Inverter) in Grid / DG power supply for a Solar lighting system used in rural home of

Indian villages. The power supply system comprises of solar (PV) array, PWM converter

incorporating PWM control strategy, energy storage battery devices. The model of the

system has been designed for its operation and a prototype solar power converter. The

system simulation of PWM Pulse generation has been done on a XILINX based FPGA

Spartan 3E board using VHDL code. The test on simulation of PWM generation program

after synthesis and compilation were recorded and verified on a prototype sample.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 11

Hades InfoTech Pvt. Ltd

HVL019

Real Time Design & Implementation of Digital Speedometer On FPGA

Abstract:

In this paper, a Digital Speedometer is designed and implemented using FPGA

(Field Programmable Gate Array). Here, the FPGA used is Smart Fusion FPGA. It is

more flexible in hardware and embedded design where need a true system-on-chip (SoC)

solution FPGA devices are ideal than traditional fixed-function microcontrollers and

without the excessive cost of soft processor cores on traditional FPGAs. At the inception,

the speedometer is designed using Verilog Hardware Description Language. Synthesissoftware algorithmically transforms the Verilog source code into a netlist, a logicallyequivalent description consisting only of elementary logic primitives (AND, OR, NOT,

flip-flops, etc.) that are available in a specific FPGA or VLSI technology. The designed

speedometer gives lots of extra features than existing speedometers. The special addition

of this speedometer is the velocity of the speedometer is accurate not only in normal

times but also at exceedingly small velocities.

HVL020

Design of Control Module for Serial DAC Based on FPGA

Abstract:

In order to increase the flexibility of control for serial DAC, a new control method

for DAC based on FPGA is proposed in this paper. A state transition diagram can be

drawn according to the timing diagram of DAC, Which can be realized in FPGA using

Very High-speed Integrated Circuit Hardware Description Language. The simulate

results show that logic in FPGA is consistent with the requirements. The module based

on FPGA can be modified just by modifying software, not the hardware.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 12

Hades InfoTech Pvt. Ltd

HVL021

FPGA-Based Evolvable Hardware Systems

Abstract:

Since 1992, year where Hugo de Garis has published the first paper on Evolvable

Hardware (EHW), a period of intense creativity has followed. It has been actively

researched, developed and applied to various problems. Different approaches have been

proposed that created three main classifications: extrinsic, mixtrinsic and intrinsic EHW.

Each of these solutions has a real interest. Nevertheless, although the extrinsic evolution

generates some excellent results, the intrinsic systems are not so advanced. This paper

suggests 3 possible solutions to implement the run-time configuration intrinsic EHW

system:

FPGA-based

Run-Time

Configuration

system,

JBits-based

Run-Time

Configuration system and Multi-board functional-level Run-Time Configuration system.

The main characteristic of the proposed architectures is that they are implemented on

Field Programmable Gate Array. A comparison of proposed solutions demonstrates that

multi-board functional-level run-time configuration is superior in terms of scalability,

flexi ility and the implementation easiness.

HVL022

Implementation of Maximum Power Point Tracking Using Kalman

Filter for Solar Photovoltaic Array on FPGA

Abstract:

This paper proposes FPGA implementation of a novel approach to track

maximum power point of a solar photovoltaic array. The approach uses Kalman filter

algorithm to track maximum power point. Using this approach tracking becomes much

faster than using the generic Perturb & Observe algorithm in case of sudden weather

changes. In this paper output of the proposed algorithm on FPGA is provided.

Experimentation was performed under optimal conditions as well as under cloudy

conditions i.e. falling irradiance levels. Using the proposed technique the maximum

power point of a solar PV array is tracked with an efficiency of 97.11%. Moreover, the

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 13

Hades InfoTech Pvt. Ltd

maximum power point has been tracked at a much faster rate i.e. 4.5 ms using the

proposed algorithm compared to the existing generic Perturb and Observe approach.

HVL023

An FPGA Based Implementation of a Flexible Digital PID Controller

For a Motion Control System

Abstract:

Implementation of digital controllers in embedded environment suffers from the

inherent problems associated with analog-digital signals interfacing in hard real-time,

therefore, the control algorithms are invariantly subjected to approximations. This paper

presents a novel technique for implementation of an efficient FPGA based digital

Proportional-Integral-Derivative (PID) controller for the motion control of a permanent

magnet DC motor. The implementation technique circumnavigates the problem of

interfacing analog and digital systems in real-time. The controller is used in a speed

control loop. The hardware implementation has been done on a Xilinx Spartan 3 FPGA

chip. A novel technique has been adopted for the generation of the control input as a

PWM signal for controlling the motor driver circuit and decoding the optical encoder

data for using it for the speed feedback in the PID control loop. The VHDL algorithm for

the proposed implementation has also been presented in this paper. A comparison of the

experimental results with the Matlab based simulation shows the effectiveness of the

proposed method.

HVL024

Design of an Oximeter Based on LED-LED Configuration and FPGA

Technology

Abstract:

A fully digital photoplethysmographic (PPG) sensor and actuator has been

developed. The sensing circuit uses one Light Emitting Diode (LED) for emitting light

into human tissue and one LED for detecting the reflectance light from human tissue. A

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 14

Hades InfoTech Pvt. Ltd

Field Programmable Gate Array (FPGA) is used to control the LEDs and determine the

PPG and Blood Oxygen Saturation (SpO2). The configurations with two LEDs and four

LEDs are developed for measuring PPG signal and Blood Oxygen Saturation (SpO2). NLEDs configuration is proposed for multichannel SpO2 measurements. The approach

resulted in better spectral sensitivity, increased and adjustable resolution, reduced noise,

small size, low cost and low power consumption.

HVL025

Smart Camera Based on FPGA Oriented to Embedded Image

Processing

Abstract:

This paper presents an image processing system based on smart camera platform,

whose two principle elements are a Wide-VGA CMOS Sensor and a Field Programmable

Gate Array (FPGA). The latter is used to control the various sensor parameter

configurations and, where desired, to receive and process the images captured by the

CMOS sensor. With the advent of today's highly integrated Field Programmable Gate

Array (FPGA) it is possible to have a software programmable processor and hardware

computing resources on the same chip. Apart from having sufficient logic blocks on

which the hardware is implemented these chips also have an embedded processor with

system software to implement the application software around it. In this paper, the

Spartan-3A DSP based Xilinx VSK platform is used for developing the proposed

extensible hardware-software video streaming and processing modules. In order to

develop the required hardware and software in an integrated fashion, Xilinx Embedded

Development Kit (EDK) design tool has been used. A number of Xilinx provided IPs are

customized to realize the hardware modules in the FPGA fabric. Copyright 2013 Praise

Worthy Prize S.r.l. -All rights reserved.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 15

Hades InfoTech Pvt. Ltd

HVL026

Real Time Vehicular Camera Vision Acquisition System Using FPGA

Abstract:

With the advent of active safety technologies in the automotive industry, a need to

record and replay the actual on-road vehicular scenario has risen, especially in systems

involving camera-based vision. The primary objective of the paper is to propose a design

of a system for real-time video acquisition. Hence, a design for a Camera Hardware

simulator has been proposed in this paper. The system involves a camera that captures

visual information through its image sensor. The system is designed such that it can do

direct display; that is, it can generate vertical and horizontal synchronization signals, as

per the specification of the camera and it can buffer the pixel clock coming from the

camera and send it to another system that uses the video information being received such

as an in-vehicle display to display it. It also includes the ability to record the incoming

data stream in a computer for offline processing. As the aforementioned functionality is

to be achieved for high incoming data rates and also handy interfacing to any recording

device is required, we are using a Universal Serial Bus (USB) 2.0 (high speed). Many

subsystems are to be designed on the same chip, so we propose the use of a Field

Programmable Gate Array (FPGA) based system for fast data processing and

miniaturization of the system. The system under consideration is comprised of a

Complementary Metal-Oxide Semiconductor (CMOS) camera at the input and a highspeed USB interface at the output. The FPGA is programmed as a Video Graphics Array

(VGA) Controller, buffer and a USB Controller. FPGA consumes less power when

compared to any other embedded-based system, making it more usable inside an

automobile. This system can be used for offline video processing and simulation of the

exact on-road scenario in lab for vision based active safety system's testing purpose or for

active safety algorithm improvement to achieve desired results (by tweaking the

algorithm for desired results, based on the observations made from the recorded data

without having the need to go on road again and again).

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 16

Hades InfoTech Pvt. Ltd

HVL027

Constructivist Multi-Access Lab Approach in Teaching FPGA Systems

Design with LabVIEW

Abstract:

Embedded systems play vital role in modern applications [1]. They can be found

in autos, washing machines, electrical appliances and even in toys. FPGAs are the most

recent computing technology that is used in embedded systems. There is an increasing

demand on FPGA based embedded systems, in particular, for applications that require

rapid time responses. Engineering education curricula needs to respond to the increasing

industrial demand of using FPGAs by introducing new syllabus for teaching and learning

this subject. This paper describes the development of new course material for teaching

FPGA-based embedded systems design by using G Programming Language of

LabVIEW. A general overview of FPGA role in engineering education is provided. A

survey of available Hardware Programming Languages for FPGAs is presented. A survey

about LabVIEW utilization in engineering education is investigated; this is followed by a

motivation section of why to use LabVIEW graphical programming in teaching and its

capabilities. Then, a section of choosing a suitable kit for the course is laid down. Later,

constructivist closed-loop model the FPGA course has been proposed in accordance with

[2-4; 80,86,89,92]. The paper is proposing a pedagogical framework for FPGA teaching;

pedagogical evaluation will be conducted in future studies. The complete study has been

done at the Faculty of Electrical and Electronic Engineering, Aleppo University.

HVL028

FPGA-Based Educational Platform for Real-Time Image Processing

Experiments

Abstract:

In this paper, an implementation of an educational platform for real-time linear

and morphological image filtering using a FPGA NexysII, Xilinx, Spartan 3E, is

described. The system is connected to a USB port of a personal computer, which in that

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 17

Hades InfoTech Pvt. Ltd

way form a powerful and low-cost design station for educational purposes. The FPGAbased system is accessed through a MATLAB graphical user interface, which handles the

communication setup and data transfer. The system allows the students to perform

comparisons between results obtained from MATLAB simulations and FPGA-based realtime processing. Concluding remarks derived from course evaluations and lab reports are

presented.

HVL029

Real-time Traffic Sign detection and Recognition on FPGA

Abstract:

This paper presents the implementation of an embedded automotive system that

detects and recognizes traffic signs within a video stream. In addition, it discusses the

recent advances in driver assistance technologies and highlights the safety motivations

for smart in-car embedded systems. An algorithm is presented that processes RGB image

data, extracts relevant pixels, filters the image, labels prospective traffic signs and

evaluates them against template traffic sign images. A reconfigurable hardware system is

described which uses the Virtex-5 Xilinx FPGA and hardware/software co-design tools in

order to create an embedded processor and the necessary hardware IP peripherals. The

implementation is shown to have robust performance results, both in terms of timing and

accuracy.

HVL030

Design and implementation of a secure RFID system on FPGA

Abstract:

Radio Frequency Identification systems have been widely used in many

applications nowadays. Since then, data security has been an important issue in RFID

communication in order to prevent undesired people to decrypt communication data.

Considering the problem, a secure RFID system is designed in this study. An RFID

communication at 868MHz is demonstrated by programming transceiver modules via

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 18

Hades InfoTech Pvt. Ltd

Spartan3E FPGA Kits. To increase communication security between reader and tag, 2stage authentication protocol is preferred. Tiny Encryption Algorith (TEA) module is

used as IP Core in FPGA to provide data encryption and sistem design has been

completed.

STIMULATION ONLY

HVL031

A 2.63 Mbit/s VLSI Implementation of SISO Arithmetic Decoders for

High Performance Joint Source Channel Codes

Abstract:

This paper highlights the implementation challenges faced by the current high

performing error resilient joint source channel coding (JSCC) techniques based on the

concept of soft-input soft-output (SISO) decoding of arithmetic codes (AC). Further, it

proposes several efficient algorithmic and a very large scale integration (VLSI)

architectural techniques to improve the throughput performance of SISO for JSCC. The

VLSI hardware implementation of the proposed algorithm, when implemented on a 90

nm standard cells technology running at 588 MHz, achieves a decoding throughput of up

to 2.63 Mbits/s capable of decoding QCIF format for video conferencing.

HVL032

3-D Mesh-Based Optical Network-on-Chip for Multiprocessor Systemon-Chip

Abstract:

Optical networks-on-chip (ONoCs) are emerging communication architectures

that can potentially offer ultrahigh communication bandwidth and low latency to

multiprocessor systems-on-chip (MPSoCs). In addition to ONoC architectures, 3-D

integrated technologies offer an opportunity to continue performance improvements with

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 19

Hades InfoTech Pvt. Ltd

higher integration densities. In this paper, we present a 3-D mesh-based ONoC for

MPSoCs, and new low-cost nonblocking 4 4, 5 5, 6 6, and 7 7 optical routers for

dimension-order routing in the 3-D mesh-based ONoC. Besides, we propose an

optimized floorplan for the 3-D mesh-based ONoC. The floorplan follows the regular 3D mesh topology but implements all optical routers in a single optical layer. The

floorplan is optimized to minimize the number of extra waveguide crossings caused when

merging the 3-D ONoC to one optical layer. Based on a set of real applications and

uniform traffic pattern, we develop a SystemC-based cycle-accurate NoC simulator and

compare the 3-D mesh-based ONoC with the matched 2-D mesh-based ONoC and 2-D

electronic NoC for performance and energy efficiency. Additionally, we quantitatively

analyze thermal effects on the 3-D 8 8 2 mesh-based ONoC.

HVL033

A Built-In Repair Analyzer With Optimal Repair Rate for WordOriented Memories

Abstract:

This paper presents a built-in self repair analyzer with the optimal repair rate for

memory arrays with redundancy. The proposed method requires only a single test, even

in the worst case. By performing the must-repair analysis on the fly during the test, it

selectively stores fault addresses, and the final analysis to find a solution is performed on

the stored fault addresses. To enumerate all possible solutions, existing techniques use

depth first search using a stack and a finite-state machine. Instead, we propose a new

algorithm and its combinational circuit implementation. Since our formulation for the

circuit allows us to use the parallel prefix algorithm, it can be configured in various ways

to meet area and test time requirements. The total area of our infrastructure is dominated

by the number of content addressable memory entries to store the fault addresses, and it

only grows quadratically with respect to the number of repair elements. The

infrastructure is also extended to support various types of word-oriented memories.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 20

Hades InfoTech Pvt. Ltd

HVL034

A Fast-Locking All-Digital Deskew Buffer With Duty-Cycle Correction

Abstract:

In this paper, a fast-locking all-digital deskew buffer with duty cycle correction is

proposed and implemented. A cyclic time-to-digital converter is introduced to decrease

the locking time in conventional register-controlled delay-locked loop to only two input

clock cycles in coarse tuning. With the aid of the three half delay lines technique, the

mismatch between half delay lines causing the duty cycle distortion can be alleviated by

interpolation. A balanced edge combiner to achieve a precise 50% output clock is also

presented. A test chip is fabricated in 0.18-m technology to demonstrate the feasibility

of the proposed architecture. The circuit can accept the input clock rates from 250 to 625

MHz with the duty cycle variation within 30% and 70% to generate 50% output clocks. It

preserves the capability of closed-loop control with a small area and power consumption.

HVL035

A High-Speed Low-Complexity Modified FFT Processor for High Rate

WPAN Applications

Abstract:

This paper presents a high-speed low-complexity modified radix-25 512-point

fast Fourier transform (FFT) processor using an eight data-path pipelined approach for

high rate wireless personal area network applications. A novel modified radix-25 FFT

algorithm that reduces the hardware complexity is proposed. This method can reduce the

number of complex multiplications and the size of the twiddle factor memory. It also uses

a complex constant multiplier instead of a complex Booth multiplier. The proposed FFT

processor achieves a signal-to-quantization noise ratio of 35 dB at 12 bit internal word

length. The proposed processor has been designed and implemented using 90-nm CMOS

technology with a supply voltage of 1.2 V. The results demonstrate that the total gate

count of the proposed FFT processor is 290 K. Furthermore, the highest throughput rate

is up to 2.5 GS/s at 310 MHz while requiring much less hardware complexity.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 21

Hades InfoTech Pvt. Ltd

HVL036

A Low-Complexity Turbo Decoder Architecture for Energy-Efficient

Wireless Sensor Networks

Abstract:

Turbo codes have recently been considered for energy-constrained wireless

communication applications, since they facilitate a low transmission energy consumption.

However, in order to reduce the overall energy consumption, lookup table-log-BCJR

(LUT-Log-BCJR) architectures having a low processing energy consumption are

required. In this paper, we decompose the LUT-Log-BCJR architecture into its most

fundamental add compare select (ACS) operations and perform them using a novel lowcomplexity ACS unit. We demonstrate that our architecture employs an order of

magnitude fewer gates than the most recent LUT-Log-BCJR architectures, facilitating a

71% energy consumption reduction. Compared to state-of-the-art maximum logarithmic

Bahl-Cocke-Jelinek-Raviv implementations, our approach facilitates a 10% reduction in

the overall energy consumption at ranges above 58 m.

HVL037

A Meet-in-the-Middle Algorithm for Fast Synthesis of Depth-Optimal

Quantum Circuits

Abstract:

We present an algorithm for computing depth-optimal decompositions of logical

operations, leveraging a meet-in-the-middle technique to provide a significant speedup

over simple brute force algorithms. As an illustration of our method, we implemented this

algorithm and found factorizations of commonly used quantum logical operations into

elementary gates in the Clifford+T set. In particular, we report a decomposition of the

Toffoli gate over the set of Clifford and T gates. Our decomposition achieves a total Tdepth of 3, thereby providing a 40% reduction over the previously best known

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 22

Hades InfoTech Pvt. Ltd

decomposition for the Toffoli gate. Due to the size of the search space, the algorithm is

only practical for small parameters, such as the number of qubits, and the number of

gates in an optimal implementation.

HVL038

AC-Plus

Scan

Methodology

for

Small

Delay

Testing

and

Characterization

Abstract:

Small delay defects escaping traditional delay testing could cause a device to

malfunction in the field and thus detecting these defects is often necessary. To address

this issue, we propose three test modes in a new methodology called AC-plus scan, in

which versatile test clocks can be generated on the chip by embedding an all-digital

phase-locked loop (ADPLL) into the circuit under test (CUT). AC-plus scan can be

executed on an in-house wireless test platform called HOY system. The first test mode of

our AC-plus scan provides a more efficient way to measure the longest path delay

associated with each test pattern. Experimental result shows that our method could

greatly reduce the test time by 81.8%. The second test mode is designed for volume

production test. It could effectively detect small delay defects and provide fast

characterization on those defective chips for further processing. This mode could be used

to help predict which chips are more likely to fall victim to operational failure in the

field. The third test mode is to extract the waveform of each flip-flop's output in a real

chip. This is made possible by taking advantage of the almost unlimited test memory our

HOY test platform provides, so that we could easily store a great volume of data and

reconstruct the waveform for post-silicon debugging. We have successfully fabricated a

Viterbi decoder chip with such an AC-plus scan methodology inside to demonstrate its

capability.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 23

Hades InfoTech Pvt. Ltd

HVL039

Addressing Transient and Permanent Faults in NoC With Efficient

Fault-Tolerant Deflection Router

Abstract:

Continuing decrease in the feature size of integrated circuits leads to increases in

susceptibility to transient and permanent faults. This paper proposes a fault-tolerant

solution for a bufferless network-on-chip, including an on-line fault-diagnosis mechanism

to detect both transient and permanent faults, a hybrid automatic repeat request, and

forward error correction link-level error control scheme to handle transient faults and a

reinforcement-learning-based fault-tolerant deflection routing (FTDR) algorithm to

tolerate permanent faults without deadlock and livelock. A hierarchical-routing-tablebased algorithm (FTDR-H) is also presented to reduce the area overhead of the FTDR

router. Synthesized results show that, compared with the FTDR router, the FTDR-H

router can reduce the area by 27% in an 88 network. Simulation results demonstrate that

under synthetic workloads, in the presence of permanent link faults, the throughput of an

8 8 network with FTDR and FTDR-H algorithms are 14% and 23% higher on average

than that with the fault-on-neighbor (FoN) aware deflection routing algorithm and the

cost-based deflection routing algorithm, respectively. Under real application workloads,

the FTDR-H algorithm achieves 20% less hop counts on average than that of the FoN

algorithm. For transient faults, the performance of the FTDR router can achieve graceful

degradation even at a high fault rate. We also implement the fault-tolerant deflection

router which can achieve 400 MHz in TSMC 65-nm technology.

HVL040

All-Digital

Fast-Locking

Pulse

width-Control

Circuit

With

Programmable Duty Cycle

Abstract:

This paper proposes an all-digital fast-locking pulsewidth-control circuit with

programmable duty cycle. In comparison with prior state-of-the-art methods, our use of

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 24

Hades InfoTech Pvt. Ltd

two delay lines and a time-to-digital detector allows the pulsewidth-control circuit to

operate over a wide frequency range with fewer delay cells, while maintaining the same

level of accuracy. This paper presents a new duty-cycle setting circuit that calculates the

desired output duty cycle without the need for a look-up table. The circuit was fabricated

under the two-stage matrix converter 0.18-CMOS process. Results show that the

proposed circuit performs well for an input operating frequency ranging from 200 to 600

MHz, and an input duty cycle ranging from 30% to 70%. It achieves a programmable

output duty cycle ranging from 31.25% to 68.75% in increments of 6.25%.

HVL041

An Analytical Latency Model for Networks-on-Chip

Abstract:

We propose an analytical model based on queueing theory for delay analysis in a

wormhole-switched network-on-chip (NoC). The proposed model takes as input an

application communication graph, a topology graph, a mapping vector, and a routing

matrix, and estimates average packet latency and router blocking time. It works for

arbitrary network topology with deterministic routing under arbitrary traffic patterns.

This model can estimate per-flow average latency accurately and quickly, thus enabling

fast design space exploration of various design parameters in NoC designs. Experimental

results show that the proposed analytical model can predict the average packet latency

more than four orders of magnitude faster than an accurate simulation, while the

computation error is less than 10% in non-saturated networks for different system-onchip platforms.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 25

Hades InfoTech Pvt. Ltd

HVL042

An Energy-Efficient

L2

Cache

Architecture

Using

Way

Tag

Information Under Write-Through Policy

Abstract:

Many high-performance microprocessors employ cache write-through policy for

performance improvement and at the same time achieving good tolerance to soft errors in

on-chip caches. However, write-through policy also incurs large energy overhead due to

the increased accesses to caches at the lower level (e.g., L2 caches) during write

operations. In this paper, we propose a new cache architecture referred to as way-tagged

cache to improve the energy efficiency of write-through caches. By maintaining the way

tags of L2 cache in the L1 cache during read operations, the proposed technique enables

L2 cache to work in an equivalent direct-mapping manner during write hits, which

account for the majority of L2 cache accesses. This leads to significant energy reduction

without performance degradation. Simulation results on the SPEC CPU2000 benchmarks

demonstrate that the proposed technique achieves 65.4% energy savings in L2 caches on

average with only 0.02% area overhead and no performance degradation. Similar results

are also obtained under different L1 and L2 cache configurations. Furthermore, the idea

of way tagging can be applied to existing low-power cache design techniques to further

improve energy efficiency.

HVL043

An On-Chip Network Fabric Supporting Coarse-Grained Processor

Array

Abstract:

Coarse grained arrays (CGAs) with run-time reconfigurability play an important

role in accelerating reconfigurable computing applications. It is challenging to design onchip communication networks (OCNs) for such CGAs with dynamic run-time

reconfigurability whilst satisfying the tight budgets of power and area for an embedded

system. This paper presents a silicon-proven design of a 64-PE circuit-switched OCN

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 26

Hades InfoTech Pvt. Ltd

fabric with a dynamic path-setup scheme capable of supporting an embedded coarsegrained processor array. A proof-of-concept test chip fabricated in a 0.13 m CMOS

process occupies a silicon area of 23 mm2 and consumes a peak power of 200 mW @

128 MHz and 1.2 Vcc, at room temperature. The OCN overhead consumes 9.4% of the

area and 18% of the power of the total chip. Experimental results and analysis show that

the proposed OCN fabric with its dynamic path-setup is suitable for use in an embedded

CGA supporting fast run-time reconfigurability.

HVL044

An

Ultrasynchronization

Checking

Method

With

Trace-Driven

Simulation for Fast and Accurate MPSoC Virtual Platform Simulation

Abstract:

Efficiency and accuracy are two critical concerns in multiprocessor system on

chip (MPSoC) virtual platform simulation. Traditional simulation approaches that

achieve high efficiency usually sacrifice accuracy. On the other hand, the cycle-accurate

simulation algorithms are generally slow in speed. In this paper, we propose an

ultrasynchronization checking method with an efficient trace-driven simulation

mechanism that can not only improve simulation speed, but also maintain simulation

accuracy. We build a SystemC-based MPSoC virtual platform to evaluate the

effectiveness of our approach. The experimental results show that our proposed

simulation scheme can improve simulation speed up to 156× over the traditional

clock-step simulation method. Furthermore, our proposed method can also guarantee the

cycle-accurate simulation result.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 27

Hades InfoTech Pvt. Ltd

HVL045

Application

Space

Exploration

of

Heterogeneous

Run-Time

Configurable Digital Signal Processor

Abstract:

This paper describes the application space exploration of a heterogeneous digital

signal processor with dynamic reconfiguration capabilities. The device is built around

three reconfigurable engines featuring different flavours and computation granularities

that make it suitable for a wide range of signal processing application domains such as

video coding, image processing, telecommunications, and cryptography. Performance of

signal processing applications is evaluated from measurements performed on a CMOS 90

nm prototype. In order to characterize the application space of the processor, performance

is compared with state-of-the-art devices, taking programmability, computational

capabilities, and energy efficiency as the main metrics. The device exploits performance

and energy efficiency significantly more than general purpose processors, while still

maintaining a user-friendly programming approach that mainly relies on softwareoriented languages. The device is able to achieve 1.2 to 15 GOPS with an energy

efficiency from 2 to 50 GOPS/W when running the selected applications

HVL046

Architecture

for

Real-Time

Nonparametric

Probability

Density

Function Estimation

Abstract:

Adaptive systems are increasing in importance across a range of application

domains. They rely on the ability to respond to environmental conditions, and hence realtime monitoring of statistics is a key enabler for such systems. Probability density

function (PDF) estimation has been applied in numerous domains; computational

limitations, however, have meant that proxies are often used. Parametric estimators

attempt to approximate PDFs based on fitting data to an expected underlying distribution,

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 28

Hades InfoTech Pvt. Ltd

but this is not always ideal. The density function can be estimated by rescaling a

histogram of sampled data, but this requires many samples for a smooth curve. Kernelbased density estimation can provide a smoother curve from fewer data samples. We

present a general architecture for nonparametric PDF estimation, using both histogrambased and kernel-based methods, which is designed for integration into streaming

applications on field-programmable gate array (FPGAs). The architecture employs

heterogeneous resources available on modern FPGAs within a highly parallelized and

pipelined design, and is able to perform real-time computation on sampled data at speeds

of over 250 million samples per second, while extracting a variety of statistical

properties.

HVL047

Built-In Generation of Functional Broadside Tests Using a Fixed

Hardware Structure

Abstract:

Functional broadside tests are two-pattern scan-based tests that avoid overtesting

by ensuring that a circuit traverses only reachable states during the functional clock

cycles of a test. In addition, the power dissipation during the fast functional clock cycles

of functional broadside tests does not exceed that possible during functional operation.

On-chip test generation has the added advantage that it reduces test data volume and

facilitates at-speed test application. This paper shows that on-chip generation of

functional broadside tests can be done using a simple and fixed hardware structure, with a

small number of parameters that need to be tailored to a given circuit, and can achieve

high transition fault coverage for testable circuits. With the proposed on-chip test

generation method, the circuit is used for generating reachable states during test

application. This alleviates the need to compute reachable states offline.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 29

Hades InfoTech Pvt. Ltd

HVL048

A Built-In Self-Repair Scheme for 3-D RAMs With Interdie

Redundancy

Abstract:

3-D integration using through silicon via is an emerging technology for integrated

circuit designs. Random access memory (RAM) is one good candidate for the application

of 3-D integration technology. However, yield will be a key challenge for the volume

production of 3-D RAMs. In this paper, we present yield-enhancement techniques for 3D RAMs. An interdie redundancy scheme is proposed to improve the yield of 3-D

RAMs. Three stacking flows with respect to different bonding technologies for 3-D

RAMs with interdie redundancy are proposed as well. Finally, a built-in self-repair

(BISR) scheme is proposed to perform the repair of 3-D RAMs with interdie

redundancies. The BISR circuits in two stacked dies can work together to allocate

interdie redundancies. Simulation results show that the proposed yield-enhancement

techniques can effectively improve the yield of 3-D RAMs.

HVL049

Check pointing for Virtual Platforms and SystemC-TLM

Abstract:

Integrating simulation models created using different simulation systems is a

common problem when constructing virtual platforms. Different companies and different

departments can create models, and virtual platforms for different purposes using

different tools. There are also existing models that need to be integrated into new tools, or

the other way around. The simulators can be quite different in details, even in the case of

transaction-level models. We present work in integrating SystemC transaction-level

models into two typical full-system simulation environments, QEMU and Simics. We

present issues in reconciling the semantics of the different platforms, and our proposed

solutions. In the Simics integration, we additionally enable checkpointing in the models,

based on the Simics checkpoint mechanism.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 30

Hades InfoTech Pvt. Ltd

HVL050

Circuit-Level Timing Error Tolerance forLow-Power DSP Filters and

Transforms

Abstract:

In this paper, we present a novel circuit-level timing error mitigation technique,

which aims to increase energy-efficiency of digital signal processing datapaths without

loss of robustness. Timing errors are detected using razor flip-flops on critical-paths, and

the error-rate feedback is used to control a dynamic voltage scaling control loop. In place

of conventional razor error correction by replay, we propose a new approach to bound the

magnitude of intermittent timing errors at the circuit level. A timing guard-band is

created by shaping the path delay distribution such that the critical paths correspond to a

group of least-significant bit registers. These end-points are ensured to be critical by

modifying the topology of the final stage carry-merge adder, and by using tool-based

device sizing. Hence, timing violations lead to weakly correlated logical errors of small

magnitude in a mean-squared-error sense. We examine this approach in an finite-impulse

response (FIR) filter and a 2-D discrete cosine transform implementation, in 32-nm

CMOS. Power saving compared to a conventional design at iso-frequency is 21%-23% at

the typical corner, while retaining a voltage guard-band to protect against fast transient

changes in switching activity and supply noise. The impact on minimum clock period is

small (16%-20%), as it does not necessitate the use of ripple-carry adders and also

requires only a bare minimum of additional design effort.

HVL051

Combined Architecture/Algorithm Approach to Fast FPGA Routing

Abstract:

We propose a new field-programmable gate array (FPGA) routing approach,

which, when combined with a low-cost architecture change, results in a 40% reduction in

router runtime, at the cost of a 6% area overhead and with no increase in critical path

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 31

Hades InfoTech Pvt. Ltd

delay. Our approach begins with PathFinder-style routing, which we run on a coarsened

representation of the routing architecture. This leads to fast generation of a partial routing

solution where the signals are assigned to groups of wire segments rather than individual

wire segments. A Boolean satisfiability (SAT)-based stage follows, generating a legal

routing solution from the partial solution. We explore approximately 165 000 FPGA

switch block architectures, showing that the choice of the architecture has a significant

impact on the complexity of the SAT formulation, and by extension, on routing runtime.

Our approach points to a new research direction, namely, reducing FPGA computer-aided

design runtime by exploring FPGA architectures and algorithms together.

HVL052

CORDIC Designs for Fixed Angle of Rotation

Abstract:

Rotation of vectors through fixed and known angles has wide applications in

robotics, digital signal processing, graphics, games, and animation. But, we do not find

any optimized coordinate rotation digital computer (CORDIC) design for vector-rotation

through specific angles. Therefore, in this paper, we present optimization schemes and

CORDIC circuits for fixed and known rotations with different levels of accuracy. For

reducing the area- and time-complexities, we have proposed a hardwired pre-shifting

scheme in barrel-shifters of the proposed circuits. Two dedicated CORDIC cells are

proposed for the fixed-angle rotations. In one of those cells, micro-rotations and scaling

are interleaved, and in the other they are implemented in two separate stages. Pipelined

schemes are suggested further for cascading dedicated single-rotation units and birotation CORDIC units for high-throughput and reduced latency implementations. We

have obtained the optimized set of micro-rotations for fixed and known angles. The

optimized scale-factors are also derived and dedicated shift-add circuits are designed to

implement the scaling. The fixed-point mean-squared-error of the proposed CORDIC

circuit is analyzed statistically, and strategies for reducing the error are given. We have

synthesized the proposed CORDIC cells by Synopsys Design Compiler using TSMC 90G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 32

Hades InfoTech Pvt. Ltd

nm library, and shown that the proposed designs offer higher throughput, less latency and

less area-delay product than the reference CORDIC design for fixed and known angles of

rotation. We find similar results of synthesis for different Xilinx field-programmable

gate-array platforms.

HVL053

Design and Implementation of an On-Chip Permutation Network for

Multiprocessor System-On-Chip

Abstract:

This paper presents the silicon-proven design of a novel on-chip network to

support guaranteed traffic permutation in multiprocessor system-on-chip applications.

The proposed network employs a pipelined circuit-switching approach combined with a

dynamic path-setup scheme under a multistage network topology. The dynamic pathsetup scheme enables runtime path arrangement for arbitrary traffic permutations. The

circuit-switching approach offers a guarantee of permuted data and its compact overhead

enables the benefit of stacking multiple networks. A 0.13- m CMOS test-chip validates

the feasibility and efficiency of the proposed design. Experimental results show that the

proposed on-chip network achieves 1.9 to 8.2 reduction of silicon overhead compared

to other design approaches.

HVL054

Design of Digit-Serial FIR Filters: Algorithms,Architectures, and a

CAD Tool

Abstract:

In the last two decades, many efficient algorithms and architectures have been

introduced for the design of low-complexity bit-parallel multiple constant multiplications

(MCM) operation which dominates the complexity of many digital signal processing

systems. On the other hand, little attention has been given to the digit-serial MCM design

that offers alternative low-complexity MCM operations albeit at the cost of an increased

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 33

Hades InfoTech Pvt. Ltd

delay. In this paper, we address the problem of optimizing the gate-level area in digitserial MCM designs and introduce high-level synthesis algorithms, design architectures,

and a computer-aided design tool. Experimental results show the efficiency of the

proposed optimization algorithms and of the digit-serial MCM architectures in the design

of digit-serial MCM operations and finite impulse response filters.

HVL055

Efficient Implementation of Reconfigurable Warped Digital Filters

With Variable Low-Pass, High-Pass,Bandpass, and Bandstop Responses

Abstract:

In this brief, an efficient implementation of reconfigurable warped digital filter

with variable low-pass, high-pass, bandpass, and bandstop responses is presented. The

warped filters, obtained by replacing each unit delay of a digital filter with an all-pass

filter, are widely used for various audio processing applications. However, warped filters

require first-order all-pass transformation to obtain variable low-pass or high-pass

responses, and second-order all-pass transformation to obtain variable bandpass or

bandstop responses. To overcome this drawback, the proposed method combines the

warped filters with the coefficient decimation technique. The proposed architecture

provides variable low-pass or high-pass responses with fine control over cut-off

frequency and variable bandwidth bandpass or bandstop responses at an arbitrary center

frequency without updating the filter coefficients or filter structure. The design example

shows that the proposed variable digital filter is simple to design and offers substantial

savings in gate counts and power consumption over other approaches.

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 34

Hades InfoTech Pvt. Ltd

HVL056

Error Detection in Majority Logic Decoding of Euclidean Geometry

Low Density Parity Check (EG-LDPC) Codes

Abstract:

In a recent paper, a method was proposed to accelerate the majority logic

decoding of difference set low density parity check codes. This is useful as majority logic

decoding can be implemented serially with simple hardware but requires a large decoding

time. For memory applications, this increases the memory access time. The method

detects whether a word has errors in the first iterations of majority logic decoding, and

when there are no errors the decoding ends without completing the rest of the iterations.

Since most words in a memory will be error-free, the average decoding time is greatly

reduced. In this brief, we study the application of a similar technique to a class of

Euclidean geometry low density parity check (EG-LDPC) codes that are one step

majority logic decodable. The results obtained show that the method is also effective for

EG-LDPC codes. Extensive simulation results are given to accurately estimate the

probability of error detection for different code sizes and numbers of errors.

HVL057

Exploration and Optimization of 3-D Integrated DRAM Subsystems

Abstract:

Energy efficiency is the major optimization criterion for systems-on-chip (SoCs)

for mobile devices (smartphones and tablets). Through silicon via (TSV) technology

enables 3-D integration of dies and the heterogeneous stacking of multiple memory or

logic layers, allowing increased bandwidth and lower energy consumption of the memory

interface compared to traditional approaches. In this paper, we explore the 3-D-DRAM

architecture design space. The result is an optimized 2 Gb 3-D-DRAM, which shows a

83% lower energy/bit than a 2 Gb device. Furthermore, we propose a highly energyefficient DRAM subsystem for next-generation 3-D-integrated SoCs, consisting of a

SDR/DDR 3-D-DRAM controller and an attached 3-D-DRAM cube with fine-grained

G2, Metha Complex, Little Mount, Saidapet, Chennai-15

Ph: 044-22200258, Mobile: 9840989556, 9952050233

Mail: projects@hades.in, contact@hades.in, www.hades.in

P a g e | 35

Hades InfoTech Pvt. Ltd

access and a flexible (WIDE-IO) interface. We assess the energy efficiency using a

synthesizable model of the SDR/DDR 3-D-DRAM channel controller (CC) as well as

functional models of the 3-D-stacked DRAM, including an accurate power estimation

engine. We also investigate different DRAM families (WIDE IO SDR/DDR, LPDDR,

and LPDDR2) and densities from 256 Mb to 4 Gb per channel. The implementation

results of the proposed 3-D-DRAM subsystem show that energy optimized accesses to

the 3-D-DRAM enable up to 50% energy savings compared to standard accesses. To the

best of our knowledge this is the first design space exploration for 3-D-stacked DRAM

considering different technologies based on real-world physical data and the first design

of a 3-D-DRAM CC and 3-D-DRAM model featuring co-optimization of memory and

controller architecture.

HVL058

Glitch-Free NAND-Based Digitally Controlled Delay-Lines

Abstract:

The recently proposed NAND-based digitally controlled delay-lines (DCDL)

present a glitching problem which may limit their employ in many applications. This

paper presents a glitch-free NAND-based DCDL which overcame this limitation by

opening the employ of NAND-based DCDLs in a wide range of applications. The

proposed NAND-based DCDL maintains the same resolution and minimum delay of

previously proposed NAND-based DCDL. The theoretical demonstration of the glitchfree operation of proposed DCDL is also derived in the paper. Following this analysis,

three driving circuits for the delay control-bits are also proposed. Proposed DCDLs have

been designed in a 90-nm CMOS technology and compared, in this technology, to the

state-of-the-art. Simulation results show that novel circuits result in the lowest resolution,

with a little worsening of the minimum delay with respect to the previously proposed

DCDL with the lowest delay. Simulations also confirm the correctness of developed

glitching model and sizing strategy. As example application, proposed DCDL is used to