Академический Документы

Профессиональный Документы

Культура Документы

Stldmid2 PDF

Загружено:

sreekantha2013Исходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Stldmid2 PDF

Загружено:

sreekantha2013Авторское право:

Доступные форматы

Signature of Invigilator

Signature of Examiner

Marks Obtained:

NAME:

ROLL NO.

GATE EC BY RK Kanodia

Logic Circuits

Q1

D1

D2

Q2

Chap 4.3

13. The counter shown in fig. P4.3.13 counts from

Q1

Q2

Q1

D1

D1

D2

Q2

A

B

Q1

1. The modulus of a 4-bit Ring CounterC is

(a) 4 (b)Q28 (c) 16 (d) 15

Q1

(A) 0 0 0 to 1 1 1

2. The modulus of a 4-bit Johnsons

Counter is

Y

Q

(C) 1 0 0 to 0 0 0

1(a) D4

2 (b) 28 (c) 16 (d) 15

Q1

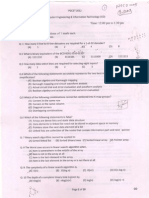

IIB. Tech II MidTerm Examinations: Objective Exam AY 2014-2015

Time: 20 Minutes Subject: S.T.L.D

Branch:E.E.E Max Marks: 10

C following

B CLR K Each question

A CLR K carries mark.

Answer the

Questions.

CLR K

(B) 1 1 1 to 0 0 0

(D) 0 0 0 to 1 0 0

14. to

Themod-numberoftheasyncr

3. How many 21 MUXS required

implement 10241 MUX

Q2

shown in fig. P4.2.13 is

(a) 10 (b)

11 (c) 1023 (d) 1024

J

4.5.QThe

forT0crictically

damping

series of

RLC

circuit are required

Q

To condition

count from

to 1024

how

many innumber

flip-flops

All J.K. input are HIGH

(a) 11 (b) CLK

10 (c) 12

B (d) 1023.

A

(A) R=2LC

(B) R= 4 L/C

(C) R^2 =4 L/C (D) R^2 =4 LC

Q and a 4 bit synchronous counter are made by flips flops having a propagation delay

6.Q A 4 bit ripple counter

Fig.P4.3.14

5. Fig.P4.3.11

Aofseries

circuit

R=15

ohms

, a counter

constantand

voltage

of 15V is applied

at t=o

10 nsRC

each.

If having

the worst

case

delayand

in L=

the0.2F

ripple

the synchronous

counter

be R and S

(A) 24

(B) 48

the

expression

for i(t) is

respectively,

then

counter

(C) 25S=10ns (c) R=10ns (D)

36

(a) 1.5e^(-t/3)

R=10ns, S=40ns

(b)e^(-t/3)

R=40ns,

,S=10ns

(d) R=40ns, S=40ns

(A)

(B) 15

(c) 1.e^(-t/3) (D) e^(-3t)

counter

T

D2

D3

the pulse

at is

z in

the network

of the pulse at 15.

z inThe

thefrequency

networkofshown

in fig

6. The time constant of the

circuit having R=5ohms L=0.2H is

Chap 8

7.00,

The

ate sequence

10, frequency

01, 00.....

shown

in

Chap 8

Analog and Digital

ate sequence 00, 10, 00, 10, 00 Analog

...... and Digital

(A) 2sec

ounter shown in fig. P4.3.12 is a

NOTES

Ring Counter

Counter

160 kHZ

MCQ

8.98

*

MCQ 8.98*Fig.P4.3.15

at

Mod-25

Ripple Counter

4-Bit Johnson

Counter

ripple

counter shown(B)

in 160

figure

(a)50%

10 HZ

(b) 160 HZ

5 HZ

(d)

40 HZ(C)

(A)The

10 Hz

Hz is made up of negative edge

(A)

efficiency

(B) (C)

100%

efficiency

20% efficiency

(D) 25%

triggered J-K

flip-flops.

The signal levels

at J efficiency

and K inputs of all

(C) 40 Hz

J

C

]2

]3

]4

[[ ] ]

(D) 5 Hz

the flip

flops are

logic triggered

1. Assume all

outputs are

8. The ripple counter shown in figure

is made

up maintained

of negativeat edge

J-Ktheflip-flops.

The signal levels

1 is applicable to

J

J

8.Q Reciprocity

Q theorem

cleared

just prior

to

applying

the clock

signal.

at J and K inputs of all the flip

are

maintained

logic

Assume

all the outputs are cleared just

16. flops

The three-stage

Johnson at

counter

as1.shown

in fig.

(A)

only

( B)signal

Bi-lateral

network

only

(C) linear/

bilateral networhonly (D) neather of the two

Blinear

A

prior

to network

applying

the clock

module

no. of

the counter

is:-

]6

[ ]

[[ ] ]

NOTES

7. Max power transfer occur

fig. P4.3.15. is

10-Bit (D)w 2.5Sec

4-Bit Parallel

Electronics

1sec

(C)Electronics

0.04 sec

( B)

]1

2

3

4

4. The Output Y of a 2-bit Comparator0 is logic 11 whenever

the 2-bit

input

A is greater than 2-bit input

B .The Number of combinations for which the logic 1 is (a) 4 (b) 5 (c) 10 (d) 6

K CLR

K CLR

K CLR

K CLR

K CLR

ircuit shown in fig. P4.3.11 is

CLK

[

Fig.P4.3.13

[ ]

[[ ] ]

P4.2.16

is clocked

at acounter

constantis:frequency of fc from the

module

no. of the

[ ]

Q

1is a property

K

K

starting

state of with

Q2Q1Q0 = 101. The frequency of output

9.Q mutual

inductance

associate

(A) only one

Fig.P4.3.12

8 up counter

10.

CLK

Q2Q1Q0 will be

(B) two or more coil

(C) two or more coil with magnetic (D) none

Q

J

J

J

The effictive value of an triangular wave

of Qalternative

quaninty

forQ peak value a is

8 down counter

6 up counter

(A) a/2

(B) a

(C) a/v3 (D) av3

K2

Q2

K1

Q1

K0

Q0

[ ]

CLK

6 down counter

11. For the below fig the polarity of(A)

the

7 mutual voltage is

(a) 7 (b) 5 (c) 8 (d) 4

Fig.P4.3.16

(C) 4

[[ ] ]

(B) 5

(D) 8

www.gatehelp.com

9. How

many 38

to implement 416 decoder

(A) Positive

(B) decoders

Negative required

( C) none

(a) 3 (b) 2 (c) 4 (6)

MCQ 8.99*

Page

218

10. The type of Flip-Flop used in a In

shift

Registers

is switch

Figure

, the ideal

S is switched on and off with a switching

. The

switching

time period is T = tON + tOFF s.

f = 10 kHz(d)

(a)SR Flip-Flop (b) D Flip-Flopfrequency

(c) T Flip-Flop

JK

Flip-Flop

The circuit is operated in steady state at the boundary of continuous

12.The

equivalent

oftoagenerated

given network

will so

have

F0 capacitor

11. TheLaplace-transformed

number of T flip-flops

required

a periodic

sequence

2

5 replaced

4 0 is

and discontinuous

conduction,

that(8/5)

the inductor

current

i6 isas3 by

(a)2 (b) 4 (c) 3 (d) 2

shown in Figure. Values of the on-time tON of the switch and peak

(A) 8/5 S (B) 5/8 S (C) 8/5S (D) 5/8S

current ip . are

12. A Flip-Flop is a Multi-vibrator

(a) Mono-Stable (b)Astable (c) both (d) Bi-stable

(A) 240 V

(B) 120 V

(C) 60 V

(D) 30 V

]10

[[ ] ]

11

]12

13. Number of parity bits required for 13-bits data word is

(a)5 (b) 3(c) 4 (d)2

]13

14. In Hamming Code Sequence number of parity bits are 6 for a range of data bits

(a)58-120 (b) 25-57 (c) 12-126 (d) 5-11

]14

15. In T Flip-Flop ,the output toggles when input T is

(a) 0 (b) 0 or 1 (c) 1 (d) dont care

]15

16. The Characteristic Equation Q(t+1) for SR Flip-Flop is

17. The Characteristic Equation Q(t+1) for JK Flip-Flop is

18. The Characteristic Equation Q(t+1) for T Flip-Flop is

19. The Characteristic Equation Q(t+1) for D Flip-Flop is

20. Race Around Condition will happen in Flip-Flop

II B.TECH II MID TERM EXAMINATIONS : DESCRIPTIVE EXAM

TIME :90 MIN SUBJECT ::STLD

AY:2014-2015

SET-1

BRANCH :EEE MAX.MARKS::30

ANSWER ANT THREE OF THE FOLLOWING QUESTIONS.

1. (a) Design a 4 bit binary UP/DOWN ripple counter.

(b) Draw the neat diagram of 4-bit Johnson counter and draw the relevant output wave forms.

SYNCHRONOUS (CLOCKED) SEQUENTIAL CIRCUITS

2. Complete the timing diagram for the circuit given below.

3.

257

Complete the timing diagram for this circuit.

CLK

CLK

Q

4.

Design a circuit that implements the state diagram

3. (a) Draw the neat diagram of locked JK flip-flop using NAND gates and give its truth table.

(b) Give the excitation table for T flip-flop,SR flip-flop,JK 0/0

flip-flop.

S0

1/1

4. (a) Design 32:1 multiplexer using 16:1 multiplexers.

S1

0/1

(b) Implement the following combinational circuit using 4 to 16 line decoder.

Y1 = m(2,3,9). 0/1

1/0

Y2 = m(10,12,13).

Y3 = m(2,4,8).

Y4 = m(1,2,4,7,10,12).S2

1/1

5. (a) List the PLA program table for combinational circuit that squares a 3-bit number.

(b) What is ROM ?Describes using the block diagram, what size ROM would it take to implement binary multiplier

that multiplies

two binary

numbers.

5. Design

a circuit

that implements the state diagram

0/0

S1

1/0

0/1

S0

1/1

S2

0/1

0/1

1/0

1/1

1/0

S4

S3

0/0

II B.TECH II MID TERM EXAMINATIONS : DESCRIPTIVE EXAM

TIME :90 MIN SUBJECT ::STLD

AY:2014-2015

SET-2

BRANCH :EEE MAX.MARKS::30

ANSWER ANT THREE OF THE FOLLOWING QUESTIONS.

1. (a) Design and implement MOD-6 synchronous counter using JK flip-flop.

(b) Draw the logic diagram of 4-bit shift register.Explain how Shift-left and Shift-Right operations are performed.

SYNCHRONOUS (CLOCKED) SEQUENTIAL CIRCUITS

2. Complete the timing diagram for the circuit given below.

3.

257

Complete the timing diagram for this circuit.

CLK

CLK

Q

4.

Design a circuit that implements the state diagram

3. (a) Draw the neat diagram of locked JK flip-flop using NAND gates and give its truth table.

(b) Give the excitation table for T flip-flop,SR flip-flop,JK 0/0

flip-flop.

S0

1/1

4. (a) Design 32:1 multiplexer using 16:1 multiplexers.

S1

0/1

(b) Implement the following combinational circuit using 4 to 16 line decoder.

Y1 = m(2,3,9). 0/1

1/0

Y2 = m(10,12,13).

Y3 = m(2,4,8).

Y4 = m(1,2,4,7,10,12).S2

1/1

5. (a) List the PLA program table for combinational circuit that squares a 3-bit number.

(b) What is ROM ?Describes using the block diagram, what size ROM would it take to implement binary multiplier

that multiplies

two binary

numbers.

5. Design

a circuit

that implements the state diagram

0/0

S1

1/0

0/1

S0

1/1

S2

0/1

0/1

1/0

1/1

1/0

S4

S3

0/0

Вам также может понравиться

- IES - Electronics Engineering - Digital Electronic CircuitsДокумент66 страницIES - Electronics Engineering - Digital Electronic Circuitsedwinaustine100% (4)

- Digital - Electronic - Assignment PDFДокумент14 страницDigital - Electronic - Assignment PDFDebbie UzoОценок пока нет

- DE PaperДокумент4 страницыDE Paperbhaveshgupta098Оценок пока нет

- Digital Electronics and CircuitsДокумент12 страницDigital Electronics and CircuitsGuruKPOОценок пока нет

- Gate - in 2011Документ18 страницGate - in 2011prabhjot singh1Оценок пока нет

- Sequential CircuitsДокумент33 страницыSequential CircuitsPrasun SinghalОценок пока нет

- Electronics June 2012Документ4 страницыElectronics June 2012bkvuvce8170Оценок пока нет

- BEST Question Bank - Digital ElectronicsДокумент157 страницBEST Question Bank - Digital Electronicsabhinav_pundir0% (1)

- DE09 SolДокумент157 страницDE09 SolRakesh KumarОценок пока нет

- Questions On Digital Electronics and MicroprocessorsДокумент12 страницQuestions On Digital Electronics and MicroprocessorsHarendra KumarОценок пока нет

- Testpaper - 1 NTДокумент13 страницTestpaper - 1 NTGattu SadashivaОценок пока нет

- Gate 23-09-2013Документ7 страницGate 23-09-2013Himanshu VasisthaОценок пока нет

- Ee2255 Digital Logic CircuitsДокумент3 страницыEe2255 Digital Logic CircuitsecessecОценок пока нет

- IES - Digital Mock Test - 2014Документ9 страницIES - Digital Mock Test - 2014Meenakshi SundaramОценок пока нет

- RRB Junior Electronics Engineer Study Material 3Документ66 страницRRB Junior Electronics Engineer Study Material 3thirumalОценок пока нет

- 9A04306 Digital Logic DesignДокумент4 страницы9A04306 Digital Logic DesignsivabharathamurthyОценок пока нет

- Ya Y Ya Y2 Ya Y A Y2: Common Data For Questions 3 & 4Документ19 страницYa Y Ya Y2 Ya Y A Y2: Common Data For Questions 3 & 4Rahul RoyОценок пока нет

- APR2013P21Документ63 страницыAPR2013P21qsashutoshОценок пока нет

- Digital Paper1Документ5 страницDigital Paper1Iyyakutti GanapathiОценок пока нет

- 1 - 1EC Model Test Paper 2Документ21 страница1 - 1EC Model Test Paper 2sacky3586Оценок пока нет

- 9A04401 Switching Theory & Logic DesignДокумент4 страницы9A04401 Switching Theory & Logic DesignsivabharathamurthyОценок пока нет

- 3CS3 04 PDFДокумент3 страницы3CS3 04 PDFprashantvlsiОценок пока нет

- Analog & Digital Electronics EC (IT) 303Документ10 страницAnalog & Digital Electronics EC (IT) 303Biswadip SahaОценок пока нет

- Digital Circuits and Logic DesignДокумент6 страницDigital Circuits and Logic DesignSharukh BujjiОценок пока нет

- Assignment EDES232CДокумент3 страницыAssignment EDES232CPrakash DasОценок пока нет

- 153psu Isro (Ec) - 2008 QuestionsДокумент11 страниц153psu Isro (Ec) - 2008 QuestionsSaisekhar AyenvalliОценок пока нет

- Gate - in 2005Документ25 страницGate - in 2005prabhjot singh1Оценок пока нет

- GATE - EC - Networks PDFДокумент39 страницGATE - EC - Networks PDFmsreenathreddyОценок пока нет

- MSQ Session 5 19Документ30 страницMSQ Session 5 19Voleti VnkumarОценок пока нет

- Prof. Anantha Chandrakasan and Prof. Don TroxelДокумент10 страницProf. Anantha Chandrakasan and Prof. Don TroxelCristian CastroОценок пока нет

- Ques of Eer in GatДокумент13 страницQues of Eer in Gatair1ingateОценок пока нет

- GATE ECE 2010 (WWW - Egate.ws)Документ16 страницGATE ECE 2010 (WWW - Egate.ws)Arun SharmaОценок пока нет

- EG2061 Electronics and ControlДокумент9 страницEG2061 Electronics and ControlTudor Octavian RusuОценок пока нет

- Ce & It July-12Документ10 страницCe & It July-12Patel PunitОценок пока нет

- ECE 2004 Gate Question PapersДокумент17 страницECE 2004 Gate Question PapersGanesh KonaОценок пока нет

- Mock ExamДокумент20 страницMock ExamkandulanageshОценок пока нет

- IES - Electronics Engineering - Control System PDFДокумент66 страницIES - Electronics Engineering - Control System PDFRod S Pangantihon Jr.Оценок пока нет

- DigitalДокумент182 страницыDigitalYeshoda MallikarjunaОценок пока нет

- IES - Electrical Engineering - Analog and Digital CircuitsДокумент81 страницаIES - Electrical Engineering - Analog and Digital CircuitsVishal KumarОценок пока нет

- EC8392-Digital EletronicsДокумент2 страницыEC8392-Digital Eletronicssyed1188Оценок пока нет

- EC Mock Test-3Документ20 страницEC Mock Test-3Arone AsadasОценок пока нет

- Electronics Sample Paper 1Документ13 страницElectronics Sample Paper 1krish_cvr2937Оценок пока нет

- Question Bank - Unit - Iii Part - A (Each Question Carries 1 Mark) Level 1-PART AДокумент8 страницQuestion Bank - Unit - Iii Part - A (Each Question Carries 1 Mark) Level 1-PART ANithya SОценок пока нет

- Digital EletronicДокумент12 страницDigital Eletronicom14440% (1)

- Q. 1 - Q. 25 Carry One Mark EachДокумент12 страницQ. 1 - Q. 25 Carry One Mark EachPooja SinhaОценок пока нет

- Chapter - 7 (Compatibility Mode)Документ32 страницыChapter - 7 (Compatibility Mode)Imran HayderОценок пока нет

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsОт EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsРейтинг: 5 из 5 звезд5/5 (1)

- Digital Signal Processing Using the ARM Cortex M4От EverandDigital Signal Processing Using the ARM Cortex M4Рейтинг: 1 из 5 звезд1/5 (1)

- Advanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkОт EverandAdvanced Electric Drives: Analysis, Control, and Modeling Using MATLAB / SimulinkОценок пока нет

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysОт EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysОценок пока нет

- Fundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsОт EverandFundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsОценок пока нет

- Combinatorial Algorithms: For Computers and CalculatorsОт EverandCombinatorial Algorithms: For Computers and CalculatorsРейтинг: 4 из 5 звезд4/5 (2)

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)От EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)Оценок пока нет

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxОт EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxРейтинг: 4 из 5 звезд4/5 (2)

- Discrete Wavelet Transform: A Signal Processing ApproachОт EverandDiscrete Wavelet Transform: A Signal Processing ApproachРейтинг: 5 из 5 звезд5/5 (2)

- Characteristic Modes: Theory and Applications in Antenna EngineeringОт EverandCharacteristic Modes: Theory and Applications in Antenna EngineeringОценок пока нет

- Service Certificate For Candidates Appearing For Divisional TestДокумент1 страницаService Certificate For Candidates Appearing For Divisional Testsreekantha2013Оценок пока нет

- Ex 1Документ1 страницаEx 1sreekantha2013Оценок пока нет

- L Tex Tutorial: University of Chicago Computer Science Instructional Laboratory (Maclab / Linux Lab)Документ11 страницL Tex Tutorial: University of Chicago Computer Science Instructional Laboratory (Maclab / Linux Lab)J_an__J_onsОценок пока нет

- How To Write A Thesis With LaTeXДокумент39 страницHow To Write A Thesis With LaTeXcongkhtnОценок пока нет

- 01 Notification No 16 2015Документ1 страница01 Notification No 16 2015sreekantha2013Оценок пока нет

- Set 2Документ5 страницSet 2sreekantha2013Оценок пока нет

- Distribution TransformerДокумент22 страницыDistribution TransformerRishi Kant SharmaОценок пока нет

- Sliptest 1Документ5 страницSliptest 1sreekantha20130% (2)

- Ex 6Документ1 страницаEx 6sreekantha2013Оценок пока нет

- Network Analysis Syllabus: Unit-IДокумент1 страницаNetwork Analysis Syllabus: Unit-Isreekantha2013Оценок пока нет

- Sliptest 2Документ4 страницыSliptest 2sreekantha2013Оценок пока нет

- EC 1997 UnsolvedДокумент11 страницEC 1997 Unsolvedsreekantha2013Оценок пока нет

- Example1: Sreekantha Reddy September 14, 2015Документ1 страницаExample1: Sreekantha Reddy September 14, 2015sreekantha2013Оценок пока нет

- C 4Документ32 страницыC 4sreekantha2013Оценок пока нет

- An Effective Approach For Distribution System Power Flow SolutionДокумент5 страницAn Effective Approach For Distribution System Power Flow SolutionSudheerKumarОценок пока нет

- Computation of VolДокумент8 страницComputation of Volsreekantha2013Оценок пока нет

- Sliptest 1Документ5 страницSliptest 1sreekantha20130% (2)

- Nov Dec 2013Документ1 страницаNov Dec 2013sreekantha2013Оценок пока нет

- Tabular MethodДокумент10 страницTabular Methodsreekantha201333% (3)

- STLD Cuorse OutcomesДокумент1 страницаSTLD Cuorse Outcomessreekantha2013Оценок пока нет

- EC 2003 UnsolvedДокумент20 страницEC 2003 Unsolvedsreekantha2013Оценок пока нет

- Gate 2002 Exam Question KeysДокумент20 страницGate 2002 Exam Question KeysAman AnandОценок пока нет

- A Loop Based Load Flow Method For Weakly Meshed Distribution NetworkДокумент5 страницA Loop Based Load Flow Method For Weakly Meshed Distribution Networksreekantha2013Оценок пока нет

- Computation of VolДокумент8 страницComputation of Volsreekantha2013Оценок пока нет

- EC 1996 UnsolvedДокумент5 страницEC 1996 Unsolvedsreekantha2013Оценок пока нет

- Ec 1993 PDFДокумент19 страницEc 1993 PDFarunathangamОценок пока нет

- Ec 1992Документ14 страницEc 1992np_nikhilОценок пока нет

- EE 1997 UnsolvedДокумент7 страницEE 1997 Unsolvedsreekantha2013Оценок пока нет

- ME 1991 Unsolved PDFДокумент13 страницME 1991 Unsolved PDFSathya ThyaguОценок пока нет

- Web Services.Документ13 страницWeb Services.vinaygarg2005Оценок пока нет

- Exercise 1 - Analog To Digital Conversion PointДокумент5 страницExercise 1 - Analog To Digital Conversion PointJoey DumandanОценок пока нет

- OLT Basic ConfigurationДокумент5 страницOLT Basic ConfigurationAndri MartianОценок пока нет

- Web Sec Quiz-Cat-309 PDFДокумент37 страницWeb Sec Quiz-Cat-309 PDFTajinder SinghОценок пока нет

- Gobi SDK Integration Guide For Windows CEДокумент17 страницGobi SDK Integration Guide For Windows CEJoaquin Andres Boilet HuertaОценок пока нет

- Exinda 4061 Datasheet PDFДокумент2 страницыExinda 4061 Datasheet PDFrebicОценок пока нет

- Feedback SrsДокумент8 страницFeedback SrsVinay Vyas0% (2)

- Online Bus Reservartion - Team 1 - Sec - B PDFДокумент27 страницOnline Bus Reservartion - Team 1 - Sec - B PDFDimo OfficialОценок пока нет

- MSA2000 Technical Cookbook - June 2nd 2009 - 4AA2-5505ENWДокумент57 страницMSA2000 Technical Cookbook - June 2nd 2009 - 4AA2-5505ENWquark2360100% (1)

- PIC18FДокумент19 страницPIC18Fsitizarina78Оценок пока нет

- STA309A: Multi-Channel Digital Audio Processor With DDX®Документ71 страницаSTA309A: Multi-Channel Digital Audio Processor With DDX®Uday KrishnaОценок пока нет

- Iot Syllabus Sem 8 Be EtrxДокумент3 страницыIot Syllabus Sem 8 Be EtrxThe Reality Check0% (1)

- Orchestration 1 - RequirementsДокумент2 страницыOrchestration 1 - RequirementsGamal AsaadОценок пока нет

- ETRI openTAM ONOSДокумент26 страницETRI openTAM ONOSkid4888Оценок пока нет

- 8085 Architecture Memory InterfacingДокумент46 страниц8085 Architecture Memory InterfacingRakesh Kumar DОценок пока нет

- Esp and Arduino ProgrammingДокумент31 страницаEsp and Arduino ProgrammingRaj Kumar82% (11)

- Lab 6 PDFДокумент8 страницLab 6 PDFDiego OrtegaОценок пока нет

- Onda Vx610w Tablet 7 Inch Capacitive Touchscreen All Winner A10 1.5GHz 2160P 8GBДокумент12 страницOnda Vx610w Tablet 7 Inch Capacitive Touchscreen All Winner A10 1.5GHz 2160P 8GBHong LeОценок пока нет

- Installing Cadence Virtuoso PDFДокумент25 страницInstalling Cadence Virtuoso PDFAhmed SalehОценок пока нет

- Parity Cloud ServiceДокумент34 страницыParity Cloud ServiceAbinBabyElichirayil100% (1)

- SAOUG-FlexCube 12c Architect For DBAДокумент14 страницSAOUG-FlexCube 12c Architect For DBAChuong NguyenОценок пока нет

- Physicslogic GatesДокумент19 страницPhysicslogic Gatesvijay tiwari0% (1)

- HiPath 3000 & 5000 V8 Manager C Administrator Documentation - Issue 6Документ271 страницаHiPath 3000 & 5000 V8 Manager C Administrator Documentation - Issue 6Rabii Maafi100% (1)

- Traffic Engineering Capacity PlanningДокумент16 страницTraffic Engineering Capacity PlanningRohit Chaudhary100% (2)

- Abc 5GДокумент25 страницAbc 5GMUHAMMED NASEEF MKОценок пока нет

- Tn179 05 PDFДокумент517 страницTn179 05 PDFchimbwaОценок пока нет

- AmikoДокумент7 страницAmikoAlexander WieseОценок пока нет

- Endpoint Advance Suite Install GuideДокумент12 страницEndpoint Advance Suite Install GuideSabkim23Оценок пока нет

- Mastering Citrix® XenDesktop® - Sample ChapterДокумент63 страницыMastering Citrix® XenDesktop® - Sample ChapterPackt PublishingОценок пока нет

- Chap8 HCI NotesДокумент3 страницыChap8 HCI Notesrboy1993Оценок пока нет