Академический Документы

Профессиональный Документы

Культура Документы

FPGA Realisation of SVPWM

Загружено:

srfmlpАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

FPGA Realisation of SVPWM

Загружено:

srfmlpАвторское право:

Доступные форматы

14th National Conference on Technological Trends | 30 - 31, August 2013 | College of Engineering Trivandrum

FPGA Realization of Space-Vector Pulse Width Modulation for a 3-Level

Inverter

Muhamed Shereef1 , Shiny.G2

Power Electronics Research Laboratory

Dept. of Electronics and Communication Engineering

College of Engineering Trivandrum, Kerala, India

srfmlp@gmail.com1

Abstract

A simplified space-vector pulse width modulation

(SVPWM) scheme for a 3-level inverter is presented. The

method involves the mapping of reference vector in the

space vector diagram of 3-level inverter to a 2-level inverter.

60 coordinate system is used to represent space vectors instead of using cartesian coordinate system. In 60 coordinate system only integer coordinates are involved. So the

computational complexity is reduced. The proposed scheme

is simulated and verified using Xilinx system generator software.

1. Introduction

Multilevel inverters are widely used in industrial drive

applications due to their ability to produce waveforms with

improved harmonic spectrum [1, 2]. Multi level inverters

can produce variable voltages and frequencies from discrete

voltage levels using pulse width modulation (PWM) strategies. Several techniques have been developed for the implementation of PWM [3, 4]. The two main methods are Sine

triangle Pulse width Modulation (SPWM) and Space Vector Pulse Width Modulation (SVPWM) [5, 6]. SPWM is

the simple and widely used scheme which generates PWM

signals by comparison of level shifted triangular carrier signals with a sinusoidal reference waveform [7, 8]. SVPWM

involves synthesising of reference sinusoidal voltage by

switching amoung the nearest three voltage spacevectors.

SVPWM is the best technique to implement PWM due to

following advantages. 1) higher o/p voltage for the same

dc-bus voltage 2) lower switching losses and 3) Better harmonic performance.

Implementation of SVPWM scheme involves 1.sector

identification 2.determination of nearest voltage space vectors to be switched 3.determination of duration of each

switching voltage space vectors 4.determination of an op-

timum switching sequence. A new approach for sector

identification using fractal concept is proposed in [9]. The

scheme in [9] uses cartesian coordinate system for the representation of space vectors. SVPWM scheme based on 60

coordinate system has been proposed in [10, 11, 12, 13].

For the implementation of SVPWM techniques Digital

Signal Processors (DSP) are widely used [14].But DSP executes control procedures sequentially using their mathematically oriented resources. So the mutual influences of

various control procedures should no longer be neglected

in high sampling rate applications. But differ from DSP

FPGA can execute control procedures concurrently. Due

to its powerful calculation ability and flexibility, FPGA is

considered as an appropriate solution to boost system performance of a digital controller including an SVPWM algorithm [15, 16, 17].

This paper proposes the implementation of SVPWM algorithm for a 3-level inverter based on 60 coordinate system using FPGA. As compared to cartesian coordinate system the representation of space vector using 60 coordinate

system greately reduces computational complexity since

only integer coordinates are involved.

2. Proposed Scheme

SVPWM involves synthesising of reference sinusoidal

voltage(Vref ) by switching amoung the nearest three voltage space vectors. In the proposed work 60 coordinate

system is used to represent the space vectors. Suppose

Va , Vb and Vc represents the instantaneous amplitudes of

three phase reference sinusoid, 60 coordinates (m, n) of

Vref can be found using the equations given below,

Vm = Va Vb

(1)

Vn = Vb Vc

(2)

(m, n) coordinates are normalized using the division by

Vdc /(l 1). Where Vdc is the d.c link voltage and l is the

362

14th National Conference on Technological Trends | 30 - 31, August 2013 | College of Engineering Trivandrum

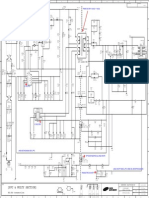

number of levels of inverter. Space vector representation

of a 3-level inverter using 60 coordinate system is shown

Figure. 1

Table 1. Sector identification (1=Satisfy, 0=Notsatisfy, =Dont

care)

Sector

1

2

3

4

5

6

Vmm 0

1

0

0

0

1

1

Vnm 0

1

1

1

0

0

0

|Vmm | |Vnm |

0

1

0

1

Determination of sub hexagon to which Vref belongs.

Mapping of Vref into the inner hexagon.

Find the sector of inner hexagon to which the mapped

reference vector Vrefm belongs.

Determination of duration of switching voltage space

vectors.

Determination of an optimum switching sequence.

Determination of actual switching vectors by adding

the switching vector corresponds to the sub hexagon

center.

Figure 1. Space vector representation of a 3-level inverter in 60

coordinate system

The space vector diagram of a three-level inverter can

be viewed as the composition of one inner hexagon and

six outer sub hexagons that are the space vector diagrams

of conventional two-level inverters. Each of these six sub

hexagons, constitutes the space vector diagram of a 3-level

inverter, centers on the six apexes of the inner hexagon. Figure. 2 shows the sub hexagon centers of 3-level inverter.

2.1. Sub Hexagon Center Identification

Sub hexagon center closest to the tip of Vref is determined by comparing (m, n) coordinates of Vref with each

sub hexagon center. Comparison is done by calculating

the distance from (m, n) coordinates of Vref to each sub

hexagon center using the equation

p

d = (Vm Vmh )2 + (Vn Vnh )2 + (Vm Vmh )(Vn Vnh )

(3)

where Vmh & Vnh are the corresponding sub hexagon center. The sub hexagon center with least value of d is selected.

2.2. Mapping to 2-level space vector

The hexagon center closest to the tip of Vref is subtracted from the respective (m, n) coordinates of Vref . Suppose Vref is located in sub hexagon with center B as in

Figure. 3 then the new coordinates of mapped reference

vector(Vref m ) can be calculated as

Figure 2. Space vector of a 3-level inverter showing Sub hexagon

centers

Steps involved in the implementation of SVPWM are

Vmm = Vm 0

(4)

Vnm = Vn 1

(5)

The sector to which the Vref m belongs can be found using Table. 1

Once the sector of operation is identified phase voltage switching timings of switching vectors can be found

as in Table. 2. It should be ensured the selected vectors are

switched in an optimum sequence so that only one switching occurs when the inverter changes its state.

363

14th National Conference on Technological Trends | 30 - 31, August 2013 | College of Engineering Trivandrum

FPGA. Coupled with a capability for implementing highly

parallel arithmetic architectures, this makes the FPGA ideally suited for creating high-performance PWM controllers.

Though VHDL provides many high level abstractions and

language constructs for simulation, its synthesizable subset

is far too restrictive for system design. System Generator

is a software tool for modeling and designing FPGA-based

DSP systems in Simulink. The tool presents a high level abstract view of a DSP system, yet nevertheless automatically

maps the system to a faithful hardware implementation. The

most significant is that System Generator provides these services without substantially compromising either the quality

of the abstract view or the performance of the hardware implementation.

3.1. System Generator

Figure 3. Mapping of Vref in to inner hexagon

Table 2. Equations for determining T1 and T2 for a two level inverter

Sector

1

2

3

4

5

6

T1

Ts Vmm

Ts (Vmm + Vnm )

Ts Vnm

Ts Vmm

Ts (Vmm + Vnm )

Ts Vnm

T2

Ts Vnm

Ts Vmm

Ts (Vmm + Vnm )

Ts Vnm

Ts Vmm

Ts (Vmm + Vnm )

2.3. Generation of Actual Switching Vector

Actual switching vector is generated by adding back the

hexagon center to the calculated switching vectors as shown

in Figure. 4.

Simulink provides a powerful high level modeling environment for DSP systems, and consequently is idely used

for algorithm development and verification. System Generator maintains an abstraction level very much in keeping

with the traditional Simulink block sets, but at the same time

automatically translates designs into hardware implementations that are faithful, synthesizable, and efficient [18].

The implementation is faithful in that the system model

and hardware implementation are bit-identical and cycleidentical at ample times defined in Simulink. The implementation is made efficient through the instantiation of intellectual property (IP) blocks that provide a range of functionality from arithmetic operations to complex DSP functions [18]. These IP blocks have been carefully designed

to run at high speed and to be area efficient. In System

Generator, the capabilities of IP blocks have been extended

transparently and automatically to fit gracefully into a system level framework. For example, although the underlying IP blocks operate on unsigned integers, System Generator allows signed and unsigned fixed point numbers to be

used, including saturation arithmetic and rounding. Userdefined IP blocks can be incorporated into a System Generator model as black boxes which will be embedded by the

tool into the HDL implementation of the design.

4. Modeling with system genereator

Figure 4. Generation of Actual switching vector

3. FPGA Implementation

Field-Programmable Gate Arrays (FPGAs) have become

key components in implementing high performance digital

signal processing (DSP) systems [17]. The memory bandwidth of a modern FPGA far exceeds that of a microprocessor or DSP running at clock rates two to ten times that of the

Before developing the hardware circuit for power, control and isolation circuit based on the FPGA, the entire

system is generated with the aid of simulation package

simulink/system generator for FPGA in order to verify the

pulses and the patterns of the output pulses. The creation of

a DSP design begins with a mathematical description of the

operations needed and concludes with a hardware realization of the algorithm [18]. The hardware implementation is

rarely faithful to the original functional description instead

it is faithful enough. The challenge is to make the hardware

area and speed efficient while still producing acceptable re-

364

14th National Conference on Technological Trends | 30 - 31, August 2013 | College of Engineering Trivandrum

Table 3. Status of the top switches of each Inverter during different

Voltage levels (For A-phase)

Inverter-1

OFF

OFF

ON

Inverter-2

OFF

ON

ON

VA0 O

0

Vdc /2

Vdc

Realized switching level

0

1

2

Figure 6. Simulation model

Figure 5. 3-level Inverter by Cascading two 2-level Inverters

sults. In a typical design flow, a flow supported by System

Generator the following steps occur:

1. Describe the algorithm in mathematical terms

2. Realize the algorithm in the design environment, initially using double precision

Figure 7. Switching signals generated for 2-level operation: Top 3traces for Inverter-1 & Lower 3-traces for Inverter-2 (Modulation

index 0.25)

3. Trim double precision arithmetic down to fixed point

4. Translate the design into efficient hardware

Step 4 is error prone because it can be difficult to guarantee the hardware implements the design faithfully. System

Generator eliminates this concern by automatically generating a faithful hardware implementation.

5. Simulation and Results

5.1. 3-Level Inverter Configuration

3-Level Inverter is achieved by cascading two 2-level Inverters having same D.C link voltage of Vdc /2 as shown in

Figure. 5.

VAO , VBO and VCO represents the pole voltages of

Inverter-1. VA0 O , VB 0 O and VC 0 O represents pole voltages

of Inverter-2. Status of the top switches of the individual inverters during different voltage levels is shown in Table. 3. In case of 2-level operation ie, the reference vector

(Vref ) is in the inner hexagon, only inverter-2 is switched

and inverter-1 is clamped to zero level.

5.2. Modeling Using System Generator

The proposed algorithm is generated in front end with

the aid of system generator editor, and the sampling fre-

Figure 8. Switching signals generated for 3-level operation: Top 3traces for Inverter-1 & Lower 3-traces for Inverter-2 (Modulation

index 0.75)

quency is set to 5kHz. The entire system is shown in Figure 6.

Switching pulses generated for a modulation index of

0.25, i.e. corresponds to 2-level operation, are shown in

Figure 7. As seen, in 2-level operation, only inverter-2

is switched and inverter-1 is clamped to zero level. The

switching pulses generated for 3-level operation (modulation index = 0.75) are shown in Figure 8. Both the inverters

switch equally during 3-level operation.

6. Conclusion

This paper proposes a method for the implementation of

SVPWM in FPGA. Since the SVPWM method is based on

the 60 coordinate system instead of cartesian coordinate

system computational complexity is greatly reduced. The

scheme is simulated for a 3-level inverter. 3-level inverter is

365

14th National Conference on Technological Trends | 30 - 31, August 2013 | College of Engineering Trivandrum

realised by cascading two 2-level inverters.

References

[1] A. Nabae, I.Takahashi, and H. Akagi, A new neutral

point clamped pwm inverter, IEEE Transactions on Industry Applications, vol. 1A-17, no. 5, pp. 518523, September/October 1981.

[2] Heinz Willi Van Der Broeck, Hans-Christoph Skudelny,

and Georg Viktor Stanke, Analysis and realization of a

pulsewidth modulator based on voltage space vectors, IEEE

Transactions on Industry Applications, vol. 24, no. 1, pp.

142150, January/February 1988.

[3] J. Holtz, Pulse width modulationa survey, IEEE Trans.

Ind. Electron., vol. 39, no. 5, pp. 410420, Dec. 1992.

[4] W. Yao, H. Hu, and Z. Lu, Comparisons of space-vector

modulation and carrier based modulation of multilevel inverter, IEEE Trans. Power Electron., vol. 23, no. 1, pp.

4551, Jan. 2008.

[14] F. Blaabjerg A. M. Trzynadlowski, M. M. Bech and J. K.

Pedersen, An integral space-vectorpwmtechnique for dspcontrolled voltagesource inverters, IEEE Trans. Ind. Appl.,

vol. 35, no. 5, pp. 10911097, Jul./Aug. 1999.

[15] T. Ying-Yu and H. Hau-Jean, Fpga realization of spacevector pwm control 1c for three-phase pwm inverters, EEE

Trans. Power Electron., vol. 12, no. 6, pp. 953963, Nov.

1997.

[16] L. Wenhua C. Yuanhua L. Tian, S. Qiang and L. Jianguo,

Fpgabased universal multilevel space vector modulator,

Proc. IECON 32nd Annu. Conf, pp. 745749, 2005.

[17] P. Fioravanti C. Cecati. M. Cirstea. M. Mc. Cormick, Design of a fpga implementing a passivity-based pulsewidth

modulation, SPEEDAM 2002, pp. A2 43A2 48, 2002.

[18] Xtremedsp starter kit - spartan-3a dsp application notes and

product information available online at (www.xilinx.com),

.

[5] V. T. Somasekhar and K. Gopakumar, Three-level inverter

configuration cascading two two-level inverters, Proc. Inst.

Elect. Eng.Electr. Power Appl., vol. 150, no. 3, pp. 245254,

May 2003.

[6] A. K. Gupta and A. M. Khambadkone, A space vector

modulation scheme to reduce common mode voltage for cascaded multilevel inverters, IEEE Trans. Power Electron.,

vol. 22, no. 5, pp. 16721681, Sep. 2007.

[7] G. Carrara, S. G. Gardella, M. Marchesoni, R. Salutari, and

G. Sciutto, A new multilevel pwmmethod: A theoretical

analysis, IEEE Trans. Power Electron., vol. 7, no. 3, pp.

497505, Jul. 1992.

[8] H. Bai, Z. Zhao, S. Meng, J. Liu, and X. Sun, Comparison

of three pwm strategies-spwm, svpwm & one-cycle control,

Proc. 5th Int. Conf. Power Electron. Drive Syst., vol. 2, pp.

13131316, 2003.

[9] Anish Gopinath, Aneesh Mohamed A.S, and M.R.Baiju,

Fractal based space vector pwm for multilevel inverters a

novel approach, IEEE Transactions on Industrial Electronics, vol. 52, no. 4, pp. 12301238, April 2009.

[10] Haibing Hu Wenxi Yao and Zhengyu Lu, Comparison of

space vector modulation and carrier based modulation of

multilevel inverter, IEEE Transactions on Power Electronics, vol. 23, no. 1, pp. 4541, January 2008.

[11] N.Celanovic and Dushan Boroyevich, A fast space-vector

modulation algorithm for multilevel three-phase converters,

IEEE Transactions on Industry Applications, vol. 37, no. 2,

pp. 637641, March/April 2001.

[12] Fahai Li Sanmin Wei, Bin Wu and Congwei Liu, A general

space vector pwm control algorithm for multilevel inverters,

Proc. APEC 2003, pp. 562568.

[13] Chang Ho Choi Jae Hyeong Seo and Dong Seok Hyun, A

new simplified space vector pwm method for three-level inverters, IEEE Transactions on Industry Applications, vol.

16, no. 4, pp. 545550, July 2001.

366

Вам также может понравиться

- Spline and Spline Wavelet Methods with Applications to Signal and Image Processing: Volume III: Selected TopicsОт EverandSpline and Spline Wavelet Methods with Applications to Signal and Image Processing: Volume III: Selected TopicsОценок пока нет

- Space Vector PWM - 1Документ5 страницSpace Vector PWM - 1guanitouОценок пока нет

- Software Radio: Sampling Rate Selection, Design and SynchronizationОт EverandSoftware Radio: Sampling Rate Selection, Design and SynchronizationОценок пока нет

- FPGA Implementation On SVPWM MLIДокумент5 страницFPGA Implementation On SVPWM MLISheetal VermaОценок пока нет

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDОт EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDОценок пока нет

- VLP 0401 " Space Vector PWM Using FPGA"Документ6 страницVLP 0401 " Space Vector PWM Using FPGA"ashish3179100% (1)

- Generalized Rail Clamping Sequences Based PWM (GRCPWM) Algorithm For Direct Torque Controlled Induction Motor DriveДокумент22 страницыGeneralized Rail Clamping Sequences Based PWM (GRCPWM) Algorithm For Direct Torque Controlled Induction Motor DriveHari ReddyОценок пока нет

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsОт EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsОценок пока нет

- De Embedding and Embedding S Parameter Networks Using A Vector Network AnalyzerДокумент24 страницыDe Embedding and Embedding S Parameter Networks Using A Vector Network AnalyzerAlexander LaraОценок пока нет

- Power Systems-On-Chip: Practical Aspects of DesignОт EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardОценок пока нет

- Kiran Gunnam, Weihuang Wang, Euncheol Kim, Gwan Choi, Mark YearyДокумент6 страницKiran Gunnam, Weihuang Wang, Euncheol Kim, Gwan Choi, Mark YearypathmakerpkОценок пока нет

- FPGA Implementation of Simplified SVPWM Algorithm For Three Phase Voltage Source InverterДокумент8 страницFPGA Implementation of Simplified SVPWM Algorithm For Three Phase Voltage Source InverterVenkata Krishna AndeyОценок пока нет

- Volume 3 - Number 1 - Tools For Microwave Radio Communications System DesignДокумент13 страницVolume 3 - Number 1 - Tools For Microwave Radio Communications System DesignArter AlayОценок пока нет

- Energies: Adaptive Wide-Area Damping Control Scheme For Smart Grids With Consideration of Signal Time DelayДокумент18 страницEnergies: Adaptive Wide-Area Damping Control Scheme For Smart Grids With Consideration of Signal Time Delaycontrol_613Оценок пока нет

- Cascaded Multilevel InvertersДокумент6 страницCascaded Multilevel InvertersMinhaj NaimОценок пока нет

- Fast-Predictive Optimal Control of NPC Multilevel ConvertersДокумент9 страницFast-Predictive Optimal Control of NPC Multilevel Converterskanda71Оценок пока нет

- A Digital-Based Optimal AVR Design of Synchronous Generator Exciter Using LQR TechniqueДокумент13 страницA Digital-Based Optimal AVR Design of Synchronous Generator Exciter Using LQR Technique3KaiserEОценок пока нет

- Modif 24626-48450-1-PBДокумент10 страницModif 24626-48450-1-PBdodol garutОценок пока нет

- Design of FMCW Radars For Active Safety Applications PDFДокумент5 страницDesign of FMCW Radars For Active Safety Applications PDFAnonymous LoJy6ERXdОценок пока нет

- Simplified SVPWM Algorithm For Neutral Point Clamped 3-Level Inverter Fed DTC-IM DriveДокумент6 страницSimplified SVPWM Algorithm For Neutral Point Clamped 3-Level Inverter Fed DTC-IM DrivePasupuleti SivakumarОценок пока нет

- A Simple and Ultra-Fast DSP-Based Space Vector PWM Algorithm andДокумент6 страницA Simple and Ultra-Fast DSP-Based Space Vector PWM Algorithm andShiviAroraОценок пока нет

- A Simplified Dwell Time Computation Method For SVPДокумент13 страницA Simplified Dwell Time Computation Method For SVPFlynn RyderОценок пока нет

- Ntroduction: Fig.1. Principle Block DiagramДокумент4 страницыNtroduction: Fig.1. Principle Block Diagramanant0008Оценок пока нет

- DSSS Synchronization SubsystemДокумент21 страницаDSSS Synchronization Subsystemapi-26331790Оценок пока нет

- Implementation of Adaptive Viterbi DecoderДокумент7 страницImplementation of Adaptive Viterbi DecoderseventhsensegroupОценок пока нет

- Vlsi Design Approach To High-Performance Direct Torque Control of Induction Motor DrivesДокумент8 страницVlsi Design Approach To High-Performance Direct Torque Control of Induction Motor Drivesjooner45Оценок пока нет

- Pscad ModelingДокумент21 страницаPscad ModelingSumith Wellawa100% (1)

- Multilevel Multiphase Space Vector PWM Algorithm Applied To Three-Phase ConvertersДокумент7 страницMultilevel Multiphase Space Vector PWM Algorithm Applied To Three-Phase ConvertersAthiesh KumarОценок пока нет

- Power Quality RecorderДокумент8 страницPower Quality RecorderSpiros LoutridisОценок пока нет

- Digital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveДокумент7 страницDigital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveijsretОценок пока нет

- Design and Implement of QPSK Modem Based On FPGAДокумент3 страницыDesign and Implement of QPSK Modem Based On FPGAAnil PatilОценок пока нет

- A General Space Vector PWM Algorithm For Multilevel Inverters, Including Operation in OvermodulationДокумент10 страницA General Space Vector PWM Algorithm For Multilevel Inverters, Including Operation in OvermodulationxuanthamdhqnОценок пока нет

- A Compact Ultra-Wideband Load-Pull Measurement SystemДокумент6 страницA Compact Ultra-Wideband Load-Pull Measurement Systemoğuz odabaşıОценок пока нет

- Simulation of A Space Vector PWM Controller For A Five-Level Voltage-Fed Inverter Motor DriveДокумент7 страницSimulation of A Space Vector PWM Controller For A Five-Level Voltage-Fed Inverter Motor DriveIOSRjournalОценок пока нет

- FPGA Based Implementation of Symmetrical Switching in SVPWM For Three Level NPC ConverterДокумент6 страницFPGA Based Implementation of Symmetrical Switching in SVPWM For Three Level NPC ConvertersateeshОценок пока нет

- FPGA-Based Implementation of Digital Control For A Magnetic BearingДокумент6 страницFPGA-Based Implementation of Digital Control For A Magnetic Bearingajith.ganesh2420Оценок пока нет

- Design and Implemation of An Enhanced Dds Based Digital Modulator For Multiple Modulation Schemes Manoj Kollam, S.A.S Krishna Chaithanya and Nagaraju Kommu IJSSAN 2011Документ6 страницDesign and Implemation of An Enhanced Dds Based Digital Modulator For Multiple Modulation Schemes Manoj Kollam, S.A.S Krishna Chaithanya and Nagaraju Kommu IJSSAN 2011John JohnstonОценок пока нет

- Modeling Heterogeneous Systems Using Systemc-Ams Case Study: A Wireless Sensor Network NodeДокумент6 страницModeling Heterogeneous Systems Using Systemc-Ams Case Study: A Wireless Sensor Network Nodesimon9085Оценок пока нет

- FPGA Implementation of CORDIC-Based QRD-RLS AlgorithmДокумент5 страницFPGA Implementation of CORDIC-Based QRD-RLS Algorithmsappal73asОценок пока нет

- Assignment: Application of Graphs in Computer ProgrammingДокумент11 страницAssignment: Application of Graphs in Computer ProgrammingSaran AgarwalОценок пока нет

- Lab No.2 Modeling A Micro Strip Transmission Line in ADS: Objective: TheoryДокумент5 страницLab No.2 Modeling A Micro Strip Transmission Line in ADS: Objective: Theorymuhammad jehangirОценок пока нет

- Paper-7 An Application of Direct Modulation To Generate SPWM Waveform Using VHDL For FPGA Interfaced H-Bridge Power InverterДокумент6 страницPaper-7 An Application of Direct Modulation To Generate SPWM Waveform Using VHDL For FPGA Interfaced H-Bridge Power InverterRachel WheelerОценок пока нет

- IET - KCJ - Performance Evaluation of A General SVPWMДокумент9 страницIET - KCJ - Performance Evaluation of A General SVPWMKartick JanaОценок пока нет

- Edm CNC Paper NCДокумент10 страницEdm CNC Paper NCramjoceОценок пока нет

- Automated Measurement of Frequency Response of Electrical Networks Filters and AmplifiersДокумент7 страницAutomated Measurement of Frequency Response of Electrical Networks Filters and AmplifiersDiscrete ComponentОценок пока нет

- FPGA Implementation of The Ternary Pulse Compression SequencesДокумент5 страницFPGA Implementation of The Ternary Pulse Compression SequencesvijaykannamallaОценок пока нет

- Energies 12 04332 v2Документ24 страницыEnergies 12 04332 v2thinhОценок пока нет

- Internal ModelДокумент15 страницInternal ModelDiego RamirezОценок пока нет

- Digital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveДокумент7 страницDigital Scalar Pulse Width Modulation Methods For Voltage Source Inverter Fed Ac DriveMuhamad Taufiq AhsanОценок пока нет

- Research Inventy: International Journal of Engineering and ScienceДокумент10 страницResearch Inventy: International Journal of Engineering and ScienceresearchinventyОценок пока нет

- National Institute of Technology: Karnataka, SurathkalДокумент36 страницNational Institute of Technology: Karnataka, SurathkalSneha JogdhankarОценок пока нет

- Design of Linear Array Transducer Using Ultrasound Simulation Program Field-IIДокумент7 страницDesign of Linear Array Transducer Using Ultrasound Simulation Program Field-IIinventyОценок пока нет

- Patch Antenna Design Using MICROWAVE STUDIOДокумент6 страницPatch Antenna Design Using MICROWAVE STUDIOmayank sharmaОценок пока нет

- FFT in SarДокумент5 страницFFT in SarBhuvanachandran AОценок пока нет

- A Simple Space Vector PWM Generation Scheme For Any General N-Level InverterДокумент9 страницA Simple Space Vector PWM Generation Scheme For Any General N-Level InverterAhmad MqdadОценок пока нет

- Microprocessors and Microsystems: Ganesan R, S. Suresh, SS SivarajuДокумент9 страницMicroprocessors and Microsystems: Ganesan R, S. Suresh, SS SivarajufvijayamiОценок пока нет

- Vol. 12 No. 2 Pp. 571-579Документ10 страницVol. 12 No. 2 Pp. 571-579Abdelmalik BendaikhaОценок пока нет

- A Software Radio Architecture For Smart AntennasДокумент8 страницA Software Radio Architecture For Smart AntennasRockstar_rohithОценок пока нет

- Hardware Implementation: Branch Metric Unit (BMU)Документ6 страницHardware Implementation: Branch Metric Unit (BMU)api-19790923Оценок пока нет

- Scotle Technology Group Ltd. Scotle IR6000 V3. BGA Rework Station. User Manual.Документ17 страницScotle Technology Group Ltd. Scotle IR6000 V3. BGA Rework Station. User Manual.zigmund zigmundОценок пока нет

- 6040z Usb GuideДокумент14 страниц6040z Usb GuideArchil GogorishviliОценок пока нет

- RB941-2nD-TC Product Details 2018-08-08 0104Документ2 страницыRB941-2nD-TC Product Details 2018-08-08 0104AliviaNovitaAndariОценок пока нет

- Nikola TeslaДокумент4 страницыNikola TeslaipraoОценок пока нет

- FSL100 Series Flame Detector Quick Start Guide: Wiring To A 4-20 Ma Current Sourcing PLCДокумент2 страницыFSL100 Series Flame Detector Quick Start Guide: Wiring To A 4-20 Ma Current Sourcing PLCeng_elbarbaryОценок пока нет

- Programming Analogue SynthsДокумент132 страницыProgramming Analogue SynthsGui Felipe100% (1)

- S150-41-K001 SK330-SK350-6E Main Pump & Software ChangeДокумент2 страницыS150-41-K001 SK330-SK350-6E Main Pump & Software ChangePHÁT NGUYỄN THẾ100% (2)

- Apm213 QuizДокумент17 страницApm213 QuizCem ArasanОценок пока нет

- Leroy Somer LSA 54.2Документ16 страницLeroy Somer LSA 54.2Seno PT. AAEОценок пока нет

- Frequency Ranges: H5: 518.000-542.000 MHZДокумент5 страницFrequency Ranges: H5: 518.000-542.000 MHZJОценок пока нет

- Installed FilesДокумент32 страницыInstalled FilesDavid Martinez VazquezОценок пока нет

- VHDL Based Circuits Design and Synthesis On FPGA: A Dice Game Example For EducationДокумент6 страницVHDL Based Circuits Design and Synthesis On FPGA: A Dice Game Example For EducationRam RajaОценок пока нет

- CLARO COMBO Emergency Light With Exit Signs v1.3Документ2 страницыCLARO COMBO Emergency Light With Exit Signs v1.3Charlie MendozaОценок пока нет

- Oil Burner Controls Type BHO 64 and LOA 44 - DanfossДокумент12 страницOil Burner Controls Type BHO 64 and LOA 44 - Danfossr_cristiОценок пока нет

- Alsa Alsatom SU-50,100,140 - User ManualДокумент9 страницAlsa Alsatom SU-50,100,140 - User ManualdianОценок пока нет

- GST200-2 Intelligent Fire Alarm Control Panel Issue 1.11 PDFДокумент60 страницGST200-2 Intelligent Fire Alarm Control Panel Issue 1.11 PDFelmerbarrerasОценок пока нет

- Investigation - of - 3G IRAT CS Handover Degradation Due To Iphone 5Документ9 страницInvestigation - of - 3G IRAT CS Handover Degradation Due To Iphone 5Akhtar KhanОценок пока нет

- WC 4250 MFP BrochДокумент4 страницыWC 4250 MFP BrochLaser-Way Office-MachinesОценок пока нет

- Proline Promass 80 Operating InstructionsДокумент130 страницProline Promass 80 Operating InstructionsOgnjen DrljanОценок пока нет

- R2R Link Kit Installation GuideДокумент12 страницR2R Link Kit Installation GuideKe HolaОценок пока нет

- C M ProjectДокумент54 страницыC M ProjectCONVEX VENTURESОценок пока нет

- CCE Microonda M-190 120V Diagrama Esquematico PDFДокумент1 страницаCCE Microonda M-190 120V Diagrama Esquematico PDFJose UzcateguiОценок пока нет

- DSA I/O For Distributed Starters: Cat. Nos. 100-DNY41R, 100-DNY42R, 100-DNY42SДокумент6 страницDSA I/O For Distributed Starters: Cat. Nos. 100-DNY41R, 100-DNY42R, 100-DNY42SelyuyaОценок пока нет

- Exercise 11Документ36 страницExercise 11David BamОценок пока нет

- JVM 4 5Документ2 страницыJVM 4 5icygears21Оценок пока нет

- (PFC & Multy Section) : Tranf - de Stby 5.3Vcd Y 13VcdДокумент2 страницы(PFC & Multy Section) : Tranf - de Stby 5.3Vcd Y 13Vcdcentauro2013100% (1)

- Artificial Transmission Line Dec 16Документ33 страницыArtificial Transmission Line Dec 16Arindam SenОценок пока нет

- NDR Jammer OverviewДокумент1 страницаNDR Jammer OverviewhardedcОценок пока нет

- DL24P Schematic DiagramДокумент1 страницаDL24P Schematic DiagramLAN JR HOUSE0% (1)

- STEP 7 Professional Programming and Configuring According To IEC 61131-3Документ16 страницSTEP 7 Professional Programming and Configuring According To IEC 61131-3scribd010% (1)

- The Millionaire Fastlane, 10th Anniversary Edition: Crack the Code to Wealth and Live Rich for a LifetimeОт EverandThe Millionaire Fastlane, 10th Anniversary Edition: Crack the Code to Wealth and Live Rich for a LifetimeРейтинг: 4.5 из 5 звезд4.5/5 (89)

- $100M Offers: How to Make Offers So Good People Feel Stupid Saying NoОт Everand$100M Offers: How to Make Offers So Good People Feel Stupid Saying NoРейтинг: 5 из 5 звезд5/5 (23)

- $100M Leads: How to Get Strangers to Want to Buy Your StuffОт Everand$100M Leads: How to Get Strangers to Want to Buy Your StuffРейтинг: 5 из 5 звезд5/5 (18)

- Broken Money: Why Our Financial System Is Failing Us and How We Can Make It BetterОт EverandBroken Money: Why Our Financial System Is Failing Us and How We Can Make It BetterРейтинг: 5 из 5 звезд5/5 (3)

- The Coaching Habit: Say Less, Ask More & Change the Way You Lead ForeverОт EverandThe Coaching Habit: Say Less, Ask More & Change the Way You Lead ForeverРейтинг: 4.5 из 5 звезд4.5/5 (186)

- 12 Months to $1 Million: How to Pick a Winning Product, Build a Real Business, and Become a Seven-Figure EntrepreneurОт Everand12 Months to $1 Million: How to Pick a Winning Product, Build a Real Business, and Become a Seven-Figure EntrepreneurРейтинг: 4 из 5 звезд4/5 (2)

- Fascinate: How to Make Your Brand Impossible to ResistОт EverandFascinate: How to Make Your Brand Impossible to ResistРейтинг: 5 из 5 звезд5/5 (1)

- Think Faster, Talk Smarter: How to Speak Successfully When You're Put on the SpotОт EverandThink Faster, Talk Smarter: How to Speak Successfully When You're Put on the SpotРейтинг: 5 из 5 звезд5/5 (1)