Академический Документы

Профессиональный Документы

Культура Документы

MCS-51™ Instruction Set Summary: Grantronics Pty LTD

Загружено:

Vishal Gudla NagrajОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

MCS-51™ Instruction Set Summary: Grantronics Pty LTD

Загружено:

Vishal Gudla NagrajАвторское право:

Доступные форматы

GRANTRONICS PTY LTD

By Prof. Rajendra Khope

45 Monash Street, P.O. Box 275,

ACN 070 123 643

WENTWORTHVILLE. N.S.W. 2145.

AUSTRALIA. Phone: (02) 9896-7150. Fax: (02) 9896-7153. Internet: http://www.grantronics.com.au

GRANTRONICS

MCS-51 Instruction Set Summary

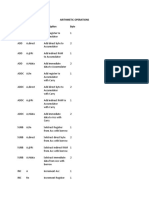

ARITHMETIC OPERATIONS

Mnemonic

Description

ADD

ADD

ADD

ADD

ADDC

ADDC

ADDC

ADDC

SUBB

SUBB

SUBB

SUBB

INC

INC

INC

INC

DEC

DEC

DEC

DEC

INC

MUL

DIV

DA

Add register to A

Add direct byte to A

Add indirect RAM to A

Add immediate data to A

Add register to A with Carry

Add direct byte to A with Carry

Add indirect RAM to A with Carry

Add immediate data to A with Carry

Subtract register from A with Borrow

Subtract direct byte from A with Borrow

Subtract indirect RAM from A with Borrow

Subtract immediate data from A with Borrow

Increment A

Increment register

Increment direct byte

Increment indirect RAM

Decrement A

Decrement register

Decrement direct byte

Decrement indirect RAM

Increment Data Pointer

Multiply A & B (A x B => BA)

Divide A by B (A/B => A + B)

Decimal Adjust A

A,Rn

A,direct

A,@Ri

A,#data

A,Rn

A,direct

A,@Ri

A,#data

A,Rn

A,direct

A,@Ri

A,#data

A

Rn

direct

@Ri

A

Rn

direct

@Ri

DPTR

AB

AB

A

BOOLEAN VARIABLE MANIPULATION

Bytes Cycles

1

2

1

2

1

2

1

2

1

2

1

2

1

1

2

1

1

1

2

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2

4

4

1

LOGICAL OPERATIONS

Mnemonic

Description

ANL

ANL

ANL

ANL

ANL

ANL

ORL

ORL

ORL

ORL

ORL

ORL

XRL

XRL

XRL

XRL

XRL

XRL

CLR

CPL

RL

RLC

RR

RRC

SWAP

AND register to A

AND direct byte to A

AND indirect RAM to A

AND immediate data to A

AND A to direct byte

AND immediate data to direct byte

OR register to A

OR direct byte to A

OR indirect RAM to A

OR immediate data to A

OR A to direct byte

OR immediate data to direct byte

Exclusive-OR register to A

Exclusive-OR direct byte to A

Exclusive-OR indirect RAM to A

Exclusive-OR immediate data to A

Exclusive-OR A to direct byte

Exclusive-OR immediate data to direct byte

Clear A

Complement A

Rotate A Left

Rotate A Left through Carry

Rotate A Right

Rotate A Right through Carry

Swap nibbles within A

A,Rn

A,direct

A,@Ri

A,#data

direct,A

direct,#data

A,Rn

A,direct

A,@Ri

A,#data

direct,A

direct,#data

A,Rn

A,direct

A,@Ri

A,#data

direct,A

direct,#data

A

A

A

A

A

A

A

Bytes Cycles

1

2

1

2

2

3

1

2

1

2

2

3

1

2

1

2

2

3

1

1

1

1

1

1

1

1

1

1

1

1

2

1

1

1

1

1

2

1

1

1

1

1

2

1

1

1

1

1

1

1

Mnemonic

Description

Move register to A

Move direct byte to A

Move indirect RAM to A

Move immediate data to A

Move A to register

Move direct byte to register

Move immediate data to register

Move A to direct byte

Move register to direct byte

Move direct byte to direct byte

Move indirect RAM to direct byte

Move immediate data to direct byte

Move A to indirect RAM

Move direct byte to indirect RAM

Move immediate data to indirect RAM

Load Data Pointer with 16-bit constant

Move Code byte relative to DPTR to A

Move Code byte relative to PC to A

Move External RAM (8-bit addr) to A

Move External RAM (16-bit addr) to A

Move A to External RAM (8-bit addr)

Move A to External RAM (16-bit addr)

Push direct byte onto stack

Pop direct byte from stack

Exchange register with A

Exchange direct byte with A

Exchange indirect RAM with A

Exchange low-order Digit indirect RAM with A

A,Rn

A,direct

A,@Ri

A,#data

Rn,A

Rn,direct

Rn,#data

direct,A

direct,Rn

direct,direct

direct,@Ri

direct,#data

@Ri,A

@Ri,direct

@Ri,#data

DPTR,#data16

A,@A+DPTR

A,@A+PC

A,@Ri

A,@DPTR

@Ri,A

@DPTR,A

direct

direct

A,Rn

A,direct

A,@Ri

A,@Ri

Description

CLR

CLR

SETB

SETB

CPL

CPL

ANL

ANL

ORL

ORL

MOV

MOV

Clear Carry flag

Clear direct bit

Set Carry flag

Set direct bit

Complement Carry flag

Complement direct bit

AND direct bit to Carry flag

AND complement of direct bit to Carry flag

OR direct bit to Carry flag

OR complement of direct bit to Carry flag

Move direct bit to Carry flag

Move Carry flag to direct bit

C

bit

C

bit

C

bit

C,bit

C,/bit

C,bit

C,/bit

C,bit

bit,C

Bytes Cycles

1

2

1

2

1

2

2

2

2

3

2

3

1

2

2

2

1

1

1

1

1

1

2

2

1

2

1

1

1

1

1

1

1

2

1

1

2

2

2

2

1

2

1

1

2

2

2

2

2

2

2

2

1

1

1

1

Bytes Cycles

1

2

1

2

1

2

2

2

2

2

2

2

1

1

1

1

1

1

2

2

2

2

1

2

PROGRAM AND MACHINE CONTROL

Mnemonic

ACALL

LCALL

RET

RETI

AJMP

LJMP

SJMP

JMP

JZ

JNZ

JC

JNC

JB

JNB

JBC

CJNE

CJNE

CJNE

CJNE

DJNZ

DJNZ

NOP

Description

addr11

addr16

Bytes Cycles

Absolute subroutine call

Long subroutine call

Return from subroutine

Return from interrupt

addr11

Absolute Jump

addr16

Long Jump

rel

Short Jump (relative addr)

@A+DPTR

Jump indirect relative to DPTR

rel

Jump if A is Zero

rel

Jump if A is Not Zero

rel

Jump if Carry flag is set

rel

Jump if No Carry flag

bit,rel

Jump if direct Bit is set

bit,rel

Jump if direct Bit is Not set

bit,rel

Jump if direct Bit is set & Clear bit

A,direct,rel

Compare direct to A & Jump if Not Equal

A,#data,rel

Compare immediate to A & Jump if Not Equal

Rn,#data,rel Compare immed. to reg. & Jump if Not Equal

@Ri,#data,rel Compare immed. to ind. & Jump if Not Equal

Rn,rel

Decrement register & Jump if Not Zero

direct,rel

Decrement direct byte & Jump if Not Zero

No operation

2

3

1

1

2

3

2

1

2

2

2

2

3

3

3

3

3

3

3

2

3

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

1

Notes on data addressing modes

Rn

direct

@Ri

#data

#data16

bit

Working register R0-R7

128 internal RAM locations, any I/O port, control or status register

Indirect internal RAM location addressed by register R0 or R1

8-bit constant included in instruction

16-bit constant included in instruction

128 software flags, any I/O pin, control or status bit

Notes on program addressing modes

addr16 Destination address may be anywhere in 64-kByte program address space

addr11 Destination address will be within same 2-kByte page of program address

space as first byte of the following instruction

rel

8-bit offset relative to first byte of following instruction (+127, -128)

All mnemonics copyrighted Intel Corporation 1979

Information from Intel Application Note AP-69

DATA TRANSFER

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOVC

MOVC

MOVX

MOVX

MOVX

MOVX

PUSH

POP

XCH

XCH

XCH

XCHD

Mnemonic

Вам также может понравиться

- Engineering Service Revenues World Summary: Market Values & Financials by CountryОт EverandEngineering Service Revenues World Summary: Market Values & Financials by CountryОценок пока нет

- Building Inspection Service Revenues World Summary: Market Values & Financials by CountryОт EverandBuilding Inspection Service Revenues World Summary: Market Values & Financials by CountryОценок пока нет

- Asembbly Operation & Sintax Program Arithmetic Operations Mnemonic Description Bytes CyclesДокумент6 страницAsembbly Operation & Sintax Program Arithmetic Operations Mnemonic Description Bytes CyclesArief HamidОценок пока нет

- Phu Luc 3 Tom Tat Tap Lenh Vi Dieu Khien MCS-51 - Smith.N StudioДокумент4 страницыPhu Luc 3 Tom Tat Tap Lenh Vi Dieu Khien MCS-51 - Smith.N StudioSmith Nguyen StudioОценок пока нет

- Atmel 8051 MCU Instruction SetДокумент3 страницыAtmel 8051 MCU Instruction SetBlack DragonОценок пока нет

- Instruction Set of 8051 MicrocontrollerДокумент5 страницInstruction Set of 8051 MicrocontrollerSubhajit Chakraborty50% (2)

- 8051 Instruction Set SummaryДокумент2 страницы8051 Instruction Set SummaryBertold Van den BerghОценок пока нет

- Instruction Sap 2Документ3 страницыInstruction Sap 2Ian RobisoОценок пока нет

- MCU Instruction Set ClassificationДокумент13 страницMCU Instruction Set ClassificationKrapa Sai PraveenОценок пока нет

- 8051 Instruction Set Summary - AtmelДокумент4 страницы8051 Instruction Set Summary - AtmelRaissan ChedidОценок пока нет

- Instruction Format 8051Документ26 страницInstruction Format 8051alex24arulОценок пока нет

- Architecture and Programming of 8051 MCU's: Chapter 3: The 8051 Instruction SetДокумент90 страницArchitecture and Programming of 8051 MCU's: Chapter 3: The 8051 Instruction SetebinОценок пока нет

- 8051 Instruction SetДокумент2 страницы8051 Instruction SetMaheswari VijayakumarОценок пока нет

- Arithmetic, logical and data transfer instructions for 8051 microcontrollerДокумент3 страницыArithmetic, logical and data transfer instructions for 8051 microcontrollerAman MohantyОценок пока нет

- Addressing Modes and Instruction Set of 8051 MicrocontrollerДокумент48 страницAddressing Modes and Instruction Set of 8051 MicrocontrollerJibu JoseОценок пока нет

- 8051 Instruction SetДокумент50 страниц8051 Instruction Setkapil singhОценок пока нет

- Intel 8051 Instruction SetДокумент55 страницIntel 8051 Instruction SetRakesh GangwarОценок пока нет

- Instrucciones y Significados Del Mc51 en MicroprocesadoresДокумент3 страницыInstrucciones y Significados Del Mc51 en Microprocesadoresjavier hernandezОценок пока нет

- Architecture and programming of 8051 MCU's instruction setДокумент178 страницArchitecture and programming of 8051 MCU's instruction setezerobert56_86874258Оценок пока нет

- CJ Instrucoes 8051Документ6 страницCJ Instrucoes 8051Luz Do Mundo PijamasОценок пока нет

- Arithmetic Instructions Mnemonics Description Bytes Instruction CyclesДокумент3 страницыArithmetic Instructions Mnemonics Description Bytes Instruction CycleschiradonideepakОценок пока нет

- 8051 Instruction SetДокумент2 страницы8051 Instruction SetMohd Zamri IbrahimОценок пока нет

- 8051 Microcontroller Lab Manual 38 CharsДокумент54 страницы8051 Microcontroller Lab Manual 38 Charstjdandin1Оценок пока нет

- Types of Instructions in 40 CharactersДокумент5 страницTypes of Instructions in 40 Charactersarul0% (1)

- Opcodes: Products Download Events Support VideosДокумент3 страницыOpcodes: Products Download Events Support VideosSefu ThakurОценок пока нет

- Mejores PracticasДокумент9 страницMejores Practicasjerry3128Оценок пока нет

- 8080 Assembly Language MnemonicsДокумент3 страницы8080 Assembly Language MnemonicsDavid StaudacherОценок пока нет

- 8051 Notes 3rd Unit PDFДокумент36 страниц8051 Notes 3rd Unit PDFfwefОценок пока нет

- MCS-51 Instruction: Arithmetic OperationsДокумент3 страницыMCS-51 Instruction: Arithmetic OperationsAgus GunawanОценок пока нет

- Arithmetic OperationsДокумент2 страницыArithmetic OperationsRoselee Ann MontevirgenОценок пока нет

- M @-51 Instruction Set: Programmer'SДокумент7 страницM @-51 Instruction Set: Programmer'Swen_galsОценок пока нет

- 4 ThunitДокумент5 страниц4 ThunitJawaharsantosh GundapaneniОценок пока нет

- Introduction To 8085 MPДокумент16 страницIntroduction To 8085 MPDeepikaОценок пока нет

- Instruction SetДокумент22 страницыInstruction SetmeghaОценок пока нет

- Bahasa Assembly 1 (Compatibility Mode)Документ29 страницBahasa Assembly 1 (Compatibility Mode)itmyОценок пока нет

- 8051 Instruction Set GuideДокумент2 страницы8051 Instruction Set GuideGnanasundaram ChinnarajuОценок пока нет

- Instruction Set in 8051 MicrocontrollerДокумент7 страницInstruction Set in 8051 MicrocontrollerAjnamol N RОценок пока нет

- Parallel-In, Parallel-Out, Universal Shift RegisterДокумент12 страницParallel-In, Parallel-Out, Universal Shift Registerawa buayaОценок пока нет

- 8051 Instruction Set: Data Moving or Handling InstructionsДокумент3 страницы8051 Instruction Set: Data Moving or Handling InstructionsDHANANJAY POPAT MANEОценок пока нет

- Microcontroller Instruction Set: Subject: Microcontroller and Embeded System Class: 5, Ece Presented byДокумент73 страницыMicrocontroller Instruction Set: Subject: Microcontroller and Embeded System Class: 5, Ece Presented byLavanya VallbhareddyОценок пока нет

- V V V V V V V V VVV V V V V V V V VVV VVV V V VV V V V V V V V V V V V V !V"Документ9 страницV V V V V V V V VVV V V V V V V V VVV VVV V V VV V V V V V V V V V V V V !V"Manjunatha AcОценок пока нет

- Instruction SetДокумент18 страницInstruction SetGirl OnFireОценок пока нет

- 8051 Assembly LanguageДокумент39 страниц8051 Assembly LanguagemanvithbОценок пока нет

- ALU, Logic Instructions & Program FundamentalsДокумент62 страницыALU, Logic Instructions & Program FundamentalsColesha BarukaОценок пока нет

- Opcodes: The Following Table Lists The 8051 Instructions by HEX CodeДокумент3 страницыOpcodes: The Following Table Lists The 8051 Instructions by HEX CodeVijay VermaОценок пока нет

- Shift Register, Parallel-In, Serial-OutДокумент11 страницShift Register, Parallel-In, Serial-OutAwa StelkОценок пока нет

- 8051 Microcontroller Instruction Set TableДокумент4 страницы8051 Microcontroller Instruction Set TableBalaji KannanОценок пока нет

- 09 Assembly ExampleДокумент16 страниц09 Assembly ExampleKavyashree JamadagniОценок пока нет

- Chapter 3 The 8051 Instruction Set - Architecture and Programming of 8051 MCU - MikroElektronikaДокумент55 страницChapter 3 The 8051 Instruction Set - Architecture and Programming of 8051 MCU - MikroElektronikadreamylove_tnОценок пока нет

- KPI monitoring of network performanceДокумент15 страницKPI monitoring of network performancefarhanhhh100% (1)

- ATtiny24/44/84 Instruction Set SummaryДокумент2 страницыATtiny24/44/84 Instruction Set SummaryRajsekhar NagОценок пока нет

- Shift Sins OutДокумент11 страницShift Sins Outawa buayaОценок пока нет

- Opcodes PrabhaДокумент2 страницыOpcodes PrabhaDhivya Ad A DОценок пока нет

- 8051 OpcodeДокумент4 страницы8051 OpcodeGokulakrishnan100% (1)

- Transfer string data from code to RAMДокумент10 страницTransfer string data from code to RAMAditya KulkarniОценок пока нет

- Controlled Assesment Little Man ComputerДокумент18 страницControlled Assesment Little Man Computeribrahimelakkad100% (1)

- 8051 Instruction Set: FacebooktwitterlinkedinredditpinterestshareДокумент13 страниц8051 Instruction Set: FacebooktwitterlinkedinredditpinterestshareManjunath KV Assistant Professor (CSE)Оценок пока нет

- Service Location Workorder Number Cust Class Cust NameДокумент12 страницService Location Workorder Number Cust Class Cust NameSonia VermaОценок пока нет

- Architectural Service Revenues World Summary: Market Values & Financials by CountryОт EverandArchitectural Service Revenues World Summary: Market Values & Financials by CountryОценок пока нет

- Drafting Service Revenues World Summary: Market Values & Financials by CountryОт EverandDrafting Service Revenues World Summary: Market Values & Financials by CountryОценок пока нет

- Module6 - 7 Segment InterfaceДокумент12 страницModule6 - 7 Segment InterfaceVishal Gudla NagrajОценок пока нет

- Instruction Set SummaryДокумент5 страницInstruction Set SummaryAg CristianОценок пока нет

- Microcontroller Basics and ProgrammingДокумент92 страницыMicrocontroller Basics and ProgrammingVishal Gudla NagrajОценок пока нет

- Module5 - Stepper Motor InterfaceДокумент16 страницModule5 - Stepper Motor InterfaceVishal Gudla NagrajОценок пока нет

- 8453Документ18 страниц8453Vishal Gudla NagrajОценок пока нет

- Module 3 - LCD InterfaceДокумент12 страницModule 3 - LCD InterfaceVishal Gudla NagrajОценок пока нет

- Embedded C vs Assembly Language: Advantages and DisadvantagesДокумент5 страницEmbedded C vs Assembly Language: Advantages and DisadvantagesVishal Gudla NagrajОценок пока нет

- Module4 - DC Motor InterfaceДокумент16 страницModule4 - DC Motor InterfaceVishal Gudla NagrajОценок пока нет

- Module2 Led InterfaceДокумент5 страницModule2 Led InterfaceVishal Gudla NagrajОценок пока нет

- Microcontroller 8051Документ42 страницыMicrocontroller 8051om18sahuОценок пока нет

- Embedded C Programming With 8051: ObjectivesДокумент73 страницыEmbedded C Programming With 8051: ObjectivesyogeeshaОценок пока нет

- What Is Microcontroller?Документ119 страницWhat Is Microcontroller?Vishal Gudla NagrajОценок пока нет

- Microcontroller NPДокумент55 страницMicrocontroller NPVishal Gudla NagrajОценок пока нет

- Internal Interface ProgrammingДокумент42 страницыInternal Interface ProgrammingVishal Gudla NagrajОценок пока нет

- 8051 Assembly Language Programming: ©2009, CE DepartmentДокумент47 страниц8051 Assembly Language Programming: ©2009, CE DepartmentVishal Gudla NagrajОценок пока нет

- 8051 Tutorial by (Craig Steiner)Документ29 страниц8051 Tutorial by (Craig Steiner)Kaumudi TunuguntlaОценок пока нет

- 8051 Assembly Language ProgrammingДокумент51 страница8051 Assembly Language ProgrammingVishal Gudla NagrajОценок пока нет

- 8051 2Документ61 страница8051 2Harshad LokhandeОценок пока нет

- GNJDДокумент29 страницGNJDNagi Reddy BobbaliОценок пока нет

- 8051 ContentsДокумент2 страницы8051 ContentsVishal Gudla NagrajОценок пока нет

- 8051 Programming in CДокумент25 страниц8051 Programming in CVishal Gudla NagrajОценок пока нет

- 8051 Programming in CДокумент25 страниц8051 Programming in CVishal Gudla NagrajОценок пока нет

- 120v 8-Circuit Switching RiserДокумент1 страница120v 8-Circuit Switching RiserVishal Gudla NagrajОценок пока нет

- Elektor 1988 02Документ64 страницыElektor 1988 02M.Nadeem Ullah KhanОценок пока нет

- Servicemaster: Section M - Electronic NetworkДокумент9 страницServicemaster: Section M - Electronic NetworkmorusОценок пока нет

- P Winning Submission: Atroll U.S. Patent 8,209,411Документ11 страницP Winning Submission: Atroll U.S. Patent 8,209,411Jennifer M GallagherОценок пока нет

- OS MCQ Set 5Документ20 страницOS MCQ Set 5Sudhanshu Singh100% (1)

- Crack Mitsubishi PLC PasswordsДокумент4 страницыCrack Mitsubishi PLC PasswordsshaniimranОценок пока нет

- C++ Programming Guide for Government CollegeДокумент11 страницC++ Programming Guide for Government CollegeMUHAMMAD SALEEM RAZAОценок пока нет

- Intermec pc43t Pc43ta101eu302 User ManualДокумент3 страницыIntermec pc43t Pc43ta101eu302 User ManualAdrian Aguilar TapiaОценок пока нет

- Nor Nand Flash GuideДокумент9 страницNor Nand Flash GuidejvgediyaОценок пока нет

- Microsoft Student AdvantageДокумент7 страницMicrosoft Student AdvantageMohammedHajОценок пока нет

- WinCC Flexible 2008 Communication With PLC Omron PDFДокумент40 страницWinCC Flexible 2008 Communication With PLC Omron PDFthanh_cdt01Оценок пока нет

- Update Game Code for S.A.M. System MachinesДокумент2 страницыUpdate Game Code for S.A.M. System MachinesZoran KovacevicОценок пока нет

- Thuyet Trinh CEA201Документ5 страницThuyet Trinh CEA201Tùng TrịnhОценок пока нет

- CompTIA A+ Core 1 (220-1101) ToC and Quiz QuestionsДокумент149 страницCompTIA A+ Core 1 (220-1101) ToC and Quiz Questionsalankros776Оценок пока нет

- MagicEyes Manual ENG (Mv.9.9.2)Документ108 страницMagicEyes Manual ENG (Mv.9.9.2)gsicm2Оценок пока нет

- Esx DatasheetДокумент6 страницEsx DatasheetJuan_Pablo_Agu_1041Оценок пока нет

- Tomson 32LB220B4 2Документ83 страницыTomson 32LB220B4 2lust1Оценок пока нет

- Tejas Micro 1 RTU Technical ManualДокумент110 страницTejas Micro 1 RTU Technical ManualAlex ProchotОценок пока нет

- 3ADR010121, 14, en - US, CAA-Merger-2Документ1 319 страниц3ADR010121, 14, en - US, CAA-Merger-2Jose Luis Manso LoredoОценок пока нет

- Vikta102 Ecl Modbus OpcДокумент10 страницVikta102 Ecl Modbus OpcTobias AngererОценок пока нет

- Fastest switch for demanding setups with 40G ports (CRS326-24S+2Q+RMДокумент3 страницыFastest switch for demanding setups with 40G ports (CRS326-24S+2Q+RMHeri PurwantoОценок пока нет

- XK 3 y ManualДокумент36 страницXK 3 y ManualAndreas BangОценок пока нет

- Slot10 11 CH06 ExternalMemory 50 SlidesДокумент52 страницыSlot10 11 CH06 ExternalMemory 50 Slidestuan luuОценок пока нет

- Session Plan COC 1Документ6 страницSession Plan COC 1Katty Cedro Dela CruzОценок пока нет

- SBC 81822Документ1 страницаSBC 81822Asep KurniawanОценок пока нет

- NAND Vs NOR Flash Memory Technology Overview Read Write Erase Speed For SLC MLC Semiconductor Consulting ExpertДокумент4 страницыNAND Vs NOR Flash Memory Technology Overview Read Write Erase Speed For SLC MLC Semiconductor Consulting ExpertvarunmrОценок пока нет

- HP - Verification of Authentic HP Memory ModulesДокумент6 страницHP - Verification of Authentic HP Memory ModulesRyan BelicovОценок пока нет

- HEGCU-4 Operating InstructionДокумент17 страницHEGCU-4 Operating InstructionAntonio Mauricio Salomon MedinaОценок пока нет

- EC303 Lab2 StudentДокумент7 страницEC303 Lab2 StudentZahir ZabidiОценок пока нет