Академический Документы

Профессиональный Документы

Культура Документы

J Fet Final

Загружено:

Hans Huaranga LindoОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

J Fet Final

Загружено:

Hans Huaranga LindoАвторское право:

Доступные форматы

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

INFORME

DE

CIRUITOS

ELECTONICOS

JFET EN AC

OBJETIVOS:

-Analizar el comportamiento del transistor FET en circuitos de

polarizacin.

-A partir de las mediciones obtenidas, comparar los resultados

tericos con los resultados prcticos.

-|Utilizar

herramientas

de

simulacin

para

analizar

el

comportamiento de los circuitos implementados.

I. MARCO TERICO:

En los transistores bipolares, una pequea corriente de entrada (corriente

de base) controla la corriente de salida (corriente de colector); en los casos

de los FET, es un pequeo voltaje de entrada que controla la corriente de

salida.

La corriente que circula en la entrada es generalmente despreciable

(menos de un pico amperio). Esto es una gran ventaja, cuando la seal

proviene de un dispositivo tal como un micrfono de condensador o un

transductor pieza elctrico, los cuales proporcionan corrientes

insignificantes.

Los FETs, bsicamente son de dos tipos:

El transistor de efecto de campo de Juntura o JFET.

El transistor de efecto de campo con compuerta aislada o IGFET,

tambin conocido como semiconductor de xido de metal, MOS, o

simplemente MOSFET.

El analisis de ca de una configuracion del JFET requiere el desarrollo de un

modelo de ca de seal pequea para el JFET. Un componente importante

LAB.DE CIRCUITOS ELECTRONICOS I J FET

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

del modelo de ca reflejara el hecho de que un voltaje de ca aplicado a las

terminales de entrada de la compuerta a la fuente controlara el nivel de

corriente del drenaje a la fuente

LAB.DE CIRCUITOS ELECTRONICOS I J FET

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

AMPLIFICADOR EN FUENTE COMUN

Un amplificador en fuente comn es aquel en el que se aplica una seal de

entrada de CA a la Compuerta y la seal de salida de CA se toma de la

terminal del drenador. La terminal de fuente es Comn tanto para la seal de

entrada como para la de salida. Las configuraciones bsicas para este

Amplificador pueden incluir un resistor de fuente RS; o dos resistores Rs en

serie (RS=RS1+RS2), donde Slo uno de ellos cuenta con un capacitor en

derivacin (conectado en paralelo a este); o puede ser una

Configuracin donde RS=0. Un ejemplo de este tipo de amplificador que

utiliza dos resistores RS se Ilustra en la Figura 2. El circuito utiliza un JFET

canal N polarizado mediante un divisor de voltaje. Si Este circuito se modifica

de tal forma que R1= (circuito abierto), entonces la polarizacin del

Amplificador cambia a la de un JFET autopolarizado. La resistencia de carga

RL as como la fuente de Seal de CA vs se encuentran acoplados a la red de

polarizacin mediante capacitores (denominados Capacitores de

acoplamiento).

LAB.DE CIRCUITOS ELECTRONICOS I J FET

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

Anlisis de CD. El circuito que se ilustra en la Figura 3(a) muestra el

circuito equivalente de CD para el amplificador fuente comn de la Figura 2.

En el anlisis de CD se considera la impedancia de los capacitores como

infinita de tal forma que estos actan como circuitos abiertos. Tambin la

red de polarizacin de la compuerta se ha simplificado mediante la

aplicacin del teorema de Thevenin, las ecuaciones para la red de la

compuerta se presentan enseguida.

La resistencia de compuerta es dada por: RG = R 1 || R2 . Generalmente

IGSS es muy pequea por lo que para efectos prcticos se considera como

IGSS=0, el resistor RG mantiene a la compuerta en aproximadamente VGG

volts de CD. VGG se obtiene aplicando un divisor de voltaje:

En el caso de un red de autopolarizacin donde R1=, las ecuaciones son

RG=R2 y VGG=0V. El anlisis de la malla compuerta-fuente arroja la

ecuacin:

De esta relacin se despeja el voltaje VGS y se sustituye en la ecuacin de

Shockley:

LAB.DE CIRCUITOS ELECTRONICOS I J FET

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

Anlisis de CA. La Figura 4 muestra el circuito equivalente de CA para el

amplificador fuente comn que se ilustra en la Figura 2. Para obtener este

circuito se consideran los capacitores en corto circuito al

Igual que la fuente de CD. Enseguida se reemplaza el modelo simplificado

del JFET mostrado en la Figura 1(b).

Las ecuaciones para el clculo de la ganancia de voltaje, ganancia

de corriente, resistencia de Entrada y resistencia de salida se

presentan a continuacin.

LAB.DE CIRCUITOS ELECTRONICOS I J FET

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

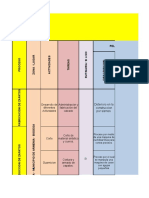

*SIMULACION EN PROTEUS

DISEO 1

Divisor de voltaje

+12v

R1

R2

6.8M

3.3K

D= 3.34 mA

I

Q1

V =12

2N4222A

1

=1.54

6.8+1

R4(2)

I=0.00334903

R3

1M

R4

GS= 7.34

V

2.2K

RG =0.87 M

Hallando

gm=

gm

2.5

7.34

1

=0.026

8

8

LAB.DE CIRCUITOS ELECTRONICOS I J FET

FIEE-

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

A v =(0.26)

3.3

1+2.2(0.026)

A v =0.81

A i=(0.026)

0.87 M

1+2.2(0.026)

A i=0,O 21.103

DISEO 2

LAB.DE CIRCUITOS ELECTRONICOS I J FET

FIEE-

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

I D =1.17

+12v

R5

C2

10k

GS= 2.57

V

100uF

C1

Q2

2N4222A

P=8

V

10nF

C1(1)

R6

R7

10k

10k

C3(2)

I=0.00117697

DSS= 5 mA

I

C3

100uF

gm=

2.2

1+2.2( 0.84)

2.2

1+2.2(0.84 )

A v =(0.84)

v =0.64

A

A i=(0.84)

i=0.64

A

LAB.DE CIRCUITOS ELECTRONICOS I J FET

2.5

2.57

1

=0.84

8

8

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

SIMULANDO LA SEAL

+12v

R2

3k

C3

A

100uF

C1(1)

Q?

C1

2N4222A

D

10nF

R1

10k

C2

R4

3k

LAB.DE CIRCUITOS ELECTRONICOS I J FET

100uF

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

DE FORMA EXPERIEMENTAL

LAB.DE CIRCUITOS ELECTRONICOS I J FET

FIEE-

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

LAB.DE CIRCUITOS ELECTRONICOS I J FET

FIEE-

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

PREGUNTAS

POR QUE RAZON SOLO SE TOMA EN CUENTA LA CORRIENTE

ID ?

La unin que se establece entre los cristales del graduador y el surtidor se

comporta como si fuese un diodo de silicio polarizado inversamente, por lo que

la corriente inversa que fluye por el graduador es muy pequea, prcticamente

despreciable. sta es la razn por la que slo se tiene en cuenta una corriente,

la ID.

QUAPLICACIONES TIENE EL JFET?

El JFET posee bastantes aplicaciones, como son:

interruptores analgicos, multiplexores, control

automtico de ganancia "CAG" en receptores de

radio, amplificadores de pequea seal en

receptores de radio y TV, troceadores o choppers,

etc.

En la figura de la izquierda, se muestra un ejemplo

de interruptor analgico con un JFET.

Si a este circuito se le aplica una tensin VGS=0, el

transistor entrar en saturacin y se comportar

como un interruptor cerrado. Por otro lado, si la

tensin aplicada es VGS=VGS(apag), el transistor se

pondr en corte y actuar como un interruptor abierto.

Cuando se utiliza un JFET como interruptor, se le hace trabajar nicamente en

dos estados, corte y saturacin.

CUALES SON LAS VENTAJAS Y DESVENTAJAS DE UN JFET?

-Los JFET generan menos ruido que los BJT

-Por lo general son ms fciles de fabricar que los BJT

LAB.DE CIRCUITOS ELECTRONICOS I J FET

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

-Reaccionan como resistores variables controlados por voltaje para valores

pequeos de voltaje de drenaje a fuente

-La elevada impedancia de los FET permite que estos almacenen carga por

tiempo

suficientemente

largo

para

usarlos

como

elementos

de

almacenamiento

-Usualmente exhiben una pobre respuesta de frecuencia debido a un alta

capacitancia de entrada

-Algunos exhiben pobre linealidad

COMO ACTUA UN JFET COMO RESISTENCIA VARIABLE?

Se puede polarizar un JFET o en la regin activa o en la regin hmica. Los JFET

a menudo se polarizan en la regin hmica para usarlos como un resistor

variable controlado por voltaje. El voltaje de control es VGS y determina su

resistencia variando el punto Q. Para polarizar un JFET en la regin hmica, la

recta de carga de cd debe cortar la curva caracterstica en la regin hmica,

como ilustra la figura. Para hacer esto en una forma que permita a VGS

controlar RDS, la corriente en cd de saturacin se ajusta a un valor mucho

menor que IDSS, de modo que la recta de carga corte la mayora de las curvas

caractersticas en la regin hmica, como se ilustra. En este caso,

QUE ES LA REGION DE OPERACIN?

Esta hoja de especificaciones y la curva definida por los niveles de

estrangulamiento en cada nivel

LAB.DE CIRCUITOS ELECTRONICOS I J FET

UNIVERSIDAD NACIONAL DEL CALLAO

2015A

FIEE-

de VGS definen la regin de operacin de amplificacin lineal en las

caractersticas de drenaje como se muestra en la figura 6.24. La regin hmica

define los valores mnimos permisibles de

VDS en cada nivel de VGS y VDS mx especifica el valor mximo para este

parmetro. La corriente de saturacin IDSS es la corriente de drenaje mxima y

el nivel de disipacin de potencia mximo define la curva trazada como se

describi para transistores BJT. La regin sombreada resultante es la regin de

operacin normal para un diseo de amplificador.

*CONCLUSIONES

-Se aprecia que la seal de salida se reduce a comparacin de la de entrada.

-La apreciacin e la seal reducida se corrobora tanto experimental mente

como en la simulacin en proteus como se observa en las imgenes anteriores

LAB.DE CIRCUITOS ELECTRONICOS I J FET

Вам также может понравиться

- Matriz Riesgos GT 45Документ16 страницMatriz Riesgos GT 45AlejandroÁngel100% (1)

- Trabajo Final-Gestion de ProyectosДокумент29 страницTrabajo Final-Gestion de ProyectosHans Huaranga LindoОценок пока нет

- DINSTARДокумент2 страницыDINSTARHans Huaranga LindoОценок пока нет

- 01.27.20 Catalogo Grill Store La Tienda de Mr. Grill 2020 PDFДокумент93 страницы01.27.20 Catalogo Grill Store La Tienda de Mr. Grill 2020 PDFHans Huaranga LindoОценок пока нет

- Ficha de InscripcionДокумент1 страницаFicha de InscripcionHans Huaranga LindoОценок пока нет

- S1 ArquitectosДокумент9 страницS1 ArquitectosHans Huaranga LindoОценок пока нет

- PR5 EcdiferencialesДокумент11 страницPR5 EcdiferencialesHans Huaranga LindoОценок пока нет

- 2 Campo Eléctrico-1Документ4 страницы2 Campo Eléctrico-1Abril GardeniaОценок пока нет

- HPLCДокумент29 страницHPLCbaneador500100% (1)

- Libro Dig Astrofísica - Cuerpos CelestesДокумент153 страницыLibro Dig Astrofísica - Cuerpos CelestesFernando BenottiОценок пока нет

- Molienda 150124022603 Conversion Gate01Документ43 страницыMolienda 150124022603 Conversion Gate01Carlos Erik Escobar RiquelmeОценок пока нет

- Enlaces Con AnimacionДокумент31 страницаEnlaces Con AnimacionVanessaSolarОценок пока нет

- Relajacion ExponencialДокумент5 страницRelajacion ExponencialMateoalias NaniОценок пока нет

- AtropellosДокумент2 страницыAtropellosHannessy NicolasОценок пока нет

- RodamientosДокумент36 страницRodamientosJuan AyalaОценок пока нет

- FeedBack Lab3 (Péndulo Invertido)Документ5 страницFeedBack Lab3 (Péndulo Invertido)Jason S. BastidasОценок пока нет

- EL PÉNDULO y Sus Usos. Venti.Документ12 страницEL PÉNDULO y Sus Usos. Venti.Olga AmarantaОценок пока нет

- Calculo VI Ejercirtario 6 2do PDFДокумент3 страницыCalculo VI Ejercirtario 6 2do PDFOscar AmarillaОценок пока нет

- 5Документ6 страниц5Julio Miranda AlarconОценок пока нет

- Grados de LibertadДокумент25 страницGrados de Libertaduriel1293100% (1)

- Interruptor Tanque MuertoДокумент17 страницInterruptor Tanque MuertoMartin Garcia AtienciaОценок пока нет

- S10 LONGITUD DE ARCO-CENTROIDE-TrabajoДокумент4 страницыS10 LONGITUD DE ARCO-CENTROIDE-TrabajoJonathan Vigil CenturionОценок пока нет

- Motores de Corriente Directa Fuerza Contraelectromotriz - UnlockedДокумент19 страницMotores de Corriente Directa Fuerza Contraelectromotriz - UnlockedCarlOs OzïlОценок пока нет

- Solucion Eva 1 Clave 1 PDFДокумент3 страницыSolucion Eva 1 Clave 1 PDFCarlos PleitezОценок пока нет

- Laboratorio 7Документ6 страницLaboratorio 7Abel Morillo MinayaОценок пока нет

- Ventanas de AluminioДокумент31 страницаVentanas de Aluminioomar minaya100% (2)

- Vectores 2Документ42 страницыVectores 2Edgar Enrique Pérez Camacho75% (4)

- 20172SMatDeber5 PDFДокумент13 страниц20172SMatDeber5 PDFJuan Carlos Garcia EstrellaОценок пока нет

- Clase 3 InstrumentacionДокумент70 страницClase 3 InstrumentacionArturo Tapia100% (1)

- Pre Reporte 5Документ12 страницPre Reporte 5Alfredo AnguianoОценок пока нет

- Inf Practica 2 Reacciones QuimicasДокумент15 страницInf Practica 2 Reacciones QuimicasFernando Cota GarciaОценок пока нет

- El Carbono 7 GuionДокумент2 страницыEl Carbono 7 GuionMauricio Nahuel MoryОценок пока нет

- Informe Calculo 3Документ15 страницInforme Calculo 3Carlos Alberto Periche CuroОценок пока нет