Академический Документы

Профессиональный Документы

Культура Документы

A Low Cost Power Amplifier For 5-GHz W-LAN Applications

Загружено:

Ham Radio HSMMОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

A Low Cost Power Amplifier For 5-GHz W-LAN Applications

Загружено:

Ham Radio HSMMАвторское право:

Доступные форматы

A Low Cost Power Amplifier for 5-GHz

W-LAN Applications (Invited Paper)

A. Scuderi, F. Carrara and G. Palmisano

STMicroelectronics, Stradale Primosole 50,95121, Catania, Italy

2Universitl di Catania, Facolti di Ingegneria, DIEES, Viale A. Doria 6, 95125, Catania, Italy

antonino.scuderi@st.com, fcarrara@diees.unict.it,gpalmisano@diees.unict.it

efficiency (PAE)that leads to a short operating time for the

mobile equipment.

Abstract- A monolithic 5-GHz RF linear power amplifier for WLAN IEEE802.11a applications was integrated using a very low

cost 35-GHz-fr bipolar process. The process adopts a selective

germanium implant technique to optimize the base profde. The

two-stage power amplifier exhibits a 8-dB power gain, a 27-dBm

PldB and a 27% power added efficiency (PAE). Thanks to an

optimized linealization technique the power amplifier is able to

comply with the stringent error vector magnitude (EVM)

requirement of the standard up to 23-dBm output power with an

IEEE802.11a 54-Mbiffs input signal.

In order to extend the operating time, a proper biasing

technique has to be used as will be discussed in Section HI.

KeywordsSiGe: bipolar: power amplifier: PAE; Em:RF: W-

This work presents a very low cost silicon-germanium

bipolar linear PA that exhibits a 27-dBm P L a , 8-dB small

signal gain, 29dBm saturated output power and 27% PAE at

5.25 GHz and 3.3-V supply voltage. With an IEEE802.11a

54-MbiVs input signal, the circuit is able to deliver an output

power as high as 23 dBm.

LAN: IEEE802.11a

I.

11. SlGE IMPLANTED TECHNOLOGY

The process adopts a selective germanium implant

technique. The implantation is used on an existing low cost

host process which makes available additional devices for

complex function design. Moreover, the implantation allows an

independent control of Ge dose and base profile.

INTRODUCTION

Wireless applications are capturing higher and higher

market share due to the request of mobility and flexibility bom

the end-users. The challenge is to implement attractive wireless

solutions in terms of integration, performance and costs. A

mass market perspective needs the use of very low cost

technologies capable of implementing complex functions. In

addition to cost, a basic issue of a wireless technology is the

capability to perform power amplification. This is mandatory

to integrate the RF front-end transceiver including the PA in a

single chip. Recently, this concept has been attracting

increasing attention for GSM/DCS or WCDWCDMA2k

applications where BiCMOS/SiGe technologies are becoming

the most attractive ones. For IEEE 802.11a WLAN

applications, integrated solutions have heen presented [I] and

stand-alone PAS reported [2] but they suffer from the high

production cost of the technologies. This paper shows a power

amplifier for the IEEE802.1 la standard, which is integrated in

a very low cost silicon germanium bipolar process.

The optimization of the base profile enables the design of

bipolar transistors with very low base transit time. A

cross-section of a typical implanted SiGe transistor is depicted

in Fig. 1.

The IEEE802.1 l a standard employs orthogonal frequency

division multiplexing modulation providing high data rate (54

Mb/s) with very low inter-symbol interference and a good

multi-path fading immunity. However the OFDM signal shows

very high peak-to-average power ratio that leads to a stringent

linearity requirement for the PA. The 54 Mb/s configuration is

the most critical for the fulfillment of the EVM requirement

which is as low as 5.6%.

Figure 1. Simplified SiGc BIT emss section

Due to the high peak-to-average ratio (higher than 7 dB

[3]), a deep power back-off has to be used to avoid peak

clipping. As a consequence, the PA exhibits poor power-added

A SEM photo is shown in Fig. 2. The main features of the

process are: thin centura epi layer (0.8 to l.Opn), enhanced

trench for improved F

E isolation, optimized double implanted

129

2004 IEEE CSIC Digest

__

-~

--

In order to increase the breakdown voltage from 3 V to 4.3

V for a PA operating at 3.3 V the collector was optimized

while the fr was reduced to 35 GHz. This trade-off was

achieved adopting a collector implantation dose lower than the

standard one.

selective collector, self-aligned double-poly baselemitter

structure, ion implanted germanium, directly implanted base,

junction depth < 900 A, and an effective emitter width of 0.4

pm. Moreover, it features three AISiCu-metal layers, poly

resistors, and metal-insulator-metal capacitors (0.7 fF/pm2).

Comparison between host technology performance and

implanted SiGe BJT is summarized in Tab. I .

-~

Figure 2. SEM photo

--

---

Parameter

Host Tech

SiGe Technology

h m m (VCS= 0 v)

1 IO

132

BVCEO[VI

[GHz] @ V c b 2 V

22

44

fm [GHz] @ V c b 2 V

18

68

TF

fTm

IPS1

111.

THE LINEARIZATION

TECHNIQUE

Class-AB operation is suitable to achieve low current

consumption and optimum bias current level for minimum

third-order distortion [4]. As shown in Fig. 4, the IM3

characteristic for a Class-AB PA can roughly be divided into

two regions. Gain expansion is observed for low output power

levels (weak nonlinearity), whereas saturation of the output

voltage occurs when the output power is high (hard

nonlinearity). To take into account AMIAM and AMmM

effects in the weakly nonlinear region, the PA's distortion has

to be analyzed by the Volterra series approach. IM3 can be

minimized by sening optimum bias impedances at 2oC and

Am = 1 w2- w , 1, where wc is the camer frequency and Am is

the frequency spacing between the two input tones [SI.On the

other hand, in the hard distortion region IM3 can be minimized

by properly managing the sweet spot, i.e., by controlling the

compensation between the expansion and compression of the

power gain curve [6]. The addition of a diode linearizer to the

bias circuitry, allows tracking the variation of the power

transistor base-eminer voltage thereby enhancing the I-dB

compression point of the PA [7].

Weak

nonlinearity

i'

Hard

nonlinearity

Output power [dBm]

Figure 4. Thhird-order intermodulation dirtoltion versus output power

characteristic for a Class-AB PA.

N.

h,

-

0

0.1

Figure 3. /?and/."

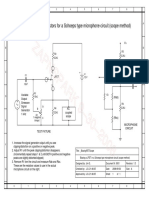

THE POWER AMPLIFIER

The proposed PA comprises 2 gain stages device and

exploits MIM capacitors, bond-wires and a spiral inductor with

pattemed ground shield to provide on-chip inter-stage and

input matching. In order to minimize the IM3, the optimization

of the base-band bias impedance was performed and an antiparallel junction at the base of the power transistor was used, as

shown in Fig. 5 . The bias circuit also allows a power control

. can be

function to be achieved through the voltage V C ~This

also used to control the quiescent current level of the power

amplifier thus optimizing the trade-off between efficiency and

linearity.

vmus collector current @ V c k 2 V

130

t vco

Fig. 8 shows the single-tone performance in terms of output

power and PAE. The PA exhibits a 27-dBm output

compression point, a 8-dB small-signal gain and a 29-dBm

saturated output power along with a 27% maximum PAE. This

was optimized with the PA operating close to the compression

point.

"cl

II

.....

Off-chip

matching

I

Figure 5. Simplified schematic of the power amplifier

V. EXPERIMENTAL

RESULTS

A die photograph of the fabricated PA is shown in Fig. 6.

The chip size is 1.5 mm x 1.2 m. Ground planes and a large

number of emitter down-bonding wires were adopted to reduce

the parasitic inductance between the emitter of the transistor

and the extemal ground. Inter-matching network exploits a

monolithic circular inductor. In order to enhance the Q-factor,

the top and the second metal layer was used for spiral and

underpass, respectively. Moreover, radial panemed ground

shied was used to avoid detrimental effects due to induced

substrate currents [8].

The control curve of the PA is repolted in Fig. 9. The curve

represents the variation of the output compression point as a

function of the extemal control voltage VCNI..More than 30 dB

of power control was measured and the maximum slope of the

power control curve is lower than 100 d B N .

In Fig. 10 the PA performance under IEEE802.11a

excitation is presented. A bit rate of 54 Mbitls was set for the

input signal, representing the worst case with respect to

linearity requirements. In this case, EVM must be less than

5.6%. Measured EVM is below 3.5% up to a 22-dBm output

power level, whereas the 5.6% requirement is fulfilled up to

23 dBm.

In Fig. 11 the output spectrum, for 23-dBm output power, is

shown, demonstrating compliance with standard emission

mask specifications.

The chip was assembled in a 4 mm x 4 mm QFN 16-lead

plastic package and mounted on a 400-pm-thick FR4 substrate

which is shown in Fig. 7. The output matching network and

input SO-ohm line are highlighted.

The PA was operated under a 3.3 V supply voltage and the

operating frequency was set to 5.25 GHz. Extemal matching

was optimized to obtain the best trade-off between the

compression point and the gain.

Figure 7. Photograph of the testing bavd

30

i

m jol

27.5

25

~~

5 17.5

2

/',

28

L4

12 1

.=

2 4 6 8 101214 1 6 1 8 2 0 2 2 2 4 2 6

Pin Idem]

Figure 6. Die photograph

Figure 8. Output paw= and PAE v m w input power (Pin)

131

VI.

30

CONCLUSION

A MMIC PA was integrated using a very low cost bipolar

technology. The process adopts a base selective germanium

implant technique to optimize the base profile. The PA

includes an optimized bias network providing linearity

enhancement, shut-down and quiescent current regulation

functionalties. With an IEEE802. I la 54-MbiVs input signal,

the PA is capable o f delivering a linear output power of

23 dBm with a 27% PAE while complying with the standard

linearity requirements.

,

I

1 1.1 1.2 1.3 1.4 1.5 1.6 1.7 1.8 1.9 2

-5-1

Vcnt [VI

ACKNOWLEDGMENT

The authors would like to thank P. Ward and C. Alemanni,

STMicroelectronics, Catania, Italy, for help with technology

issues and A. Castorina, U. Lombard0 and C. Santagati,

STMicroelectronics, Catania, Italy, for assistance with

measurements.

Figure 9. Output power versus control voltage (V,)

REFERENCES

14

18

16

20

22

C-H Lee et al., .Broadband highly integrated LTCC front-end module

for EEE802.1 la WAN applications, E E E Mimowave Symposium

Digest, 2002 IEEE M T M htemationalvol.2 p 1045-1048

l i H.Kim, lo& H. Kim, Y.S. Noh and C. S. Park, A Low Quiosccnt

Current 3.3V Operation Linear MMlC Power Amplifier For 5 GHz

WLAN Applications,IEEE MTr-SDigert, pp. 867-870,2003.

N. Ngajikin, N. Fisal and S. K. Ywof, Pcak to average ratio in

WLAN-OFDM system, in Pmc. IEEE Noliowl Conference on

Telecommunication Technology, Malaysia, Jan. Z(H13,pp. 123-126.

M. lwamoto el al., Optimum bias conditions for linear broadband

InGaPIGaAs HBT power amplifiers, in IEEE MTr-S Inl. Microwove

Sy. Diz., June 2002, pp. 901-904.

V. Aparin and C. Persico, Effect of out-of-band terminations on

intwodulation distortion in comm-emitter cimuie. in IEEE MIT-S

Inl. Micmwove Symp. Dig.,lune 1999, pp. 977-980.

N. B. De CarvaBa, and 1. C. Pedro, Urge- and small-Sigmal IMD

behavior o f microwave power amplifiers. IEEE Tram. Microwove

Theory Tech., vol. 47, pp. 2364-2374, Dec. 1999.

Y. S. Noh and C. S. Park, PCSW-CDMA dual-band MMlC power

amplifier with a newly proposed linearizing bias circuit: IEEE J.

Solid-State Circuits, vol. 37, pp. 1096-1099, Sept. 2002.

A. Scuderi, T. Biondi, E. Ragonese, G. Palmisno, A Lumped Scalable

M d e l for Silicon Integrated Spiral Inductors, IEEE Tn. Cireuirs end

System,vol. 51, pp. 1203-1209,Iunc20M

24

Pout [dBm]

Figure IO. EVM YBNS Output power (54 Mbit OFDM input sigmal)

Ref 1x4 dBm

Pink

R i m 28 dB

LO9

dB/

10%

Hi 82

S3 FC

R

af):

flu

S0

cent*

lRaf BU 188 XHz

*mu

18 L H ~

Sws~o22.88 m (681 et$).

Figure 11. Output spechum at 23 dBm output channel power (Vcc=3.3 V)

132

Вам также может понравиться

- New Throughput Analysis of Long-Distance IEEE 802.11 Wireless Communication System For Smart GridДокумент6 страницNew Throughput Analysis of Long-Distance IEEE 802.11 Wireless Communication System For Smart GridHam Radio HSMMОценок пока нет

- MKG 0375 AR92xxEEPROMДокумент52 страницыMKG 0375 AR92xxEEPROMHam Radio HSMM100% (1)

- AREDN A High Speed Data NetworkДокумент5 страницAREDN A High Speed Data NetworkHam Radio HSMMОценок пока нет

- Mesh Networking and AREDNДокумент5 страницMesh Networking and AREDNHam Radio HSMMОценок пока нет

- Atheros CalibrationДокумент26 страницAtheros CalibrationHam Radio HSMMОценок пока нет

- A 5.25 GHZ SiGe Bipolar Power Amplifier For IEEE 802.11a Wireless LAN PDFДокумент4 страницыA 5.25 GHZ SiGe Bipolar Power Amplifier For IEEE 802.11a Wireless LAN PDFHam Radio HSMMОценок пока нет

- The Impact of Adjacent Channel Interference in Multi-Radio Systems Using IEEE 802.11Документ8 страницThe Impact of Adjacent Channel Interference in Multi-Radio Systems Using IEEE 802.11Ham Radio HSMMОценок пока нет

- High-Speed Wireless Networking in The UHF and Microwave BandsДокумент5 страницHigh-Speed Wireless Networking in The UHF and Microwave BandsHam Radio HSMMОценок пока нет

- Tactical Wi-Fi NetworksДокумент5 страницTactical Wi-Fi NetworksHam Radio HSMMОценок пока нет

- A 5.8 GHZ Low Noise Amplifier For Wireless LAN Applications in Silicon Bipolar TechnologyДокумент4 страницыA 5.8 GHZ Low Noise Amplifier For Wireless LAN Applications in Silicon Bipolar TechnologyHam Radio HSMMОценок пока нет

- The Design of Power Amplifier For 5.8 GHZ Wireless LAN Application Using GaAs SubstrateДокумент4 страницыThe Design of Power Amplifier For 5.8 GHZ Wireless LAN Application Using GaAs SubstrateHam Radio HSMMОценок пока нет

- AR93xx ART2 Reference Guide MKG-15527Документ140 страницAR93xx ART2 Reference Guide MKG-15527Ham Radio HSMMОценок пока нет

- The Myth of Non-Overlapping Channels Interference Measurements in IEEE 802.11Документ8 страницThe Myth of Non-Overlapping Channels Interference Measurements in IEEE 802.11Ham Radio HSMMОценок пока нет

- Fully Integrated Doherty Power Amplifiers For 5 GHZ Wireless-LANsДокумент4 страницыFully Integrated Doherty Power Amplifiers For 5 GHZ Wireless-LANsHam Radio HSMMОценок пока нет

- Improving The Performance of Wireless Systems Though Distributed Fault DiagnosisДокумент142 страницыImproving The Performance of Wireless Systems Though Distributed Fault DiagnosisHam Radio HSMMОценок пока нет

- Ath9k and Ath9k - HTC DebuggingДокумент4 страницыAth9k and Ath9k - HTC DebuggingHam Radio HSMMОценок пока нет

- Solving The Wireless Mesh Multi-Hop DilemmaДокумент14 страницSolving The Wireless Mesh Multi-Hop DilemmaHam Radio HSMMОценок пока нет

- MKG-0906-AR92xx MFG GuideДокумент66 страницMKG-0906-AR92xx MFG GuideHam Radio HSMMОценок пока нет

- MKG 1194 ARTReferenceДокумент40 страницMKG 1194 ARTReferenceHam Radio HSMMОценок пока нет

- High-Speed Multimedia Goes Beyond The Linksys WRT54GДокумент1 страницаHigh-Speed Multimedia Goes Beyond The Linksys WRT54GHam Radio HSMMОценок пока нет

- Atheros Client Utility Help: Model AR5BMB5Документ30 страницAtheros Client Utility Help: Model AR5BMB5Ham Radio HSMMОценок пока нет

- Setting Up A Mesh Network NodeДокумент5 страницSetting Up A Mesh Network NodeHam Radio HSMMОценок пока нет

- A 5.8 GHZ Fully-Integrated Power Amplifier For 802.11a WLAN SystemДокумент4 страницыA 5.8 GHZ Fully-Integrated Power Amplifier For 802.11a WLAN SystemHam Radio HSMMОценок пока нет

- Switchless Bi-Directional AmplifierДокумент4 страницыSwitchless Bi-Directional AmplifierHam Radio HSMMОценок пока нет

- Switch Less Bidirectional RF Amplifier For 2.4 GHZ Wireless Sensor NetworksДокумент7 страницSwitch Less Bidirectional RF Amplifier For 2.4 GHZ Wireless Sensor NetworksHam Radio HSMMОценок пока нет

- High-Speed Networking - Time To Net Its BenefitsДокумент2 страницыHigh-Speed Networking - Time To Net Its BenefitsHam Radio HSMMОценок пока нет

- Simple Yet Efficent-Transparent Airtime Allocation For TCP in Wireless Mesh NetworksДокумент12 страницSimple Yet Efficent-Transparent Airtime Allocation For TCP in Wireless Mesh NetworksHam Radio HSMMОценок пока нет

- Networking Without Wires - Radio Based TCPIPДокумент254 страницыNetworking Without Wires - Radio Based TCPIPHam Radio HSMMОценок пока нет

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (119)

- 4G LTE Drive Test IntroductionДокумент18 страниц4G LTE Drive Test IntroductionHari MuklasОценок пока нет

- What is Wi-Fi? Understanding Wireless Networking TechnologyДокумент2 страницыWhat is Wi-Fi? Understanding Wireless Networking Technologyamol0037Оценок пока нет

- Introduction to Data Communication & NetworkingДокумент43 страницыIntroduction to Data Communication & NetworkingNETHRA100% (1)

- Amatuer Radio 2Документ51 страницаAmatuer Radio 2sudyОценок пока нет

- A 23 GHZ Fast-Locking PLL Using Phase Error CompensatorДокумент5 страницA 23 GHZ Fast-Locking PLL Using Phase Error Compensatornayakadarsh2000Оценок пока нет

- Putian Antenna SpecificationДокумент109 страницPutian Antenna SpecificationMukesh Jung Thapa100% (1)

- Hamming Codes Correct Single Bit Errors in 7-Bit Code WordsДокумент3 страницыHamming Codes Correct Single Bit Errors in 7-Bit Code WordsanggaОценок пока нет

- Selecting JFET Bias Resistors For A Schoeps Type Microphone Circuit (Scope Method)Документ1 страницаSelecting JFET Bias Resistors For A Schoeps Type Microphone Circuit (Scope Method)Victor PastorОценок пока нет

- RFS APXV9RxxBДокумент2 страницыRFS APXV9RxxBPavelKuzovkinОценок пока нет

- Lab 1 Dipole Simulation Using HFSSДокумент17 страницLab 1 Dipole Simulation Using HFSSQuýHoàngОценок пока нет

- DB750X UserManualДокумент46 страницDB750X UserManualBob GageОценок пока нет

- Dual-band Omnidirectional Antenna SpecsДокумент2 страницыDual-band Omnidirectional Antenna SpecsGabi GabrielОценок пока нет

- PLL Serial MC145170 Instruction SetДокумент8 страницPLL Serial MC145170 Instruction SetStephen Dunifer100% (4)

- A Compact Circular-Ring Antenna For Ultra-Wideband ApplicationsДокумент6 страницA Compact Circular-Ring Antenna For Ultra-Wideband Applicationsameya1981Оценок пока нет

- An SDR Radio TelescopeДокумент15 страницAn SDR Radio TelescopekleephОценок пока нет

- DVB-S2 Advanced Modulation Satellite Tuner: FeaturesДокумент41 страницаDVB-S2 Advanced Modulation Satellite Tuner: Featurespicatchoof1Оценок пока нет

- Casio tv-1900bxm SMДокумент21 страницаCasio tv-1900bxm SMДмитрий АртюхОценок пока нет

- 4rth LectureДокумент10 страниц4rth LectureAHMED DARAJОценок пока нет

- Matlab ProjectДокумент25 страницMatlab ProjectSandeep ChopraОценок пока нет

- Difference Equations For FIR and IIR Filters: ObjectivesДокумент8 страницDifference Equations For FIR and IIR Filters: ObjectivesAldon JimenezОценок пока нет

- 2 5-GSMДокумент47 страниц2 5-GSMTanveer Akram100% (1)

- Technical Publications: Direction 2108264Документ34 страницыTechnical Publications: Direction 2108264Rogerio CastroОценок пока нет

- Imran Ahmad CV PunitДокумент4 страницыImran Ahmad CV Punitpuneetm27Оценок пока нет

- Type 1 Drawing Rosemount 5408 Radar Level Transmitter 2d PDF en 327202Документ5 страницType 1 Drawing Rosemount 5408 Radar Level Transmitter 2d PDF en 327202Javier EspinosaОценок пока нет

- ريهام خالد جوحي PskДокумент9 страницريهام خالد جوحي Pskريهام خالد جوحيОценок пока нет

- Service Manual: HCD-GX750/RG551/RX550Документ76 страницService Manual: HCD-GX750/RG551/RX550Andres Larenas OrtizОценок пока нет

- Akai AM-2200 PDFДокумент23 страницыAkai AM-2200 PDFMarcel KontakОценок пока нет

- Node performance counter summary guideДокумент1 099 страницNode performance counter summary guidetestato123Оценок пока нет

- Eletromagnetismo Hayt 8ed Solução Chapter 10Документ41 страницаEletromagnetismo Hayt 8ed Solução Chapter 10Sabrina FermanoОценок пока нет

- VHF Radio Direction FinderДокумент1 страницаVHF Radio Direction FinderPraveen HugarОценок пока нет