Академический Документы

Профессиональный Документы

Культура Документы

Reason Tool Docs

Загружено:

sivapothiАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Reason Tool Docs

Загружено:

sivapothiАвторское право:

Доступные форматы

REASON

Workpackage WP3

Testing and Design for Testability of SOC

Contents

I. Tools for defect oriented testing..............................................................................2

1. TTU_DOFSIM - Defect-Oriented Functional Fault Simulation tool.............3

2. TTU_MAFFAD - Mapping Functional Faults to Defects tool.........................4

3. TTU_DOFGEN - Defect-Oriented Test Generation tool .................................5

II. Tools for Built-In Self-Test analysis......................................................................6

1. TTU_SIMBIST - Simulation of Built-In Self-Test tool ....................................7

2. TTU_HYBCAN - Hybrid BIST Cost Analysis tool (script) .............................9

III. Tools for design error diagnosis.........................................................................10

1. TTU_DERRIN - Design Error Insertion tool..................................................11

2. TTU_PREDIA - Prediagnostic tool..................................................................12

3. TTU_TVECIN - Test Vector Insertion tool.....................................................13

4. TTU_ECRDCR - Encryption/Decryption tool................................................14

5. TTU_COMLIB - Common Library .................................................................15

IV. Tools for high level test generation ....................................................................16

1. Software tools for VHDL Design and Test Flow (CR3-TTU)........................16

2. TTU_VHDLDD VHDL to DD Converter for hierarchical test generation

..................................................................................................................................17

I. Tools for defect oriented testing

The new tools are extensions to the Turbo-Tester (TT) diagnostic tool set developed by TTU

in the frame of previous EC COPERNICUS projects SYTIC and VILAB. The TT tools are

handling logic level SAF faults. The new tools give the TT a new functionality to handle also

physical defects.

All the tools developed by TTU in WP3 use the formats and libraries of TT. Therefore this

deliverable does not embrace all the information and documentation necessary for running

these tools. The details are available at the Turbo Tester home page in the Web:

http://www.pld.ttu.ee/tt.

1. TTU_DOFSIM - Defect-Oriented Functional Fault Simulation tool

Tool acronym:

TTU_DOFSIM

Tool destination:

The goal of the tool is to simulate functional faults for logic level

variables and to create the functional fault table.

Tool description:

The working principle of the tool is based on using a new functional

fault model which is a new concept for uniform description of

arbitrary logic faults, and also physical defects by a combination of

stuck-at fault and additional logic condition for activating a defect to

cause the given SAF. The inputs of the tool are the logic description

of circuit in the form of structurally synthesized BDDs (SSBDD). All

the functional faults to be simulated are extracted from the SSBDD

model. The result of the simulation is the fault table.

Tool platform:

OS platforms: Windows/NT, Linux and Solaris

Program. language:

ANSI C language using Microsoft Visual C++, SUN workshop and

GNU CC compilers

Command:

var_analyze

Input:

SSBDD model file (.agm), test pattern file (.tst)

Output:

test patterns including fault analysis result for each low level block

(.tst).

Syntax:

var_analyze <design>

design:

Name of the design file without .agm extension.

2. TTU_MAFFAD - Mapping Functional Faults to Defects tool

Tool acronym:

TTU_MAFFAD

Tool destination:

The tool reads the fault table of functional faults of the circuit and the

defect tables of components of the circuit and calculates the defect

coverage (both, probabilistic and enumerative).

Tool description:

The inputs of the program are the fault table of functional faults

created as the result of the functional fault simulation tool

TTU_DOFSIM, and the defect table of components. The defect

tables should be pregenerated. In this project the pregeneration of

defect tables will be done by the partner CO1-WUT for a given set of

selected complex gates or components. The defect tables are stored

as library components. For each component the very costly analysis

of physical defects to create the defect table will be done only once.

The pregenerated results (the library defect table) will be used by the

tool TTU_MAFFAD each time where a component should be

analyzed. Such a hierarchical approach allows tremendously increase

the efficiency of simulation. In fact the complexity of the defect

simulation will be reduced to the complexity of the SAF simulation.

Tool platform:

OS platforms: Windows/NT, Linux and Solaris

Program. language:

ANSI C language using Microsoft Visual C++, SUN workshop and

GNU CC compilers

Command:

deforient

Input:

SSBDD model file (.agm), test pattern file (.tst), defect tables for the

low-level blocks.

Output:

Enumerative and probabilistic defect coverage report (.prb).

Syntax:

deforient <design>

design:

Name of the design file without .agm extension.

3. TTU_DOFGEN - Defect-Oriented Test Generation tool

Tool acronym:

TTU_DOFGEN

Tool destination:

The tool generates test patterns for all the physical defects of the

circuit described in the pregenerated library defect tables.

Tool description:

The test generation is carried out in a hierarchical way and is based

on the random test generation algorithm. The patterns are generated

randomly and simulated for functional faults. The detected functional

faults are mapped into the defect space by using the defect tables of

components.

Tool platform:

OS platforms: Windows/NT, Linux and Solaris

Program. language:

ANSI C language using Microsoft Visual C++, SUN workshop and

GNU CC compilers

Command:

randomgen

Input:

SSBDD model file (.agm)

Output:

test pattern file (.tst)

Syntax:

randomgen [options] <design>

design:

Name of the design file without .agm extension.

options:

-length <x>

Generate x test patterns

II. Tools for Built-In Self-Test analysis

Due to the high cost of external testers and of inefficiency of testing in real speed by external

testers the Built-In Self-Test (BIST) is the emerging testing concept in VLSI testing and,

particularly, in the System on Chip field. BIST is the capability of a circuit to test itself. BIST

is usually based either on generating on-line pseudorandom patterns by so called LinearFeedback-Shift-Registers (LFSR) or on using functional test patterns. In both cases it is

difficult to reach high-fault coverage because of existing hard-to-detect faults which can be

detected only by a single or very few test patterns. To reach high fault coverage, the HWbased generated pseudorandom (or functional) test patterns can be complemented by

deterministically pregenerated and stored test patterns. This combination is called hybrid

BIST. The problem here is to find out the best and cost-effective combination of on-line and

stored test patterns.

The low cost tools for simulating different architectures of BIST (or hybrid BIST) and for

analyzing the quality of BIST are missing. To support the lecture courses on BIST to be

developed in WP3 by laboratory works and research training the creation of the following

low-cost tools was planned.

1. TTU_SIMBIST - Simulation of Built-In Self-Test tool

Tool acronym:

TTU_SIMBIST

Tool destination:

The tool emulates the given BIST architecture, simulates given

circuit for a given sequence of pseudorandom test patterns, calculates

the signatures and fault coverage.

Tool description:

Different Logic BIST architectures can be emulated: BILBO, CSTP.

One of the two LFSR types can be used : standard or modular. The

structures of LFSRs for test generation and signature analysis are

optional and can be selected by specifying the corresponding polynomials. By emulating the BIST architecture a sequence of pseudorandom patterns will be generated, fault simulated and the final

signature will be calculated. The best settings of the LFSR registers

can be selected by repetitive simulation and by using genetic

algorithms.

Tool platform:

OS platforms: Windows/NT, Linux and Solaris

Program. language:

ANSI C language using Microsoft Visual C++, SUN workshop and

GNU CC compilers

Command:

bist

Input:

SSBDD model file (.agm)

Output:

test pattern file (.tst)

Syntax:

bist rand glen <generator_length>

alen <analyzer_length>] [options] <design>

[-

or

bist gpoly <generator_poly> -ginit <generator_init> [

apoly <analyzer_poly> -ainit <analyzer_init>] [options]

<design>

design:

Name of the design file without .agm extension.

generator_length:

Length of the generator LFSR in bits.

(Use only with rand option!).

Length of the analyzer LFSR in bits.

(Use only with rand and simul bilbo options!).

Feedback polynomial of the generator LFSR in binary

digits. (Do not use with rand option!).

Initial value of the generator LFSR in binary digits.

(Do not use with rand option!).

Feedback polynomial of the analyzr LFSR in binary digits.

(Do not use with rand and -simul cstp option!).

Initial value of the analyzer LFSR in binary digits.

(Do not use with rand and -simul cstp option!).

analyzer_length:

generator_poly:

generator_init:

analyzer_poly:

analyzer_init:

options:

-rand

Generate random LFSR feedback polynomials and initial

states.

With this option selected, exact fault coverage values will

be reported. BIST emulation will be slower but it will take

into account possible fault aliasing in the analyzer LFSR.

-simul <bilbo|cstp> Choses between BILBO and CSTP architectures. (Default

is BILBO).

-count <cycles>

The length of the test in clock cycles. Default is 1000.

-optimize

Dismiss test patterns at the end of the test sequence that do

not detect any additional faults.

-lsb

Design outputs are connected to the side of less significant

bits of the analyzer LFSR. (Default is the side of more

significant bits).

-run <num>

Run simulation <num> times, sort results and store best

one. Makes sense when -rand option is being used

-oext <extension>

output file with given extension (default '.tst')

-generate

generate test patterns only, don't perform any simulation

-modular

use modular LFSR instead of standard one

-aliasing

2. TTU_HYBCAN - Hybrid BIST Cost Analysis tool (script)

Tool acronym:

TTU_HYBCAN

Tool destination:

The tool emulates the given BIST architecture, fault simulates the

given circuit for the given sequence of pseudorandom test patterns,

calculates the fault coverage and total costs of hybrid BIST for the

given breakpoints of the test sequence.

Tool description:

In hybrid BIST, the length of the pseudorandom test is an important

parameter, which determines the behavior of the whole test process.

A shorter pseudorandom test implies a larger deterministic test. This

however requires additional memory space, but at the same time,

shortens the overall test process. A longer pseudorandom test, on the

other hand, will lead to longer test application time with reduced

memory requirements. Therefore it is crucial to determine the

optimal length of pseudorandom test in order to minimize the total

testing cost.

The inputs of the tool are the settings of the BIST architecture, and

the circuit to be fault simulated. First, the BIST will be emulated, and

the fault coverage for the given breakpoints of the test sequence will

be calculated. The number of clocks generated up to the breakpoint

determines the cost of pseudorandom test. For each breakpoint the

needed additional test patterns are generated to reach 100% fault

coverage. The number of needed deterministic patterns determines

the cost of the stored test. As the result of this procedure two

functions will be created: the functions of the costs of pseudorandom

test and of the stored test. The sum of these functions gives the

function of the total cost. The minimum of this cost determines the

breakpoint to be found.

Tool platform:

OS platforms: Linux, Solaris or any other UNIX-like OS able to run

shell scripts. In Windows environment Cygwin (UNIX-like

environment running atop Windows) installation is required.

Program. language:

Bourne Again Shell (bash) scripting

Command:

hybcost.sh

Input:

two test pattern files (.tst) from BIST emulator and deterministic

generator and SSBDD model file (.agm)

Output:

Location (index) of breakpoints and number of additional vectors for

completing 100% test. Results are saved into <design>.res file.

Syntax:

hybcost.sh <inp1> <inp2> <design>

design:

inp1:

inp2:

Name of the design file without .agm extension.

Test pattern file (.tst) from deterministic generator.

Test pattern file (.tst) from BIST emulator (SIMBIST).

III. Tools for design error diagnosis

Design errors stand for the mistakes or faults introduced by a designer or a CAD system

during the design process. Such errors usually manifest themselves during design validation

and verification stage. If the specification and the implementation of a design do not match a

design error has been introduced. An example of a design error could be a gate substitution

error. For example, an AND gate is replaced by OR gate in the implementation. It could be

also a bad or missing connection between gates. Extra or missing inverters are also examples

of a design error.

Design error diagnosis is an illustrative area for teaching diagnosis. It shows both the essential

principles of fault diagnosis and the existence of alternative fault models other than stuck-at

faults. The latter is important because the stuck-at fault model is widely accepted and taught

over the world. Therefore students know usually very little about the existence of different

fault models and different diagnostic problems.

The software package for manual design error diagnosis contains following tools.

10

1. TTU_DERRIN - Design Error Insertion tool

Tool acronym:

TTU_DERRIN

Tool destination:

This program creates a pair of specification and implementation,

which are not functionally equal. The specification will be then taken

as correct and the implementation as wrong

Tool description:

This tool is based on the EDIF format converter from the Turbo

Tester package. The input of the converter is the design description in

EDIF format. The output is the internal Turbo Tester format a

special kind of decision diagrams. TTU_DERRIN tool is an add-on

to the EDIF converter. It analyzes the structure of the design and

inserts a single design error into. The output of TTU_DERRIN tool is

two files. The first one is the correct design while the second is the

design which contains an error.

Tool platform:

OS platforms: Windows/NT, Linux and Solaris

Program. language:

ANSI C language using Microsoft Visual C++, SUN workshop and

GNU CC compilers

Command:

xtimport

Input:

EDIF or ISCAS89 netlist file

Output:

specification (.spec), implementation (.agm), gate-level paths (.gat),

gate names and types (.pat).

Syntax:

xtimport [options] <EDIF file> <library file>

options:

-paths

-spec

-read_iscas89

-gate_level

-tool <application>

-gnd <gnd name>

-vdd <vdd name>

Preserve information about gate-level signal paths.

Create a specification (insert a design error).

Read ISCAS89 format.

Generate gate-level SSBDD model. Default output is

macro-level SSBDD.

Options for application are orcad and cadence.

gnd name is the name of the GND net.

vdd name is the name of the VDD net.

11

2. TTU_PREDIA - Prediagnostic tool

Tool acronym:

TTU_PREDIA

Tool destination:

This automated tool allows reducing the suspected faulty area in

larger circuits for subsequent application of manual diagnosis

performed by the student.

Tool description:

In order to have larger variety of tasks for students as well as to have

less restrictions on the circuits used for practicing we propose the

following tool. The tool implements a special design error diagnosis

technique to reduce the area of analysis for larger circuits. The area is

to be kept within certain boundaries, which define the minimum and

the maximum number of gates considered to be under suspicion.

Tool platform:

OS platforms: Windows/NT, Linux and Solaris

Program. language:

ANSI C language using Microsoft Visual C++, SUN workshop and

GNU CC compilers

Command:

prediag

Input:

specification (.spec), implementation (.agm), gate-level paths (.gat),

gate names and types (.pat), test pattern (.tst).

Output:

report file (.rep).

Syntax:

prediag [options] <design>

design:

Name of the design file without .agm extension.

options:

-f

-n

-g

-v <extension>

-s <extension>

-o <extension>

-scr

Show failing outputs.

Do not show suspected nodes.

Do not show suspected gates.

extension is the file name extension of the input test pattern

file. Default extension is tst.

extension is the file name extension of the specification

model file. Default extension is spec.

extension is the file name extension of the output file.

Default extension is rep.

Print everything on the screen only.

12

3. TTU_TVECIN - Test Vector Insertion tool

Tool acronym:

TTU_TVECIN

Tool destination:

It is an interactive tool for manual insertion, deletion or update of

input test vectors in a test pattern file.

Tool description:

The Turbo Tester system has a special format the test vectors are kept

in. Automatic test pattern generation tools from Turbo Tester

package use this format to store generated tests in files. However, it

is inconvenient to manually compose from scratch these test vectors

files using this format. Therefore for manual test vector generation a

special user-friendly tool is needed to create the interface between the

user and the Turbo Tester. The proposed vector manager tool

includes also some simple test manipulation possibilities, like fault

simulation, logic simulation, random test vectors creation, etc. It can

work in an interactive as well as in a command line modes. In

interactive mode (usage: vecmanager) the program asks for the name

of the design, the name of the test pattern file, and finally gives the

following menu:

S. Show existing test patterns

N. Insert completely New test

A. Add vectors

D. Remove some vectors

R. Automatically generate some Random sequence

F. Perform Fault simulation

X. Save patterns and eXit

In the command line mode you can add only a single test vector.

Tool platform:

OS platforms: Windows/NT, Linux and Solaris

Program. language:

ANSI C language using Microsoft Visual C++, SUN workshop and

GNU CC compilers

Command:

vecmanager

Input:

SSBDD model file (.agm), test pattern file (.tst).

Output:

test pattern file (.tst).

Syntax:

vecmanager [options] [<design>]

design:

Name of the design file without .agm extension.

options:

-new

-add <vector>

-i <extension>

-o <extension>

-ftable

Create completely new test set.

Add test pattern vector.

extension is the file name extension of the input file.

Default extension is tst.

extension is the file name extension of the output file.

Default extension is tst.

Perform fault simulation.

13

4. TTU_ECRDCR - Encryption/Decryption tool

Tool acronym:

TTU_ECRDCR

Tool destination:

The encryption part of the tool encrypts the information about the

design error, which includes the type of inserted error and its precise

location. The decryption part of the tool allows teacher to decrypt the

information about the design error and therefore to verify the

correctness of the diagnosis performed by the student.

Tool description:

The encryption part of the tool must be implemented as a part of the

Design Error Insertion tool - TTU-DERRIN. The decryption part of

the tool is implemented as a separate program (checkgate).

Tool platform:

OS platforms: Windows/NT, Linux and Solaris

Program. language:

ANSI C language using Microsoft Visual C++, SUN workshop and

GNU CC compilers

Command:

checkgate

Input:

encrypted name and type of the erroneous gate (can be read from file

<design>.rep).

Output:

decrypted name and type of the erroneous gate.

Syntax:

checkgate [options] [ -f <InFile>| -m <message>]

InFile:

File containing the encrypted message.

message:

String of printable ASCII characters (encrypted message).

options:

-o <file>

-s

file is the output file.

Print output also on the screen.

(default: if -f specified - don't, otherwise - yes).

14

5. TTU_COMLIB - Common Library

Tool acronym:

TTU_COMLIB

Tool destination:

This component is to be created to bind the diagnostic programs

together as well as to implement some minor functions used

throughout the package.

Tool description:

Some functions for reading and writing of common formats are to be

implemented as well as the functions to append the common log file

from all the diagnostic package components.

Tool platform:

OS platforms: Windows/NT, Linux and Solaris

Program. language:

ANSI C language using Microsoft Visual C++, SUN workshop and

GNU CC compilers

15

IV. Tools for high level test generation

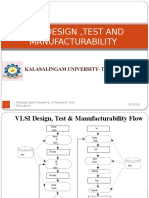

1. Software tools for VHDL Design and Test Flow (CR3-TTU)

As the degree of integration in VLSI designs has been growing, so has the need for

automation of different design tasks. Design automation helps to shorten the time-to-market

cycle and improves significantly designers productivity. The automation was first introduced

on the lower levels of design tasks, like placement and routing, and together with the growth

of design complexities, moved gradually to higher levels, e.g. logic synthesis, high-level

synthesis (HLS) and hardware/software co-design. Nowadays the goal is to automate the

entire design cycle from conceptualization to generation of silicon layout.

During recent years, more-and-more commercial and university high-level synthesis tools

have become available. These tools are applied for automatically generating a registertransfer level (RTL) description from a behavioral description of the circuit. In the RTL

descriptions the design has been partitioned into a control part, i.e. a finite state machine, and

a datapath part containing a network of interconnected functional units (FU). Usually the HLS

tools take into account several constraints, as speed, area, or testability, and allow the

designer to quickly compare the trade-offs between alternative RTL implementations.

The circuit design flow continues by synthesizing the RTL descriptions to the logic level.

Subsequently, the logic gates are placed to the chip layout and connections between them are

routed. Finally, the chip is manufactured in a silicon foundry and tested.

We propose a hierarchical test generation fitting into the circuit synthesis flow described

above. The environment consists of a hierarchical test generator and dedicated high- and lowlevel Decision Diagram (DD) model interfaces. From RT-level VHDL descriptions, highlevel DD interface generates RTL DD models, which are applied as the high-level input for

the test generator. Low-Level DD (LLDD) representations are required when generating

local, structural level tests for the functional units (FU) of the design. For that purpose, an

EDIF to LLDD interface has been implemented. The system includes also a low-level

sequential circuit fault simulator, which is needed to measure the stuck-at fault coverage of

the tests generated by the hierarchical ATPG.

The VHDL Design and Test Flow includes the following steps and tools (printed in italics).

- The user describes a design at behavioral level using VHDL.

- A high-level synthesis tool xTractor (a tool developed at TTU) synthesizes the

description into RT-level VHDL.

- VHDL interface (VHDL to DD Converter) is used to generate High-Level Decision

Diagram (HLDD) models from the RTL VHDL. This tool is to be developed in the

REASON project.

- Synopsys Design Compiler is run in order to synthesize the RTL VHDL into logic

level netlist in EDIF format.

- Low-Level Decision Diagrams (LLDD) are generated from the EDIF description by

EDIF importing tool. This tool is developed at TTU.

- The generated HLDD and LLDD models are used in hierarchical test generation by

DECIDER tool and in hierarchical fault simulation. The DECIDER tool is developed

at TTU.

- Exact fault coverage of the tests are measured using the logic level fault simulator.

This tool is developed at TTU and belongs to the tool-set Turbo-Tester

Specification of the tool developed in this project:

16

2. TTU_VHDLDD VHDL to DD Converter for hierarchical test generation

Tool acronym:

TTU_VHDLDD

Tool destination:

The tool is used to generate High-Level Decision Diagram (HLDD)

models from the RTL VHDL to create a link between high-level

synthesis flow and hierarchical test generation flow.

Tool description:

VHDL2DD tool translates behavioral register transfer level (RTL)

VHDL to high-level decision diagram representation format suitable

for simulation and test generation programs. Supported source RTL

level VHDL should describe both Data and Control path of the

digital device; description should contain the control states and

possible data operations in each state. Generated structural VHDL

code is one level lower in abstraction than RTL level VHDL code.

Control and data paths are separated and each operation in source

VHDL is replaced with proper functional element, multiplexers

introduced in order to commutate data. There is one-to-one mapping

between generated high level DD-s and generated structural VHDL

Tool platform:

OS platforms: Solaris

Program. language:

ANSI C language using SUN workshop and GNU CC compilers

Command:

vhdl2dd

Input:

Behavioral RTL VHDL (*.vhdl)

Output:

High-Level Decision Diagram, corresponding structural vhdl

(result_file_name)

Syntax:

or

vhdl2dd < source_file_name (results displayed on screen)

vhdl2dd < source_file_name >! result_file_name (results into

file)

source_file_name:

substitute with your input file name

result_file_name:

substitute with your output file name

17

Вам также может понравиться

- XCELIUM BASIC Vs ADVANCED PROFILERДокумент9 страницXCELIUM BASIC Vs ADVANCED PROFILERPriya JeejoОценок пока нет

- Aa SoftwareДокумент12 страницAa SoftwareLeopoldoОценок пока нет

- ALIZE EvaluationДокумент68 страницALIZE EvaluationJonathan Arley Torres Castañeda0% (1)

- ST20 ToolsetДокумент21 страницаST20 Toolsetprobka9378Оценок пока нет

- Karpagam University Digital Labs Revision 2.0Документ76 страницKarpagam University Digital Labs Revision 2.0vmspraneethОценок пока нет

- Analog: Section 5: Design PracticesДокумент56 страницAnalog: Section 5: Design PracticesBianca CopelandОценок пока нет

- Titanic: Mohit Kothari Roger Tanuatmadja Gautam AkiwateДокумент18 страницTitanic: Mohit Kothari Roger Tanuatmadja Gautam AkiwatezarthonОценок пока нет

- Modern GPUДокумент221 страницаModern GPUx2y2z2rmОценок пока нет

- Soc Firmware Debugging Tracer in Emulation Platform: NtroductionДокумент7 страницSoc Firmware Debugging Tracer in Emulation Platform: NtroductionMani KiranОценок пока нет

- Implementation of SystemVerilog Environment For Functional Verification of AHB-DMA BridgeДокумент4 страницыImplementation of SystemVerilog Environment For Functional Verification of AHB-DMA BridgeEditor IJRITCCОценок пока нет

- Genus Synthesis Solution: Genus RAK For Beginners With Common UI (CUI)Документ22 страницыGenus Synthesis Solution: Genus RAK For Beginners With Common UI (CUI)eadaladarenu100% (1)

- Tools To Aid Debugging On AIXДокумент12 страницTools To Aid Debugging On AIXYoussifAhmedJulaihОценок пока нет

- Digital Lab Manual Cadence PDFДокумент82 страницыDigital Lab Manual Cadence PDFLokesh Nikhade100% (1)

- Lab ManualДокумент10 страницLab Manualt.r. SanthoshОценок пока нет

- IntroductionДокумент26 страницIntroductionHitesh Bhati0% (1)

- Using 3070 For Insystem ProgrammingДокумент12 страницUsing 3070 For Insystem ProgrammingFer TorresОценок пока нет

- Lab 03Документ4 страницыLab 03FarazОценок пока нет

- Locating VLSI Failures Using Scan Design InformationДокумент8 страницLocating VLSI Failures Using Scan Design InformationSrivatsava GuduriОценок пока нет

- Verilog AMS TutorialДокумент29 страницVerilog AMS TutorialSiva KrishnaОценок пока нет

- Hardware/Software Co-Verification Using The Systemverilog DpiДокумент8 страницHardware/Software Co-Verification Using The Systemverilog DpiRude BeeОценок пока нет

- 01 PCP SystemДокумент37 страниц01 PCP SystemRobertОценок пока нет

- DM00105879 PDFДокумент865 страницDM00105879 PDFDaniel CrutanОценок пока нет

- EC6612 - VLSI Design Laboratory ManualДокумент39 страницEC6612 - VLSI Design Laboratory ManualSriramОценок пока нет

- DFT VisionДокумент18 страницDFT VisionNaganithesh Ghattamaneni0% (1)

- 4 Implementing Application Specific Routines: App.c App.cДокумент5 страниц4 Implementing Application Specific Routines: App.c App.cKailash BhosaleОценок пока нет

- Embedded Systems Tools & PeripheralsДокумент4 страницыEmbedded Systems Tools & PeripheralsShoriful Islam TarekОценок пока нет

- Interactive Debug Speeds Up UVM Regression and DebugДокумент9 страницInteractive Debug Speeds Up UVM Regression and DebugIkshvaku ModiОценок пока нет

- WCET Tool Challenge 2006 Final ReportДокумент15 страницWCET Tool Challenge 2006 Final ReportwerОценок пока нет

- 6 CosynthesisДокумент50 страниц6 CosynthesisRaghu RamОценок пока нет

- Microprocessor & Microcontroller Laboratory Manual 4Th Semester Ise Subject Code: 15Csl48Документ73 страницыMicroprocessor & Microcontroller Laboratory Manual 4Th Semester Ise Subject Code: 15Csl48Dr-Engr ShahMurtaza RashidAl MasudОценок пока нет

- Fpga Express VHDL Reference ManualДокумент496 страницFpga Express VHDL Reference ManualelfrichОценок пока нет

- PG Diploma in Embedded Systems Design (PG-DESD) Course FocusДокумент7 страницPG Diploma in Embedded Systems Design (PG-DESD) Course Focusabhijeetv2Оценок пока нет

- BCSP 801 Aos Lab FileДокумент29 страницBCSP 801 Aos Lab FileParas SharmaОценок пока нет

- DSP Lab Manual 15-11-2016 PDFДокумент73 страницыDSP Lab Manual 15-11-2016 PDFsmdeepajpОценок пока нет

- Scripting Components For AutoCAD Plant 3DДокумент14 страницScripting Components For AutoCAD Plant 3DJose TorresОценок пока нет

- OS Lab 2Документ2 страницыOS Lab 2Raj SinghОценок пока нет

- BMW Inpa English User GuideДокумент74 страницыBMW Inpa English User GuideMannfred Zaturek67% (3)

- Tce TutorialДокумент12 страницTce TutorialMuhammad RehanОценок пока нет

- Nonfictionsrivastav A 94 AtomДокумент10 страницNonfictionsrivastav A 94 AtomJoseph JohnОценок пока нет

- Synopsis Compiler DesignДокумент2 страницыSynopsis Compiler DesignAbhay ChauhanОценок пока нет

- System On Chip Architecture Design Lecture11Документ13 страницSystem On Chip Architecture Design Lecture11Thi NguyenОценок пока нет

- An Audio Example Using DSP/BIOS: Application ReportДокумент24 страницыAn Audio Example Using DSP/BIOS: Application ReportFRANKLINОценок пока нет

- Exploit Writing Tutorial ROPWith ShellcodeДокумент33 страницыExploit Writing Tutorial ROPWith ShellcodeRotem SalinasОценок пока нет

- Cdnlive Jungeblut PaperДокумент5 страницCdnlive Jungeblut PaperSamОценок пока нет

- Vlsi Manual 2013-2014Документ36 страницVlsi Manual 2013-2014hr_suresh_kОценок пока нет

- Digital System Desgin Study AssignmentДокумент5 страницDigital System Desgin Study AssignmentZohaib AliОценок пока нет

- Bal DelimitДокумент3 страницыBal Delimittempogv tempogvОценок пока нет

- DSP System Toolbox™ Getting Started GuideДокумент91 страницаDSP System Toolbox™ Getting Started GuideKhai HuynhОценок пока нет

- RN 34Документ110 страницRN 34liznОценок пока нет

- Tarmac ReportДокумент102 страницыTarmac Reportshubham.neОценок пока нет

- KernrateДокумент22 страницыKernrateSandro ReimãoОценок пока нет

- Benchmarking SlidesДокумент9 страницBenchmarking Slidessarwan111291Оценок пока нет

- A Simple Framework For Behavioral Experiments Using The Psychophysics Toolbox For MATLABДокумент32 страницыA Simple Framework For Behavioral Experiments Using The Psychophysics Toolbox For MATLABjacksonzchenОценок пока нет

- Apps TechnicalДокумент86 страницApps TechnicalAbhishekОценок пока нет

- 02 Creating HW LabДокумент5 страниц02 Creating HW LabgpuonlineОценок пока нет

- Software Engineering for Embedded Systems: Methods, Practical Techniques, and ApplicationsОт EverandSoftware Engineering for Embedded Systems: Methods, Practical Techniques, and ApplicationsРейтинг: 2.5 из 5 звезд2.5/5 (2)

- Python Advanced Programming: The Guide to Learn Python Programming. Reference with Exercises and Samples About Dynamical Programming, Multithreading, Multiprocessing, Debugging, Testing and MoreОт EverandPython Advanced Programming: The Guide to Learn Python Programming. Reference with Exercises and Samples About Dynamical Programming, Multithreading, Multiprocessing, Debugging, Testing and MoreОценок пока нет

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemОт EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemОценок пока нет

- SAS Programming Guidelines Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesОт EverandSAS Programming Guidelines Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesОценок пока нет

- Embedded Systems Design with Platform FPGAs: Principles and PracticesОт EverandEmbedded Systems Design with Platform FPGAs: Principles and PracticesРейтинг: 5 из 5 звезд5/5 (1)

- Problems To ThinkДокумент40 страницProblems To ThinksivapothiОценок пока нет

- Course Content: Soft ComputingДокумент2 страницыCourse Content: Soft ComputingKirtesh SharmaОценок пока нет

- Vlsi Design, Test and Manufacturability: Kalasalingam University-TessolveДокумент21 страницаVlsi Design, Test and Manufacturability: Kalasalingam University-TessolvesivapothiОценок пока нет

- ECE 617 - Fault Testable Design Dr. Janusz Starzyk: School of EECS Ohio University Athens, OH, 45701Документ79 страницECE 617 - Fault Testable Design Dr. Janusz Starzyk: School of EECS Ohio University Athens, OH, 45701sivapothiОценок пока нет

- 02 Fundamentals of Neural NetworkДокумент40 страниц02 Fundamentals of Neural NetworkhahaОценок пока нет

- 02 Fundamentals of Neural NetworkДокумент40 страниц02 Fundamentals of Neural NetworkhahaОценок пока нет

- Department of Electronics & Communication Engineering: National Institute of Technology CalicutДокумент41 страницаDepartment of Electronics & Communication Engineering: National Institute of Technology CalicutRakesh HsОценок пока нет

- External Member CDACДокумент1 страницаExternal Member CDACsivapothiОценок пока нет

- Btech Regulations 2015 16Документ23 страницыBtech Regulations 2015 16sivapothi100% (1)

- 01-Introduction To Soft Computing PDFДокумент61 страница01-Introduction To Soft Computing PDFHemalatha Natarajan100% (2)

- CMOS Digital Integrated Circuits Solution Manual-LibreДокумент146 страницCMOS Digital Integrated Circuits Solution Manual-LibreVivek Singh0% (1)

- Fuzzy Set TheoryДокумент42 страницыFuzzy Set TheoryKarthikeyan L.MangaОценок пока нет

- 03-Back Propagation NetworkДокумент33 страницы03-Back Propagation NetworkKirtesh SharmaОценок пока нет

- Course Content: Soft ComputingДокумент2 страницыCourse Content: Soft ComputingKirtesh SharmaОценок пока нет

- 01-Introduction To Soft Computing PDFДокумент61 страница01-Introduction To Soft Computing PDFHemalatha Natarajan100% (2)

- Course Content: Soft ComputingДокумент2 страницыCourse Content: Soft ComputingKirtesh SharmaОценок пока нет

- Design RulesДокумент14 страницDesign RulessivapothiОценок пока нет

- Course Content: Soft ComputingДокумент2 страницыCourse Content: Soft ComputingKirtesh SharmaОценок пока нет

- DEN0013D Cortex A Series PGДокумент421 страницаDEN0013D Cortex A Series PGDesai Raghavendra ReddyОценок пока нет

- Lowpowervlsidesignbook 140426055029 Phpapp02Документ326 страницLowpowervlsidesignbook 140426055029 Phpapp02sivapothiОценок пока нет

- 03-Back Propagation NetworkДокумент33 страницы03-Back Propagation NetworkKirtesh SharmaОценок пока нет

- MOS Transistors and CMOS InvertersДокумент34 страницыMOS Transistors and CMOS InverterssivapothiОценок пока нет

- FabricationДокумент26 страницFabricationAbhishek RaiОценок пока нет

- Vasthu Sastra in TamilДокумент44 страницыVasthu Sastra in Tamilkailasasundaram85% (47)

- Gated-Clock Design of Linear-Feedback Shift Registers: Walter Aloisi and Rosario Mita, Member, IEEEДокумент5 страницGated-Clock Design of Linear-Feedback Shift Registers: Walter Aloisi and Rosario Mita, Member, IEEECn RishabhОценок пока нет

- Understanding Linear Feedback Shift Registers - The Easy WayДокумент3 страницыUnderstanding Linear Feedback Shift Registers - The Easy WayrockymaxdeemannОценок пока нет

- CC6004ES Network & Cloud Security: London Metropolitan University, Faculty of ComputingДокумент25 страницCC6004ES Network & Cloud Security: London Metropolitan University, Faculty of Computingjey456Оценок пока нет

- Whack A Mole FPGA ReportДокумент8 страницWhack A Mole FPGA ReportRadhey PatelОценок пока нет

- Stream Ciphers: Cryptography - CS 507 Erkay Savas Sabancı UniversityДокумент37 страницStream Ciphers: Cryptography - CS 507 Erkay Savas Sabancı UniversitymasterofdonОценок пока нет

- Engineering Committee Digital Video Subcommittee: ANSI/SCTE 55-1 2009Документ51 страницаEngineering Committee Digital Video Subcommittee: ANSI/SCTE 55-1 2009gerardo100% (1)

- Illinois Scan ArchitectureДокумент34 страницыIllinois Scan Architectureshri1527Оценок пока нет

- Breaking Hitag2 With Reconfigurable Hardware: August 2011Документ7 страницBreaking Hitag2 With Reconfigurable Hardware: August 2011LIRO ROMAОценок пока нет

- Linear Feedback Shift RegisterДокумент3 страницыLinear Feedback Shift RegisterPappuОценок пока нет

- Lecture 3 OTP, PRG and Stream CipherДокумент39 страницLecture 3 OTP, PRG and Stream CipherMohammad BangeeОценок пока нет

- Nhập môn An toàn Thông tin - LFSRДокумент26 страницNhập môn An toàn Thông tin - LFSRDuc Anh Vu TranОценок пока нет

- GB 20600-2006 EnglishДокумент123 страницыGB 20600-2006 EnglishSharath PadaruОценок пока нет

- Design and Evaluation of Confidence-Driven Error-Resilient SystemsДокумент11 страницDesign and Evaluation of Confidence-Driven Error-Resilient SystemsNguyen Van ToanОценок пока нет

- Communication Protocols Augmentation in VLSI Design ApplicationsДокумент5 страницCommunication Protocols Augmentation in VLSI Design ApplicationsMoorthy VenkatachalamОценок пока нет

- Breaking The GSM A5/1 Cryptography Algorithm With Rainbow Tables and High - End FpgasДокумент19 страницBreaking The GSM A5/1 Cryptography Algorithm With Rainbow Tables and High - End FpgasrajithaОценок пока нет

- Module-5-Final GMITДокумент20 страницModule-5-Final GMITmvs sowmyaОценок пока нет

- PRBS Generator Using VHDL FinalДокумент16 страницPRBS Generator Using VHDL FinalDivyesh100% (1)

- Temps_utile manual (TU v.1.3) guideДокумент7 страницTemps_utile manual (TU v.1.3) guideDragos AndrianaОценок пока нет

- JMTE Vol I 2013Документ150 страницJMTE Vol I 2013malikscribdОценок пока нет

- Improvement of The Orthogonal Code Convolution Capabilities Using Fpga ImplementationДокумент50 страницImprovement of The Orthogonal Code Convolution Capabilities Using Fpga Implementationscribdashokram100% (2)

- Lab E4 Group 22 PDFДокумент12 страницLab E4 Group 22 PDFAndy NgoОценок пока нет

- LFSR Based S-Box For Lightweight Cryptographic ImplementationДокумент2 страницыLFSR Based S-Box For Lightweight Cryptographic ImplementationAMJAD HUSSAIN ZAHIDОценок пока нет

- PN Sequence GeneratorДокумент7 страницPN Sequence GeneratorTanvir Manhotra0% (1)

- Verilog ExamplesДокумент57 страницVerilog ExamplesSandeepDeyОценок пока нет

- Synchronous FIFO VerilogДокумент23 страницыSynchronous FIFO VerilogRoshan RajuОценок пока нет

- Watermark Host10Документ6 страницWatermark Host10Bala ChandranОценок пока нет

- Digital Design Interview Questions & AnswersДокумент5 страницDigital Design Interview Questions & AnswersSahil KhanОценок пока нет

- Digital Image Encryption Using AES and Random Number GeneratorДокумент10 страницDigital Image Encryption Using AES and Random Number Generatorolusayo oluwadareОценок пока нет

- A Security Analysis of Two Satphone Standards: Don't Trust Satellite PhonesДокумент15 страницA Security Analysis of Two Satphone Standards: Don't Trust Satellite Phonesganesh9619866360Оценок пока нет

- System Identification: Arun K. TangiralaДокумент13 страницSystem Identification: Arun K. TangiralaSelvarajОценок пока нет