Академический Документы

Профессиональный Документы

Культура Документы

2102-Ritu Sharma 2

Загружено:

Dr-Irfan Ahmad PindooАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

2102-Ritu Sharma 2

Загружено:

Dr-Irfan Ahmad PindooАвторское право:

Доступные форматы

International Journal of Latest Research in Science and Technology

Vol.1,Issue 2 :Page No.179-182 ,July-August (2012)

http://www.mnkjournals.com/ijlrst.htm

ISSN (Online):2278-5299

ANALYSIS OF ADIABATIC LOGIC NOR GATE FOR

POWER REDUCTION

Ritu Sharma1, Pooja Nagpal2, Nidhi Sharma3

Department of Electronics and Communication

* JCVD College, Sirsa-125055, India

1

ritusharmagemini@yahoo.co.in

#JCVD College, Sirsa-125055, India

2

poojamehra80@rediffmail.com

^YMCA University of Science and Technology, Faridabad-121006, India

3

nidhi1318@gmail.com

1,2,3

Abstract- This paper presents a new adiabatic logic family for NOR gate. The Paper discussed design of NOR gate

using adiabatic technology namely 2pascl,2padcl,Adcl,Quassi and QSERL technology The proposed two phase clocked

adiabatic static CMOS logic (2PASCL) circuit utilizes the principle of adiabatic switching and energy recovery. We

design and simulate NOR logic gates based on 2PASCL, 2PADCL, ADCL ,QUASI and QSERL with Tanner tool

version 13 implemented using 0.18m CMOS technology. From the simulation results and compared with all

technologies ,it is shown that 2PASCL NOR logic gives lowest power dissipiation at transition frequencies of 10 to 100

MHz. The transient analysis of the circuits is performed on tanners tool at a supply voltage ranging 1.8V using TSMC

0.18m CMOS process. A constant output load capacitance of 1pF is used for power and delay measurements.

Keywords - CMOS, 2PASCL, adiabatic, QUASI and TSMC

I.

INTRODUCTION

As demand for Portable products is increasing the need for

low-power design is becoming a major issue in highperformance digital systems, such as microprocessors, digital

signal processors (DSPs) and other applications. Increasing

chip density and higher operating speed lead to the design of

very complex chips with high clock frequencies. Low power

design of VLSI circuits has been identified as a critical

technological need in recent years due to the high demand for

portable consumer electronics products..In this paper NOR

gate is designed by using adiabatic technology namely

2pascl,2padcl,adcl,quasi and qserl.Paper discussed the design

of nor gates by all these technologies and compared the

power dissipiation in all the technologies

I.

DESIGN OF CIRCUITS

The Operation of the 2PASCL NOR illustrated by circuit

diagram and waveform shown in Figure. Two diodes

differentiate between 2PASCL [5] and static CMOS logic

gate. One diode from the output node to the power clock

supply and another one is placed next to the nMOS logic to

another power clock. . Both MOSFET-diodes are used to recycle the charges from the output node, to improve

discharging speed of internal signal nodes. Signal nodes got

the advantage due to the long chain of switches before them.

The other

difference is that split-level sinusoidal power clock supplies,

and are used to replace the Vdd and the Vss. Substrate of

nMOS, it is connected to clk(bar) whereas for pMOS is

connected to clk. Figure 1 illustrate the ciruit diagram and

figure 2 output waveform. In output waveform sinusoidal

clock used as power supplies as clk and clk(bar) and output

of nor is shown in second row.

A. TWO PHASE CLOCKED ADIABATIC STATIC

CMOS LOGIC (2PASCL)

Fig.1 Schematic of 2pascl nor gate

ISSN 2278-5299

Fig. 2 Output waveform of nor 2pascl

179

Ritu Sharma et.al, International Journal of Latest Research in Science and Technology

B. TWO PHASE ADIABATIC DYNAMIC CMOS

LOGIC (2PADCL)

Fig 3 Schematic of 2padcl nor gate

Fig 3,4 illustrate proposed 2PADCL NOR. In 2PADCL NOR

operated with complementary phases of power supply signals.

Supply waveform having two modes in. evaluation. and .hold,

assumption made for adiabatic mode in which clk and

clk(bar) are in evaluation mode, then there is conducting

path(s) in either PMOS devices or NMOS devices.

Evaluation of output node made from low to high or from

high to low or remain unchanged, which resembles to the

CMOS circuit. Thus, there is no need to restore the node

voltage to 0 (or Vdd) every cycle. On the other side When clk

and clk(bar) are in hold mode, Output node holds its value in

spite of the fact that clk and clk(bar) are changing their values.

By observing the function of diodes and the fact that the

inputs of a gate have a different phase with the output we can

find the above mentioned facts. Reduction of node switching

activity subsequently takes place due to not necessarily

charging and discharging of circuit nodes with every clock

cycle. Therefore, the speed of 2PADCL [6] circuits is faster

than that of ADCL circuits. Other feature of the 2PADCL is

that the logical .1. State does not reach the peak value of the

power supply but is lower by the amount of drain-source

voltage VDS of the MOS-switch and the diode voltage Vd,

i.e. V (1) = Vclk - VDS- Vd. In a similar manner, the

logical .0. State is not equal to the ground potential but

remains above that, i.e. V (0) = VDS +Vd. The circuit

diagram of 2padcl and its output waveform is shown in figure

below:

Fig.5 Schematic of adcl nor gate

Takahashi and Mizunuma [2] has provided ADCL logic

which was later modified by, Kaishita et al [2]. Placement of

rectifying diode was the main difference between the two

logic circuits. The number of diodes get reduced in the

modified ADCL logic circuit and that modified ADCL design

we have used. A low energy system is achieved by using one

sinusoidal and triangular clock supply. Two rectifying diodes

are used each in charging path and discharging path to

control the charge flow. By using MOSFET as diode, gate

and drain are shorted of mosfet together. Threshold voltage

of Mosfet or potential drop between drain and source in

conducting mosfet may cause energy dissipiation in this logic

circuit because diode in this logic circuit cut in potential and

thus energy is dissipiated in resistance of MOS devices.And

further use of slowly varying power clock provides small

energy dissipiation in the ON resistance of MOS devices. The

output waveform of ADCL logic circuit is shown in fig 5 in

first row, input given to the inverter is shown in row second

and waveform in third row shows the power clock.

D.

Fig. 6 Output waveform of adcl nor gate

QUASI ADIABATIC NOR

Fig. 4 Output waveform of nor gate

C.

ADIABATIC DYNAMIC CMOS LOGIC NOR

(ADCL)

ISSN 2278-5299

Fig. 7 Schematic of adcl nor gate

180

Ritu Sharma et.al, International Journal of Latest Research in Science and Technology

In fully adiabatic circuits no loss occurs neither adiabatic-loss

and nor non-adiabatic loss where as in Quasi-adiabatic

circuits the non adiabatic losses are present. In quasi

adiabatic circuits [4] range of frequency is divided in three

regions namely high frequency ,low frequency and mid

frequency range.In low frequency range adiabatic losses are

minimum, leakage losses are minimum in high frequency

range and in mid frequency range overall energy dissipiation

is low.Due to different numbers of transistors, power-clock

schemes these ranges of frequency are different for different

quasi adiabatic circuits .Quasi adiabatic circuits [3] is better

as it consumes less silicon area because circuits do not

requires isolation switches. The timing of input signal and

power clock supply is not critical

varies from 0 to 1.8V and first two row shows the sinusoidal

clock clk and clk(bar) in complementary phase is shown.

Fig. 10 Output Waveform Of Qserl

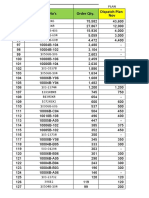

III SIMULATION RESULTS

Two-Input2PASCL,2PADCL,ADCL,QUASI,QSERL NOR

Gate structure is designed in Tanners Tool (TSPICE) and

simulated with capacitance of 1pf. The transient simulated

results are shown in table .

Table 1.

Fig. 8 Output waveform of quasi

E. QUASI-STATIC ENERGY RECOVERY LOGIC NOR

GATE (QSERL)

In

pu

tA

0

Inp

utB

2pascl

2padcl

Adcl

Quasi

Qserl

Weak0

Weak1

Strong0

Strong

0

Strong

0

Strong

0

Strong

1

Strong

0

Strong

0

Strong

0

Strong

1

Strong

0

Strong

0

Strong

0

Strong

1

Strong

0

Strong

0

Strong

0

Strong0

Strong0

Fig. 9 Schematic of qserl nor gate

Fig. 11 Power dissipation graph for nor gate at 500Hz

QSERL resembles the static CMOS logic. Diodes present at

top of p-mos tree helps in control of charging path while

discharging path is controlled by diode at bottom of n-mos

tree. Cascaded gates are in alternate phases are used.The

sinusoidal clock clk and clk(bar) in complementary phases

are used.The first gate is in evaluation mode where as first

gate is in hold phase. QSERL is static in contrast to dynamic

adiabatic logic . In QSERL [5] diodes are used to control for

charging and discharging paths which later replaced by low

threshold voltage mosfet.The output of QSERL waveform is

shown in fig in which input in form of pulse form and its

corresponding output is shown in second row whose voltage

ISSN 2278-5299

From the results, 2PASCL based inverter gives the lowest

181

Ritu Sharma et.al, International Journal of Latest Research in Science and Technology

Fig. 12 Power dissipation at different freq.

IV. CONCLUSIONS AND FUTURE WORK

This paper has described a simulation of NOR logic gate

based on adiabatic technology using five technologies

namely 2pascl,2padcl,adcl,quasi and qserl.By implementing

the adiabatic charging and energy recovery theory, 2PASCL

NOR gives the lowest result in power dissipation of all the

simulated adiabatic NOR . It has been seen that at different

frequencies power disipiation for nor gate using 2pascl

technology has the lowest power reduction . In future these

logics can be designed at other technologies to further reduce

the power consumption and voltage swing can be improved

and future work on minimization of chip area can also be

done on various technologies.

ACKNOWLEDGMENT

I would like to express my appreciation to all those whom

have made this paper a reality. My greatest appreciation and

thanks goes out to Asst. Prof. Pooja Nagpal for the support

and advice given throughout. Also I would like to thank Asst

Prof. Prashant Kumar for his expert advice throughout the

paper.

References

[1] Sung Mo kang Yusuf Leblebici CMOS digital Integrated circuits,

3rd edition, Tata McGraw-Hill,2003.

[2] Nazrul Anuar, Yasuhiro Takahashi Toshikazu Sekine Faculty of

Engineering Gifu University, Adiabatic Logic versus CMOS for Low Power

Applications.

[3] J. M. RABAEY, AND M. PEDRAM, Low Power Design

Methodologies, Kluwer Academic Publishers, 2002

[4]T. INDERMAUER AND M. HOROWITZ, Evaluation of Charge

Recovery Circuits and Adiabatic Switching for Low Power Design,

Technical Digest IEEE Symposium Low Power Electronics, San Diego, pp.

102-103, October 2002.

[5] Y. Ye and K. Roy, QSERL: Quasi-static energy recovery logic, IEEE J.

Solid-States Circuits, vol.36, no.2, pp.239248, Feb. 2001.

[6] N. Anuar, Y. Takahashi and T. Sekine, Two phase clocked adiabatic

static logic circuit: a proposal for digital low power applications, Proc.

IEICE Gen. Conf., p.102, Mar. 2009.

ISSN 2278-5299

182

Вам также может понравиться

- Adiabatic Positive Feedback Charge Recovery Logic For Low Power CMOS DesignДокумент6 страницAdiabatic Positive Feedback Charge Recovery Logic For Low Power CMOS DesignvaseemalikhanОценок пока нет

- Adiabatic Differential Cascode Voltage Switch Logic (A-DCVSL) For Low Power ApplicationsДокумент12 страницAdiabatic Differential Cascode Voltage Switch Logic (A-DCVSL) For Low Power ApplicationsVishwas GosainОценок пока нет

- Performance Analysis of Positive Feedback Adiabatic Logic For Low PowerДокумент7 страницPerformance Analysis of Positive Feedback Adiabatic Logic For Low PowerKiran KumarОценок пока нет

- Pre-Settable Sequential Circuits Design Using Single-Clocked Energy Efficient Adiabatic LogicДокумент6 страницPre-Settable Sequential Circuits Design Using Single-Clocked Energy Efficient Adiabatic LogicSiam HasanОценок пока нет

- Design and Analysis of CMOS and Adiabatic 4-Bit Binary MultiplierДокумент4 страницыDesign and Analysis of CMOS and Adiabatic 4-Bit Binary MultipliervaseemalikhanОценок пока нет

- A 52 PJ Bit OOK Transmitter With Adaptable Data RateДокумент4 страницыA 52 PJ Bit OOK Transmitter With Adaptable Data RatejaberyemeniОценок пока нет

- Recent Development in Efficient Adiabatic Logic Circuits and Power Analysis With CMOS LogicДокумент9 страницRecent Development in Efficient Adiabatic Logic Circuits and Power Analysis With CMOS LogicSaurav DixitОценок пока нет

- Low Power CMOS Digital Circuit Design Methodologies With Reduced Voltage SwingДокумент4 страницыLow Power CMOS Digital Circuit Design Methodologies With Reduced Voltage SwingMaheshОценок пока нет

- Robust Subthreshold Circuit Designing Using Sub-Threshold Source Coupled Logic (STSCL)Документ5 страницRobust Subthreshold Circuit Designing Using Sub-Threshold Source Coupled Logic (STSCL)Sonu SangwanОценок пока нет

- Project ReportДокумент37 страницProject ReportAmit SinghОценок пока нет

- Basic Design of SCLДокумент4 страницыBasic Design of SCLDunna SrinivasraoОценок пока нет

- Complementary Pass-Transistor Energy Recovery Logic For Low-Power ApplicationsДокумент6 страницComplementary Pass-Transistor Energy Recovery Logic For Low-Power Applicationshuuzr425Оценок пока нет

- Low Power Adiabatic Logic Design: G.P.S. Prashanti, N. Navya Sirisha, N. Akhila ReddyДокумент7 страницLow Power Adiabatic Logic Design: G.P.S. Prashanti, N. Navya Sirisha, N. Akhila ReddyprasanthiОценок пока нет

- Adiabatic Implementation On Full Adder Circuits: R.Swapna, Shoban MudeДокумент5 страницAdiabatic Implementation On Full Adder Circuits: R.Swapna, Shoban MudeshrivathsavsОценок пока нет

- Adiabatic Technique For Energy Efficient Logic Circuits DesignДокумент24 страницыAdiabatic Technique For Energy Efficient Logic Circuits Design07291a0461Оценок пока нет

- An Adiabatic Approach For Low Power Full Adder DesДокумент15 страницAn Adiabatic Approach For Low Power Full Adder Dessai tejuswiniОценок пока нет

- IGCT Technology Baseline and Future Opportunities: Peter Steimer, Oscar Apeldoorn, Eric Carroll, Andreas NagelДокумент6 страницIGCT Technology Baseline and Future Opportunities: Peter Steimer, Oscar Apeldoorn, Eric Carroll, Andreas NagelculwavesОценок пока нет

- Cmos Transistor AdderДокумент9 страницCmos Transistor AdderRahul KannojiaОценок пока нет

- Marcelo Baru An ASK Demodulator in CMOS Technology 1998Документ6 страницMarcelo Baru An ASK Demodulator in CMOS Technology 1998marcelobaruОценок пока нет

- 0.5 V Supply Resistorless Voltage Reference For Low Voltage ApplicationsДокумент6 страниц0.5 V Supply Resistorless Voltage Reference For Low Voltage ApplicationsSteven Curly ComalingОценок пока нет

- A Flip-Flop For The DPA Resistant Three-Phase Dual-RailДокумент5 страницA Flip-Flop For The DPA Resistant Three-Phase Dual-RailSethu GeorgeОценок пока нет

- Evaluation of The Transient Overvoltage Stresses On 132 KV Power Transmission NetworkДокумент8 страницEvaluation of The Transient Overvoltage Stresses On 132 KV Power Transmission NetworkIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalОценок пока нет

- A Low-Power and High-Speed Voltage Level Shifter Based On A Regulated Cross-Coupled Pull-Up NetworkДокумент5 страницA Low-Power and High-Speed Voltage Level Shifter Based On A Regulated Cross-Coupled Pull-Up Network15022000rskushalОценок пока нет

- Research Paper IjvesДокумент5 страницResearch Paper Ijveshemendra07Оценок пока нет

- Adiabatic SwitchingДокумент10 страницAdiabatic Switchingdhirajmore88Оценок пока нет

- Edge-Triggered Driver Circuit For Ultra-WidebandДокумент4 страницыEdge-Triggered Driver Circuit For Ultra-WidebandTeeОценок пока нет

- Computer Aided Design of Snubber Circuit For DC/DC Converter With Sic Power Mosfet DevicesДокумент9 страницComputer Aided Design of Snubber Circuit For DC/DC Converter With Sic Power Mosfet DevicesrauolОценок пока нет

- Ultra-Low: Power Silicon-on-Sapphire Energy-ScavengingДокумент4 страницыUltra-Low: Power Silicon-on-Sapphire Energy-ScavengingGurkaranjot SinghОценок пока нет

- FORTRAN Based ApproachДокумент22 страницыFORTRAN Based ApproachGS EKTAОценок пока нет

- A Novel Design of Adder For Ultra Low Power Application: M A, M M K, I BДокумент6 страницA Novel Design of Adder For Ultra Low Power Application: M A, M M K, I BAmeem Ahmed KhanОценок пока нет

- Ultra-Low-Power 2.4 GHZ Colpitts Oscillator Based On Double Feedback TechniqueДокумент4 страницыUltra-Low-Power 2.4 GHZ Colpitts Oscillator Based On Double Feedback TechniqueCamila DamascenoОценок пока нет

- Sub-Pico Joule Switching High-Speed Reliable Cmos Circuits Are FeasibleДокумент11 страницSub-Pico Joule Switching High-Speed Reliable Cmos Circuits Are FeasibleKODOMОценок пока нет

- 05682957Документ4 страницы05682957Praveenkumar ViswanathanОценок пока нет

- Design of A Under Voltage Lock Out Circuit With Bandgap StructureДокумент4 страницыDesign of A Under Voltage Lock Out Circuit With Bandgap Structured_niku100% (1)

- Low Power Ring Oscillator at 180nm CMOS Technology: Aman Shivhare M. K. GuptaДокумент4 страницыLow Power Ring Oscillator at 180nm CMOS Technology: Aman Shivhare M. K. GuptaRam MОценок пока нет

- Final ProjectДокумент5 страницFinal Projectnksharma.naveen1855Оценок пока нет

- 2 Majd2018Документ6 страниц2 Majd2018OmarFaruqeОценок пока нет

- IR-drop Reduction Through Combinational Circuit PartitioningДокумент12 страницIR-drop Reduction Through Combinational Circuit PartitioningPramod Reddy RОценок пока нет

- Line Differential Protection Scheme Modelling (PDF Library)Документ6 страницLine Differential Protection Scheme Modelling (PDF Library)Nirmal RajaОценок пока нет

- Secure Adiabatic Logic: A Low-Energy DPA-Resistant Logic StyleДокумент11 страницSecure Adiabatic Logic: A Low-Energy DPA-Resistant Logic StylevivekgwdОценок пока нет

- 2007 07 A Multi-Mode Power Gating Structure For Low-Voltage Deep-Submicron CMOS ICsДокумент5 страниц2007 07 A Multi-Mode Power Gating Structure For Low-Voltage Deep-Submicron CMOS ICsKuldeep SinghОценок пока нет

- Genetic Algorithm Based 7-Level Step-Up Inverter With Reduced Harmonics and Switching DevicesДокумент17 страницGenetic Algorithm Based 7-Level Step-Up Inverter With Reduced Harmonics and Switching DevicesMasudur RahmanОценок пока нет

- Static Power Reduction Techniques For Asynchronous Circuits: Carlos Ortega, Jonathan Tse, and Rajit ManoharДокумент10 страницStatic Power Reduction Techniques For Asynchronous Circuits: Carlos Ortega, Jonathan Tse, and Rajit ManoharK HoneeyОценок пока нет

- Nanometer MOSFETДокумент12 страницNanometer MOSFETSibi ManojОценок пока нет

- A Low-Power 1-V Supply Dynamic ComparatorДокумент4 страницыA Low-Power 1-V Supply Dynamic Comparator22pimt01Оценок пока нет

- Digital CMOS Logic Operation in The Sub-Threshold Region: Hendrawan Soeleman and Kaushik RoyДокумент6 страницDigital CMOS Logic Operation in The Sub-Threshold Region: Hendrawan Soeleman and Kaushik Royphanindra21Оценок пока нет

- Analyzing Energy-Delay Behavior in Room Temperature Single Electron TransistorsДокумент6 страницAnalyzing Energy-Delay Behavior in Room Temperature Single Electron Transistorsveeresh_bitОценок пока нет

- An0002 Efm32 Hardware Design ConsiderationsДокумент16 страницAn0002 Efm32 Hardware Design ConsiderationsRam SakthiОценок пока нет

- A Simple Current-Mode Quadrature Oscillator Using Single CDTAДокумент8 страницA Simple Current-Mode Quadrature Oscillator Using Single CDTAa_damrongОценок пока нет

- Design and Testing of An TCSC For Distribution Network Applications PDFДокумент5 страницDesign and Testing of An TCSC For Distribution Network Applications PDFRuchitaОценок пока нет

- Using Self-Driven AC-DC Synchronous Rectifier As A Direct Replacement For Traditional Power Diode RectifierДокумент10 страницUsing Self-Driven AC-DC Synchronous Rectifier As A Direct Replacement For Traditional Power Diode RectifierdabalejoОценок пока нет

- New Gate Driver Baser Ir2110Документ4 страницыNew Gate Driver Baser Ir2110Ayoub RajawiОценок пока нет

- Fundamentals of Adiabatic Logic: 2.1 The Charging Process in Adiabatic Logic Compared To Static CMOSДокумент19 страницFundamentals of Adiabatic Logic: 2.1 The Charging Process in Adiabatic Logic Compared To Static CMOSparsa_coaОценок пока нет

- Low-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationДокумент4 страницыLow-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationwhamcОценок пока нет

- SurajpaperДокумент79 страницSurajpaperSooraj SattirajuОценок пока нет

- Abstract: Ultra-Low Power Phase Locked LoopsДокумент4 страницыAbstract: Ultra-Low Power Phase Locked LoopsRizwan Shaik PeerlaОценок пока нет

- 10-Bit 30-MSs SAR ADC Using A SwitchbackДокумент5 страниц10-Bit 30-MSs SAR ADC Using A SwitchbackSethu GeorgeОценок пока нет

- High-Performance D/A-Converters: Application to Digital TransceiversОт EverandHigh-Performance D/A-Converters: Application to Digital TransceiversОценок пока нет

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsОт EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsРейтинг: 3 из 5 звезд3/5 (2)

- INT213Документ30 страницINT213Dr-Irfan Ahmad Pindoo0% (1)

- Unit 2 ACДокумент8 страницUnit 2 ACDr-Irfan Ahmad PindooОценок пока нет

- Syllabus: Unit 2: Tunnel Diodes, Clampers, Zener Diodes Numericals and LED Unit 3: All Except Dtransistor SwitchingДокумент1 страницаSyllabus: Unit 2: Tunnel Diodes, Clampers, Zener Diodes Numericals and LED Unit 3: All Except Dtransistor SwitchingDr-Irfan Ahmad PindooОценок пока нет

- SRAM ArchitectureДокумент35 страницSRAM ArchitectureDr-Irfan Ahmad PindooОценок пока нет

- GMP Male BearingДокумент3 страницыGMP Male BearingMahdi HajizadehОценок пока нет

- Esquema Elétrico NGD 9.3Документ2 страницыEsquema Elétrico NGD 9.3LuisCarlosKovalchuk100% (1)

- 1998-10 The Computer Paper - Ontario EditionДокумент156 страниц1998-10 The Computer Paper - Ontario Editionthecomputerpaper100% (1)

- Estimation Software For Presure VesselДокумент36 страницEstimation Software For Presure VesselKarthikeyan Shanmugavel0% (1)

- TD Quintolubric 888 68Документ2 страницыTD Quintolubric 888 68Haitham YoussefОценок пока нет

- AquaCal Tropical Brochure PDFДокумент2 страницыAquaCal Tropical Brochure PDFJC ParedesОценок пока нет

- Manual PC Soundcard Scope 1.4.5Документ17 страницManual PC Soundcard Scope 1.4.5NatashaKillerОценок пока нет

- Order Qty Vs Dispatch Plan - 04 11 20Документ13 страницOrder Qty Vs Dispatch Plan - 04 11 20NPD1 JAKAPОценок пока нет

- Stair Cases DesignДокумент19 страницStair Cases DesignWrishad Zia93% (14)

- Kathir CollegeДокумент3 страницыKathir Collegeshanjuneo17Оценок пока нет

- Electronic Dice Using LEDs Electrical Engineering ProjectДокумент16 страницElectronic Dice Using LEDs Electrical Engineering Projectprakhar agarwal33% (3)

- PBLauncherДокумент50 страницPBLauncherborreveroОценок пока нет

- User'S Manual: Capstone MicroturbineДокумент56 страницUser'S Manual: Capstone MicroturbinemassimocalviОценок пока нет

- A Sample of Wet Soil Has A Volume of 0Документ8 страницA Sample of Wet Soil Has A Volume of 0eph0% (1)

- Materials Today: Proceedings: Avula Suresh, T. Nancharaiah, Ravikumar Dumpala, B. Ratna SunilДокумент5 страницMaterials Today: Proceedings: Avula Suresh, T. Nancharaiah, Ravikumar Dumpala, B. Ratna SunilBart MaxОценок пока нет

- Oracle Jrockit Mission Control Lab GuideДокумент17 страницOracle Jrockit Mission Control Lab GuideashuhegdeОценок пока нет

- Published Document Guidance On The Use of BS EN 13108, Bituminous Mixtures - Material SpecificationsДокумент8 страницPublished Document Guidance On The Use of BS EN 13108, Bituminous Mixtures - Material SpecificationsCristián JiménezОценок пока нет

- " " Reach: Ordering InformationДокумент8 страниц" " Reach: Ordering InformationTrong TranОценок пока нет

- Chemical Thermodynamics: Theodore L. Brown H. Eugene Lemay, Jr. and Bruce E. BurstenДокумент43 страницыChemical Thermodynamics: Theodore L. Brown H. Eugene Lemay, Jr. and Bruce E. BurstenChery-an PletОценок пока нет

- Slope Stability in Slightly Fissured Claystones and MarlsДокумент25 страницSlope Stability in Slightly Fissured Claystones and MarlsrullyirwandiОценок пока нет

- U042en PDFДокумент12 страницU042en PDFTatiya TatiyasoponОценок пока нет

- Gordon NovelДокумент50 страницGordon NovelNic Hotep100% (2)

- Magneto Hydro Dynamics PresentationДокумент19 страницMagneto Hydro Dynamics PresentationVipul GuptaОценок пока нет

- Standardization of Naoh 1Документ3 страницыStandardization of Naoh 1api-309208977Оценок пока нет

- Final Reporting GuidelinesДокумент183 страницыFinal Reporting GuidelinesAkhmad NuzulОценок пока нет

- 8J Summary SheetДокумент2 страницы8J Summary Sheet박찬우Оценок пока нет

- Online Order Processing SystemДокумент34 страницыOnline Order Processing SystemMuhammad ShujaОценок пока нет

- Mauser 98K - Model 48 Rifle ManualДокумент20 страницMauser 98K - Model 48 Rifle ManualMeor Amri96% (28)

- Cisco Network DiagramДокумент1 страницаCisco Network DiagramĐỗ DuyОценок пока нет