Академический Документы

Профессиональный Документы

Культура Документы

DFT Syllabus

Загружено:

Sanmati JainОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

DFT Syllabus

Загружено:

Sanmati JainАвторское право:

Доступные форматы

Introduction

CurrentIssueswith Test

Fault Models

Introduction Behavioral Level / Gate Level (RTL) / Component Level

Types of Fault Models examples detailed

(DC) Stuck-at

Opens

Bridging

Functional

Toggle

Parametric

(AC) Transition Delay

Path Delay

Automatic Test Pattern Generation

What is ATPG?

Structural Test

Overview of the ATPG process

Targets Cone of Logic

Injecting Faults

Generating Vectors examples using various Fault Models

D and Dbar Notation

Sensitive Paths

Reconvergent Fanouts

Reconvergent Inputs

Student Exercise determine pathways and conditions

ATPG vector validation

Fault Coverage / Fault Grading

Benefits of ATPG

Design For Test (DFT) Introduction

Functional vs. Structural Test

Phases of Test

Vectors Functional / Application / Parallel / Broadside

Vectors Structural / Scan

Ad-Hoc vs. Structured DFT

DFT methods

Full Scan vs. Partial Scan

DFT benefits

DC Scan

Implementing Logic Scan

Flops Mux-D, LSSD, Two Clock Scan Flops

ATPG and Scan Logic

Single, Multiple Chains (example data)

Scan Terminology

Scan Timing Diagrams detailed waveforms, timing values, timing sequences

Shared Scan interface functions

Shifting Scan Data whats important, ways shifting can fail

Testing Scan Logic Scan integrity tests

Data Alignment Issues examples, keeping it correct

Why DC Scan Tests Fail

Scan Design / Test Data/ Test Application/ Device

AC Scan

Why perform AC Scan?

High Frequency AC Scan

Delay Fault Models and AC Scan

Delay Path Distribution

Path Delay Example Ideal Case

Transition Delay Example

Dynamic Hazards

Robust Delay Rules, Tests examples of good/bad

AC Scan Terminology Controlling/Non-controlling/Enabling/On-Path/Off-Path

Delay Test Examples

Strategies for Delay Tests

How AC Scan works

Launch On Shift (L-O-S)

LOS detailed timing

LOS test generation and associated issues

Functional Launch (Launch on Capture LOC)

Functional Launch detailed timing

Functional Launch test generation and associated issues

AC Scan Debug

Using AC Scan to make Timing Measurements

Low Voltage Stress Effects

Clocks and Phase Lock Loops (PLL)

PLL basics

Chop Clocks

Using Chop Clocks to generate Shift/Launch/Capture sequences

Boundary Scan 1149.1 IEEE Standard JTAG

Introduction to Boundary Scan and the JTAG team

Why it was needed (PCB test requirements)

The IEEE 1149.1 Standard whats defined

The Boundary Scan Register functions

TAP Controller and dedicated pins

TAP 16 State Machine

TAP Operations

Boundary Scan Instructions

Instruction Behavior

Boundary Scan Register hardware

Bypass Register

Identification Register

BS Timing Instruction Load

BS Timing Data Scan

Using BS for parametric tests VOH/VOL/VIL/VIH/IOZL/IOZH

Another look at In-Circuit Test (PCB test addressed)

Built-In Self Test (BIST)

BIST defined

BIST applications

Memory BIST Architecture, Algorithms

Logic BIST Architecture

Pseudo-Random-Pattern-Generation (PRPG)

Linear Feedback Shift Register (LFSR)

LFSR designs: Type 1 & 2, Pattern Sequences

Seed Codes, Polynomials

Correlated Data Issues

Phase Shifters, Spreaders, Broadcasters

Output Compression Multiple Input Shift Registers (MISR)

Output Signature

Logic BIST Test Sequence

BIST Clocking

IO BIST Reduced Pin Count Testing (RPCT)

Why IO BIST

Reduced Pin Count Testing, whats involved

IO BIST pin circuitry

No Contact Shorts Test

Basic IO Functional Test (VOL/VOH/VIL/VIH) no contact

IIL/IIH No Contact Leakage Tests

IO Loop Back Test

DFT and ATE systems

ATE system overview types of test systems

Uses for each type of system

Introduction to DFT ATE

What DFT ATE is designed for (capabilities/limitations)

Faults

Scan

Debug

IDDQ

MBIST

IEEE

compression techniques, Serdes,LNC,Shadow

S@,transition

Clocking,LOC,LOS,LO pipelineS

CG gating,latch

Low power

Coverage improvement

Pattern count reduction

broken chain

Simulation

ATE fails

JTAG

Boundary Scan

IEE1500 WBR TAM

clock grouping

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- DFTДокумент32 страницыDFTjeevithpaul100% (1)

- Letter of Recommendation Sample 2Документ1 страницаLetter of Recommendation Sample 2saman702702100% (1)

- Advsopstem PDFДокумент39 страницAdvsopstem PDFjohnОценок пока нет

- Guidelines For Writing Reco (19th Item) PDFДокумент2 страницыGuidelines For Writing Reco (19th Item) PDFSalmaanCadeXaajiОценок пока нет

- Subject: Regarding The Financial Documentation of Support: Applicant Name: Shivam Patel. Online Application ID: ShivashpДокумент1 страницаSubject: Regarding The Financial Documentation of Support: Applicant Name: Shivam Patel. Online Application ID: Shivashpvignesh270991Оценок пока нет

- DFT FAQsДокумент2 страницыDFT FAQsSanmati JainОценок пока нет

- Count Your Stress LevelДокумент8 страницCount Your Stress LevelSanmati JainОценок пока нет

- Admission Essay PreviewДокумент6 страницAdmission Essay Previewapi-3815459100% (1)

- Lab 2: Logic Gates / Simulation Software: EIE2810 Digital Systems Design LaboratoryДокумент10 страницLab 2: Logic Gates / Simulation Software: EIE2810 Digital Systems Design LaboratoryYabin CHENGОценок пока нет

- Types of SimulationДокумент3 страницыTypes of Simulationhumtum_shri573667% (3)

- Mosfet: Presented by Vivek Krishna Kannan Siddarth Ram Mohan ArunДокумент15 страницMosfet: Presented by Vivek Krishna Kannan Siddarth Ram Mohan ArunMushaim AfreenОценок пока нет

- AI-Thinker RHF-76-052 Hardware Design Guide v01 PDFДокумент10 страницAI-Thinker RHF-76-052 Hardware Design Guide v01 PDFJuan SanchezОценок пока нет

- Project 2 Technical Definition and DescriptionДокумент5 страницProject 2 Technical Definition and Descriptionapi-302916816Оценок пока нет

- CH 08Документ82 страницыCH 08Luis Eduardo García QuesadaОценок пока нет

- XC836 Data SheetДокумент56 страницXC836 Data SheetNegru AndreiОценок пока нет

- PIC Base A9Документ28 страницPIC Base A9Alfonso NiñoОценок пока нет

- ASUS X51RL Rev.2.00 Schematic DiagramДокумент64 страницыASUS X51RL Rev.2.00 Schematic Diagramqueequeg73100% (1)

- Enhanced Emir Flow Development PDFДокумент58 страницEnhanced Emir Flow Development PDFJagadish KgОценок пока нет

- Block Diagram of MotherboardДокумент9 страницBlock Diagram of MotherboardJay Zala0% (1)

- System-On-Chip Design Book 2019 200dpi AwДокумент334 страницыSystem-On-Chip Design Book 2019 200dpi AwAndrea SpitaleОценок пока нет

- Module 5 - Combinational Logic Digital Arithmetic CircuitsДокумент15 страницModule 5 - Combinational Logic Digital Arithmetic CircuitsPatrick Joshua GlimadaОценок пока нет

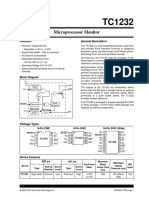

- TC1232Документ24 страницыTC1232efremofeОценок пока нет

- aIVR1004 2104 4208Документ8 страницaIVR1004 2104 4208huytung1501Оценок пока нет

- MindShare x86 ISAДокумент1 567 страницMindShare x86 ISArrs_1988100% (3)

- Libraryparts PDFДокумент2 страницыLibraryparts PDFsatheesh_240Оценок пока нет

- 10022Документ262 страницы10022Dan EsentherОценок пока нет

- EE 533 Lab #10: Convertible First-In First-Out (SRAM) MemoryДокумент1 страницаEE 533 Lab #10: Convertible First-In First-Out (SRAM) MemoryPokemonponponОценок пока нет

- Computer Science Solved Past Paper For IGCSE EDEXCELДокумент4 страницыComputer Science Solved Past Paper For IGCSE EDEXCELaayanshehzad09Оценок пока нет

- Advent 4211B NetbookДокумент8 страницAdvent 4211B NetbookCarlos ValverdeОценок пока нет

- PIC18F97J60 Family Data SheetДокумент476 страницPIC18F97J60 Family Data SheetcoccomОценок пока нет

- 280 Lab 8 Task 2 AsmДокумент15 страниц280 Lab 8 Task 2 AsmBasselM.ElAmineОценок пока нет

- 4017 & 4026Документ3 страницы4017 & 4026Ronny SinagaОценок пока нет

- Request Letter For ComputerДокумент3 страницыRequest Letter For ComputerLiza Marie NeryОценок пока нет

- Intel 8255Документ7 страницIntel 8255shida67Оценок пока нет

- Advance Digital Design Using VeilogДокумент99 страницAdvance Digital Design Using Veilogpcjoshi02Оценок пока нет

- HP Mini 110 Inventec 6050A2262301-MB-A03 BIXBY1.1 MV Rev A SchematicsДокумент56 страницHP Mini 110 Inventec 6050A2262301-MB-A03 BIXBY1.1 MV Rev A SchematicsJose Miguel Rivera MaresОценок пока нет

- KIM 1 Microprocessor Fundamentals PDFДокумент244 страницыKIM 1 Microprocessor Fundamentals PDFAli AHОценок пока нет

- Computer Organization & ArchitectureДокумент37 страницComputer Organization & ArchitectureHardik DarjiОценок пока нет