Академический Документы

Профессиональный Документы

Культура Документы

Circuitos lógicos para funciones combinacionales

Загружено:

hvillafuerteb0 оценок0% нашли этот документ полезным (0 голосов)

98 просмотров3 страницыsistemas digitales

Оригинальное название

Prob3

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документsistemas digitales

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

98 просмотров3 страницыCircuitos lógicos para funciones combinacionales

Загружено:

hvillafuertebsistemas digitales

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 3

1.

- a) Sea la funcin lgica de 3 variables:

f ( a, b, c ) = (3, 5, 7)

codificadores de prioridad 148 , 2 convertidores de cdigo 48 y dos

displays. Utilizar las puertas lgicas que sean necesarias.

b)

Implementarla con un multiplexor 151.

Sea la funcin lgica de cuatro variables:

f ( a, b, c, d ) = ( 0, 2, 4, 5, 6,11,12,14 )

4

Implementarla con un multiplexor 151 y un inversor.

2. - Disear:

a) Un circuito sumador-restador de 3 bits y signo. Utilizar para ello un

circuito sumador 83 y las puertas XOR que sean necesarias.

b) Un detector de rebasamiento para el sumador-restador del apartado

anterior.

c) Basndose en el circuito diseado en los apartados anteriores, un

sumador-restador de 7 bits y signo con detector de rebasamiento.

3. - Se dispone de 2 circuitos integrados. El primero de ellos contiene dos

sumadores completos de 2 bits, y el segundo es un multiplexor 151.

Utilizando los 2 circuitos anteriores y los inversores que se precisen, disear

un circuito capaz de detectar la presencia de 3 y slo 3 bits a "1", en palabras

de 6 bits en paralelo.

6. - Disear un multiplexor de 16 canales o vas I0 ...I15 de 1 bit cada uno a partir

de 2 multiplexores 151 con las siguientes caractersticas:

a) Cuando los multiplexores 151 estn deshabilitados, su salida est en

alta impedancia.

b) Cuando los multiplexores 151 estn deshabilitados, sus salidas estn

en el nivel lgico 0.

c) Cuando los multiplexores 151 estn deshabilitados, sus salidas estn

en el nivel lgico 1.

Emplear las puertas lgicas que sean necesarias.

7. - Disear un circuito que realice la suma del nmero A de 4 bits con el mayor

de dos nmeros B y C (tambin de 4 bits). Todos los nmeros estn

codificados en el sistema binario natural. Si los nmeros B y C son iguales,

el resultado ha de ser igual al nmero A. Utilizar los circuitos

combinacionales integrados que sean necesarios.

4. - Utilizando sumadores binarios de dos nmeros de 4 bits (por ejemplo SUM

83), y puertas lgicas AND, disear un circuito combinacional capaz de

multiplicar 2 nmeros codificados en binario natural de 4 bits cada uno.

Considerar que el algoritmo de multiplicacin de dos nmeros codificados

en binario natural es el mismo que el de la multiplicacin decimal.

8. - Uno de los circuitos aritmticos ms usados es el sumador binario de 4 bits

en paralelo 83.

Basndose en este circuito se desea disear un sumador aritmtico en cdigo

BCD para nmeros positivos de 2 cifras (del 00 al 99).

Explicar detalladamente el proceso de suma en BCD y disear un sumador

BCD utilizando sumadores 83 junto con las puertas lgicas que sean

necesarias.

5. - Sea un sistema digital que dispone de 16 lneas de peticin de servicio activas

en baja. Disear un circuito que nos muestre a travs de 2 displays el

nmero de la lnea de peticin de servicio de mayor prioridad activa en cada

instante. Si no hay ninguna activa, no mostrar nada. Hacer el diseo con 2

9. Un desplazador de tambor de 4 bits es un circuito combinacional con 4

entradas de datos (D3 D2 D1 D0), 2 entradas de control (C1 C0) y 4 salidas (Z3

Z2 Z1 Z0) donde la palabra saliente es igual a la palabra entrante rotada a la

derecha el nmero de bits especificado por las entradas de control. Por

1/1

ejemplo, si la palabra entrante es D3D2D1D0=ABCD y los controles son

C1C0=11, la palabra de salida es Z3Z2Z1Z0=BCDA. Disear el desplazador

de tambor utilizando combinacionales integrados.

10. Implementar un comparador para nmeros de 4 bits en complemento a 2

utilizando un comparador binario 85 y las puertas lgicas que sean

necesarias.

11.- Para entrar en un recinto hay que atravesar 2 puertas, P1 y P2. Se desea

disear un circuito digital como el de la figura para controlar su acceso. Para

abrir P1 hay que introducir un nmero BCD A=(A3A2A1A0) mayor o igual a

6 por las entradas A de un circuito digital. Este nmero A accionar la salida

Z1 (Z1=1) y ser memorizado en un registro del sistema. Una vez abierta la

puerta P1, un pasillo conduce a la puerta P2. Para abrir la puerta P2 por las

entradas B del circuito hay que introducir un nmero BCD B=(B3B2B1B0)

que debe estar comprendido entre 2 unidades por arriba o por debajo de la

mitad por defecto del nmero introducido para abrir la puerta P1. Esta

accin har que la salida Z2 se active (Z2=1) y se abra la puerta P2. Por

ejemplo, si el nmero A = 8 (1000) se abrir la puerta P1 y el nmero B

tendr que estar comprendido entre 2 (0010) y 6 (0110), ambos inclusive,

para abrir P2.

12.- Disear un mdulo sumador completo con entradas A, B y acarreo de

entrada Cin y salidas S (bit de suma) y acarreo de salida Cout utilizando:

a) Dos decodificadores genricos de 3 entradas y salidas activas en alta y

dos puertas NOR del nmero de entradas que se precisen.

b) Un nico multiplexor de 4 entradas de 2 bits por entrada y un inversor.

13.- Disear utilizando exclusivamente puertas NOR la funcin f(D, C, B, A)

definida por el siguiente circuito de multiplexores teniendo en cuenta que en

los multiplexores 4 a 1 A es el bit de mayor peso (21) y B el de menor peso

(20):

Circuito Digital

Z1

4

Registro

B

CircComb

Z2

Disear la parte combinacional del circuito utilizando los circuitos integrados

que se precisen (sumadores, comparadores, multiplexores, etc). Comprobar

que no se producen situaciones de error en ningn caso. Qu valores deben

tomar las entradas A y B por defecto, es decir, cuando no se est

introduciendo ningn nmero, para que las puertas permanezcan cerradas?

2/2

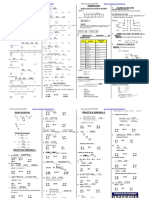

14.- Determinar la funcin realizada por el circuito de la figura. Redisearlo

utilizando exclusivamente puertas NAND. (FA full adder sumador

completo)

16.- Determinar la funcin que realiza el circuito de la figura (1 punto).

I0

I1

I2

I3

A0

A1

A2

A3

X

A1

Y

Z

A0

DECODIFICADOR

15.- Hallar la expresin mnima de F como producto de sumas (1 punto).

O2

O3

83

Z0

Z1

Z2

Z3

CO

CI

O0

O1

B0

B1

B2

B3

S0

S1

S

SUM S2

3

B0 A/B

B1

B2

O0

B3

MUX O1

O

A0 157 2

O3

A1

A2

A3 E

17.- Disear un multiplexor de 8 entradas de 1 bit cada una utilizando 2

multiplexores de 4 entradas de 1 bit cada una, dos puertas triestado con

entrada de habilitacin activa en alta y un inversor. Indicar claramente el

nombre de todos los terminales implicados en el diseo as como sus

conexiones.

18.- Disear un circuito que proporcione el valor absoluto de un nmero de 4 bits

escrito en complemento a dos. Utilizar para ello 4 sumadores completos,

cuatro multiplexores de 2 entradas de 1 bit y 4 inversores. Indicar

claramente el nombre de todos los terminales implicados en el diseo as

como sus conexiones.

3/3

Вам также может понравиться

- Problemas de circuitos digitalesДокумент14 страницProblemas de circuitos digitalesJessica Karina Farinango UshiñaОценок пока нет

- Ejercicios de Aplicación de Sistemas CombinacionalesДокумент5 страницEjercicios de Aplicación de Sistemas CombinacionalesgglrОценок пока нет

- Problemas 5Документ5 страницProblemas 5EberSantaCruzBerriosОценок пока нет

- CIRCUITOS COMBINACIONALESДокумент6 страницCIRCUITOS COMBINACIONALESJoeliTo VeraОценок пока нет

- Prob 3 BДокумент16 страницProb 3 BLeandro SchenoneОценок пока нет

- Tema5 2Документ10 страницTema5 2FerchoОценок пока нет

- Deber 2 - SIstemas Digitales - Carlos NovilloДокумент5 страницDeber 2 - SIstemas Digitales - Carlos NovilloWilson Francisco BritoОценок пока нет

- Trabajo Practico Sobre MSIДокумент19 страницTrabajo Practico Sobre MSImigofОценок пока нет

- Algebra BooleanaДокумент9 страницAlgebra Booleanavargasc7Оценок пока нет

- Ejercicios DigitalesДокумент7 страницEjercicios DigitalesAlvaro SanchezОценок пока нет

- Sistemas combinacionales: problemas de diseño digitalДокумент5 страницSistemas combinacionales: problemas de diseño digitalAlex WongОценок пока нет

- Taller Ejercicios Unidad5Документ4 страницыTaller Ejercicios Unidad5STEVEN ANDRES NUNEZ GOMEZОценок пока нет

- Problemas Tema 4Документ18 страницProblemas Tema 4Yani Ivanov ManovОценок пока нет

- Guia Sistemas LogicosДокумент13 страницGuia Sistemas LogicosGian Franco IemmaОценок пока нет

- 01 GuiaCombinacionalesДокумент8 страниц01 GuiaCombinacionalesCesar Lautaro AngeloffОценок пока нет

- Diseño lógico serie modificadaДокумент2 страницыDiseño lógico serie modificadaBlacksimb CanalОценок пока нет

- Laboratorio 3Документ13 страницLaboratorio 3jorge perezОценок пока нет

- Taller UAOДокумент3 страницыTaller UAOJose David CastroОценок пока нет

- Informe Previo N°5Документ20 страницInforme Previo N°5Hubert Vásquez CuevaОценок пока нет

- Unidad 4. Lógica Combinacional CircuitosДокумент17 страницUnidad 4. Lógica Combinacional CircuitosAlejandro PerezОценок пока нет

- Prob Elct Digital IIДокумент25 страницProb Elct Digital IIEsteban RiquelmeОценок пока нет

- ProblemasCircuitosCombinacionales 072012Документ5 страницProblemasCircuitosCombinacionales 072012Santiago GuallichicoОценок пока нет

- Circuitos digitales DAC conversión temperaturaДокумент2 страницыCircuitos digitales DAC conversión temperaturaRonaldo PaipaОценок пока нет

- Convertidor B-H P4Документ17 страницConvertidor B-H P4Jorge Alberto Ortiz GalloОценок пока нет

- TP07 Diseño Con MSI 2019Документ7 страницTP07 Diseño Con MSI 2019JonatanArtalОценок пока нет

- Problemas Circuitos Combinacionales 0506Документ6 страницProblemas Circuitos Combinacionales 0506Abner Isaac RomeroОценок пока нет

- Contadores digitales con CI estándarДокумент33 страницыContadores digitales con CI estándarMiguelTesenRomeroОценок пока нет

- Digitales. Sumador.Документ17 страницDigitales. Sumador.greomerОценок пока нет

- Decodificadores y circuitos combinacionalesДокумент6 страницDecodificadores y circuitos combinacionalesManuel Campos BorrasОценок пока нет

- Ejercicios de Codificadores y Circuitos LógicosДокумент6 страницEjercicios de Codificadores y Circuitos LógicosAngel MelaraОценок пока нет

- En Word REPASO EX FINALДокумент3 страницыEn Word REPASO EX FINALCriss-tian Eduardo Estupiñan VasquezОценок пока нет

- T2 EjerciciosДокумент6 страницT2 EjerciciosHernan Ali LopezОценок пока нет

- UNI Nac Ing Eléctrica: Circuitos lógicos y displays 7 segmentosДокумент29 страницUNI Nac Ing Eléctrica: Circuitos lógicos y displays 7 segmentosJosue Cornelio PОценок пока нет

- Circuitos_combinacionalesДокумент19 страницCircuitos_combinacionalescc ddОценок пока нет

- Circuito combinacional: análisis y componentesДокумент44 страницыCircuito combinacional: análisis y componentesKim SungОценок пока нет

- Practico 6Документ3 страницыPractico 6Ronald Requejo Samame100% (2)

- Trabajo de Logica Digital DecodificadoresДокумент12 страницTrabajo de Logica Digital DecodificadoreskarenpadronОценок пока нет

- Ejercicios Cir Comb 1raPP (07-08)Документ6 страницEjercicios Cir Comb 1raPP (07-08)Yenisley Padrón GonzálezОценок пока нет

- Informe Sumador y Restador 1Документ21 страницаInforme Sumador y Restador 1Mery VelásquezОценок пока нет

- Final 3Документ12 страницFinal 3Felipe CarreñoОценок пока нет

- Elementos A UtilizarДокумент10 страницElementos A Utilizarisailv18Оценок пока нет

- Informe Practica 4 SimuladaДокумент9 страницInforme Practica 4 SimuladaJuan Jose Eraso DelgadoОценок пока нет

- Problemas Diseño Combinacionales PDFДокумент7 страницProblemas Diseño Combinacionales PDFXiomaraОценок пока нет

- Taller Grupal Tercer CorteДокумент8 страницTaller Grupal Tercer CorteAstrid DayannaОценок пока нет

- Qdoc - Tips Sistemas-Digitales PDFДокумент35 страницQdoc - Tips Sistemas-Digitales PDFLuisa FernandaОценок пока нет

- Tipos de CircuitosДокумент11 страницTipos de Circuitosalonsoalex25Оценок пока нет

- Informe Lab. 1 DigitalesДокумент7 страницInforme Lab. 1 DigitalesFabio AyalaОценок пока нет

- Ejercicios CombinДокумент3 страницыEjercicios Combinjose manuelОценок пока нет

- Cuestionario Examen FinalДокумент6 страницCuestionario Examen FinalDiego Manjarres BurgosОценок пока нет

- Boletin 2Документ4 страницыBoletin 2Jose Teijeiro CruzОценок пока нет

- Problem Ass DigДокумент107 страницProblem Ass DigYani Ivanov ManovОценок пока нет

- Sumadores, comparadores y decodificadores digitalesДокумент4 страницыSumadores, comparadores y decodificadores digitalesVictor Castrejon100% (3)

- Contador DigitalДокумент12 страницContador DigitalSaulRosalОценок пока нет

- Circuitos Aritméticos 5Документ14 страницCircuitos Aritméticos 5John QueralesОценок пока нет

- Sistemas DigitalesДокумент10 страницSistemas DigitalesIsrael SologurenОценок пока нет

- Como Hacer Un ContadorДокумент12 страницComo Hacer Un ContadorBeastrid Urbaez OvallesОценок пока нет

- Diseño circuito multiplicador 4x2 bitsДокумент27 страницDiseño circuito multiplicador 4x2 bitsHenry TipanОценок пока нет

- Simulación de circuitos electrónicos con OrCAD® PSpice®От EverandSimulación de circuitos electrónicos con OrCAD® PSpice®Оценок пока нет

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiОт EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiРейтинг: 5 из 5 звезд5/5 (1)

- Aseguramiento de La CalidadДокумент1 страницаAseguramiento de La CalidadhvillafuertebОценок пока нет

- Enrique Eduardo Tarifa - Teoría de Modelos y Simulación PDFДокумент17 страницEnrique Eduardo Tarifa - Teoría de Modelos y Simulación PDFAndreamОценок пока нет

- Analysis and Simulation of Waiting Times by Applying Queuing Theory in A Transport TerminalДокумент10 страницAnalysis and Simulation of Waiting Times by Applying Queuing Theory in A Transport TerminalhvillafuertebОценок пока нет

- CI2 Intermedio 2017-18 Netiqueta PDFДокумент12 страницCI2 Intermedio 2017-18 Netiqueta PDFjorge camachoОценок пока нет

- Crisi Venezolana VДокумент2 страницыCrisi Venezolana VhvillafuertebОценок пока нет

- Ejemplos de Llenado Anexo 1 y Anexo 2 (Carga Lectiva y No Lectiva)Документ9 страницEjemplos de Llenado Anexo 1 y Anexo 2 (Carga Lectiva y No Lectiva)hvillafuertebОценок пока нет

- SUMILLAДокумент1 страницаSUMILLAhvillafuertebОценок пока нет

- Escaneos SnortДокумент3 страницыEscaneos SnortJorge GuerronОценок пока нет

- Transparencias SRDДокумент230 страницTransparencias SRDAngel Manuel Ruiz DominguesОценок пока нет

- Bisección Con MacrosДокумент2 страницыBisección Con MacroshvillafuertebОценок пока нет

- Elabcitas PDFДокумент20 страницElabcitas PDFhvillafuertebОценок пока нет

- Análisis de Error para Los Métodos Iterativos - 1Документ11 страницAnálisis de Error para Los Métodos Iterativos - 1Milagros VegaОценок пока нет

- Magerit v3 Libro1 MetodoДокумент127 страницMagerit v3 Libro1 MetodoAnonymous ul5cehОценок пока нет

- Criptografía y Métodos de CifradoДокумент19 страницCriptografía y Métodos de CifradoGili MartinezОценок пока нет

- 89 13 970 1 10 20171213Документ41 страница89 13 970 1 10 20171213hvillafuertebОценок пока нет

- Manual Radio MobileДокумент31 страницаManual Radio MobilesoylacabezaОценок пока нет

- ADC Cuantificando Identidades en LatAmДокумент25 страницADC Cuantificando Identidades en LatAmhvillafuertebОценок пока нет

- RP Blockchain Security RisksДокумент28 страницRP Blockchain Security RiskshvillafuertebОценок пока нет

- 06 Smic EsteДокумент18 страниц06 Smic EstehvillafuertebОценок пока нет

- Seguridad Salud TrabajoДокумент4 страницыSeguridad Salud TrabajoMaria PerezОценок пока нет

- Aprueban La Definición de Seguridad Digital en El Ámbito NacionalДокумент2 страницыAprueban La Definición de Seguridad Digital en El Ámbito NacionalFidel Francisco Quispe HinostrozaОценок пока нет

- JARDINESДокумент10 страницJARDINEShvillafuertebОценок пока нет

- Residencial PerseoДокумент26 страницResidencial PerseoPauloThiagoОценок пока нет

- Alfonso Amador Sotomayor - Administración de Recursos Humanos - Su Proceso Organizacional 2016 PDFДокумент462 страницыAlfonso Amador Sotomayor - Administración de Recursos Humanos - Su Proceso Organizacional 2016 PDFMonica Yineth100% (2)

- CNE Codigo Nacional de ElectricidadДокумент839 страницCNE Codigo Nacional de Electricidadtramirezs83% (12)

- Mineria de Datos 1Документ18 страницMineria de Datos 1Leviatan ErmilsonОценок пока нет

- Manual de Redes de Virtual BoxДокумент27 страницManual de Redes de Virtual Boxmcmcx100% (1)

- Informe Tecnico Evaluacion Software Herramientas de DesarrolloДокумент3 страницыInforme Tecnico Evaluacion Software Herramientas de DesarrollohvillafuertebОценок пока нет

- Parcial1 PDFДокумент24 страницыParcial1 PDFgabyОценок пока нет

- Cursos Certificados para BiДокумент7 страницCursos Certificados para BihvillafuertebОценок пока нет

- 3er Grado Matemáticas (2019-2020)Документ40 страниц3er Grado Matemáticas (2019-2020)Rod Oda ZenОценок пока нет

- Guia Nº3 - Intervalos de LongitudДокумент7 страницGuia Nº3 - Intervalos de Longitudmonica mendoza galvezОценок пока нет

- Medidas AngulДокумент3 страницыMedidas AngulEdwar Jhon Chacon AlayaОценок пока нет

- Boletin 01 - Sistemas de Numeracion I - Sistemas de Numeracion IIДокумент7 страницBoletin 01 - Sistemas de Numeracion I - Sistemas de Numeracion IIArmando Terrones YoplaОценок пока нет

- Manejo de Punto Flotante en Pic Basic Pro PlusДокумент14 страницManejo de Punto Flotante en Pic Basic Pro PlusFatality Joseph100% (1)

- TIPOS DE NOTACIÓN RENACENTISTA Power PointДокумент10 страницTIPOS DE NOTACIÓN RENACENTISTA Power PointLaura Espejo GarciaОценок пока нет

- Resumen JavaДокумент7 страницResumen JavaJuan AcostaОценок пока нет

- Emoticon Cara Llena de Besos - Búsqueda de GoogleДокумент1 страницаEmoticon Cara Llena de Besos - Búsqueda de Googlegretteljaneth01Оценок пока нет

- Numero RomanosДокумент2 страницыNumero RomanosRobert Summer Ancalli EscobarОценок пока нет

- Binario a HexadecimalДокумент15 страницBinario a HexadecimalJaimelo RodriОценок пока нет

- Alteraciones y TonalidadДокумент4 страницыAlteraciones y TonalidadKevin Otarola PorrasОценок пока нет

- Estudio de La Guitarra Jazz - Ars NovaДокумент9 страницEstudio de La Guitarra Jazz - Ars NovaLuis TovarОценок пока нет

- Lenguaje en Programación C++ - 12Документ2 страницыLenguaje en Programación C++ - 12N.R SquireОценок пока нет

- Tipos de Datos y Variables PDFДокумент6 страницTipos de Datos y Variables PDFFlorencia PorcelОценок пока нет

- Metodo NumericoДокумент27 страницMetodo NumericoRuben FloresОценок пока нет

- Escuchar Leer y Tocar El Saxofón (DIGITALIZADO) .Документ42 страницыEscuchar Leer y Tocar El Saxofón (DIGITALIZADO) .Dali S MОценок пока нет

- Jingle Bells EasyДокумент1 страницаJingle Bells EasyBeatriz VergaraОценок пока нет

- Numeracion Academia Circulo 2014Документ3 страницыNumeracion Academia Circulo 2014Anonymous 7za15o0100% (1)

- Planes Clase Mate 7 MaestroДокумент187 страницPlanes Clase Mate 7 Maestrocashito100060% (5)

- 04 Magnitudes Fisicas IIДокумент2 страницы04 Magnitudes Fisicas IIAndy LilaОценок пока нет

- Manual balanza ASC-ZДокумент9 страницManual balanza ASC-ZDayboJoseGuerreroHernandezОценок пока нет

- Ejercicio de Costos TerminadoДокумент48 страницEjercicio de Costos TerminadoJosé IgnacioОценок пока нет

- Factores de Longitud y SuperficieeДокумент14 страницFactores de Longitud y SuperficieeViviana Karen Lima IrigoyenОценок пока нет

- Historia de Los Números RomanosДокумент4 страницыHistoria de Los Números RomanosJeisonQüirozÜrielesОценок пока нет

- Alfavero RumanoДокумент5 страницAlfavero Rumanocindy Alarcon FicaОценок пока нет

- Material Interactivo de Apoyo para Tercero Del Primer Bimestre - Carmen García IbarraДокумент76 страницMaterial Interactivo de Apoyo para Tercero Del Primer Bimestre - Carmen García IbarraJeancarlos Zendejas Anda89% (38)

- Ejercicios de Lectura RelativaДокумент6 страницEjercicios de Lectura RelativaSony AОценок пока нет

- NSR 2022Документ10 страницNSR 2022sdfgsdfgscdbfsdfgsgОценок пока нет

- Compases Irregulares SibeliusДокумент12 страницCompases Irregulares SibeliusGuillermo González CastilloОценок пока нет

- Tutorial Musescore Chopin Preludio 22Документ11 страницTutorial Musescore Chopin Preludio 22Volodymyr DyzhakОценок пока нет