Академический Документы

Профессиональный Документы

Культура Документы

Syllabus For Short Term FPGA Course

Загружено:

manikkalsiОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Syllabus For Short Term FPGA Course

Загружено:

manikkalsiАвторское право:

Доступные форматы

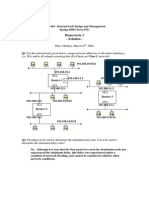

ECE 428 Programmable ASIC Design

Spring 2013

Course Syllabus

Instructor:

Haibo Wang, Room: ENGR E-116, Tel: 453-1522, zhwang@siu.edu

Office Hours: Tuesday and Thursday 2:00 PM - 4:00 PM, Monday 2:30-4:30PM

Textbook:

Steve Kilts, Advanced FPGA Design, Wiley Inter-Science,

ISBN 9780470054376

Reference:

P. Chu, FPGA Prototyping by Verilog Examples, Wiley, 2008

P. Chu, FPGA Prototyping by VHDL Examples, Wiley, 2008 (Library has this

book as e-book)

Xilinx User Manuals and Application Notes

Course Time/Place:

Lecture:

Tuesday & Thursday 4:00AM - 5:15 AM

ENGR A-208

Course website: http://www.engr.siu.edu/~haibo/ece428

Course Description:

The goal of the course is to introduce digital design techniques using field

programmable gate arrays (FPGAs). We will discuss FPGA architecture, digital

design flow using FPGAs, and other technologies associated with field

programmable gate arrays. The course study will involve extensive lab projects

to give students hands-on experience on designing digital systems on FPGA

platforms.

Topics:

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

Introduction to ASICs and FPGAs

Fundamentals in digital IC design

FPGA & CPLD Architectures

FPGA Programming Technologies

FPGA Logic Cell Structures

FPGA Programmable Interconnect and I/O Ports

FPGA Implementation of Combinational Circuits

FPGA Sequential Circuits

Timing Issues in FPGA Synchronous Circuits

Introduction to Verilog HDL and FPGA Design flow with using Verilog HDL

FPGA Arithmetic Circuits

FPGAs in DSP Applications

Design Case Study: Design of SDRAM Controller

Design Case Study: Design of Halftone Pixel Converter

Programming FPGAs in Electronic Systems

Design issues in complex systems containing both FPGA and Microprocessors

Exam Schedule:

Midterm 1

Midterm 2

Final Exam

2/19/13

4/9/13

5/9/13

ECE 428 Programmable ASIC Design

Spring 2013

Grading Policy

Homework

Labs

Class Project

Midterm 1

Midterm 2

Final Exam

A: 100-90,

10%

10%

15%

15%

20%

30%

B: 89-80,

C:79-70,

D:69-60,

F: <60

Class Policy:

1. No late homework, lab & project reports will be accepted except rare cases.

2. No early or makeup exams will be given except rare cases.

3. Rare cases are medical conditions (with Doctors notes), family emergency, and

religious observations. Note that leaving school early for winter break is not qualified

as a rare case.

Lab & Project

1. Four labs will be assigned with focus on Xilinx ISE EDA tools, Spartan prototype

board, how to use users constraints, arithmetic circuits.

2. A large design project will be assigned as the course project.

3. Groups need to be formed to carry out labs and the project. Each group can at most

have two students.

Course online materials

Assignment, exam solutions and supplementary materials will be posted on Desire2learn.

Вам также может понравиться

- Network Management System A Complete Guide - 2020 EditionОт EverandNetwork Management System A Complete Guide - 2020 EditionРейтинг: 5 из 5 звезд5/5 (1)

- DFIG Wind Power Rapid Controller Prototyping System Based On PXI and StarSimДокумент7 страницDFIG Wind Power Rapid Controller Prototyping System Based On PXI and StarSimRoger IlachoqueОценок пока нет

- Free Range VHDLДокумент151 страницаFree Range VHDLpickup666Оценок пока нет

- Electric Circuit Analysis QBДокумент16 страницElectric Circuit Analysis QBboopathy kОценок пока нет

- PIAIC AIoT Q1 Syllabus FinalДокумент3 страницыPIAIC AIoT Q1 Syllabus FinalHammad UrfiОценок пока нет

- Cse Lab Manual NetworksДокумент40 страницCse Lab Manual NetworksLoganathan RmОценок пока нет

- Cisco Packet Tracer ProjectsДокумент4 страницыCisco Packet Tracer ProjectsAlmysariОценок пока нет

- CG Monitors WorkstationДокумент14 страницCG Monitors WorkstationAmbika JaiswalОценок пока нет

- Final Year Project ProposalДокумент1 страницаFinal Year Project ProposalAmirul AizatОценок пока нет

- Cisco Packet Tracer 6.1 FAQsДокумент6 страницCisco Packet Tracer 6.1 FAQspdaboyОценок пока нет

- AOA Analysis of Well Known AlgorithmsДокумент29 страницAOA Analysis of Well Known AlgorithmsBalaji JadhavОценок пока нет

- Unit3pptx 2019 03 05 13 35 22Документ116 страницUnit3pptx 2019 03 05 13 35 22Vishal JoshiОценок пока нет

- Windows Registry PresentationДокумент22 страницыWindows Registry Presentationvoxpop51Оценок пока нет

- BP 09 08 Cover Story KorrДокумент4 страницыBP 09 08 Cover Story KorrmeggioОценок пока нет

- Web Technology Paper MidsДокумент5 страницWeb Technology Paper MidsAbdullah Bin Rauf100% (1)

- Fs LabДокумент52 страницыFs LabMonica SudarshanОценок пока нет

- Mobile Computing Lab ManualДокумент64 страницыMobile Computing Lab Manualvishnu91_k100% (2)

- W3Schools: Angularjs Ajax - $HTTPДокумент12 страницW3Schools: Angularjs Ajax - $HTTPccalin10Оценок пока нет

- Session 13 AO Memory Bounded Heuristic Search Heuristic FunctionsДокумент22 страницыSession 13 AO Memory Bounded Heuristic Search Heuristic FunctionsMarkapuri Santhoash kumarОценок пока нет

- MYD IT Solutions Technical Support Written ExamДокумент2 страницыMYD IT Solutions Technical Support Written Examمحمد يوسفОценок пока нет

- Software Engineering Question BankДокумент71 страницаSoftware Engineering Question BankMAHENDRAОценок пока нет

- Digital Watermarking Using DCT TransformationДокумент12 страницDigital Watermarking Using DCT TransformationTomer FilibaОценок пока нет

- Crystal Report For EclipseДокумент19 страницCrystal Report For Eclipse78roloОценок пока нет

- HAL 102 - LabДокумент43 страницыHAL 102 - LabSyrd MdeОценок пока нет

- Es Lab Manual For M.tech JwfilesДокумент108 страницEs Lab Manual For M.tech JwfilessubbuОценок пока нет

- ASP Net 4 5 Black Book PDFДокумент1 страницаASP Net 4 5 Black Book PDFsrinivas kandregulaОценок пока нет

- Thin ClientДокумент23 страницыThin ClientDevender Rohilla0% (1)

- Umbrella ActivityДокумент14 страницUmbrella ActivityFajri Rakhmat UmbaraОценок пока нет

- School Management System PPT - Soumya - RefrenceДокумент19 страницSchool Management System PPT - Soumya - RefrencetempОценок пока нет

- STK442-110 70W Audio Power Amplifier SpecificationsДокумент4 страницыSTK442-110 70W Audio Power Amplifier SpecificationsIvan AsimovОценок пока нет

- Steganography Project Report For Major Project in B TechДокумент74 страницыSteganography Project Report For Major Project in B Techablond2Оценок пока нет

- Online Feedback Collection SystemДокумент23 страницыOnline Feedback Collection Systempkrmms100% (1)

- Color Detection Using FPGA Based Smart CameraДокумент19 страницColor Detection Using FPGA Based Smart Cameratry199Оценок пока нет

- SE Syllabus DTUДокумент152 страницыSE Syllabus DTUMayukh MaitraОценок пока нет

- Network Programming ImpДокумент5 страницNetwork Programming Impsharath_rakkiОценок пока нет

- Files Homeworks Sol HW3 Coe 444 072Документ2 страницыFiles Homeworks Sol HW3 Coe 444 072Wong VoonyeeОценок пока нет

- Fee Management System PDF FreeДокумент44 страницыFee Management System PDF FreeATUL SHRIVASTAVОценок пока нет

- Student Network Design Projects Using OPNETДокумент7 страницStudent Network Design Projects Using OPNETMoustapha RachidiОценок пока нет

- Panasonic KX-TD500 Users Guide v1Документ442 страницыPanasonic KX-TD500 Users Guide v1Петар ПитаревићОценок пока нет

- DSP Book v300 Extended Preview InternetДокумент303 страницыDSP Book v300 Extended Preview InternetSemoОценок пока нет

- Smart Home Control System LabView PrototypeДокумент5 страницSmart Home Control System LabView PrototypeElaine LaLaОценок пока нет

- Vishveshwarya Technological University BELAGAVI - 590018.: A Mini Project Report OnДокумент35 страницVishveshwarya Technological University BELAGAVI - 590018.: A Mini Project Report OnSoul ReaperОценок пока нет

- Software Requirements Specification: COMSATS University Islamabad, COMSATS Road, Off GT Road, Sahiwal, PakistanДокумент13 страницSoftware Requirements Specification: COMSATS University Islamabad, COMSATS Road, Off GT Road, Sahiwal, PakistanFarah QandeelОценок пока нет

- Vineel Resume RTL Design PDFДокумент4 страницыVineel Resume RTL Design PDFVineel TalluriОценок пока нет

- Getting Started With PIC 18F Microcontroller - MikroC PDFДокумент9 страницGetting Started With PIC 18F Microcontroller - MikroC PDFdevchandarОценок пока нет

- Unit 1Документ12 страницUnit 1Pranjul Kushwaha100% (1)

- Panasonic Program CodesДокумент4 страницыPanasonic Program CodesEiflaRamosStaRitaОценок пока нет

- Insignia Network DesignДокумент3 страницыInsignia Network DesignHannahОценок пока нет

- Software EngineeringДокумент194 страницыSoftware EngineeringPALASH KHAREОценок пока нет

- BTP ThesisДокумент71 страницаBTP ThesisPulkit AggarwalОценок пока нет

- OpenCV Android Programming by Example - Sample ChapterДокумент41 страницаOpenCV Android Programming by Example - Sample ChapterPackt PublishingОценок пока нет

- 9.3.2.13 Lab - Configuring and Verifying Extended ACLsДокумент14 страниц9.3.2.13 Lab - Configuring and Verifying Extended ACLsDerillioОценок пока нет

- SPPU Computer Networks Lab Manual TitleДокумент132 страницыSPPU Computer Networks Lab Manual TitleAachal VaishnavОценок пока нет

- CIVENG 186 - Design of IoTДокумент3 страницыCIVENG 186 - Design of IoTMatthew McGoffinОценок пока нет

- A SicДокумент3 страницыA SicSudha SriramОценок пока нет

- EC6612-VLSI Lab - Lesson PlanДокумент6 страницEC6612-VLSI Lab - Lesson PlanDsce CoimbatoreОценок пока нет

- Sr. No Reg Number Roll Number Candidate's Name Father's Name DOB Reason CommitteeДокумент5 страницSr. No Reg Number Roll Number Candidate's Name Father's Name DOB Reason CommitteemanikkalsiОценок пока нет

- Basic PCДокумент1 страницаBasic PCmanikkalsiОценок пока нет

- O1 Feb11Документ2 страницыO1 Feb11manikkalsiОценок пока нет

- ArduinoДокумент5 страницArduinomanikkalsiОценок пока нет

- Sr. No Reg Number Roll Number Candidate's Name Father's Name DOB Reason CommitteeДокумент5 страницSr. No Reg Number Roll Number Candidate's Name Father's Name DOB Reason CommitteemanikkalsiОценок пока нет

- Design and Implementation of Photo Voltaic System: Arduino ApproachДокумент6 страницDesign and Implementation of Photo Voltaic System: Arduino ApproachjurdeОценок пока нет

- Designing Microcontroller 8051Документ1 страницаDesigning Microcontroller 8051manikkalsiОценок пока нет

- How To Setup The Freertos Project in Visual Studio Express 2015Документ5 страницHow To Setup The Freertos Project in Visual Studio Express 2015manikkalsiОценок пока нет

- S&T Syllabus 20151130Документ22 страницыS&T Syllabus 20151130nannurahОценок пока нет

- Azl W5200 Ethernet Shield: DescriptionДокумент5 страницAzl W5200 Ethernet Shield: DescriptionmanikkalsiОценок пока нет

- Sensor Temp y Humedad Dht11Документ7 страницSensor Temp y Humedad Dht11JuanKar Riveiro VilaboaОценок пока нет

- GSM Shield Sim900a PDFДокумент10 страницGSM Shield Sim900a PDFmanikkalsiОценок пока нет

- Service 2Документ9 страницService 2manikkalsiОценок пока нет

- Embedded Systems - ARM Programming TechniquesДокумент258 страницEmbedded Systems - ARM Programming TechniquesSamir KhОценок пока нет

- LPC2148 ProductDatasheetДокумент45 страницLPC2148 ProductDatasheetSuresh ThiraviamОценок пока нет

- TM4C123 Launch Pad Users ManualДокумент27 страницTM4C123 Launch Pad Users Manualchamp1909Оценок пока нет

- Arduino BasicДокумент6 страницArduino BasicmanikkalsiОценок пока нет

- HW 8-American Megatrends Inc (AMI) 2.61 BIOS Setup Guidelines For AM2 AM3 MotherboardsДокумент5 страницHW 8-American Megatrends Inc (AMI) 2.61 BIOS Setup Guidelines For AM2 AM3 MotherboardsmanikkalsiОценок пока нет

- Msa BookletДокумент39 страницMsa BookletAli HafeezОценок пока нет

- ME Rules 2014Документ15 страницME Rules 2014manikkalsiОценок пока нет

- CH 4Документ6 страницCH 4manikkalsiОценок пока нет

- Arduino BasicДокумент6 страницArduino BasicmanikkalsiОценок пока нет

- Chipset Gpio SW Config Appl NoteДокумент18 страницChipset Gpio SW Config Appl NotemanikkalsiОценок пока нет

- Biodata: Application Form For Direct Election/ Transfer To The Class of Fellow/ Member/ Associate Member/ AssociateДокумент6 страницBiodata: Application Form For Direct Election/ Transfer To The Class of Fellow/ Member/ Associate Member/ AssociatemanikkalsiОценок пока нет

- 1181 Datasheet PDFДокумент10 страниц1181 Datasheet PDFmanikkalsiОценок пока нет

- What Is A Stroke - What Causes A Stroke - Medical News TodayДокумент11 страницWhat Is A Stroke - What Causes A Stroke - Medical News TodaymanikkalsiОценок пока нет

- ICT Sector Report NewzealandДокумент104 страницыICT Sector Report NewzealandmanikkalsiОценок пока нет

- Up Down Counter Xilinx WaveformsДокумент2 страницыUp Down Counter Xilinx WaveformsmanikkalsiОценок пока нет

- Programmable Logic Devices (PLDs): An Introduction to PROM, PAL, PLA, CPLDs and FPGAsДокумент10 страницProgrammable Logic Devices (PLDs): An Introduction to PROM, PAL, PLA, CPLDs and FPGAsjamaalnasirОценок пока нет

- Document E202 - 2008: Building Information Modeling Protocol ExhibitДокумент9 страницDocument E202 - 2008: Building Information Modeling Protocol ExhibitAndres Cedeno TutivenОценок пока нет

- Synopsis Sagar Project - A Study On The Need of CRM in OrganizatonДокумент3 страницыSynopsis Sagar Project - A Study On The Need of CRM in OrganizatonViraja GuruОценок пока нет

- Phy433 Lab Report 1Документ9 страницPhy433 Lab Report 1rabbani abdul rahimОценок пока нет

- Duration of LTMДокумент3 страницыDuration of LTMsamueldaОценок пока нет

- Local Materials Used in Creating Art and TechniquesДокумент29 страницLocal Materials Used in Creating Art and TechniquesAnne Carmel PinoОценок пока нет

- A Review of Solar Parabolic Trough CollectorДокумент7 страницA Review of Solar Parabolic Trough Collectoraxel_oscОценок пока нет

- ProjectДокумент5 страницProjectMahi MalikОценок пока нет

- 1SM6 2015Документ63 страницы1SM6 2015chikoo499Оценок пока нет

- A Simple Method To Transfer The SelectedДокумент2 страницыA Simple Method To Transfer The SelectedrekabiОценок пока нет

- OAF Hello Word Page PDFДокумент20 страницOAF Hello Word Page PDFNaveen KumarОценок пока нет

- Paper Velocity String SPE-30197-PAДокумент4 страницыPaper Velocity String SPE-30197-PAPablo RaffinОценок пока нет

- Meinrad 2018 All Symbols With NumbersДокумент4 страницыMeinrad 2018 All Symbols With NumbersXer N. AcostaОценок пока нет

- Book 3: The SiphonophoresДокумент29 страницBook 3: The SiphonophoresRaquel SilvaОценок пока нет

- Mastercam Book 5 Axis Bai 1Документ31 страницаMastercam Book 5 Axis Bai 1tuanvn76100% (3)

- FSR & FST First Stage Regulator: Maintenance Manual FOR Authorised TechniciansДокумент23 страницыFSR & FST First Stage Regulator: Maintenance Manual FOR Authorised TechniciansпавелОценок пока нет

- RDSCM HowTo GuideДокумент17 страницRDSCM HowTo GuideEric LandryОценок пока нет

- Bid ProcessДокумент85 страницBid ProcessRobiatol Adawiah Mohammad ShamsidiОценок пока нет

- Hwids - 2012 05 22 - 19 04 00Документ9 страницHwids - 2012 05 22 - 19 04 00RONAL DAMIANO PAREJAОценок пока нет

- Beamware 2: Users ManualДокумент14 страницBeamware 2: Users ManualAdi FaizinОценок пока нет

- Air Blue E-TicketДокумент1 страницаAir Blue E-TicketMuneeb Ahmed100% (3)

- The Crime of Galileo - de Santillana, Giorgio, 1902Документ372 страницыThe Crime of Galileo - de Santillana, Giorgio, 1902Ivo da Costa100% (2)

- Solar Panel Cleaning System Design and DevelopmentДокумент4 страницыSolar Panel Cleaning System Design and DevelopmentMohammed safarulla HОценок пока нет

- Learn About Steganography TechniquesДокумент11 страницLearn About Steganography TechniquesashaОценок пока нет

- Event Rulebook Authorsgate 3.0 IEEE SB KUETДокумент9 страницEvent Rulebook Authorsgate 3.0 IEEE SB KUETKUET²⁰²¹Оценок пока нет

- FormatCARS KAAUH Alqahtani 106Документ8 страницFormatCARS KAAUH Alqahtani 106ZEYNOОценок пока нет

- KTO12 Curriculum ExplainedДокумент24 страницыKTO12 Curriculum ExplainedErnesto ViilavertОценок пока нет

- 8279Документ32 страницы8279Kavitha SubramaniamОценок пока нет

- TDS VH202 Steel Spore Discs B - Atrophaeus Cell Line 9372 SDN 06 Rev. 1.0Документ3 страницыTDS VH202 Steel Spore Discs B - Atrophaeus Cell Line 9372 SDN 06 Rev. 1.0Muhammad FirdausОценок пока нет

- Fop 2.1Документ11 страницFop 2.1Paramita HalderОценок пока нет

- #1 Introduction To C LanguageДокумент6 страниц#1 Introduction To C LanguageAtul SharmaОценок пока нет

- Autodesk Fusion 360: A Power Guide for Beginners and Intermediate Users (3rd Edition)От EverandAutodesk Fusion 360: A Power Guide for Beginners and Intermediate Users (3rd Edition)Рейтинг: 5 из 5 звезд5/5 (2)

- Mastering Autodesk Inventor 2014 and Autodesk Inventor LT 2014: Autodesk Official PressОт EverandMastering Autodesk Inventor 2014 and Autodesk Inventor LT 2014: Autodesk Official PressРейтинг: 5 из 5 звезд5/5 (1)

- SolidWorks 2015 Learn by doing-Part 2 (Surface Design, Mold Tools, and Weldments)От EverandSolidWorks 2015 Learn by doing-Part 2 (Surface Design, Mold Tools, and Weldments)Рейтинг: 4.5 из 5 звезд4.5/5 (5)

- Autodesk Inventor 2020: A Power Guide for Beginners and Intermediate UsersОт EverandAutodesk Inventor 2020: A Power Guide for Beginners and Intermediate UsersОценок пока нет

- Fusion 360 | Step by Step: CAD Design, FEM Simulation & CAM for Beginners.От EverandFusion 360 | Step by Step: CAD Design, FEM Simulation & CAM for Beginners.Оценок пока нет

- The Geometrical Tolerancing Desk Reference: Creating and Interpreting ISO Standard Technical DrawingsОт EverandThe Geometrical Tolerancing Desk Reference: Creating and Interpreting ISO Standard Technical DrawingsРейтинг: 4.5 из 5 звезд4.5/5 (10)

- FreeCAD | Step by Step: Learn how to easily create 3D objects, assemblies, and technical drawingsОт EverandFreeCAD | Step by Step: Learn how to easily create 3D objects, assemblies, and technical drawingsРейтинг: 5 из 5 звезд5/5 (1)