Академический Документы

Профессиональный Документы

Культура Документы

Implementation of Low Power and Area Efficient 2BitStep Asynchronous SAR ADC Using Successively Activated Comparators

Загружено:

Editor IJRITCCАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Implementation of Low Power and Area Efficient 2BitStep Asynchronous SAR ADC Using Successively Activated Comparators

Загружено:

Editor IJRITCCАвторское право:

Доступные форматы

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6577 - 6581

______________________________________________________________________________________

Implementation of Low Power and Area Efficient 2-Bit/Step Asynchronous SAR

ADC using Successively Activated Comparators

Sruthy D [1]

PG Scholar, Department of ECE,

Kingston Engineering College,

Vellore, Tamil Nadu, India[1] .

sruthydevarajan@gmail.com

Paul Richardson Gnanaraj J[2]

M.E.,Assistant Professor, Department of ECE,

Kingston Engineering College,

Vellore, Tamil Nadu, India[2].

Paulrichardson.j@gmail.com

Abstract A low power (0.4-09V) 2-Bit/Step successive approximation register (SAR) analog to digital converter (ADC) is conferred. A 2Bit/Step operation technique is proposed which implementing a dynamic threshold configuring comparator instead of number of digital to

analog converters (DACs). Area and power is reduced by successively activated comparators. Here the second comparator is activated reflecting

the preceding comparators results. Because the second comparator threshold is configured dynamically for every cycle, only two comparators

are required instead of three. By successively activating the comparators, the number of DAC settling is halved, so the power and area overhead

is very small and the performance will be increased. The proposed ADC was implemented in a 90nm technology achieved a gain of 35.4 db,

power of 0.89 w and the conversion time of 0.32ns with a supply voltage of 0.4v. The total core area of this ADC is 7.74 m 2.

Keywords- SAR ADC, 2-bit/step, low power, threshold configuring comparator.

__________________________________________________*****_________________________________________________

I.

INTRODUCTION

Recently, immensely low-voltage circuit designs attract a

lot of attention by its supreme power efficiency not only in

digital circuits but also in analog circuits. One of the assuring

applications of such immensely low-voltage circuits is a

wireless sensor network. In the sensor nodes, for easy

distribution into the environment, the power must be supplied

by using energy harvesting technologies to eliminate the need

of a battery replacement. Most of the small size energy

harvesting devices can produce extremely low output voltage,

for example 0.5 V, and fixed power [1]. Therefore sensor node

circuits must operate at immensely low voltage along with low

power. Furthermore, the size of the circuits must be as small as

possible to slow down the cost of the chip, because massive

number of sensor nodes will be embedded in the environment.

Therefore we concentrated on designing low-powered analog

to digital converters (ADCs) for wireless frontends.

Many low power ADCs for radios and sensor nodes has been

suggested, mostly the successive approximation register

(SAR) ADC architecture are used [2]-[4]. When compare to

other architecture, the SAR ADC produce superior power

efficiency. The Other architecture are using power-hungry opamps. For low speed domains, a number of highly power

efficient designs are conferred. By enhancing the chargeredistribution digital-to-analog-converters (DACs) [2] and 500

af unit capacitors are used in the DAC [3], significantly the

analog power consumption was minimized. The SAR ADC

has high power efficiency at a high resolution can be achieved

by designing reconfigurable comparators [4] and bulk voting

[5].

While in most of the research, the operating speed is within

sensor application and is not adequate for radio requirements

which often demand ADCs operating over few tens of MS/s.

The SAR ADC has a constriction of speed, because n clock

cycles are required for SAR search algorithm, in order to

achieve n bit resolution. We have worked on enhancing the

speed of low power SAR ADC in the past, the delay time of

each cycle will be optimized. However, only the 20% speed is

increased. Considering that only the dynamic power are

absorbed by the SAR ADC, in order to provide an high speed

operation, time interleaving is a better way [7]. Still there is a

significant area overhead and timing mismatch calibration

circuits makes the system complicated. We can remove the n

clock cycle and high speed operation is achieved by using 2bit/step SAR ADC.

Without time interleaving, the 2-bit/step method [9]-[12]

can raise the operating speed. It has attracted care to overcome

the speed limits of the SAR ADC.

However, in contrast to the normal SAR ADC, triple times as

more elements are needed [9] resulting in a area overhead and

large power. In [11], a resistive ladder is used to generate

references which absorb dc power. Therefore, designing a

power efficient 2-bit/step ADC which can contend with the

state-of-the art SAR ADC is challenging.

We suggest a area and power efficient 2-bit/step method.

Which is given by adding threshold configuring comparator

(TCC) into an normal SAR ADC [8]. By successively

activating the comparators, the number of DAC settling is

reduced. Even though the power and area is too small, an

increase in speed of over 50% can be achieved. By using an

6577

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6577 - 6581

______________________________________________________________________________________

variable current source (VCs) the comparator threshold is

configured widely and dynamically. By internally producing

voltage the VCs is biased. This maintains the ADC free from

varying power supply. A foreground calibration is identified,

which needs only a 1/2 input throughout the calibration

process. The measured power efficiency is highly comparable

with low power state-of-the art works and the operating speed

is rapidly increased. Therefore 2-bit/step operation method

utilizing TCC has the potential to over the conventional

method that generates number of reference voltages.

II.

METHODOLOGIES

A. 2-BIT/STEP WITH CONVENTIONAL DESIGNS

The successive approximation search using 2-bit/step

method [9]-[12] instead of 1-bit comparator. A 2-bit/step

operation method uses a 2-bit quantizer. Because only n/2

cycles are needed for the n-bit conversion, without time

interleaving the SAR ADC speed is increased. The little

modification is needed in SAR logic to realize the 2-bit/step

operation. In the digital circuitry, there will be the small

overhead is available. However, providing a 2-bit quantizer

need many analog components to be added and the ADC get a

area overhead and large power. For example, for the 2-bit

quantizer, the flash ADC is the suitable choice. It can collect

the comparison results in single clock cycle but has a larger

power consumption. In addition, when operating as a 2bit/step SAR ADC, the reference of the flash ADC should be

configured every SA cycle. The reference must be 1/4,2/4,3/4

Vref at the first SA cycle. Before proceeding to the next cycle,

the CDAC switches its capacitors then it reflects the

comparison results. Therefore the second SA cycle reference is

7/16,8/16,9/16 Vref, respectively. In [9] and [11] too fast 2-bit

SAR ADC researches with a different production of references

are described.

The 2-bit/step SAR ADC method was first suggested in

[9], and in this paper using three capacitor DACs (CDACs) in

order to generate the three references. By providing each

CDAC different switching codes, three references needed for

2-bit quantizing can be generated for each cycle. The fault of

this multi CDAC approach is that the power efficiency drops

significantly because analog components are tripled.

When related with 8-bit 1-bit/step SAR ADCs, the analog

area and power raise 50% and 200% respectively. In order to

relax the power and area overhead, the CDAC was divided to

signal DAC and reference DAC, but the area overhead is

exponentially raise if further resolution , that is, of over 8 bits,

is attempted.

are switched as in the fine ADC in subrange ADCs. The

references are generated without a lot of power and area

overhead, and file the peak power efficiency of 42fJ/conv.at

400 MS/s.

However this result is not proper for low-voltage operation

because switches for each reference will need much longer

settling. Moreover, the DC current of the resistive ladder will

overrule the power consumption at low speed, and lose the

power scalability of the SAR ADC.

The preceding researches of a 2-bit/step SAR ADC

planned several hundred MS/s to GS/s operation at a standard

power supply voltage. Power efficient 2-bit/step for utterly

low voltage and low power operation has not been announced

yet.

B. 2-BIT/STEP WITH THRESHOLD CONFIGURING

COMPARATOR

Rather than using multiple reference voltages, 2-bit/step

operation can be implemented by configuring comparator

offset (Voffset) each cycle. The 2-bit/step SAR ADC enabled

with TCC. Here, the CP2 is an normal comparator, which

easily analyze the input signal Vin and VDAC. Suppose in order

that Voffset of 1/4 Vref and -1/4 Vref is applied to comparator

CP1 and CP3.The comparator threshold (VTHcomp) could be3/4

Vref and 1/4 Vref, respectively and 2-bit quantizer is furnished.

In this approach, at a certain SA cycle N, Voffset of CP1 and

CP3 must be

Voffset =

1

2 2

(1)

When calibration is completed and Voffset is set perfectly. This

approach will need only one CDAC and sampling switch,

consequently. Hence, power can be extremely minimized

when compared with [9] and ADC does not absorb dc power.

However, several area overheads and power remain in this

TCC-based 2-bit/step SAR ADC. First, because for each cycle

that the comparators should configured their threshold, there is

dynamic power of Voffset control circuit. Second and most

critically, there is an overhead in comparator activation.

Although the SA search needs two comparator activation, in 2bit conversion, the 2-bit flash needs three comparators to be

activated. As a result, the comparator power raised 50%. The

problem is severe because TCC absorbs large power than

ordinary comparator.

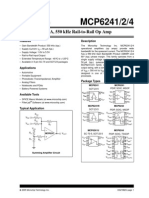

C. 2-BIT/STEP WITH SUCCESIVELY ACTIVATED

COMPARATORS

For more power reduction, we introduce a 2-bit/step ADC

with successively activated comparators (SAC). The block

diagram of SAC as shown in fig.1.

Then again, [11] and [12] use resistive ladder to generate

references for the 2-bit quantizer. At every cycle the references

6578

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6577 - 6581

______________________________________________________________________________________

A. IMPLEMENTATION OF DYNAMIC COMPARATOR

The Fig. 2 shows the circuit design of dynamic comparator.

Here the circuit was designed by cascode current mirror

topology. The Regenerative feedback will be used in this

comparator. This comparator will increase the speed in ADC.

Fig.1 Block Diagram of Proposed 2-bit/step SAR ADC

successively activated comparators

The external sampling clock (CLKext) sets down, an SA

cycle 1 is started by increasing and 1 CP1 determine the first

bit (OUTCP1). After the decision of the first bit, VTHcomp of CP2

(VTHCP2) is set and revert the result of OUTCP1. If the OUTCP1

is 1, thus VTHCP2 is set to 12/16 Vref and the second bit

(OUTCP2) is determined. In the proposed ADC, the 2-bit

quantizer works like a binary-search ADC [13], so the second

comparator is activated reflecting the previous comparators

results. For every cycle the threshold is configured

dynamically in the second comparator, only two comparators

are needed rather than three. The internal clock generator and

register units (cycle N reg) are custom designed logic cells and

particular information are discussed in [14]. The results of SA

cycle 1 are stored in MSB and 2nd MSB registers, respectively.

A generic SAR ADC cycle time is decided by three delays:

SAR logic delay (tlogic), comparator delay (tcomp), and DAC

settling (tDAC). Therefore, the conventional 2-bit/step SAR

ADC conversion time is only 4(tcomp+tlogic+tDAC), since two bits

are processed concurrently. Here the proposed circuit is

considered, in this the tlogic and tDAC is halved, because the

comparators are activated successively [15], there is no

enhancement in tcomp. Therefore, the conversion time for 8-bit

SAC operation is

tconversion = 8tcomp+4(tlogic+tcomp)

(2)

Fig.2 Proposed Dynamic Comparator Circuit

Fig.3 Output of Dynamic Comparator

The Fig.2 and Fig.3 represents the proposed circuit, the

given input is only 1.15v and since the comparator operates in

the open loop circuit mode so we could see that the output

goes to peak value of the supply voltage which is

approximately equal to 3V. This clearly shows that it is

operating as comparator.

B. IMPLEMENTATION OF 2 STAGE LATCH

The Fig.4 shows the circuit design of 2 Stage latch. It was

designed by cascode current mirror topology.

III. DESIGN AND SIMULATION RESULTS

The 2-Bit/Step SAR ADC with SAC was designed and

simulated by using Tanner EDA tool and ModelSim. In the

Tanner EDA (Electronic Design and Automation) Circuit

Design, the low voltage source is given to the circuit for

circuit operation. Here the transistors are designed based on

the Length and Width. The Length and Width is chosen as

L=0.25u W=2.50u and the scaling of these circuit design is

fixed as 1. The Circuit Design and Simulation Results are

shown below.

Fig.4 Proposed 2 Stage Latch Circuit

Fig.5 Output of 2 Stage Latch

The Fig.4 and Fig.5 represents the latch samples and

retains the value of the input at the positive level of the clock.

6579

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6577 - 6581

______________________________________________________________________________________

Since the clk=1 so the value in the input 1.55v is being latched

to the output which is the addition of sampled output and the

latched input.

C. IMPLEMENTATION OF CDAC

The Fig.8 and Fig.9 represents the sample and hold circuit

samples the input and it retains the value in the capacitor even

after the sampling period. The input given was 1.1v volt and

the S/H circuit holds the value of around 440mv in the circuit

even after the sampling in both the nodes at N and P MOS

circuit.

The Fig.6 Shows the circuit design of CDAC. This was

implemented by cascode current mirror topology.

Fig.10 Output of Shift Register

Fig.6 CDAC Circuit

The Fig.10 represents the output waveform of Shift Register

by using ModelSim. Here the waveform represents the 8-bit

input is given and it will produce the 8bit output and the clock

is used to generate the clock pulse internally.

Fig.7 Output of CDAC

The Fig.6 and Fig.7 represents the circuit gives the analog

output of 1.1v for the digital input 1v in the circuit it clearly

shows that the analog input is obtained.

D. IMPLEMENTATION OF SAMPLE AND HOLD

CIRCUIT

The Fig.8 shows the Sample and Hold circuit design. The

cascode current mirror topology was implemented.

Fig.11 Output of Counter

The Fig.11 shows the output waveform of the counter. This

waveform is obtained by using ModelSim tool. In this the

counter is used to count the clock pulse. Here the clock pulse

will be started in a rising Edge.

TABLE I. Proposed ADC Performance Summary

Fig.8 Sample and Hold Circuit

Fig.9 Output of Sample and Hold Circuit

Technology

90nm TSMC

Core Area

7.74 2

Supply

Voltage(V)

0.4

0.5

0.6

0.7

0.8

0.9

Power()

0.89

8.23

8.23

78.32

123.6

188.5

Timing(ns)

0.32

0.49

0.49

0.97

1.03

1.18

Gain(dB)

35.4

35.6

35.6

35.9

36.1

36.01

The Table I represents the low voltage of (0.4v-0.9v), and it

was achieved the core area, power and timing and gain of these

supply voltages. This was implemented in a 90nm technology.

6580

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 3 Issue: 12

ISSN: 2321-8169

6577 - 6581

______________________________________________________________________________________

IV.

[11] H. Wei, C.-H. Chan, U.-F. Chio, S.-W. Sin, U.-S. Pan, R.

Martins, et al., A 0.024mm2 8b 400MS/s SAR ADC with

2b/Cycle and Resistive DAC in 65nm CMOS, in IEEE

ISSCC Dig. Tech. Papers, Feb. 2011, pp. 188189.

[12] Y. Lien, A 4.5-mW 8-b 750-MS/s 2-b/step asynchronous

subranged SAR ADC in 28-nm CMOS technology, in

IEEE Symp. VLSI Circuits Dig. Tech. Papers, Jun. 2012,

pp. 8889.

[13] G. Van der Plas and B. Verbruggen, A 150 MS/s 133 uW

7 bit ADC in 90 nm digital CMOS, IEEE J. Solid-State

Circuits, vol. 43, no. 12, pp. 26312640, Dec. 2008.

[14] A. Shikata, R. Sekimoto, K. Yoshioka, T. Kuroda, and H.

Ishikuro, A 4-10bit, 0.4-1V power supply, power scalable

asynchronous SAR-ADC in 40nm-CMOS with wide

operating range SAR controller, Trans. IEICE, vol. 96, no.

2, pp. 443452, Feb. 2013

[15] Akira Shikata, Ryota Sekimoto, Tadahiro Kuroda and

Hiroki Ishikuro, "An 8 bit 0.30.8 V 0.240 MS/s 2bit/Step SAR ADC With Successively Activated Threshold

Conguring Comparators in 40 nm CMOS," IEEE Trans.

VLSI Syst., vol. 23, no. 2, pp. 356-368, Feb.2015.

CONCLUSION

An immensely low-voltage operating high-speed and lowpower SAR ADC were presented. Using Dynamic threshold

conguring comparators, 2-bit/step operation is presented with

a small area and low-power consumption. Successive

activation of comparators is proposed, It was reduced the more

power and its enhanced conversion speed at low supply

voltages. The proposed ADC was implemented in a 90nm

technology achieved a gain of 35.4 db, power of 0.89 w and

the conversion time of 0.32ns with a supply voltage of 0.4v.

The total core area of this ADC is 7.74 m2. Further we can

reduce even more power and area by implementing in a 32nm

technology.

V.

REFERENCES

[1] B. H. Calhounet al., Design considerations for ultra-low

energy wireless microsensor nodes, IEEE Trans. Comput,

vol 54, no.6, pp.727-740, june 2005.

[2] M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E.

A. M. Klumperink, and B. Nauta, A 10-bit chargeredistribution ADC consuming 1.9 W at 1MS/s,IEEE J.

Solid-State Circuits, vol. 45, no. 5, pp. 10071015, May

2010.

[3] A. Shikata, R. Sekimoto, T. Kuroda, and H. Ishikuro, A

0.5V 1.1 MS/sec 6.3fJ/conversion-step SAR-ADC with trilevel comparator in 40 nm CMOS, IEEE J. Solid-State

Circuits, vol. 47, no. 4, pp. 10221030, Apr. 2012.

[4] P. Harpe, Y. Zhang, G. Dolmans, K. Philips, and H. de

Groot, A 7-to-10b 0-to-4MS/s exible SAR ADC with

6.5-to-16fJ/conversionstep, in IEEE ISSCC Dig. Tech.

Papers, Feb. 2012, pp. 472473.

[5] P. Harpe, E. Cantatore, and A. van Roermund, A

2.2/2.7fJ/conversionstep 10/12b 40kS/s SAR ADC with

data-driven noise reduction, in IEEE ISSCC Dig. Tech.

Papers, Feb. 2013, pp. 270271.

[6] R. Sekimoto, A. Shikata, T. Kuroda, and H. Ishikuro, A

40nm 50S/s-8MS/s ultra low voltage SAR ADC with

timing optimized asynchronous clock generator, in Proc.

IEEE ESSCIRC, Sep. 2011, pp. 471474.

[7] D. Stepanovic and B. Nikolic, A 2.8GS/s 44.6mW timeinterleaved ADC achieving 50.9dB SNDR and 3dB

effective resolution bandwidth of 1.5GHz in 65nm CMOS,

in IEEE Symp. VLSI Circuits Dig. Tech. Papers, Jun. 2012,

pp. 8485.

[8] K. Yoshioka, A. Shikata, R. Sekimoto, T. Kuroda, and H.

Ishikuro, An 8bit 0.35-0.8V 0.5-30MS/s 2-bit/step SAR

ADC with wide range threshold conguring comparator,

in Proc. IEEE ESSCIRC, Sep. 2012, pp. 381384.

[9] Z. Cao, S. Yan, and Y. Li, A 32 mW 1.25 GS/s 6b 2b/Step

SAR ADC in 0.13 m CMOS,IEEE J. Solid-State

Circuits, vol. 44, no. 3, pp. 862873, Mar. 2009.

[10] H.-K. Hong, W. Kim, S.-J. Park, M. Choi, H.-J. Park, and

S.-T. Ryu, A 7b 1GS/s 7.2mW Nonbinary 2b/cycle SAR

ADC with register-to DAC direct control, in Proc. IEEE

CICC, Sep. 2012, pp. 14.

BIOGRAPHY

Sruthy D[1] pursuing Master of Engineering (M.E) in the

Electronics and Communication Department, Kingston

Engineering College, Vellore, Anna University. She received

Bachelor of Engineering (B.E) degree in 2013 from Anna

University, Chennai, India.

Paul Richardson Gnanaraj J[2] received the B.E. (ECE) and

M.E. (VLSI Design) degrees from the Anna University

Chennai in 2008 and 2010 respectively. He is currently

working as Assistant Professor in Kingston Engineering

College Vellore for the past few years. His current research

interests include VLSI design for nanoscale silicon, low power

and high speed reliable system design. He is the author or

coauthor of over 10 papers in journals and conference

proceedings.

6581

IJRITCC | December 2015, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

Вам также может понравиться

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5795)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Comptia Network+ N10-006 Authorized Cert GuideДокумент61 страницаComptia Network+ N10-006 Authorized Cert GuidejbiebsОценок пока нет

- Aptra: Advance XFS Product OverviewДокумент48 страницAptra: Advance XFS Product OverviewJalal Zahidur RahmanОценок пока нет

- Sullair Compressor 7500 2017Документ104 страницыSullair Compressor 7500 2017JoNathanGranatoCaldeiraОценок пока нет

- LS6 LAS (Desktop Computer)Документ12 страницLS6 LAS (Desktop Computer)Ronalyn Maldan100% (1)

- Sullair Air Compressor Parts CatalogДокумент96 страницSullair Air Compressor Parts Catalogedascribd67% (6)

- Importance of Similarity Measures in Effective Web Information RetrievalДокумент5 страницImportance of Similarity Measures in Effective Web Information RetrievalEditor IJRITCCОценок пока нет

- A Review of 2D &3D Image Steganography TechniquesДокумент5 страницA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCОценок пока нет

- Diagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmДокумент5 страницDiagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmEditor IJRITCCОценок пока нет

- Channel Estimation Techniques Over MIMO-OFDM SystemДокумент4 страницыChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCОценок пока нет

- A Study of Focused Web Crawling TechniquesДокумент4 страницыA Study of Focused Web Crawling TechniquesEditor IJRITCCОценок пока нет

- Prediction of Crop Yield Using LS-SVMДокумент3 страницыPrediction of Crop Yield Using LS-SVMEditor IJRITCCОценок пока нет

- Predictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth KotianДокумент3 страницыPredictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth Kotianrahul sharmaОценок пока нет

- Hybrid Algorithm For Enhanced Watermark Security With Robust DetectionДокумент5 страницHybrid Algorithm For Enhanced Watermark Security With Robust Detectionrahul sharmaОценок пока нет

- Itimer: Count On Your TimeДокумент4 страницыItimer: Count On Your Timerahul sharmaОценок пока нет

- 45 1530697786 - 04-07-2018 PDFДокумент5 страниц45 1530697786 - 04-07-2018 PDFrahul sharmaОценок пока нет

- Paper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineДокумент4 страницыPaper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineEditor IJRITCCОценок пока нет

- 44 1530697679 - 04-07-2018 PDFДокумент3 страницы44 1530697679 - 04-07-2018 PDFrahul sharmaОценок пока нет

- Safeguarding Data Privacy by Placing Multi-Level Access RestrictionsДокумент3 страницыSafeguarding Data Privacy by Placing Multi-Level Access Restrictionsrahul sharmaОценок пока нет

- 41 1530347319 - 30-06-2018 PDFДокумент9 страниц41 1530347319 - 30-06-2018 PDFrahul sharmaОценок пока нет

- 49 1530872658 - 06-07-2018 PDFДокумент6 страниц49 1530872658 - 06-07-2018 PDFrahul sharmaОценок пока нет

- Configure VLANs in Juniper SwitchДокумент3 страницыConfigure VLANs in Juniper SwitchhellcrowОценок пока нет

- EPower - HA029836 - 4Документ10 страницEPower - HA029836 - 4monica_lelisОценок пока нет

- OpAmp - MCP6241Документ28 страницOpAmp - MCP6241Ludwig SchmidtОценок пока нет

- Car Radio CD USB SD BluetoothДокумент32 страницыCar Radio CD USB SD BluetoothVeress JozsefОценок пока нет

- 5eda5a6b 4afa 4352 9716 917a247cef12 VGTType2AElectricActuatorДокумент2 страницы5eda5a6b 4afa 4352 9716 917a247cef12 VGTType2AElectricActuatorhaviettuanОценок пока нет

- CAL-LAB Lightning Isolators - Terms of Sales, Lifetime Service Arrangement (LLSWA) and How To Use?Документ4 страницыCAL-LAB Lightning Isolators - Terms of Sales, Lifetime Service Arrangement (LLSWA) and How To Use?BPL-geekОценок пока нет

- Dahua XVR4104C PDFДокумент3 страницыDahua XVR4104C PDFthanhОценок пока нет

- HP Z2 SFF G4 Workstation - Support and Service: July 2018Документ29 страницHP Z2 SFF G4 Workstation - Support and Service: July 2018Luhtfi F Fauzi NОценок пока нет

- SQL Assignment 2 Opt3Документ10 страницSQL Assignment 2 Opt3Nguyễn Đức Bảo SơnОценок пока нет

- 354 39 Solutions Instructor Manual 4 Assembly Language Programming 8085 Chapter 4Документ4 страницы354 39 Solutions Instructor Manual 4 Assembly Language Programming 8085 Chapter 4Saravanan Jayabalan50% (2)

- Simpana Backup and Recovery For Oracle Datasheet PDFДокумент2 страницыSimpana Backup and Recovery For Oracle Datasheet PDFbanala.kalyanОценок пока нет

- Tips MIRC - Dialogs (PaiRC)Документ8 страницTips MIRC - Dialogs (PaiRC)svasilichОценок пока нет

- Gamry Potentiostat - SeriesG Quick Start GuideДокумент16 страницGamry Potentiostat - SeriesG Quick Start GuideIshmael WoolooОценок пока нет

- Microprocessor Rapper Control User Manual: Neundorfer, Inc. 1990, 2005 Revised July, 2005Документ55 страницMicroprocessor Rapper Control User Manual: Neundorfer, Inc. 1990, 2005 Revised July, 2005Ankur SahariaОценок пока нет

- Lennox Pellet PartsДокумент88 страницLennox Pellet Partsahyre1Оценок пока нет

- Service Manual DP750 DP760 ENG Rev1Документ96 страницService Manual DP750 DP760 ENG Rev1Дмитрий РазуваевОценок пока нет

- SRT 1F K-Shelf Tests ProcedureДокумент116 страницSRT 1F K-Shelf Tests ProcedureMihaelОценок пока нет

- Data and Computer Exam LLLДокумент5 страницData and Computer Exam LLLSuper RageОценок пока нет

- Startup ManualДокумент3 страницыStartup ManualProcurement PardisanОценок пока нет

- Vibration Analyzer ComparisonДокумент4 страницыVibration Analyzer ComparisonJuanVargasОценок пока нет

- GDL 330 001 403 R10 en FieldCablingGuidelinesДокумент36 страницGDL 330 001 403 R10 en FieldCablingGuidelinesJose JohnОценок пока нет

- TDA8375AДокумент73 страницыTDA8375Asontuyet82Оценок пока нет

- Sony SLV Ga30 Ga40k Ga600 Ga77k Gf90kДокумент67 страницSony SLV Ga30 Ga40k Ga600 Ga77k Gf90kfulop_hubaОценок пока нет

- Generics - QuestionsДокумент28 страницGenerics - Questionscristi_pet4742Оценок пока нет

- CTV 2 ModifiedДокумент5 страницCTV 2 ModifiedStack GanОценок пока нет