Академический Документы

Профессиональный Документы

Культура Документы

2input AND Gate Data Flow Model

Загружено:

Pronadeep Bora0 оценок0% нашли этот документ полезным (0 голосов)

2 просмотров2 страницыww

Оригинальное название

2inputandgate

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документww

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

2 просмотров2 страницы2input AND Gate Data Flow Model

Загружено:

Pronadeep Boraww

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 2

2input AND gate Data Flow Model

`timescale 1ns / 1ps

module and2_gate(

input A,B,

output F

);

assign F=A&B;

endmodule

2input AND gate Structural Model

`timescale 1ns / 1ps

module and2_gate(

input A,B,

output F

);

and(F,A,B);

endmodule

2input AND gate Data Flow Model

`timescale 1ns / 1ps

module and2_gate(

input A,B,

output reg F

);

always@(A or B)

begin

F=A&B;

end

endmodule

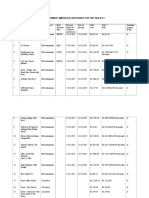

RTL Schematic

Test Bench

`timescale 1ns / 1ps

module and2_gate_tb();

reg A,B;

wire F;

and2_gate dut(.A(A),.B(B),.F(F));

initial

begin

A=0;B=0;

#10 A=0;B=1;

#10 A=1;B=0;

#10 A=1;B=1;

end

endmodule

Timing Diagram

Вам также может понравиться

- AMBA AHB Protocol PresentationДокумент45 страницAMBA AHB Protocol Presentationachanta1291% (11)

- ASIC Design Lab ReportsДокумент16 страницASIC Design Lab ReportsNisar Ahmed RanaОценок пока нет

- Verilog Modules For Common Digital FunctionsДокумент30 страницVerilog Modules For Common Digital Functionselle868Оценок пока нет

- VLSI Cadance ManualДокумент84 страницыVLSI Cadance ManualTony ParkerОценок пока нет

- Verilog Code For Basic Gates and Test BenchДокумент25 страницVerilog Code For Basic Gates and Test BenchApple FoodОценок пока нет

- Digital Design Lab (Ec661) Experiment N0.:1: Brief Description of WorkДокумент63 страницыDigital Design Lab (Ec661) Experiment N0.:1: Brief Description of WorkBhaskar KОценок пока нет

- Lab 3Документ13 страницLab 3J JAYDONОценок пока нет

- Verilog Modules For Common Digital FunctionsДокумент30 страницVerilog Modules For Common Digital Functionssudarshan poojaryОценок пока нет

- Demux To ALUДокумент13 страницDemux To ALUkarry4galsОценок пока нет

- List of Experiments: Expt. No. Date Name of The Experiment Page No. RemarksДокумент55 страницList of Experiments: Expt. No. Date Name of The Experiment Page No. RemarksRakesh KumarОценок пока нет

- LAB FAT QUESTIONS ANALYSISДокумент15 страницLAB FAT QUESTIONS ANALYSISSrinivasan UmaОценок пока нет

- DSD Lab1Документ8 страницDSD Lab1Muazam MalikОценок пока нет

- All VerilogLabsДокумент74 страницыAll VerilogLabssamruthОценок пока нет

- Verilog modules for 4-bit ALU, register, RAM and instruction decoderДокумент6 страницVerilog modules for 4-bit ALU, register, RAM and instruction decoderRaffi SkОценок пока нет

- TỔNG HỢP ÔN TẬP THIẾT KẾ VI MẠCH SỐДокумент28 страницTỔNG HỢP ÔN TẬP THIẾT KẾ VI MẠCH SỐHải ĐăngОценок пока нет

- CSE 321 Verilog Tutorial: Register Transfer Level Design with Verilog ModulesДокумент14 страницCSE 321 Verilog Tutorial: Register Transfer Level Design with Verilog ModulesMirza BaigОценок пока нет

- Verilog code for basic and universal gatesДокумент30 страницVerilog code for basic and universal gatesImrannkhanОценок пока нет

- F Pga Chan de AssignmentДокумент38 страницF Pga Chan de AssignmentSubbuNaiduОценок пока нет

- Embedded Systems Design UCS614: Assignment 1-4Документ12 страницEmbedded Systems Design UCS614: Assignment 1-4Pankaj GuptaОценок пока нет

- 4-bit Ripple Carry Full Adder Subtractor Verilog CodeДокумент6 страниц4-bit Ripple Carry Full Adder Subtractor Verilog Code伊布蘭Оценок пока нет

- ECAD and VLSI Lab ManualДокумент107 страницECAD and VLSI Lab ManualHarold WilsonОценок пока нет

- Verilog HDL Gate-Level ModelingДокумент33 страницыVerilog HDL Gate-Level ModelingVaishnavi ReddyОценок пока нет

- Verilog Code For Comb. CircuitsДокумент33 страницыVerilog Code For Comb. Circuitsjayaprasadkalluri100% (1)

- Lab Programs: Computer Organization and ArchitectureДокумент57 страницLab Programs: Computer Organization and ArchitectureTharun S vОценок пока нет

- 3 to 8 Decoder Verilog designДокумент59 страниц3 to 8 Decoder Verilog designvaishnaviОценок пока нет

- Verilog HDL Lab CodesДокумент30 страницVerilog HDL Lab CodesImrannkhanОценок пока нет

- Digital Hardware Design Assignment: Verilog Codes and SimulationsДокумент16 страницDigital Hardware Design Assignment: Verilog Codes and SimulationsTeja Krishna Kopuri100% (2)

- PIC18F4550 Pin FunctionsДокумент2 страницыPIC18F4550 Pin Functionsveeramaniks408Оценок пока нет

- Saksham Porwal DSD Experiment-2Документ5 страницSaksham Porwal DSD Experiment-2chinusood08Оценок пока нет

- Micro 133 Midterm Lecture 2 - IO Interfacing With 8255 & Assembly Language - EditedДокумент10 страницMicro 133 Midterm Lecture 2 - IO Interfacing With 8255 & Assembly Language - EditedKeilla Romabiles LeopandoОценок пока нет

- Pipelines in VerilogДокумент6 страницPipelines in VerilogHotmedal TalhaОценок пока нет

- VerilogДокумент6 страницVerilogShaik IliyasОценок пока нет

- Vlsi Comple Lab TaskДокумент37 страницVlsi Comple Lab TaskTausique SheikhОценок пока нет

- Logic Design Lab Verilog 101Документ49 страницLogic Design Lab Verilog 101杜岳Оценок пока нет

- EE312 Experiment 07: Objective 1Документ18 страницEE312 Experiment 07: Objective 1SAURABH RAJОценок пока нет

- Verilog CodesДокумент4 страницыVerilog CodesHusnain AliОценок пока нет

- Shiva 2651533Документ62 страницыShiva 2651533Punna Shiva RamaKrishnaОценок пока нет

- Final VLSI LAB Digital Analog RecordДокумент22 страницыFinal VLSI LAB Digital Analog RecordManjunatha Swamy VОценок пока нет

- Vlsi Design Lab FileДокумент59 страницVlsi Design Lab Filemkpriya02Оценок пока нет

- Verilog HDL: ModuleДокумент9 страницVerilog HDL: ModuleAvinash ReddyОценок пока нет

- Along With The Test Bench:-I) All Basic Gates Ii) Half Adder, Full Adder, Half Subtractor, Full Subtractor (Using Structural Modelling Style)Документ12 страницAlong With The Test Bench:-I) All Basic Gates Ii) Half Adder, Full Adder, Half Subtractor, Full Subtractor (Using Structural Modelling Style)AkshatОценок пока нет

- Verilog CodeДокумент85 страницVerilog Codeappuamreddy75% (8)

- Lab 13Документ11 страницLab 13ubaidОценок пока нет

- PartB VLSI UpdatedДокумент7 страницPartB VLSI UpdatedChetan BhajantriОценок пока нет

- DSD HDL Exp1Документ9 страницDSD HDL Exp1ROHIT HANSALIYAОценок пока нет

- Lab 1Документ23 страницыLab 1Santosh KumarОценок пока нет

- VLSI Lab 9Документ33 страницыVLSI Lab 9Umar AyubОценок пока нет

- Module Orgate (A, B, C,) Input A, B, Output C Reg C Always@ (A or B) Case (A) 1'b0:c B 1'b1:c 1 Endcase EndmoduleДокумент7 страницModule Orgate (A, B, C,) Input A, B, Output C Reg C Always@ (A or B) Case (A) 1'b0:c B 1'b1:c 1 Endcase EndmodulejayasrivenkatОценок пока нет

- Synthesizeable Verilog Code ExamplesДокумент9 страницSynthesizeable Verilog Code ExamplesSiva Krishna BandiОценок пока нет

- Arduino - ATmega328 - PWM Signal.cДокумент3 страницыArduino - ATmega328 - PWM Signal.cvackyvipin100% (1)

- 1.basic Gates and or Nor NandДокумент32 страницы1.basic Gates and or Nor NandmrajkumarpatelОценок пока нет

- Eastern Mediterranean UniversityДокумент24 страницыEastern Mediterranean UniversityMpu KatanaОценок пока нет

- Assignment 01 Cavd PDFДокумент14 страницAssignment 01 Cavd PDFnamanrana237Оценок пока нет

- Micro ProposalДокумент6 страницMicro ProposalKye GarciaОценок пока нет

- Practical No - 1 Aim: Implementation of Gates.: 1) AND GateДокумент18 страницPractical No - 1 Aim: Implementation of Gates.: 1) AND GatePrince SharmaОценок пока нет

- Verilog HDL Synthesis and ImplementationДокумент41 страницаVerilog HDL Synthesis and ImplementationAlexandru OleinicОценок пока нет

- SSN College of Engineering, It Highway, KALAVAKKAM-603 110: Lab RecordДокумент93 страницыSSN College of Engineering, It Highway, KALAVAKKAM-603 110: Lab RecordKarthikai SelviОценок пока нет

- Vlsi A & B - 2011Документ70 страницVlsi A & B - 2011Amaresh RamathalОценок пока нет

- 22BCP367 DECO Assignment 5Документ11 страниц22BCP367 DECO Assignment 5Smit PatelОценок пока нет

- VHDL SynthesisДокумент91 страницаVHDL SynthesisFennil KinsperОценок пока нет

- SerDes - WikipediaДокумент3 страницыSerDes - WikipediaPronadeep BoraОценок пока нет

- What Is JESD204 and Why Should We Pay Attention To ItДокумент3 страницыWhat Is JESD204 and Why Should We Pay Attention To ItPronadeep BoraОценок пока нет

- Amukh Expre CertifДокумент1 страницаAmukh Expre CertifPronadeep BoraОценок пока нет

- SMDP - Project - Final - Proposal - NIT - N - Draft PDFДокумент17 страницSMDP - Project - Final - Proposal - NIT - N - Draft PDFPronadeep BoraОценок пока нет

- Demystifying Deterministic Latency Within JESD204B Converters - Electronic DesignДокумент11 страницDemystifying Deterministic Latency Within JESD204B Converters - Electronic DesignPronadeep BoraОценок пока нет

- Difference Between AHB and AXI - Difference BetweenДокумент2 страницыDifference Between AHB and AXI - Difference BetweenPronadeep BoraОценок пока нет

- 8b - 10b Encoding - WikipediaДокумент8 страниц8b - 10b Encoding - WikipediaPronadeep BoraОценок пока нет

- JESD204C primer introduces new high-speed serial link standardДокумент3 страницыJESD204C primer introduces new high-speed serial link standardPronadeep BoraОценок пока нет

- EDN - Understanding Layers in The JESD204B Specification - A High Speed ADC Perspective, Part 2 - EDNДокумент8 страницEDN - Understanding Layers in The JESD204B Specification - A High Speed ADC Perspective, Part 2 - EDNPronadeep BoraОценок пока нет

- 2quickly Implement JESD204BДокумент4 страницы2quickly Implement JESD204BPronadeep BoraОценок пока нет

- UARTДокумент24 страницыUARTPronadeep BoraОценок пока нет

- UART SpecДокумент24 страницыUART SpecPronadeep BoraОценок пока нет

- AMBA AHB AXI Interview Questions Verification Guide PDFДокумент2 страницыAMBA AHB AXI Interview Questions Verification Guide PDFPronadeep BoraОценок пока нет

- Asynchronous FIFO Basics for Safe Clock Domain CrossingДокумент40 страницAsynchronous FIFO Basics for Safe Clock Domain CrossingPronadeep Bora100% (1)

- Valid Documents List PDFДокумент2 страницыValid Documents List PDFAnoop DubeyОценок пока нет

- Asynchronous FIFO Basics for Safe Clock Domain CrossingДокумент40 страницAsynchronous FIFO Basics for Safe Clock Domain CrossingPronadeep Bora100% (1)

- AXI vs AHB: Understanding the Differences Between the Two Popular ARM Bus ProtocolsДокумент3 страницыAXI vs AHB: Understanding the Differences Between the Two Popular ARM Bus ProtocolsPronadeep Bora100% (2)

- Utilization Certificate - SMDP-1Документ1 страницаUtilization Certificate - SMDP-1Pronadeep BoraОценок пока нет

- V2 - Proforma For Submitting 6 MONTHLY REPORTДокумент9 страницV2 - Proforma For Submitting 6 MONTHLY REPORTPronadeep BoraОценок пока нет

- WHMS NitnДокумент14 страницWHMS NitnPronadeep BoraОценок пока нет

- SMDP C2SDSixmonthlyProgressFinalДокумент4 страницыSMDP C2SDSixmonthlyProgressFinalPronadeep BoraОценок пока нет

- Quotations For Components Required For SMDP ProjectДокумент2 страницыQuotations For Components Required For SMDP ProjectPronadeep BoraОценок пока нет

- Six Monthly Progress-FormatДокумент3 страницыSix Monthly Progress-FormatPronadeep BoraОценок пока нет

- AQMS NitnДокумент11 страницAQMS NitnPronadeep BoraОценок пока нет

- Digilent LABSeupimentsДокумент1 страницаDigilent LABSeupimentsPronadeep BoraОценок пока нет

- Six Monthly Progress-Annexures (Tables)Документ6 страницSix Monthly Progress-Annexures (Tables)Pronadeep BoraОценок пока нет

- Current Project StatusДокумент1 страницаCurrent Project StatusPronadeep BoraОценок пока нет

- Nit Nagaland - Pmod - Quote - DG - CoreelДокумент1 страницаNit Nagaland - Pmod - Quote - DG - CoreelPronadeep BoraОценок пока нет

- Element14equipments PDFДокумент1 страницаElement14equipments PDFPronadeep BoraОценок пока нет