Академический Документы

Профессиональный Документы

Культура Документы

Digital Basic - 1 PDF

Загружено:

jeravi84Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Digital Basic - 1 PDF

Загружено:

jeravi84Авторское право:

Доступные форматы

DIGITAL BASIC - 1.

5 : Multiplexer (MUX) |VLSI Concepts

1 of 6

http://www.vlsi-expert.com/2013/12/digital-basic-15-multiplexer-mux.html

Powered by

Translate

A online information Center for all who have Interest in Semiconductor Industry.

Content

VLSI BASIC

Low Power

STA & SI

Physical Design

Video Lectures

VLSI Glossary

Extraction & DFM

Vlsi Interview Questions

VLSI Industry: Insight

About Us

Recommended Book

Call for Help

Featured Post

Search This Blog

Journey from M.tech to Internship (Sanjay

Goyal)

Wednesday, December 25, 2013

People always ask me how to get into VLSI Industry and

every time, I try to help them with few basic rules.

Complete your required Educat...

DIGITAL BASIC - 1.5 : Multiplexer (MUX)

Follow by Email

Index

Chapter1

Chapter2

Chapter3

Digital

Background

Semiconductor Background

CMOS

Processing

Chapter4

1.1

1.2

1.3a

1.3b

1.4

1.5

Number

System

Digital

Arithmetic

Logic

Gates

Logic

Gates

Combinational

Circuits

Multiplex

(MUX)

1.6

Be the first of your friends to like this

De-Multiplexer:

Receives information on a single line and transmits that information on one of 2n possible output lines.

The selection of specific output line is controlled by the bit values of n selection lines.

Multiplexer:

Multiplexing means transmitting a large number of information units over a smaller number of channels lines.

A digital multiplexer is a combinational circuit that selects binary information from one of many inputs lines and directs it

in a signal output line.

The selection of a particular line is controlled by a set of selection lines.

Normally, there are 2n input lines and n selection lines whose bit combinations determine which input is selected.

Multiplexers can be used for the implementation of Boolean functions, combinational circuits. They can also used for

parallel to serial conversion.

Multiplexer is also called data selector or universal circuit.

It is used for connection two or more sources to a single destination among computer units and it is useful for

constructing a common bus system

Total Pageviews

3,436,496

Subscribe To VLSI EXPERT

Posts

Comments

Important Points:

To implement 2n :1 MUX by using 2:1 MUX, the total number or 2:1 MUX required is 2n-1

Given MUX

4

4

8

8

:

:

:

:

1

1

1

1

To be implemented

MUX

16 : 1

64 : 1

64 : 1

256 : 1

Required

No of MUX

4+1=5

16+4+1=21

8+1 =9

32+4+1=37

Implementation of Higher Order MUX using Lower Order MUX:

4:1 MUX by 2:1 MUX

Popular Posts

Basic of Timing

Analysis in Physical

Design

"Timing Paths" : Static

Timing Analysis (STA)

basic (Part 1)

Blog Archive

2016 (8)

2015 (15)

2014 (15)

Delay - "Wire Load

Model" : Static Timing

Analysis (STA) basic

(Part 4c)

Delay - "Interconnect

Delay Models" : Static

Timing Analysis (STA)

basic (Part 4b)

"Setup and Hold Time"

: Static Timing Analysis

(STA) basic (Part 3a)

"Setup and Hold Time

2013 (12)

December (6)

DIGITAL BASIC 1.5 : Multiplexer

(MUX)

DIGITAL BASIC 1.4 :

Combinational

Circuits

DIGITAL BASIC 1.3 : LOGIC

GATES (Part - b)

DIGITAL BASIC -

7/17/2016 10:30 PM

DIGITAL BASIC - 1.5 : Multiplexer (MUX) |VLSI Concepts

2 of 6

http://www.vlsi-expert.com/2013/12/digital-basic-15-multiplexer-mux.html

Violation" : Static

Timing Analysis (STA)

basic (Part 3b)

"Examples Of Setup

and Hold time" : Static

Timing Analysis (STA)

basic (Part 3c)

"Time Borrowing" :

Static Timing Analysis

(STA) basic (Part 2)

Effect of Wire Length

On the Slew: Static

Timing Analysis (STA)

Basic (Part-7a)

Total number of 2: 1 MUX = 3

MUX as a universal logic gate

Gate Type

Buffer

Implemented by MUX + Equation

Y=output = A

10 Ways to fix SETUP

and HOLD violation:

Static Timing Analysis

(STA) Basic (Part-8)

1.3 : LOGIC

GATES (Part - a)

DIGITAL BASIC 1.2 : DIGITAL

ARITHMETIC

DIGITAL BASIC 1.1 : NUMBER

SYSTEM

October (2)

May (1)

April (1)

March (1)

January (1)

2012 (15)

2011 (17)

2010 (5)

2008 (1)

Recent Visitors

NOT/Inverter

Y=A

AND

Y=A.B

OR

Y=A+B

Live Traffic Feed

A visitor from United

States arrived from

www.bing.com and

viewed VLSI

A

visitor from

Concepts:

VLSI

Kirkland,

United

BASIC 2 secs

ago

States viewed "Setup

and Hold Time

A visitor from

Bangalore,

Violation"

: Static...

9

Karnataka

secs ago arrived from

google.co.in and viewed

"DIGITAL BASIC - 1.5 :

Multiplexer (MUX) |VLSI

A visitor from India

Concepts" 44 secs ago

arrived from

vlsi-expert.com and

viewed ""Setup and Hold

Time" : Static Timing

A visitor from United

Analysis (STA) basic (Part

Kingdom arrived from

3a) |VLSI Concepts" 1

vlsi-expert.com and

min ago

viewed ""Examples Of

Setup and Hold time" :

Static Timing Analysis

A

visitor

from

Japan

(STA)

basic

(Part

3c)

arrived

from google.co.in

|VLSI Concepts"

15 mins

and

ago viewed ""Timing

Paths" : Static Timing

Analysis (STA) basic (Part

A visitor from India

1) |VLSI Concepts" 16

arrived from google.co.in

mins ago

and viewed "VLSI

Concepts"

22 mins

A

visitor from

Indiaago

viewed "Basic of Timing

Analysis in Physical

EDN: IC Design

Design

A

visitor|VLSI

fromConcepts"

Munich,

25 minsarrived

ago from

Bayern

Choosing a mobilestorage interface:

images.google.de and

viewed ""Setup and Hold eMMC or UFS

The future of IC design

Time" : Static Timing

Analysis (STA) basic (Part FPGA constraints for

the modern world:

A

United31

3a)visitor

|VLSIfrom

Concepts"

Product how-to

States

arrived from

mins ago

edaboard.com and viewed Moving averager

rejects noisy outlier

"Clock Reconvergence

values

Pessimism (CRP) basic

10 Ways to program

|VLSI

Concepts"

35Delhi,

mins your FPGA

A

visitor

from New

ago view

Delhi

arrived

Real-time

Get Feedjitfrom

Followers

NOR

Y=(A+B)

with Google Friend Connect

Members (359) More

Already a member? Sign in

NAND

Y=(A.B)

7/17/2016 10:30 PM

DIGITAL BASIC - 1.5 : Multiplexer (MUX) |VLSI Concepts

3 of 6

http://www.vlsi-expert.com/2013/12/digital-basic-15-multiplexer-mux.html

XOR

XNOR

Implementation of Boolean function using Multiplexer:

The Boolean function may be implemented in 2n to 1 multiplexer.

If we have a Boolean function of n variables, we take n-1 of these variables and connect them to the selection lines of a

multiplexer (lets say these are select variables).

The remaining single variable (MSB variable) of the function is used for the inputs of the multiplexer (lets say these are

input variable).

Now form the implementation table

First row lists all those minterms where input variable is complemented (say 0).

Second row lists all those minterms where input variable is in its normal form (say 1).

The minterms are circled as per the given Boolean function. Now use the following steps to find out final multiplexer

inputs.

If the 2 minterms in a column are not circled, 0 is placed to the corresponding multiplexer inputs.

If the 2 minterms in a column are circled, 1 is placed to the corresponding multiplexer inputs.

If the minterms in the second row is circled and the first row is not circled, apply second row of variable to

the corresponding multiplexer inputs.

If the minterms in the first row is circled and not the second row, apply first row of the variable to the

corresponding multiplexer inputs.

Example: Implementation of given function using 8 to 1 multiplexer

F(A,B,C,D) = (1,3,4,11,12,13,14,15)

Solution.

Total number of variable n = 4 (A,B,C,D)

Number of select lines: n-1= 3 (B, C, D)

The given function has 4 variable, so 16 possible minterms (0 15) are entered in the implementation table.

All the minterms are divided into 2 groups

The first group (0-7) minterms are entered in the first row (Variable A =0)

The second group (815) minterms are entered in the second row (Variable A= 1)

Circle the minterm number as per function, which you have to implement (in this case its 1,3,4,11,12,13,14,15)

Find out the multiplexer input as per above given steps.

Implementation Table

Given multiplexer is 8:1

Logic diagram

Example

7/17/2016 10:30 PM

DIGITAL BASIC - 1.5 : Multiplexer (MUX) |VLSI Concepts

4 of 6

http://www.vlsi-expert.com/2013/12/digital-basic-15-multiplexer-mux.html

Implement the following Boolean function using 8 : 1 MUX

F(A,B,C,D) = m(0,1,2,4,6,9,12,14)

Solution.

Select lines are B, C and D

Follow all the steps as per above points.

Example

Implement the following Boolean function with 8 : 1 multiplexer

F(A,B,C,D) = M (0,3,5,6,8,9,10,12,14)

Solution

The given maxterms are inverted to obtain minterms. From the minterms, we can implement the above Boolean function by using 8 :

1 multiplexer. Select lines are B, C and D, the input variable is A.

F(A,B,C,D) = m(1,2,4,7,11,13,15)

Example

Implement the following Boolean function with 8 : 1 multiplexer

F(A,B,C,D) = m (0,2,6,10,11,12,13) + d(3,8,14)

Solution.

The Boolean function has three dont care conditions which can be treated as either 0s or 1s. In this example dont care condition is

consider as 1.

You might also like:

DIGITAL BASIC 1.1 : NUMBER

SYSTEM

DIGITAL BASIC 1.4 : Combinational

Circuits

DIGITAL BASIC 1.3 : LOGIC

GATES (Part - a)

Linkwithin

Posted by VLSI EXPERT at 1:24 PM

+2 Recommend this on Google

Reactions:

6 comments:

7/17/2016 10:30 PM

DIGITAL BASIC - 1.5 : Multiplexer (MUX) |VLSI Concepts

5 of 6

http://www.vlsi-expert.com/2013/12/digital-basic-15-multiplexer-mux.html

Anonymous October 10, 2014 at 7:34 AM

Very good explaination

Reply

Anonymous November 4, 2014 at 6:12 PM

very helpful..are you going to post remaining concepts of digital designing

Reply

Replies

your VLSI November 4, 2014 at 11:45 PM

Yes I will do. but it will take some time.

Reply

Ketan Rathod January 2, 2016 at 11:21 PM

How many 16:1mux required for 64:1 mux

Reply

Ketan Rathod January 2, 2016 at 11:23 PM

Someone gave me answer as 4 -64/16= 4

And some as 5- 64/16=4+1(for next one)=5

So which one is correct 5 or 4

Reply

Replies

VlsiExpertGroup January 4, 2016 at 7:31 PM

if you can't use anyother gate.. like AND, OR, XOR .. then 5 is correct. but in case you can use any such basic gates - then 4

is correct answer.

Reply

Comment as:

Publish

Links to this post

Create a Link

Newer Post

Home

Older Post

Subscribe to: Post Comments (Atom)

Must Read Articles

"Setup and Hold

Time Violation" : S...

Synopsys Design

Constraints (SDC)...

Parasitic

Interconnect Corn...

Clock

Reconvergence P...

"Examples Of Setup

and Hold time" : St...

www.vlsi-expert.com

www.vlsi-expert.com

www.vlsi-expert.com

www.vlsi-expert.com

www.vlsi-expert.com

7/17/2016 10:30 PM

DIGITAL BASIC - 1.5 : Multiplexer (MUX) |VLSI Concepts

6 of 6

http://www.vlsi-expert.com/2013/12/digital-basic-15-multiplexer-mux.html

"Timing Paths" :

Static Timing Anal...

Maximum Clock

Frequency : Static...

Fixing Setup and

Hold Violation : St...

"Time Borrowing" :

Static Timing Anal...

Design constraint :

Maximum transitio...

www.vlsi-expert.com

www.vlsi-expert.com

www.vlsi-expert.com

www.vlsi-expert.com

www.vlsi-expert.com

AddThis

7/17/2016 10:30 PM

Вам также может понравиться

- SCM - 11 01 2005Документ18 страницSCM - 11 01 2005Marius FerdyОценок пока нет

- Csi 3131 Midterm 2015Документ10 страницCsi 3131 Midterm 2015Carlos MorenoОценок пока нет

- KTU B-Tech Questions SolutionДокумент39 страницKTU B-Tech Questions SolutionSreenath SreeОценок пока нет

- Implementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKДокумент16 страницImplementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKhamim ahmedОценок пока нет

- Implementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKДокумент16 страницImplementation and Code Generation of Digital Circuits and System Using MATLAB & SIMULINKVLSISD36 Edwin DominicОценок пока нет

- Efficient Implementation of 16-Bit Multiplier-Accumulator Using Radix-2 Modified Booth Algorithm and SPST Adder Using VerilogДокумент12 страницEfficient Implementation of 16-Bit Multiplier-Accumulator Using Radix-2 Modified Booth Algorithm and SPST Adder Using VerilogAnonymous e4UpOQEPОценок пока нет

- Software Process and RequirementДокумент25 страницSoftware Process and RequirementUnicorn54Оценок пока нет

- CS201 Solved Subjective Final Term by JunaidДокумент22 страницыCS201 Solved Subjective Final Term by JunaidAtif MubasharОценок пока нет

- Fuzzy ModelingДокумент65 страницFuzzy ModelingAbouzar SekhavatiОценок пока нет

- Matrix Chain MultiplicationДокумент20 страницMatrix Chain MultiplicationHarsh Tibrewal100% (1)

- Efficient Implementation of A Pseudorandom Sequence Generator For High-Speed Data CommunicationsДокумент8 страницEfficient Implementation of A Pseudorandom Sequence Generator For High-Speed Data CommunicationsRekhaPadmanabhanОценок пока нет

- 08.508 DSP Lab Manual Part-BДокумент124 страницы08.508 DSP Lab Manual Part-BAssini Hussain100% (2)

- CS201 Final Term Subjectivebymoaaz PDFДокумент18 страницCS201 Final Term Subjectivebymoaaz PDFMuhammad ZeeshanОценок пока нет

- Data Structures - Data Structures - : Lecture 1: IntroductionДокумент55 страницData Structures - Data Structures - : Lecture 1: IntroductionMohamed TahaОценок пока нет

- Cse625h3 2022Документ3 страницыCse625h3 2022Umair AhmadОценок пока нет

- Logic Design Syllabus SummaryДокумент193 страницыLogic Design Syllabus SummaryAnup Konnur100% (1)

- Logika Kombinasi II (Lie)Документ10 страницLogika Kombinasi II (Lie)Desi NoviantiОценок пока нет

- Simulation Lab Manual 3107Документ30 страницSimulation Lab Manual 3107rajee101Оценок пока нет

- Introduction To VLSI SystemДокумент16 страницIntroduction To VLSI SystemPrabakaran RajendranОценок пока нет

- Introduction to Model Order Reduction assignmentsДокумент9 страницIntroduction to Model Order Reduction assignmentsSaheed ImranОценок пока нет

- Java ExamДокумент5 страницJava ExamtmrubunyaОценок пока нет

- A Novel Architecture of RNS Based Lifting Integer Wavelet Transform (Iwt) and Comparative Study With Other Binary and Non-Binary DWTДокумент9 страницA Novel Architecture of RNS Based Lifting Integer Wavelet Transform (Iwt) and Comparative Study With Other Binary and Non-Binary DWTAnonymous e4UpOQEPОценок пока нет

- Data Structures and ProgrammingДокумент162 страницыData Structures and ProgramminggullisathaОценок пока нет

- DSP Lab Manual For ECE 3 2 R09Документ147 страницDSP Lab Manual For ECE 3 2 R09Jandfor Tansfg Errott100% (2)

- Cs201 Final Notce by Mohsin Raza (1) - 1Документ30 страницCs201 Final Notce by Mohsin Raza (1) - 1Umme Rubab saleemОценок пока нет

- Simulation of a Communication SystemДокумент15 страницSimulation of a Communication SystemArnab NiloyОценок пока нет

- ECE.488 Multi-Various Analog ControlsДокумент3 страницыECE.488 Multi-Various Analog ControlsphoebezzОценок пока нет

- Implementation of Low Power and High Speed Multiplier-Accumulator Using SPST Adder and VerilogДокумент8 страницImplementation of Low Power and High Speed Multiplier-Accumulator Using SPST Adder and Verilogsujaganesan2009Оценок пока нет

- FSMDДокумент18 страницFSMDjagadeshjОценок пока нет

- Delayed Branch Logic: Texas Instruments TMS320 Is A Blanket Name For A Series ofДокумент13 страницDelayed Branch Logic: Texas Instruments TMS320 Is A Blanket Name For A Series ofnomadcindrellaОценок пока нет

- Part 3Документ33 страницыPart 3ketrisОценок пока нет

- Lab1FA11 PDFДокумент11 страницLab1FA11 PDFaxecaleverОценок пока нет

- 2013 Lab MatlabSimulinkДокумент9 страниц2013 Lab MatlabSimulinkwilldota100% (1)

- Simulation tools for power electronicsДокумент21 страницаSimulation tools for power electronicsAmy HicksОценок пока нет

- DSP - Manual PartДокумент12 страницDSP - Manual PartShivani AgarwalОценок пока нет

- VLSI Syllabus 2013-14Документ43 страницыVLSI Syllabus 2013-14Eric DharanОценок пока нет

- Simulation: 4.1 Introduction To MATLAB/SimulinkДокумент11 страницSimulation: 4.1 Introduction To MATLAB/SimulinkSaroj BabuОценок пока нет

- Signal Processing and CommunicationsДокумент38 страницSignal Processing and CommunicationsoveiskntuОценок пока нет

- Cis016-2, Cis116-2 & Pat001-2Документ5 страницCis016-2, Cis116-2 & Pat001-2ruslanas reОценок пока нет

- Asn HS07Документ6 страницAsn HS07saravanan_nallusamyОценок пока нет

- Matlab PrimerДокумент27 страницMatlab Primerneit_tadОценок пока нет

- DSP Lab Manual PallaviДокумент67 страницDSP Lab Manual Pallavib vamshi100% (1)

- Fuzzy logic calculation of train braking distance using MatlabДокумент11 страницFuzzy logic calculation of train braking distance using MatlabMilan MilosavljevicОценок пока нет

- Fast Fourier Transform: VLSI Architectures: Vladimir StojanovićДокумент26 страницFast Fourier Transform: VLSI Architectures: Vladimir StojanovićTharun ThampanОценок пока нет

- C Lang Quest AnsДокумент17 страницC Lang Quest AnsArun Kumar GargОценок пока нет

- Machine Learning Techniques for Pattern Recognition and ClassificationДокумент35 страницMachine Learning Techniques for Pattern Recognition and ClassificationPhuc SJОценок пока нет

- Chapter 1Документ36 страницChapter 1Gauri100% (1)

- Labs-TE Lab Manual DSPДокумент67 страницLabs-TE Lab Manual DSPAntony John BrittoОценок пока нет

- CS201 Final Term Solved SUBJECTIVE by JUNAID-1Документ20 страницCS201 Final Term Solved SUBJECTIVE by JUNAID-1abaidullah bhattiОценок пока нет

- Assignment 4 Rishab MatlabДокумент7 страницAssignment 4 Rishab MatlabBABAJIОценок пока нет

- CSA Lab 8Документ4 страницыCSA Lab 8vol damОценок пока нет

- 17IT8029Документ7 страниц17IT8029AlexОценок пока нет

- CS101 Final Term ObjectiveДокумент17 страницCS101 Final Term ObjectiveMuhammad Aamir SialОценок пока нет

- A MatlabSimulink Toolbox For Inversion of Local Linear Model Trees PDFДокумент8 страницA MatlabSimulink Toolbox For Inversion of Local Linear Model Trees PDFAfi LAОценок пока нет

- CMPS Lab ManualДокумент64 страницыCMPS Lab Manualomi ChavanОценок пока нет

- MCSE011Документ18 страницMCSE011Anusree AntonyОценок пока нет

- Matlab Simulink IntroДокумент14 страницMatlab Simulink IntrobdeepeshОценок пока нет

- Performance Evaluation by Simulation and Analysis with Applications to Computer NetworksОт EverandPerformance Evaluation by Simulation and Analysis with Applications to Computer NetworksОценок пока нет

- Social Systems Engineering: The Design of ComplexityОт EverandSocial Systems Engineering: The Design of ComplexityCésar García-DíazОценок пока нет

- Multiple Models Approach in Automation: Takagi-Sugeno Fuzzy SystemsОт EverandMultiple Models Approach in Automation: Takagi-Sugeno Fuzzy SystemsОценок пока нет

- CSC GateДокумент20 страницCSC Gatejeravi84100% (2)

- Net PhysicsДокумент25 страницNet Physicsjeravi84Оценок пока нет

- DIGITAL COMMUNICATION SYSTEMS SyllabusДокумент2 страницыDIGITAL COMMUNICATION SYSTEMS Syllabusjeravi84Оценок пока нет

- Database: GATE CS Topic Wise QuestionsДокумент42 страницыDatabase: GATE CS Topic Wise QuestionsSagar ChingaliОценок пока нет

- Apt SHRДокумент70 страницApt SHRjeravi84Оценок пока нет

- C-Programming GATE Computer Science Postal Study MaterialДокумент12 страницC-Programming GATE Computer Science Postal Study MaterialtruptiОценок пока нет

- Dslam Cpu Card ProgrammingДокумент2 страницыDslam Cpu Card Programmingjeravi84Оценок пока нет

- General Aptitude Reasoning GATE PSUsДокумент17 страницGeneral Aptitude Reasoning GATE PSUsasif shaikhОценок пока нет

- Computer Network by Kanodia PublicationДокумент30 страницComputer Network by Kanodia PublicationNeha BhavsarОценок пока нет

- CS Gatebook-2018 (Final) WebДокумент13 страницCS Gatebook-2018 (Final) Webjeravi84Оценок пока нет

- Imp Written BitsДокумент5 страницImp Written Bitsjeravi84Оценок пока нет

- Disaster Management - CBSE Class XI (Shashidthakur23.wordpress - Com) PDFДокумент63 страницыDisaster Management - CBSE Class XI (Shashidthakur23.wordpress - Com) PDFjeravi84Оценок пока нет

- Upkar Radar EngineeringДокумент9 страницUpkar Radar Engineeringjeravi84Оценок пока нет

- Shortcuts in Quantitative Aptitude For Competitive ExamsДокумент113 страницShortcuts in Quantitative Aptitude For Competitive Examsjeravi84Оценок пока нет

- Jawaharlal Nehru Technological University Anantapur B. Tech III-I Sem. (EEE) L T P C 3 1 0 3 15A04510 Digital Circuits and Systems (Moocs-I) Course OutcomesДокумент2 страницыJawaharlal Nehru Technological University Anantapur B. Tech III-I Sem. (EEE) L T P C 3 1 0 3 15A04510 Digital Circuits and Systems (Moocs-I) Course Outcomesjeravi84Оценок пока нет

- Classroom vocabulary bookДокумент15 страницClassroom vocabulary bookjeravi84Оценок пока нет

- Algorithms Data Structures GATE Computer Science Postal Study MaterialДокумент15 страницAlgorithms Data Structures GATE Computer Science Postal Study MaterialCrystalОценок пока нет

- Current Affairs Jan2017Документ77 страницCurrent Affairs Jan2017SantoshKumarОценок пока нет

- Vocabulary Builder Book-2 (Animals)Документ37 страницVocabulary Builder Book-2 (Animals)jeravi84Оценок пока нет

- Objective Electromagnetic QuestionsДокумент10 страницObjective Electromagnetic Questionsjeravi840% (1)

- 300AH 400AH 1000AH Battery Sets SMPS PP 25A Transfer PostingДокумент4 страницы300AH 400AH 1000AH Battery Sets SMPS PP 25A Transfer Postingjeravi84Оценок пока нет

- BSNL JE (TTA) 28th 2nd Shift Answer KeyДокумент39 страницBSNL JE (TTA) 28th 2nd Shift Answer KeyTushitaОценок пока нет

- Microprocessor & microcontroller introductionДокумент20 страницMicroprocessor & microcontroller introductionjeravi84Оценок пока нет

- Je BitsДокумент5 страницJe Bitsjeravi84Оценок пока нет

- BSNL Je Key 110Документ38 страницBSNL Je Key 110jeravi84Оценок пока нет

- A.C. Network Anaylsis: Learning ObjectivesДокумент28 страницA.C. Network Anaylsis: Learning ObjectivesDio Ilham Tirta AdiОценок пока нет

- The resistances in the equivalent star network are:R1 = 20 QR2 = 30 QR3 = 50 QДокумент11 страницThe resistances in the equivalent star network are:R1 = 20 QR2 = 30 QR3 = 50 Qjeravi84Оценок пока нет

- Genenet ABtLtrY Tesr 1-40 Multiple Choice QuestionsДокумент29 страницGenenet ABtLtrY Tesr 1-40 Multiple Choice Questionsjeravi84Оценок пока нет

- Timebase CircuitsДокумент2 страницыTimebase Circuitsjeravi84Оценок пока нет

- Clap Switch PresentationДокумент9 страницClap Switch Presentation20EUEE018 - DEEPAK. MОценок пока нет

- TODX296: Fiber Optic Transceiving Module For Duplex Digital Signal CommunicationДокумент10 страницTODX296: Fiber Optic Transceiving Module For Duplex Digital Signal CommunicationwesbgОценок пока нет

- Broadcom IP2 IP3Документ7 страницBroadcom IP2 IP3shengquan_hu1512Оценок пока нет

- Fiber Optic Components For High Power Fiber Laser ApplicationsДокумент2 страницыFiber Optic Components For High Power Fiber Laser ApplicationsDK PhotonicsОценок пока нет

- ANALOGE AND DIGITAL ELECTRONICS MCQ NOTESДокумент7 страницANALOGE AND DIGITAL ELECTRONICS MCQ NOTESAkshay KarmareОценок пока нет

- Th327 ModsДокумент32 страницыTh327 Modsva7Оценок пока нет

- Optical Computers: Presented by Adarsh R. 1AY06EC104Документ16 страницOptical Computers: Presented by Adarsh R. 1AY06EC104Sonia SinghОценок пока нет

- Photovoltaic Solar Cells PresentationДокумент23 страницыPhotovoltaic Solar Cells Presentationmohmmad1972Оценок пока нет

- Second Generation Solar CellsДокумент4 страницыSecond Generation Solar CellsAboothahir AfzalОценок пока нет

- Hench and West, The Sol-Gel Process, Chem Rev 90 (1990) 33Документ40 страницHench and West, The Sol-Gel Process, Chem Rev 90 (1990) 33Cristiano Nunes100% (1)

- Flash ADC Design Challenges and MethodologyДокумент15 страницFlash ADC Design Challenges and MethodologyJagadeep KumarОценок пока нет

- TOP244Документ52 страницыTOP244Rimla OtenОценок пока нет

- Minimize Inrush Current in Power TransformersДокумент12 страницMinimize Inrush Current in Power TransformersaocalayОценок пока нет

- Soft Starter PDFДокумент6 страницSoft Starter PDFPaun AlОценок пока нет

- Radar Basics - Traveling Wave TubeДокумент1 страницаRadar Basics - Traveling Wave TubeVinay Nagnath JokareОценок пока нет

- All Pcb-Tda2030 - 2.1 ChannellДокумент18 страницAll Pcb-Tda2030 - 2.1 ChannellJose GarciaОценок пока нет

- OLED - Saurabh YadavДокумент5 страницOLED - Saurabh Yadavsaysky100% (1)

- 1673Документ3 страницы1673heribertosfaОценок пока нет

- Permanant Magnet Synchronous MotorДокумент47 страницPermanant Magnet Synchronous Motorsubaganesh232Оценок пока нет

- Philips SW3660 Service ID4069Документ14 страницPhilips SW3660 Service ID4069sony reseОценок пока нет

- Appendix A: Parts listДокумент28 страницAppendix A: Parts listproctepОценок пока нет

- Analogue DialogueДокумент56 страницAnalogue DialoguetorinomgОценок пока нет

- Small Signal Transistors (NPN) : Dimensions in Inches and (Millimeters)Документ4 страницыSmall Signal Transistors (NPN) : Dimensions in Inches and (Millimeters)ausper01Оценок пока нет

- ConnexДокумент7 страницConnexpanktiОценок пока нет

- Solid-state Timer Guide for H3DE SeriesДокумент33 страницыSolid-state Timer Guide for H3DE SeriesHemraj Singh RautelaОценок пока нет

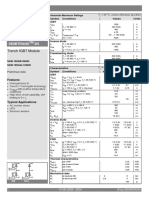

- SKM 195GB126DN: Semitrans 2NДокумент4 страницыSKM 195GB126DN: Semitrans 2NDilip GamiОценок пока нет

- Mit Lab 01Документ6 страницMit Lab 01api-247714257Оценок пока нет

- Manual de Usuaria de TV 14lk14Документ28 страницManual de Usuaria de TV 14lk14alexis marcanoОценок пока нет

- Thermal Management EELДокумент10 страницThermal Management EELDamisha DamishaОценок пока нет

- Manual Masterpact NTДокумент182 страницыManual Masterpact NTbillitusОценок пока нет