Академический Документы

Профессиональный Документы

Культура Документы

Manual Notebook H12Y

Загружено:

gm799763Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Manual Notebook H12Y

Загружено:

gm799763Авторское право:

Доступные форматы

5

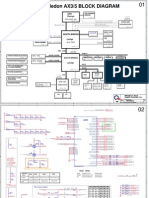

PG01 Cover Page

PG02 Block Diagram

PG03 Yonah (HOST)

PG04 Yonah (POWER)

PG05 CPU POWER

PG06 Calistoga (HOST/IGDS/DMI)

PG07 Calistoga (DDR2 I/F)

PG08 Calistoga (PWR/NCTF)

PG09 Calistoga (PWR/GND)

PG10 DDR2 SO-DIMM

PG11 CRT/LCD CON

PG12 ICH7-M (GTL+/DMI/PCI)

PG13 ICH7-M (PM/GPIO/LPC/IO)

PG14 ICH7-M (PWR/GND)

PG15 System Pull Up/Down

PG16 CLK GEN

PG17 HDD/CDROM CON

PG18 LAN

PG19 MINIPCI CON

PG20 1394+CardReader Controller

PG21 Audio Codec

PG22 Audio Amp

PG23 KBC M38857 KB

PG24 LPC (TPM/DEBUG CON)/FAN

PG25 I/O (1394/SATA/MDC/BT/USB)

PG26 PCI-E NEWCARD

PG27 PCI-E MINICARD

PG28 LED

PG29 PWR/WL/BT ON_OFF

PG30 PWR (3V/5V)

PG31 PWR (0.9V_SW/1.8V)

PG32 PWR(VCC_P/1.5V_SW/2.5V_SW)

PG33 PWR OK

PG34 DC IN/CHARGE

PG35 SPARE PARTES

PG36 POWER SEQUENCE

PG37 POWER DIAGRAM

PG38 History

Model : H12YV1 Rev:A

D

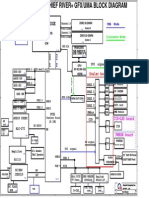

Intel Yonah/Merom+Calistoga 945GM+ICH7-M

Revision History

A

2006/11/24

ORIGINAL RELEASE

PCB STACK UP

B

LAY1

LAY2

LAY3

LAY4

LAY5

LAY6

LAY7

LAY8

TOP

GND1

IN1

IN2

VCC

IN3

GND2

BOTTOM

Project Name

H12YV1

Pag Title

Cover Page

Document

Number

Date: Friday, November 24, 2006

5

Rev

A

Sheet 1

of 38

82+A32000+00A

1

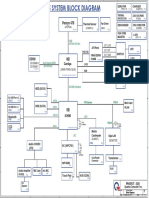

H12YT1 System Block Diagram

Differential 100MHz(GMCH/ICH7-M/

NEWCARD/MINICARD/SATA)

96MHz(GMCH)

48MHz(ICH7-M/Debug Port)

(TBD)

Micro-FCPGA 478

CPU TEMP

MONITOR

MAX6692

PG04

THERMDA/C

PG03,04

AGTL+ BUS

533/667MHz(Yonah)

667MHz(Merom Only)

PG16

DDR2 SO-DIMM x1

Yonah/

Merom

Differential

133/166MHz

CLK GEN

ICS954226

33MHz(ICH7-M/1394/LAN/KBC

/Debug Port/MINIPCI)

14.318MHz

PG11

Differential

133/166MHz

DDR2-A 400MHz/533MHz/667MHz

LVDS

12.1" Wide XGA

TFT LCD Panel

Calistoga

945GM

DDR2 Single Channel

ODD

Micro-FCBGA 1466

CRT

CON

RGB

PG06,07,08,09

PG17

PG10

DMI

PG11

SATA HDD

USB 2.0

IDE

PG17

PG21

PG25

SATA

HD Audio

CODEC

ALC262

ICH7-M

HD Audio

PG25

Port 0

Port 2, 4, 6

Bluetooth

Module

USB

PORT*3

PCI Express

PG27

mBGA652

Port 1

PCI Express

Mini Card

SPI

PG22

AMP

MAX9710

PCI 2.3

LM833MMX

PG22

Line Out

MIC In

AMP

MAX4411

PG22

PG25

Port 7

PG12,13,14

Flash ROM

LPC

PG13

SPK

SPK

E.phone

RJ11

Jack

PG22

TPM

1.2

Daughter Board

PG24

KBC

M38857

LAN REALTEK

RTL8100CL

PG23

PG22

SMBus Diagram

Clock Gen

ICH7-M

Port 2

NEWCARD

CON

MDC

INT_MIC

EXT_MIC

PG26

Port 1

SMBICH_

CLK/DATA

SMBus

Switch

SMBICH_SW

CLK/DATA

SMBus

Switch

DDR2

SO-DIMM

PCI-E

NEWCARD

PWR_RCLKEN

A

SMB_KBC_CLK/DATA

PCI-E

MINICARD

BATTERY

MAX6692

Thermal Sensor

KBC

KeyBoard

PG18

PG19

IEEE1394 +

CardReader

Controller

OZ128TN

PG20

IEEE

1394

Port

RJ45

Jack

Touch

Pad

MINIPCI CON

(Reserve For

Debug

Function)

PG25

Daughter Board

4 in 1

Card

Reader

Conn

PG18

Charger PWM

Controller

PG34

Battery

Project Name

CPU FAN

H12YV1

Pag Title

PG24

Block Diagram

Document

Number

M38857

5

Rev

A

Sheet 2

of 38

82+A32000+00A

Date: Friday, November 24, 2006

1

6 AGTL+_ADSTB#[0:1]

AGTL+_ADSTB#0

AGTL+_ADSTB#1

6

6

6

6

6

6

L2

V4

H1

E2

G5

F1

E1

H5

F21

G6

E4

H4

G2

6 AGTL+_ADS#

6 AGTL+_BNR#

6 AGTL+_BPRI#

6 AGTL+_BR0#

AGTL+_DBSY#

AGTL+_DEFER#

AGTL+_DRDY#

6 AGTL+_HIT#

AGTL+_HITM#

AGTL+_LOCK#

AGTL+_TRDY#

6 AGTL+_RS#[0:2]

AGTL+_RS#0

AGTL+_RS#1

AGTL+_RS#2

F3

F4

G3

AGTL+_CPURST# B1

6 AGTL+_CPURST#

CPU_IERR#

D20

ADSTB0#

ADSTB1#

ADS#

BNR#

BPRI#

BR0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

LOCK#

TRDY#

RS0#

RS1#

RS2#

RESET#

IERR#

AGTL+_DINV#0

AGTL+_DINV#1

AGTL+_DINV#2

AGTL+_DINV#3

DINV0#

DINV1#

DINV2#

DINV3#

J26

M26

V23

AC20

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

G22

N25

Y25

AE24

AGTL+_DSTBP#0

AGTL+_DSTBP#1

AGTL+_DSTBP#2

AGTL+_DSTBP#3

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

H23

M24

W24

AD23

AGTL+_DSTBN#0

AGTL+_DSTBN#1

AGTL+_DSTBN#2

AGTL+_DSTBN#3

12 CPU_A20M#

12 CPU_DPSLP#

12 CPU_FERR#

12 CPU_IGNNE#

12 CPU_INIT#

12 CPU_INTR

12 CPU_NMI

12 CPU_PWRGD

A6

B5

A5

C4

B3

C6

B4

D6

A20M#

DPSLP#

FERR#/PBE#

IGNNE#

INIT#

LINT0/INTR

LINT1/NMI

PWRGOOD

6 CPU_CPUSLP#

12 CPU_SMI#

12 CPU_STPCLK#

D7

A3

D5

SLP#

SMI#

STPCLK#

AE6

5,13 PM_DPRSTP#

E5

A22

A21

16 CLK_CPU_BCLK

16 CLK_CPU_BCLK#

6,13 PM_THERMTRIP#

13 PM_SYS_RESET#

R181

0_5%

0402R

PM_SYS_RESET#

4 THERMDA

4 THERMDC

CPU_THERMTRIP#

CPU_PROCHOT#

5 CPU_PROCHOT#

R222

0_5%_OP

0402R

CPU_DBR#

6 AGTL+_DPWR#

5

5

5

5

5

5

5

R279

R280

R283

R284

R281

R285

R282

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

0_5%

0_5%

0_5%

0_5%

0_5%

0_5%

0_5%

VCC1_5_SW

C273

10U_Y5V

0805C

AGTL+_DINV#[0:3]

C252

0.01U_X7R

0402C

Close to PIN B26

0402R

0402R

0402R

0402R

0402R

0402R

0402R

VID0

VID1

VID2

VID3

VID4

VID5

VID6

Yonah(120mA)

Merom(130mA)

A24

A25

C7

D21

R26

U26

U1

V1

COMP0

COMP1

COMP2

COMP3

BPM0#

BPM1#

BPM2#

BPM3#

AD4

AD3

AD1

AC4

BPM#0

BPM#1

BPM#2

BPM#3

BCLK0

BCLK1

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

DBR#

D24

DPWR#

AD6

AF5

AE5

AF4

AE3

AF2

AE2

VID0

VID1

VID2

VID3

VID4

VID5

VID6

B26

VCCA

C26

D25

BSEL0

BSEL1

BSEL2

B22

B23

C21

27.4_1%

54.9_1%

27.4_1%

54.9_1%

0402R

0402R

0402R

0402R

D

TP8

TP3

TP5

TP7

TCK

TDI

TDO

TMS

AC5

AA6

AB3

AB5

CPU_TCK

CPU_TDI

CPU_TDO

CPU_TMS

1K_1%_OP

51_1%

0402R

0402R

1K_1%

0402R

R230

Strapping option

R237

R236

TRST#

AB6

CPU_TRST#

PRDY#

PREQ#

AC2

AC1

BPM#4

BPM#5

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

RSVD11

B25

RSVD12

T22

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

D2

F6

D3

C1

AF1

D22

C23

C24

5 VCCSENSE

AF7

VCCSENSE

NC

5 VSSSENSE

AE7

VSSSENSE

GTLREF

AGTL+_DSTBP#[0:3] 6

AGTL+_DSTBN#[0:3] 6

R579

R238

TEST1

TEST2

DPRSTP#

C20

1K_1%

1K_1%

BSEL0 8,16

BSEL1 8,16

BSEL2 8,16

0402R

0402R

VCC_P

TP2

TP4

A#[32-39], APM#[0-1]:

Leave escape routing on for

future functionality

VCC_P

R576

1K_1%

0402R

A2

AD26

CPU_GTLREF

GTLREF= 2/3*VCCP+-2%

0.5" max length

Yonah

MFCPGA479

VCCSENSE/VSSSENSE

trace width & space 18mil/7mil

, Length match to within 25mils

R578

R577

R138

R139

PSI#

JTK

PM_PSI#

COMP0

COMP1

COMP2

COMP3

R238 for A0, A1, B0

Stepping used

DEB

HOST BUS

U54B

RESERVE

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

E22 AGTL+_D#0

F24 AGTL+_D#1

E26 AGTL+_D#2

H22 AGTL+_D#3

F23 AGTL+_D#4

G25 AGTL+_D#5

E25 AGTL+_D#6

E23 AGTL+_D#7

K24 AGTL+_D#8

G24 AGTL+_D#9

J24 AGTL+_D#10

J23 AGTL+_D#11

H26 AGTL+_D#12

F26 AGTL+_D#13

K22 AGTL+_D#14

H25 AGTL+_D#15

N22 AGTL+_D#16

K25 AGTL+_D#17

P26 AGTL+_D#18

R23 AGTL+_D#19

L25 AGTL+_D#20

L22 AGTL+_D#21

L23 AGTL+_D#22

M23 AGTL+_D#23

P25 AGTL+_D#24

P22 AGTL+_D#25

P23 AGTL+_D#26

T24 AGTL+_D#27

R24 AGTL+_D#28

L26 AGTL+_D#29

T25 AGTL+_D#30

N24 AGTL+_D#31

AA23 AGTL+_D#32

AB24 AGTL+_D#33

V24 AGTL+_D#34

V26 AGTL+_D#35

W25 AGTL+_D#36

U23 AGTL+_D#37

U25 AGTL+_D#38

U22 AGTL+_D#39

AB25 AGTL+_D#40

W22 AGTL+_D#41

Y23 AGTL+_D#42

AA26 AGTL+_D#43

Y26 AGTL+_D#44

Y22 AGTL+_D#45

AC26 AGTL+_D#46

AA24 AGTL+_D#47

AC22 AGTL+_D#48

AC23 AGTL+_D#49

AB22 AGTL+_D#50

AA21 AGTL+_D#51

AB21 AGTL+_D#52

AC25 AGTL+_D#53

AD20 AGTL+_D#54

AE22 AGTL+_D#55

AF23 AGTL+_D#56

AD24 AGTL+_D#57

AE21 AGTL+_D#58

AD21 AGTL+_D#59

AE25 AGTL+_D#60

AF25 AGTL+_D#61

AF22 AGTL+_D#62

AF26 AGTL+_D#63

ICH

J4

L4

M3

K5

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

CLK

AGTL+_A#3

AGTL+_A#4

AGTL+_A#5

AGTL+_A#6

AGTL+_A#7

AGTL+_A#8

AGTL+_A#9

AGTL+_A#10

AGTL+_A#11

AGTL+_A#12

AGTL+_A#13

AGTL+_A#14

AGTL+_A#15

AGTL+_A#16

AGTL+_A#17

AGTL+_A#18

AGTL+_A#19

AGTL+_A#20

AGTL+_A#21

AGTL+_A#22

AGTL+_A#23

AGTL+_A#24

AGTL+_A#25

AGTL+_A#26

AGTL+_A#27

AGTL+_A#28

AGTL+_A#29

AGTL+_A#30

AGTL+_A#31

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

Layout note of COMP0,2 : 18mil wide traces and

shorter than 0.5'' traces.

Layout note of COMP1,3 : 5mil wide trace and shorter

than 0.5" trace.

THM

6 AGTL+_A#[3:31]

K3

H2

K2

J3

L5

AGTL+_D#[0:63] 6

U54A

AGTL+_REQ#0

AGTL+_REQ#1

AGTL+_REQ#2

AGTL+_REQ#3

AGTL+_REQ#4

VID

6 AGTL+_REQ#[0:4]

R575

2K_1%

0402R

Yonah/Merom CPU BSEL[2:0]

Yonah

MFCPGA479

VCC_P

BSEL[2]

L

L

L

L

3.0" max length

R232

R231

75_1%

56_1%

0402R

0402R

CPU_PROCHOT#

CPU_IERR#

0402R

0402R

0402R

0402R

0402R

CPU_TDI

CPU_TMS

CPU_TDO

AGTL+_CPURST#

CPU_DBR#

BSEL[1]

L

L

H

H

BSEL[0]

L

H

L

H

BCLK frequency

Reserved

133MHz(Yonah Only)

Reserved

166MHz

2.0" max length

R184

R183

R182

R137

R223

150_1%

39_1%

51_1%_OP

51_1%_OP

150_1%_OP

R168

R169

27.4_1%

680_1%

0402R

0402R

CPU_TCK

CPU_TRST#

Project Name

H12YV1

ITP Debug port not used strapping option

Pag Title

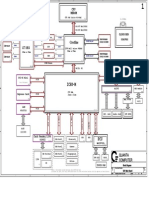

Yonah (HOST)

Document

Number

Rev

A

Sheet 3

of 38

82+A32000+00A

Date: Friday, November 24, 2006

1

VCC_CORE

U54D

D

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

U54C

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCCP0

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCC

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

during power up, Iccp for Yonah processor can spike up to 6.0

A, Once core Vcc is enabled, Iccp max spec of 2.5 A still applies

C179

0.1U_Y5V

0402C

C180

0.1U_Y5V

0402C

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

C181

0.1U_Y5V

0402C

C244

0.1U_Y5V

0402C

VCC_P

Yonah(2.5A)

Merom(2A)

C246

0.1U_Y5V

0402C

C247

0.1U_Y5V

0402C

C245

39P_NPO

0402C

C503

10U_X5R

0805C

C484

10U_X5R

0805C

VCC_CORE

Yonah (36A)

Merom (44A)

C485

10U_X5R

0805C

C492

10U_X5R

0805C

C493

10U_X5R

0805C

C496

10U_X5R

0805C

C497

10U_X5R

0805C

C504

10U_X5R

0805C

C505

10U_X5R

0805C

C483

10U_X5R

0805C

C490

10U_X5R

0805C

C491

10U_X5R

0805C

C494

10U_X5R

0805C

C495

10U_X5R

0805C

C501

10U_X5R

0805C

C502

10U_X5R

0805C

C192

10U_X5R

0805C

C204

10U_X5R

0805C

C214

10U_X5R

0805C

C215

10U_X5R

0805C

C236

10U_X5R

0805C

C206

10U_X5R

0805C

C207

10U_X5R

0805C

C216

10U_X5R

0805C

C217

10U_X5R

0805C

C237

10U_X5R

0805C

C191

1000P_X7R

0402C

C235

1000P_X7R

0402C

C193

1000P_X7R

0402C

V13

1000P_2.5K

1206C

C248

1000P_X7R

0402C

C208

39P_NPO

0402C

C205

10U_X5R

0805C

+ C486

C_D

220U_2V_SPCAP

A4

A8

A11

A14

A16

A19

A23

A26

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3

V3

1000P_2.5K

1206C

For EMI

Yonah

MFCPGA479

VCC3

R568

200_1% 0402R

VCC3_CPUTS

C507

1U_Y5V

0603C

R570

10K_5%

0402R

Yonah

MFCPGA479

U58

3 THERMDA

3 THERMDC

C508 2200P_X7R

0402C

29 PM_THRM_SHUTDOWN#

1

2

3

4

VCC

SCLK

DXP

SDA

DXN ALERT#

OVERT# GND

8

7

6

5

R569

0_5%_OP

0402R

SMB_KBC_CLK 23,34

SMB_KBC_DATA 23,34

PM_THRM# 13,15

MAX6692MUA+

uSOIC8

Route THERMDA and THERMDC on same layer.

10mil trace/10mil spacing

Project Name

H12YV1

Pag Title

Yonah (POWER)

82+A32000+00A

Document

Number

Date: Friday, November 24, 2006

5

Rev

A

Sheet 4

of 38

VIN

VCC5_SW

Modify RB.39

C600

0.01U_X7R_OP

0402C

RBIAS

R323

68K_1%

0402R

21

R292

0_5%

0402R

OCSET

VSUM

17

VO

16

D4

D3

D2

D1

G

S3

S2

S1

5

6

7

8

D4

D3

D2

D1

G

S3

S2

S1

4

3

2

1

4

3

2

1

D4

D3

D2

D1

G

S3

S2

S1

5

6

7

8

D4

D3

D2

D1

4

3

2

1

LGTE

G

S3

S2

S1

5

6

7

8

PHSE

GND

4

3

2

1

PWM

JMP

JP_10A

DCR=1.1m Ohm

20K_1%

0402R

L8

VCC5_SW

IMVP6_VSUM

R270

5.1K_1%

0402R

IMVP6_ISEN2

IMVP6_VO

R269

R268

10K_1%

10_1%

0402R

0402R

FMJ-10402-R36_24A

CHOKE_10X11_5MM

5

6

7

8

D4

D3

D2

D1

G

S3

S2

S1

D4

D3

D2

D1

G

S3

S2

S1

ISL6208CBZ

SOIC8

5

6

7

8

R566

5

6

7

8

U20

IRF7807ZPBF

SOIC8

D55

SS34A_3A

SOD106

R207

0_5%

0402R

0.002_1%_OP

RL3264

R205

0_5%_OP

0402R

R206

0_5%

0402R

R204

0_5%_OP

0402R

+ C499

+ C500

+ C498

6m Ohm

C238

1U_Y5V

0603C

DROOP

14

VSEN

R185

100_1% 0402R

R186

100_1% 0402R

C209

0.01U_X7R

0402C

VCCSENSE/VSSSENSE

trace width & space 18mil/7mil

, Length match to within 25mils

RT2

10K_5%_NTC

0603R

VCCSENSE 3

VSSSENSE 3

Close to Phase 1

Inductor

C289

0.1U_Y5V

0402C

Modify RB.01

12

RTN

13

R303(Rdrp2)

15

VCCSENSE/VSSSENSE: 100 ohm Pull up/Pull down

resister close to CPU Socket, Max length 2"

Close to CPU

C288 270P_X7R

0402C

C286 0.01U_X7R

0402C

A

R247

C297 1000P_X7R

0402C

R319

10K_1%

0402R

(Rocset)

IMVP6_VSUM

5.36K_1%

0402R

DFB

CCM MODE Fix to 307.55KHz

ISL6260CRZ

LFCSP41

0402R

VW

2

1

C480

10U_X5R

1206C

Close to CPU Socket Point

FB

BOOT

FCCM UGTE

C488

10U_X5R

1206C

4

3

2

1

ISEN3

VDIFF

COMP

C194

1U_Y5V

0603C

JP2

4

3

2

1

PWM3

0_5%

0402R

R304(Rdrp1)

6.49K_1%

0402R

C298 1000P_X7R

0402C

0.22U_X7R

0603C

R574

1K_1%

0402R

R320

0_5%_OP

C269

25

NTC

VCC

U21

IRF7807ZPBF

SOIC8

(Rseries)

R321

22

C270

0.22U_X7R

0603C

R267

R248

0_5%

0402R

U22

IMVP6_PWM2

C276(Cn)

10

C300 0.022U_X7R

0603C

C299 220P_X7R

0402C

0402R

R290 2.7K_1%

0402R

(Rpar)

R289 4.7K_1%

0402R

11

0.22U_X7R

0603C

C277 0.1U_Y5V

0402C

187_1%

0402R

1.2K_1%

0402R

C268

26

0.22U_X7R

0603C

R322

ISEN2

0_5%_OP

C489

0.1U_Y5V

0603C

330U_2V_SPCAP_OP

SEC_7343

SOFT

PWM2

IMVP6

+ C487

330U_2V_SPCAP

SEC_7343

470K_5%_NTC 5

0402R

Close to Phase 1 Inductor

C294 0.01U_X7R

0402C

C301 2200P_X7R

0402C

VR_ON

+ C482

330U_2V_SPCAP

SEC_7343

RT1

35

VID0

VID1

VID2

VID3

VID4

VID5

VID6

23

R266

4.7K_1%

0402R

0402R

Soft-Start Time of 429.65us

Modify R1.05

C296 0.047U_X7R_OP

0402C

C295 0.015U_X7R

0402C

R313

150K_1%

0402R

27

BAT54W-F_OP

SOT323_ACN

U57

R318

10K_5%

C253

2.2U_Y5V

0603C

PGD_IN

VR_TT#

Modify RB.39

C599

0.01U_X7R_OP

0402C

IRF8113PBF_OP

SOIC8

U56

N

R286

4

3

2

1

4

3

2

1

18

VIN

VDD

PWM1

24

IRF8113PBF

SOIC8

U55

N

VCC3_SW

28

29

30

31

32

33

34

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

+ C481

VCC5_SW

D21

FCCM

IRF8113PBF

SOIC8

3

3

3

3

3

3

3

R195

0_5%_OP

0402R

6m Ohm

D4

D3

D2

D1

3 CPU_PROCHOT#

0_5% VR_TT#

0402R

R197

0_5%

0402R

VIN

ISEN1

R317

R194

0_5%_OP

0402R

Modify RB.46

4

3

2

1

20

41

19

GND

VSS

39

3V3

0402R

0402R

0402R

R196

0_5%

0402R

330U_2V_SPCAP_OP

SEC_7343

0_5%

10K_1%

10_1%

D54

SS34A_3A

SOD106

330U_2V_SPCAP

SEC_7343

R316

PSI#

DPRSLPVR

DPRSTP#

CLK_EN#

PGOOD

R265

R264

0.002_1%_OP

RL3264

330U_2V_SPCAP

SEC_7343

1

36

37

38

40

IMVP6_ISEN1

0402R

0402R

0402R

0402R

0402R

0402R

U52

0_5%

499_1%

0_5%

0_5%

0_5%

5.1K_1%

R315

R296

R299

R297

R314

R291

32,33 PM_VCCP_PWRGD

U32

IMVP6_VSUM

C254 0.1U_Y5V

0402C

IRF8113PBF_OP

SOIC8

U51

N

Modify RB.46

C284

0.1U_Y5V

0402C

R298

10K_5%

0402R

3 PM_PSI#

6,13 PM_DPRSLPVR

3,13 PM_DPRSTP#

16 PM_CLK_EN#

13,33 PM_VGATE

IRF8113PBF

SOIC8

U50

N

ISL6208CBZ

SOIC8

VCC3_SW_IMVP6

10_1%

0402R

VCC_CORE

R563

FMJ-10402-R36_24A

CHOKE_10X11_5MM

5

6

7

8

D4

D3

D2

D1

LGTE

G

S3

S2

S1

PHSE

GND

2Phase OCP 47.6A

JMP

JP_10A

4

3

2

1

PWM

YONAH (MAX36A)

MEROM (MAX44A)

L7

5

6

7

8

C472

10U_X5R

1206C

DCR=1.1m Ohm

D4

D3

D2

D1

C475

10U_X5R

1206C

JP1

G

S3

S2

S1

FCCM UGTE

C476

0.1U_Y5V

0603C

U19

IRF7807ZPBF

SOIC8

20K_1%

0402R

IRF8113PBF

SOIC8

R300

VCC3_SW

R146

C274

1U_Y5V

0603C

VCC3_SW

G

S3

S2

S1

VCC5_SW

BOOT

5

6

7

8

IMVP6_PWM1

VCC5_SW_IMVP6

10_1%

0402R

VCC

D4

D3

D2

D1

0402R

0_5%

6

R573

U17

IRF7807ZPBF

SOIC8

C158

0.22U_X7R

0603C

U14

C275

0.1U_Y5V

0603C

R287

R147

0_5%

0402R

0.1U_Y5V

0402C

VIN_IMVP6

10_1%

0402R

BAT54W-F_OP

SOT323_ACN

G

S3

S2

S1

C145

VIN

R288

5

6

7

8

D14

C144

2.2U_Y5V

0603C

C285

0.01U_X7R

0402C

C287 0.01U_X7R

0402C

A

TP11

VSSSENSE_IMVP6

R225

0_5%

0402R

VCCSENSE_IMVP6

R224

0_5%

0402R

Project Name

TP12

R301

27.4_1%_OP

0402R

H12YV1

R302

27.4_1%_OP

0402R

Pag Title

CPU POWER

Document

Number

Close to IMVP6 within 100mils(resistor & test point)

5

Rev

A

Sheet 5

of 38

82+A32000+00A

Date: Friday, November 24, 2006

DMI: 100MHz reference clock (shared with PCI Express Graphics Attach)

16 CLK_MCH_BCLK

16 CLK_MCH_BCLK#

BCLK

BCLK#

HXSWING

HXSCOMP

HXRCOMP

HYSWING

HYSCOMP

HYRCOMP

HVREF

E4

E2

E1

W1

U1

Y1

J13

K13

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

AGTL+_A#3

AGTL+_A#4

AGTL+_A#5

AGTL+_A#6

AGTL+_A#7

AGTL+_A#8

AGTL+_A#9

AGTL+_A#10

AGTL+_A#11

AGTL+_A#12

AGTL+_A#13

AGTL+_A#14

AGTL+_A#15

AGTL+_A#16

AGTL+_A#17

AGTL+_A#18

AGTL+_A#19

AGTL+_A#20

AGTL+_A#21

AGTL+_A#22

AGTL+_A#23

AGTL+_A#24

AGTL+_A#25

AGTL+_A#26

AGTL+_A#27

AGTL+_A#28

AGTL+_A#29

AGTL+_A#30

AGTL+_A#31

HADSTB0#

HADSTB1#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

B9

C13

K4

T7

Y5

AC4

K3

T6

AA5

AC5

AGTL+_ADSTB#0

AGTL+_ADSTB#1

AGTL+_DSTBN#0

AGTL+_DSTBN#1

AGTL+_DSTBN#2

AGTL+_DSTBN#3

AGTL+_DSTBP#0

AGTL+_DSTBP#1

AGTL+_DSTBP#2

AGTL+_DSTBP#3

D8

G8

B8

F8

A8

AGTL+_REQ#0

AGTL+_REQ#1

AGTL+_REQ#2

AGTL+_REQ#3

AGTL+_REQ#4

J7

W8

U3

AB10

AGTL+_DINV#0

AGTL+_DINV#1

AGTL+_DINV#2

AGTL+_DINV#3

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

DINV0#

DINV1#

DINV2#

DINV3#

5,13 PM_DPRSLPVR

0_5%

0402R

PM_EXTTS1#

R559

0_5%

0402R

A16

C18

A19

VCC1_5_SW

AGTL+_ADSTB#[0:1] 3

AGTL+_DSTBN#[0:3] 3

AGTL+_DSTBP#[0:3] 3

AGTL+_REQ#[0:4] 3

AGTL+_DINV#[0:3]

ADS#

BNR#

BPRI#

BREQ0#

CPURST#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HTRDY#

HLOCK#

E8

C6

F6

C7

B7

A7

C3

H8

D3

D4

E7

B3

AGTL+_ADS# 3

AGTL+_BNR# 3

AGTL+_BPRI# 3

AGTL+_BR0# 3

AGTL+_CPURST# 3

AGTL+_DBSY# 3

AGTL+_DEFER# 3

AGTL+_DRDY# 3

AGTL+_HIT# 3

AGTL+_HITM# 3

AGTL+_TRDY# 3

AGTL+_LOCK# 3

DPWR#

CPUSLP#

J9

E3

AGTL+_DPWR# 3

CPU_CPUSLP# 3

RS0#

RS1#

RS2#

B4

E6

D6

HXSWING

HXSCOMP

HXRCOMP

HYSWING

HYSCOMP

HYRCOMP

HVREF0

HVREF1

R219

AGTL+_RS#[0:2] 3

Calistoga

FBGA_1466_42_34_ALONE

VCC1_5_SW

VCC_P

VCC_P

VCC_P

VCC_P

B16

B18

B19

TV_IRTN_A

TV_IRTN_B

TV_IRTN_C

K30

J29

TV_DCONSEL0

TV_DCONSEL1

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

AGTL+_RS#0

AGTL+_RS#1

AGTL+_RS#2

R73

24.9_1%

0402R

VCC_P

TV_DAC_A

TV_DAC_B

TV_DAC_C

D40

D38

DMI

AG2

AG1

CLK_MCH_BCLK

CLK_MCH_BCLK#

HOST

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

LVDS

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

PM_BM_BUSY#

RSTIN#

PWROK

THRMTRIP#

PM_EXT_TS0#

PM_EXT_TS1#

ICH_SYNC#

IGDS

CRT

F1

J1

H1

J6

H3

K2

G1

G2

K9

K1

K7

J8

H4

J3

K11

G4

T10

W11

T3

U7

U9

U11

T11

W9

T1

T8

T4

W7

U5

T9

W6

T5

AB7

AA9

W4

W3

Y3

Y7

W5

Y10

AB8

W2

AA4

AA7

AA2

AA6

AA10

Y8

AA1

AB4

AC9

AB11

AC11

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD10

AD4

AC8

100_1% 0402R

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

R202

100_1%

0402R

C213

0.1U_Y5V

0402C

HYSWING

R216

100_1%

0402R

C233

0.1U_Y5V

0402C

HVREF

HXSCOMP

HYSCOMP

HXRCOMP

HYRCOMP

R220

24.9_1%

0402R

R215

24.9_1%

0402R

Trace width/Space:

10mil/20mil

R179

200_1%

0402R

C190

0.1U_Y5V

0402C

R154

150_1%

0402R

DMI_RXP[0:3] 12

LVDS1_CLK- 11

LVDS1_CLK+ 11

LA_DATAN0

LA_DATAN1

LA_DATAN2

C37

B35

A37

LVDS1_Y0- 11

LVDS1_Y1- 11

LVDS1_Y2- 11

LA_DATAP0

LA_DATAP1

LA_DATAP2

B37

B34

A36

LVDS1_Y0+ 11

LVDS1_Y1+ 11

LVDS1_Y2+ 11

LB_CLKN

LB_CLKP

E27

E26

LB_DATAN0

LB_DATAN1

LB_DATAN2

G30

D30

F29

LB_DATAP0

LB_DATAP1

LB_DATAP2

F30

D29

F28

LBKLT_CTL

LBKLT_EN

LVDDEN

D32

J30

F32

LCTLA_CLK

LCTLB_DATA

LDDCCLK

LDDCDATA

H30

H29

G26

G25

RED

GREEN

BLUE

RED#

GREEN#

BLUE#

A21

C22

E23

B21

B22

D23

DDCADATA

DDCACLK

HSYNC

VSYNC

C25

C26

G23

H23

LCDBLT_CTL

LCD_ENBLT

LCD_ENVCC

LCDBLT_CTL 11

LCD_ENBLT 11

LCD_ENVCC 11

LCTLA_CLK 15

LCTLB_DATA 15

LDDCCLK 11,15

LDDCDATA 11,15

DAC_RED

DAC_GREEN

DAC_BLUE

DAC_RED 11

DAC_GREEN 11

DAC_BLUE 11

IGD_HSYNC R166

IGD_VSYNC R167

AF33

AG33

CLK_PEG_MCH#

CLK_PEG_MCH

DREF_CLKN

DREF_CLKP

A27

A26

CLK_DREF_CLK#

CLK_DREF_CLK

DREF_SSCLKN

DREF_SSCLKP

C40

D41

CLK_DREF_SSCLK#

CLK_DREF_SSCLK

CLK_REQ#

H32

GMCH_CLKREQ#

INT-L

SDVOCTRL_DATA

SDVOCTRL_CLK

H27

H28

CRT_IREF

TV_IREF

J22

J20

LVREFH

LVREFL

LIBG

LVBG

C33

C32

B38

C35

DDC1_DATA 11

DDC1_CLK 11

DAC_HSYNC 11

DAC_VSYNC 11

39_1% 0402R

39_1% 0402R

CLK_PEG_MCH# 16

CLK_PEG_MCH 16

CLK_DREF_CLK# 16

CLK_DREF_CLK 16

CLK_DREF_SSCLK# 16

CLK_DREF_SSCLK 16

CRT_IREF

VCC1_5_SW

R152

255_1%

0402R

LIBG

Net CRT_IREF:

Minimum spacing of

20mils

Zdiff=100 ohm +-15%

DAC_RED/DAC_GREEN/DAC_BLUE

are ground referenced

R145

150_1%

0402R

R155

150_1%

0402R

Capacitor needs to be within 100mils of

GMCH pin J13, K13

R126

100K_1%_OP

0402R

LCDBLT_CTL

R123

100K_1%

0402R

LCD_ENBLT

R124

100K_1%

0402R

LCD_ENVCC

Close to GMCH pin D32, J30, F32

Project Name

H12YV1

Pag Title

Calistoga(HOST/IGDS/DMI)

Document

Number

Close to GMCH DAC_RED/DAC_GREEN/DAC_BLUE

max length 0.5"

4

Rev

A

Sheet 6

of 38

82+A32000+00A

Date: Friday, November 24, 2006

5

TP1

R111

1.5K_1%

0402R

EXP_COMPI

EXP_ICOMPO

Close to NB

R180

100_1%

0402R

DMI_RXN[0:3] 12

GMCH Pin ball G23, H23 to 39Ohm trace length <0.5"

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

DAC_BLUE

R218

54.9_1%

0402R

DAC_GREEN

HXSWING

R221

54.9_1%

0402R

DAC_RED

R217

221_1%

0402R

DMI_TXP[0:3] 12

A33

A32

Calistoga

FBGA_1466_42_34_ALONE

R203

221_1%

0402R

DMI_TXN[0:3] 12

LA_CLKN

LA_CLKP

GCLKN

GCLKP

CLK

AGTL+_D#0

AGTL+_D#1

AGTL+_D#2

AGTL+_D#3

AGTL+_D#4

AGTL+_D#5

AGTL+_D#6

AGTL+_D#7

AGTL+_D#8

AGTL+_D#9

AGTL+_D#10

AGTL+_D#11

AGTL+_D#12

AGTL+_D#13

AGTL+_D#14

AGTL+_D#15

AGTL+_D#16

AGTL+_D#17

AGTL+_D#18

AGTL+_D#19

AGTL+_D#20

AGTL+_D#21

AGTL+_D#22

AGTL+_D#23

AGTL+_D#24

AGTL+_D#25

AGTL+_D#26

AGTL+_D#27

AGTL+_D#28

AGTL+_D#29

AGTL+_D#30

AGTL+_D#31

AGTL+_D#32

AGTL+_D#33

AGTL+_D#34

AGTL+_D#35

AGTL+_D#36

AGTL+_D#37

AGTL+_D#38

AGTL+_D#39

AGTL+_D#40

AGTL+_D#41

AGTL+_D#42

AGTL+_D#43

AGTL+_D#44

AGTL+_D#45

AGTL+_D#46

AGTL+_D#47

AGTL+_D#48

AGTL+_D#49

AGTL+_D#50

AGTL+_D#51

AGTL+_D#52

AGTL+_D#53

AGTL+_D#54

AGTL+_D#55

AGTL+_D#56

AGTL+_D#57

AGTL+_D#58

AGTL+_D#59

AGTL+_D#60

AGTL+_D#61

AGTL+_D#62

AGTL+_D#63

R92

TV

AGTL+_A#[3:31] 3

G28

AH34

AH33

G6

F25

H26

K28

PCI-EXPRESS GRAPHICS

3 AGTL+_D#[0:63]

13 PM_BMBUSY#

13,24,26,27 PM_PLTRST#

13,29,33 PM_PWROK

3,13 PM_THERMTRIP#

10,15 PM_EXTTS0#

15 PM_EXTTS1#

13 MCH_ICH_SYNC#

PM

U53B

U53A

DDRA_MA[0:13]

U53C

10 DDRA_MD[0:63]

10 DDRA_SDM[0:7]

10 DDRA_DQS[0:7]

10 DDRA_DQS#[0:7]

DDRA_MD0

DDRA_MD1

DDRA_MD2

DDRA_MD3

DDRA_MD4

DDRA_MD5

DDRA_MD6

DDRA_MD7

DDRA_MD8

DDRA_MD9

DDRA_MD10

DDRA_MD11

DDRA_MD12

DDRA_MD13

DDRA_MD14

DDRA_MD15

DDRA_MD16

DDRA_MD17

DDRA_MD18

DDRA_MD19

DDRA_MD20

DDRA_MD21

DDRA_MD22

DDRA_MD23

DDRA_MD24

DDRA_MD25

DDRA_MD26

DDRA_MD27

DDRA_MD28

DDRA_MD29

DDRA_MD30

DDRA_MD31

DDRA_MD32

DDRA_MD33

DDRA_MD34

DDRA_MD35

DDRA_MD36

DDRA_MD37

DDRA_MD38

DDRA_MD39

DDRA_MD40

DDRA_MD41

DDRA_MD42

DDRA_MD43

DDRA_MD44

DDRA_MD45

DDRA_MD46

DDRA_MD47

DDRA_MD48

DDRA_MD49

DDRA_MD50

DDRA_MD51

DDRA_MD52

DDRA_MD53

DDRA_MD54

DDRA_MD55

DDRA_MD56

DDRA_MD57

DDRA_MD58

DDRA_MD59

DDRA_MD60

DDRA_MD61

DDRA_MD62

DDRA_MD63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

DDRA_SDM0

DDRA_SDM1

DDRA_SDM2

DDRA_SDM3

DDRA_SDM4

DDRA_SDM5

DDRA_SDM6

DDRA_SDM7

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

SADM0

SADM1

SADM2

SADM3

SADM4

SADM5

SADM6

SADM7

DDRA_DQS0

DDRA_DQS1

DDRA_DQS2

DDRA_DQS3

DDRA_DQS4

DDRA_DQS5

DDRA_DQS6

DDRA_DQS7

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

DDRA_DQS#0

DDRA_DQS#1

DDRA_DQS#2

DDRA_DQS#3

DDRA_DQS#4

DDRA_DQS#5

DDRA_DQS#6

DDRA_DQS#7

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

SA_RCVENIN#

SA_RCVENOUT#

AK23

AK24

SA_WE#

SA_RAS#

SA_CAS#

AY14

AW14

AY13

DDRA_SWE#

DDRA_SRAS#

DDRA_SCAS#

SA_BS0

SA_BS1

SA_BS2

AU12

AV14

BA20

DDRA_SBS0

DDRA_SBS1

DDRA_SBS2

SCS0#

SCS1#

SCS2#

SCS3#

AW13

AW12

AY21

AW21

DDR_CS#0

DDR_CS#1

SCK0

SCK#0

SCK1

SCK#1

SCK2

SCK#2

SCK3

SCK#3

AY35

AW35

AR1

AT1

AW7

AY7

AW40

AY40

SCKE0

SCKE1

SCKE2

SCKE3

AU20

AT20

BA29

AY29

DDR_CKE0

DDR_CKE1

SODT0

SODT1

SODT2

SODT3

BA13

BA12

AY20

AU21

DDR_SODT0

DDR_SODT1

SMOCDCOMP0

SMOCDCOMP1

AL20

AF10

R151

R178

40.2_1%_OP 0402R

40.2_1%_OP 0402R

AV9

AT9

R192

80.6_1%

DDR2-A

SMRCOMPN

SMRCOMPP

10

DDRA_SWE# 10

DDRA_SRAS# 10

DDRA_SCAS# 10

DDRA_SBS0 10

DDRA_SBS1 10

DDRA_SBS2 10

DDR_CS#0 10

DDR_CS#1 10

DDR_CLK0

DDR_CLK#0

DDR_CLK1

DDR_CLK#1

10

10

10

10

DDR_CKE0 10

DDR_CKE1 10

DDR_SODT0 10

DDR_SODT1 10

0402R

VCC1_8

32mA

R193

80.6_1%

0402R

SMVREF0

SMVREF1

AK1

AK41

SMVREF

U53F

DDRA_MA0

DDRA_MA1

DDRA_MA2

DDRA_MA3

DDRA_MA4

DDRA_MA5

DDRA_MA6

DDRA_MA7

DDRA_MA8

DDRA_MA9

DDRA_MA10

DDRA_MA11

DDRA_MA12

DDRA_MA13

SAMA0

SAMA1

SAMA2

SAMA3

SAMA4

SAMA5

SAMA6

SAMA7

SAMA8

SAMA9

SAMA10

SAMA11

SAMA12

SAMA13

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AJ9

AN10

AK13

AH11

AK10

AJ8

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ5

AJ3

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

DDR2-B

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

AM39

AT39

AU35

AR29

AR16

AR10

AR7

AN5

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

AM40

AU39

AT35

AP29

AP16

AT10

AT7

AP5

SBDM0

SBDM1

SBDM2

SBDM3

SBDM4

SBDM5

SBDM6

SBDM7

AK36

AR38

AT36

BA31

AL17

AH8

BA5

AN4

SB_RCVENIN#

SB_RCVENOUT#

AK16

AK18

SB_WE#

SB_CAS#

SB_RAS#

AR27

AR24

AU23

SB_BS0

SB_BS1

SB_BS2

AT24

AV23

AY28

Calistoga

FBGA_1466_42_34_ALONE

10uA

* DDR2 400MHz/533MHz/667MHz memory device

* 256Mb/512Mb/1Gb using *8/*16 device

* Minimum memory support 128MB

* Calistoga GMCH does not support ECC & third SCK pair non-ECC memory module.

VCC1_8

R90

10K_1%

0402R

SMVREF

Calistoga

FBGA_1466_42_34_ALONE

C212

0.1U_Y5V

0402C

C96

0.1U_Y5V

0402C

R91

10K_1%

0402R

Project Name

H12YV1

Pag Title

Close to MGCH pin AK1, AK41

Calistoga(DDR2 I/F)

Document

Number

Rev

A

Sheet 7

of 38

82+A32000+00A

Date: Friday, November 24, 2006

1

B7

DHBS2012_G301

0805B

C203 0.47U_Y5V

0603C

VTTLF_CAP3

C234 0.22U_X7R

0603C

C232 0.47U_Y5V

0603C

VTTLF_CAP2

VTTLF_CAP1

VCC3_SW

40mA

C157

4.7U_Y5V

0805C

C156

0.1U_Y5V

0402C

C155

39P_NPO

0402C

20mA

VCC1_5_SW

60mA

C143

10U_Y5V

0805C

C140

0.1U_Y5V

0402C

C141

39P_NPO

0402C

10mA

VCCHV0

VCCHV1

VCCHV2

A28

B28

C28

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

C30

B30

A30

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

A38

B39

VCCA_LVDS

VSSA_LVDS

C129

39P_NPO

0402C

Close to PIN C30

< 200mil

VCC2_5_SW

R113

0_5%

0603R

VCCA_LVDS

C111

0.1U_Y5V

0402C

C110

0.01U_X7R

0402C

HIGH VOLTAGE

C230

0.1U_Y5V

0402C

VCC1_5_SW

C242

10U_Y5V_OP

0805C

B5

AMB2012R101NT

0805B

VCCA_3GPLL

C124

0.1U_Y5V

0402C

VCC1_5_SW

C125

10U_Y5V

0805C

Close to PIN Ball

< 200mil

VCCD_HMPLL1

VCCD_HMPLL2

AH1

AH2

150mA

B26

C39

AJ41

AB41

Y41

V41

R41

N41

L41

VCCA_TVDACA0

VCCA_TVDACA1

E19

F19

VCCA_TVDACB0

VCCA_TVDACB1

C20

D20

VCCA_TVDACC0

VCCA_TVDACC1

E20

F20

VCCA_TVBG

VSSA_TVBG

H20

G20

VCC_SYNC

VCCA_CRTDAC0

VCCA_CRTDAC1

H22

E21

F21

VSSA_CRTDAC

G21

3.5A

1.5A

VCCD_LVDS(VCC1_5_SW)

20mA

VCCD_TVDAC(VCC1_5_SW)

24mA

VCCA_HPLL(VCC1_5_SW)

45mA

VCCA_DPLLA,B(VCC1_5_SW)

100mA

VCCA_MPLL(VCC1_5_SW)

45mA

VCCD_HMPLL(VCC1_5_SW)

150mA

VCCAUX(VCC1_5_SW)

1.9A

VCCSM & DDR2 Single

Channel 667MTs(VCC1_8)

1.7A

VCCA_3GBG(VCC2_5_SW)

2mA

VCCA_LVDS(VCC2_5_SW)

10mA

VCCTX_LVDS(VCC2_5_SW)

60mA

VCCCRT(VCC2_5_SW)

70mA

VCCHV(VCC3_SW)

40mA

4.3A

C98

0.1U_Y5V

0402C

C97

39P_NPO

0402C

VCC1_5_SW

C73

10U_Y5V

0805C

VCCA_3GBG

R72

C100

0.1U_Y5V

0402C

VCC1_5_SW

C72

10U_Y5V_OP

0805C

0_5%

0603R

Close to PIN G41

< 250mil

VCC2_5_SW

VCC1_5_SW

70mA

VCC3G(VCC1_5_SW)

B3

AMB2012R101NT

0805B

C99

0.1U_Y5V

0402C

D21

H19

VCC1_5_SW

C74

10U_Y5V_OP

0805C

VCC3G

1.5A (VCC3G+VCCA_3GPLL)

VCCD_TVDAC

VCCDQ_TVDAC

VCC1_05(VCC_P)

C101

0.1U_Y5V

0402C

50mA

50mA

2mA

Total

B4

AMB2012R101NT

0805B

VCCA_DPLLB

24mA

Current

C142

10U_Y5V_OP

0805C

VCC1_5_SW

AC33

G41

H41

VCCA_3GBG

VSSA_3GBG

C154

0.1U_Y5V

0402C

VCC1_5_SW

VCCA_CRTDAC

C172

0.1U_Y5V

0402C

R153

C171

0.1U_Y5V

0402C

Close to PIN H22

C178

10U_Y5V

0805C

0_5%

0603R

VCC2_5_SW

Within 3" of GMCH

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF68

VCC_NCTF69

VCC_NCTF70

VCC_NCTF71

VCC_NCTF72

AG27

AF27

AG26

AF26

AG25

AF25

AG24

AF24

AG23

AF23

AG22

AF22

AG21

AF21

AG20

AF20

AG19

AF19

R19

AG18

AF18

R18

AG17

AF17

AE17

AD17

AB17

AA17

W17

V17

VCCAUX_NCTF0

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

NC

AD27

AC27

AB27

AA27

Y27

W27

V27

U27

T27

R27

AD26

AC26

AB26

AA26

Y26

W26

V26

U26

T26

R26

AD25

AC25

AB25

AA25

Y25

W25

V25

U25

T25

R25

AD24

AC24

AB24

AA24

Y24

W24

V24

U24

T24

R24

AD23

V23

U23

T23

R23

AD22

V22

U22

T22

R22

AD21

V21

U21

T21

R21

AD20

V20

U20

T20

R20

AD19

V19

U19

T19

AD18

AC18

AB18

AA18

Y18

W18

V18

U18

T18

INT-H

B12

AMB2012R101NT

0805B

VCC_P

CFG

VCC1_5_SW

C243

10U_Y5V_OP

0805C

VCCA_MPLL

45mA

45mA

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

0.8A

VCCTVDAC(VCC3_SW)

U53G

VCC1_5_SW

C137

10U_Y5V_OP

0805C

VCCA_HPLL

C231

0.1U_Y5V

0402C

AF1

AF2

VCCA_3GPLL

VTT(VCC_P)

Close to PIN A38 < 200mil

C123

10U_Y5V

0805C

B13

AMB2012R101NT

0805B

VCCA_HPLL

VCCA_MPLL

Calistoga Power Consumption

C128

0.1U_Y5V

0402C

C166

10U_Y5V

0805C

B6

AMB2012R101NT

0805B

VCCA_DPLLA

VCCA_DPLLB

Power Plane

C130

4.7U_Y5V

0805C

C186

39P_NPO

0402C

VCCA_DPLLA

Calistoga

FBGA_1466_42_34_ALONE

Close to PIN A28,B28,C28

< 200mil

VCC2_5_SW

C188

0.1U_Y5V

0402C

INT-L

I/O

A23

B23

B25

VCCAUX_GMCH

1.9A

NCTF

RSVD

AK31

AF31

AE31

AC31

AL30

AK30

AJ30

AH30

AG30

AF30

AE30

AD30

AC30

AG29

AF29

AE29

AD29

AC29

AG28

AF28

AE28

AH22

AJ21

AH21

AJ20

AH20

AH19

P19

P16

AH15

P15

AH14

AG14

AF14

AE14

Y14

AF13

AE13

AF12

AE12

AD12

POWER

PLL

VCCAUX0

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCAUX5

VCCAUX6

VCCAUX7

VCCAUX8

VCCAUX9

VCCAUX10

VCCAUX11

VCCAUX12

VCCAUX13

VCCAUX14

VCCAUX15

VCCAUX16

VCCAUX17

VCCAUX18

VCCAUX19

VCCAUX20

VCCAUX21

VCCAUX22

VCCAUX23

VCCAUX24

VCCAUX25

VCCAUX26

VCCAUX27

VCCAUX28

VCCAUX29

VCCAUX30

VCCAUX31

VCCAUX32

VCCAUX33

VCCAUX34

VCCAUX35

VCCAUX36

VCCAUX37

VCCAUX38

VCCAUX39

VCCAUX40

PCI-EXPRESS/

DMI

C202

TV DAC

C189

39P_NPO

0402C

0.22U_X7R

0603C

10U_Y5V_OP

0805C

C187

10U_Y5V

0805C

VTT0

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT35

VTT36

VTT37

VTT38

VTT39

VTT40

VTT41

VTT42

VTT43

VTT44

VTT45

VTT46

VTT47

VTT48

VTT49

VTT50

VTT51

VTT52

VTT53

VTT54

VTT55

VTT56

VTT57

VTT58

VTT59

VTT60

VTT61

VTT62

VTT63

VTT64

VTT65

VTT66

VTT67

VTT68

VTT69

VTT70

VTT71

VTT72

VTT73

VTT74

VTT75

VTT76

CRT DAC

C201

AC14

AB14

W14

V14

T14

R14

P14

N14

M14

L14

AD13

AC13

AB13

AA13

Y13

W13

V13

U13

T13

R13

N13

M13

L13

AB12

AA12

Y12

W12

V12

U12

T12

R12

P12

N12

M12

L12

R11

P11

N11

M11

R10

P10

N10

M10

P9

N9

M9

R8

P8

N8

M8

P7

N7

M7

R6

P6

M6

A6

R5

P5

N5

M5

P4

N4

M4

R3

P3

N3

M3

R2

P2

M2

D2

AB1

R1

P1

N1

M1

LVDS

0.8A

VTT

VCC_P

VSS_NCTF

U53D

VCC_NCTF

VCCAUX_NCTF

(VCCSM_NCTF)

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

D1

C41

C1

BA41

BA40

BA39

BA3

BA2

BA1

B41

B2

AY41

AY1

AW41

AW1

A40

A4

A39

A3

011 = 667 MT/s(667MHz)FSB

CFG[2:0]

Others = Reserved

K16 MCH_BSEL0 R199

K18 MCH_BSEL1 R201

J18 MCH_BSEL2 R200

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

J25

K27

J26

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

T32

R32

F3

F7

AG11

AF11

H7

J19

A41

A35

A34

D28

D27

VSS_NCTF0

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

AE27

AE26

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AC17

Y17

U17

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VCCAUX_NCTF39

VCCAUX_NCTF40

VCCAUX_NCTF41

VCCAUX_NCTF42

VCCAUX_NCTF43

VCCAUX_NCTF44

VCCAUX_NCTF45

VCCAUX_NCTF46

VCCAUX_NCTF47

VCCAUX_NCTF48

VCCAUX_NCTF49

VCCAUX_NCTF50

VCCAUX_NCTF51

VCCAUX_NCTF52

VCCAUX_NCTF53

VCCAUX_NCTF54

VCCAUX_NCTF55

VCCAUX_NCTF56

VCCAUX_NCTF57

T17

R17

AG16

AF16

AE16

AD16

AC16

AB16

AA16

Y16

W16

V16

U16

T16

R16

AG15

AF15

AE15

AD15

AC15

AB15

AA15

Y15

W15

V15

U15

T15

R15

001 = 533 MT/s(533MHz)FSB

1K_1%

1K_1%

1K_1%

0402R

0402R

0402R

BSEL0 3,16

BSEL1 3,16

BSEL2 3,16

CFG5 15

CFG7 15

CFG9 15

CFG11 15

CFG12 15

CFG13 15

CFG16 15

CFG18 15

CFG19 15

CFG20 15

Calistoga

FBGA_1466_42_34_ALONE

3.784A

1.7A

Project Name

142mA

H12YV1

Pag Title

Calistoga(PWR/NCTF)

Document

Number

40mA

120mA(N/A)

4

Rev

A

Sheet 8

of 38

82+A32000+00A

Date: Friday, November 24, 2006

CTF

CTF

L35

J35

H35

G35

F35

D35

AN34

AK34

AG34

AF34

AE34

AC34

C34

AW33

AV33

AR33

AE33

AB33

Y33

V33

T33

R33

M33

H33

G33

F33

D33

B33

AH32

AG32

AF32

AE32

AC32

AB32

G32

B32

AY31

AV31

AN31

AJ31

AG31

AB31

Y31

AB30

E30

AT29

AN29

AB29

T29

N29

K29

G29

E29

C29

B29

A29

BA28

AW28

AU28

AP28

AM28

AD28

AC28

W28

J28

E28

AP27

AM27

AK27

J27

G27

F27

C27

B27

AN26

M26

K26

F26

D26

AK25

P25

K25

H25

E25

D25

A25

BA24

AU24

AL24

AW23

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

CTF

CTF

Layout Notice:

VCC_P

NCTF

13X13

CTF

5X5

CTF

MEMORY

CORE

CTF

AU41

VCCSM_LF4

AT41

VCCSM_LF3

AM41

AU40

C71

C70

BA34

0.47U_Y5V

0.47U_Y5V

AY34

0603C

0603C

AW34

AV34

AU34

AT34

AR34

D

BA30

AY30

AW30

AV30

AU30

AT30

AR30

AP30

AN30

AM30

AM29

AL29

AK29

AJ29

AH29

AJ28

AH28

AJ27

AH27

BA26

AY26

AW26

AV26

AU26

AT26

AR26

AJ26

AH26

AJ25

AH25

AJ24

AH24

BA23

AJ23

C152

BA22

0.47U_Y5V

AY22

0603C

AW22

C

AV22

AU22

Close to PIN BA23

AT22

AR22

AP22

AK22

AJ22

AK21

AK20

BA19

AY19

AW19

AV19

AU19

AT19

AR19

AP19

AK19

AJ19

AJ18

DDR2(1.8V, 667MTS)

AJ17

1 Channel 1.7A

AH17

VCC1_8

2 Channel 3.2A (N/A)

AJ16

AH16

BA15

AY15

C177

C136

C165

AW15

10U_Y5V

10U_Y5V

AV15

0805C

0805C

AU15

AT15

AR15

AJ15

AJ14

Close to PIN BA15

AJ13

AH13

AK12

AJ12

B

C153

C200

AH12

39P_NPO

10U_Y5V

AG12

0402C

0805C

AK11

BA8

AY8

AW8

AV8

AT8

AR8

AP8

BA6

AY6

AW6

AV6

AT6

AR6

AP6

AN6

AL6

AK6

AJ6

AV1 VCCSM_LF2

AJ1 VCCSM_LF1

C229

0.47U_Y5V

0603C

C228

0.47U_Y5V

0603C

Calistoga

FBGA_1466_42_34_ALONE

External GFX 1.5A (N/A)

Integrated GFX 3.5A

Modify R0.08

C467

Metal defined thermal connection 6mil wide

spokes connect to top layer plane shapes

220U_2V_SPCAP

C_D

CTF

Calistoga

FBGA_1466_42_34_ALONE

CTF

CTF

VCC

CTF

CTF

E12

H12

K12

AC12

AY12

B13

D13

F13

P13

AG13

AL13

AM13

AN13

AR13

AV13

E14

H14

K14

U14

AA14

AD14

AK14

AT14

BA14

A15

B15

L15

M15

N15

AK15

AM15

AN15

C16

F16

J16

AL16

AN16

AV16

AK17

AM17

AP17

AR17

AY17

A18

D18

H18

P18

AH18

C19

G19

K19

W19

AC19

AN19

A20

B20

K20

AA20

AM20

AR20

AW20

C21

H21

J21

K21

P21

Y21

AB21

AL21

AN21

AR21

AV21

BA21

A22

D22

E22

F22

G22

K22

AA22

C23

F23

J23

K23

W23

AC23

AH23

AM23

AN23

AT23

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

VCCSM65

VCCSM66

VCCSM67

VCCSM68

VCCSM69

VCCSM70

VCCSM71

VCCSM72

VCCSM73

VCCSM74

VCCSM75

VCCSM76

VCCSM77

VCCSM78

VCCSM79

VCCSM80

VCCSM81

VCCSM82

VCCSM83

VCCSM84

VCCSM85

VCCSM86

VCCSM87

VCCSM88

VCCSM89

VCCSM90

VCCSM91

VCCSM92

VCCSM93

VCCSM94

VCCSM95

VCCSM96

VCCSM97

VCCSM98

VCCSM99

VCCSM100

VCCSM101

VCCSM102

VCCSM103

VCCSM104

VCCSM105

VCCSM106

VCCSM107

0.47U_Y5V

0603C

VSS

VSS269

VSS268

VSS267

VSS266

VSS265

VSS264

VSS263

VSS262

VSS261

VSS260

VSS259

VSS258

VSS257

VSS256

VSS255

VSS254

VSS253

VSS252

VSS251

VSS250

VSS249

VSS248

VSS247

VSS246

VSS245

VSS244

VSS243

VSS242

VSS241

VSS240

VSS239

VSS238

VSS237

VSS236

VSS235

VSS234