Академический Документы

Профессиональный Документы

Культура Документы

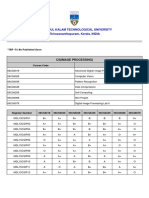

VLSI Design Automation Syllabus Modified

Загружено:

akhАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

VLSI Design Automation Syllabus Modified

Загружено:

akhАвторское право:

Доступные форматы

Course Code

Course Name

L-T-P-C

Year of Introduction

06EC6036

VLSI DESIGN AUTOMATION

3-0-0-3

2015

Course Objectives

1. To learn basic concepts and flow in hardware design

2. To learn fundamental algorithms in physical design

3. To have a basic exposure to physical design automation, optimization techniques and data

structures inside modern VLSI tools

Syllabus

Graph Algorithms,

Compaction,

Partitioning,

Placement,

Floorplanning,

Pin Assignment,

Global Routing,

Detailed Routing

Expected outcome

At the end of the course, student will know the different stages of design flow; the basic data

structures and algorithms used in each stage; and will be able to understand data structures and

algorithms used in recent CAD tools; choose suitable data structures and propose new algorithms

for CAD applications and develop new CAD tools

Text Books

1. Gerez,Sabih H., Algorithms for VLSI Design Automation, John Wiley & Sons, 2006.

2. Sherwani, Naveed A., Algorithms for VLSI Physical Design Automation,Kluwer

Academic Publishers, 1999.

References

1. Drechsler, Rolf, Evolutionary Algorithms for VLSI CAD Springer

Science & Business Media, 1998.

2. Trimberger, Stephen M., An Introduction to CAD for VLSI,

Springer Science & Business Media, 1987.

3. Sadiq M. Sait and H. Youssef, VLSI Physical Design Automation:

Theory and Practice, World Scientific, 1999.

4. Cormen, Thomas H., Charles E. Leiserson, and Ronald L. Rivest.

"Introduction to Algorithms." The MIT Press, 3rd edition, 2009.

Module

Content

Hour

II

II

VLSI Physical Design Automation:

VLSI Design Cycle,

Physical Design Cycle

Graph Search Algorithms:

Terminology,

Data structures for Representation of Graphs,

Breadth First Search,

Depth First Search,

Topological Sort,

Spanning Tree Algorithm Prims Algorithm

Shortest Path Algorithms:

Dijkstras Algorithm for single pair Shortest path,

Floyd-Warshall Algorithm for All pair Shortest path

Logic Synthesis:

Introduction to Combinational Logic Synthesis

Basic Issues and Terminology,

Practical Example.

High-level Synthesis:

Hardware Models for High-Level Synthesis,

Allocation, Assignment and Scheduling - ASAP Scheduling.

Compaction:

Problem Formulation,

Longest Path Algorithm for DAGs withoutcycles and with

cycles,

Liao-Wong Algorithm,

Bellman-Ford Algorithm.

Partitioning:

Kernighan-Lin Partitioning Algorithm,

Fiduccia-Mattheyses Algorithm.

Floorplanning:

Floorplan Representation,

Shape Functions,

Floorplan Sizing.

Placement:

Circuit Representation,

Wire-length Estimation,

Types of Placement Problem,

Placement Algorithms Constructive Placement, Iterative

Improvement.

Pin Assignment:

Problem Formulation,

General Pin Assignment,

Channel Pin Assignment.

12

10

IV

Global Routing:

Problem Formulation,

Classification of Global Routing Algorithms,

Maze Routing Algorithm Lees Algorithm,

Line-Probe algorithm,

Shortest Path Based Algorithm.

Local Routing:

Problem Formulation,

Types of Local Routing Problems,

Area Routing,

Channel Routing Channel Routing Models,

Vertical and Horizontal Constraint Graph,

Left-edge Algorithm,

Robust Channel Routing Algorithm.

END SEMESTER EXAM

10

Вам также может понравиться

- Blueprint 7 Student Book Teachers GuideДокумент128 страницBlueprint 7 Student Book Teachers GuideYo Rk87% (38)

- Installing OpenSceneGraphДокумент9 страницInstalling OpenSceneGraphfer89chopОценок пока нет

- 26th Academic Council ProceedingsДокумент2 страницы26th Academic Council Proceedingsnetgalaxy2010Оценок пока нет

- M.Tech CSE SyllabusДокумент15 страницM.Tech CSE SyllabusutpalrguОценок пока нет

- IV Sem BTech AIML230222083345Документ10 страницIV Sem BTech AIML230222083345rajtiwari7284Оценок пока нет

- CA 1804 Discrete Structures: Department of Computer Applications (MCA)Документ25 страницCA 1804 Discrete Structures: Department of Computer Applications (MCA)ramsethu12Оценок пока нет

- Fifth Semester: BTCS 501 Computer Networks - IIДокумент6 страницFifth Semester: BTCS 501 Computer Networks - IIPrincess deepikaОценок пока нет

- MCA 2YDC SyllabusДокумент25 страницMCA 2YDC SyllabusabdcОценок пока нет

- Cse2002 Data-structures-And-Algorithms LTP 2.0 2 Cse2002 Data-structures-And-Algorithms LTP 2.0 1 Cse2002-Data Structures and AlgorithmsДокумент3 страницыCse2002 Data-structures-And-Algorithms LTP 2.0 2 Cse2002 Data-structures-And-Algorithms LTP 2.0 1 Cse2002-Data Structures and Algorithmspankaj yadavОценок пока нет

- Code No. Course Title L T P C Theory: Semester VДокумент0 страницCode No. Course Title L T P C Theory: Semester VThyagu RajanОценок пока нет

- 05 MTCST PDFДокумент19 страниц05 MTCST PDFAkhtar RazaОценок пока нет

- Department of Computer Science and Engineering - PGДокумент31 страницаDepartment of Computer Science and Engineering - PGMegha BheemaraoОценок пока нет

- CSE4SEMSYLLABUSДокумент7 страницCSE4SEMSYLLABUSVikas ChaubeyОценок пока нет

- Data Structures and Algorithms CS201Документ88 страницData Structures and Algorithms CS201ApОценок пока нет

- Syllabus Sem 7Документ15 страницSyllabus Sem 7Shankar SinghОценок пока нет

- M.tech Cse FTДокумент33 страницыM.tech Cse FTBalaji SsrОценок пока нет

- 7BCE3C1 Data Structures and Computer AlgorithmsДокумент137 страниц7BCE3C1 Data Structures and Computer Algorithmshhc407319Оценок пока нет

- B.Tech (IT) - V SemДокумент16 страницB.Tech (IT) - V SemHatheem BeaucaОценок пока нет

- B.SC CSIT Micro Syllabus - Semester VДокумент21 страницаB.SC CSIT Micro Syllabus - Semester VKamal ShrishОценок пока нет

- OPTIMIZATION TECHNIQUES AND DATA STRUCTURESДокумент4 страницыOPTIMIZATION TECHNIQUES AND DATA STRUCTURESArun SivakumarОценок пока нет

- Data Structures and Algorithms Course SyllabusДокумент2 страницыData Structures and Algorithms Course Syllabusnetgalaxy2010Оценок пока нет

- Master of Science-Computer Science-SyllabusДокумент22 страницыMaster of Science-Computer Science-SyllabusManish MittalОценок пока нет

- Network Engineering 05 It 60xxДокумент62 страницыNetwork Engineering 05 It 60xxwhiteelephant93Оценок пока нет

- II Year - 3 Sem SyllabusДокумент14 страницII Year - 3 Sem SyllabussankarcsharpОценок пока нет

- Advanced Data and File Structures (ADS) : Paper 1Документ11 страницAdvanced Data and File Structures (ADS) : Paper 1xbabaxОценок пока нет

- B.Tech CSE IV SemДокумент9 страницB.Tech CSE IV SemsourabhОценок пока нет

- Compre SyllabusДокумент11 страницCompre SyllabusSUJIT KUMARОценок пока нет

- CSE-5th-sem-R2008 SyllabusДокумент13 страницCSE-5th-sem-R2008 SyllabusCSETUBEОценок пока нет

- COMP S.Y. B.tech Sem 3 2020 Pattern Syllabus 1Документ24 страницыCOMP S.Y. B.tech Sem 3 2020 Pattern Syllabus 1ruchihonaleОценок пока нет

- 401 SylДокумент12 страниц401 SylSatendra KumarОценок пока нет

- Computer Science EngineeringДокумент33 страницыComputer Science Engineeringsrinivasa_ds2kОценок пока нет

- MG Btech 4th Sem Cs SyllabusДокумент10 страницMG Btech 4th Sem Cs SyllabusJinu Madhavan100% (1)

- BooksДокумент3 страницыBooksMridanku Shekhar Pramanick0% (1)

- Detailed syllabus-MCA-2019-2020Документ34 страницыDetailed syllabus-MCA-2019-2020Total FunОценок пока нет

- Object Oriented Software Engineering, Data Warehousing, Computer Graphics & Fundamentals of AlgorithmsДокумент4 страницыObject Oriented Software Engineering, Data Warehousing, Computer Graphics & Fundamentals of Algorithmsrenuka05sharmaОценок пока нет

- Syllabus - I Yr PG - CSEДокумент46 страницSyllabus - I Yr PG - CSENaveenkumar BaskaranОценок пока нет

- Uttar Pradesh Technical University Lucknow: Bachelor of Information TechnologyДокумент24 страницыUttar Pradesh Technical University Lucknow: Bachelor of Information TechnologyRajeev SahaniОценок пока нет

- B.Tech 5th Sem SyllabusДокумент13 страницB.Tech 5th Sem Syllabusrahulchaudhary27075Оценок пока нет

- DSI 136 Module OutlineДокумент3 страницыDSI 136 Module OutlinePardon ChiumburukeОценок пока нет

- Code No.: MCA 202 LTC Paper: Design and Analysis of Algorithms 3 1 4Документ13 страницCode No.: MCA 202 LTC Paper: Design and Analysis of Algorithms 3 1 4kuku288Оценок пока нет

- B Tech CSE Sem5 SyllabusДокумент19 страницB Tech CSE Sem5 SyllabusJayant PahwaОценок пока нет

- Syllabus 4 ThsemДокумент11 страницSyllabus 4 ThsemARPITA ARORAОценок пока нет

- Anna University, Chennai: Affiliated InstitutionsДокумент7 страницAnna University, Chennai: Affiliated InstitutionsShama AnvarОценок пока нет

- Detailed SyllabusДокумент25 страницDetailed SyllabusxbabaxОценок пока нет

- Ma 2262 Probability and Queueing Theory 3 1 0 4Документ8 страницMa 2262 Probability and Queueing Theory 3 1 0 4karthickpsvОценок пока нет

- B.E (CSE) - V SemДокумент11 страницB.E (CSE) - V SemAnand KarthikОценок пока нет

- MG Btech 5th Sem Cs SyllabusДокумент9 страницMG Btech 5th Sem Cs SyllabusJinu MadhavanОценок пока нет

- M.E. (Comp. Scien. & Engg.) June 2013Документ44 страницыM.E. (Comp. Scien. & Engg.) June 2013barakОценок пока нет

- Textbooks GateДокумент4 страницыTextbooks GatesaitejОценок пока нет

- Updated Syllabus - ME CSE Word Document PDFДокумент62 страницыUpdated Syllabus - ME CSE Word Document PDFGayathri R HICET CSE STAFFОценок пока нет

- Proposed-Data Structure SyllabusДокумент3 страницыProposed-Data Structure SyllabussovitsovitsovitsovitОценок пока нет

- M Tech VLSI SyllabusДокумент45 страницM Tech VLSI Syllabussanjeev meenaОценок пока нет

- BE Comp SyllabusДокумент41 страницаBE Comp Syllabusjaimin_mojidraОценок пока нет

- M.C.a.sem III Operation Research 1Документ50 страницM.C.a.sem III Operation Research 1Pankaj SatkarОценок пока нет

- SGGS Institute of Engg & Technology,: Vishnupuri, NandedДокумент9 страницSGGS Institute of Engg & Technology,: Vishnupuri, NandedYogesh MahajanОценок пока нет

- DAA SyllabusДокумент2 страницыDAA SyllabusLalithya TumuluriОценок пока нет

- Original 1676265125 DAA SyllabusДокумент2 страницыOriginal 1676265125 DAA SyllabusVignesh DevamullaОценок пока нет

- Btechcomp 5thДокумент9 страницBtechcomp 5thAbhijeet BhagavatulaОценок пока нет

- 2 CMOS Diff Ampl Analysis - LSA PDFДокумент11 страниц2 CMOS Diff Ampl Analysis - LSA PDFakhОценок пока нет

- Familiarization of Beaglebone Black: Exp No: 1 Date:15-01-16Документ7 страницFamiliarization of Beaglebone Black: Exp No: 1 Date:15-01-16akhОценок пока нет

- 4 Diff Pair With MOS LoadsДокумент8 страниц4 Diff Pair With MOS LoadsakhОценок пока нет

- 2 CMOS Diff Ampl Analysis - LSAДокумент11 страниц2 CMOS Diff Ampl Analysis - LSAakhОценок пока нет

- 1 CMOS Diff Ampl IntroductionДокумент21 страница1 CMOS Diff Ampl IntroductionakhОценок пока нет

- Apj Abdul Kalam Technological University Thiruvananthapuram, Kerala, INDIAДокумент5 страницApj Abdul Kalam Technological University Thiruvananthapuram, Kerala, INDIAakhОценок пока нет

- APJ Abdul Kalam Technological University: Cs (Image Processing)Документ5 страницAPJ Abdul Kalam Technological University: Cs (Image Processing)akhОценок пока нет

- Switched Capacitor FiltersДокумент14 страницSwitched Capacitor FiltersakhОценок пока нет

- Switched Capacitor FiltersДокумент14 страницSwitched Capacitor FiltersakhОценок пока нет

- Switched Capacitor Integrator - PPTX (Repaired)Документ17 страницSwitched Capacitor Integrator - PPTX (Repaired)akhОценок пока нет

- AICDДокумент13 страницAICDakhОценок пока нет

- Switched Capacitor AmplifierДокумент13 страницSwitched Capacitor AmplifierakhОценок пока нет

- 2.01-Motion in A Straight Line-HWДокумент2 страницы2.01-Motion in A Straight Line-HWNirmal gkОценок пока нет

- Oracle® Database: Administrator's Reference 11g Release 1 (11.1) For Linux and UNIX-Based Operating Sys-TemsДокумент174 страницыOracle® Database: Administrator's Reference 11g Release 1 (11.1) For Linux and UNIX-Based Operating Sys-TemsPrakash MohantyОценок пока нет

- AgendaДокумент72 страницыAgendaThusitha WickramasingheОценок пока нет

- Proposal LayoutДокумент11 страницProposal Layoutadu g100% (1)

- Methods of Data Collection: Primary, Secondary, Observation, Interview & QuestionnaireДокумент19 страницMethods of Data Collection: Primary, Secondary, Observation, Interview & QuestionnairePraveen Nair100% (2)

- Galletto 1250 User GuideДокумент9 страницGalletto 1250 User Guidesimcsimc1Оценок пока нет

- Fisica Básica 3er Año SantillanaДокумент66 страницFisica Básica 3er Año SantillanaElifrnak91% (22)

- Branch and Cut Algorithm IME 960 ProjectДокумент23 страницыBranch and Cut Algorithm IME 960 ProjectAbhishek SinghОценок пока нет

- Sfnhs Form 138 & 137 No LinkДокумент9 страницSfnhs Form 138 & 137 No LinkZaldy TabugocaОценок пока нет

- Lesson Exemplar On Contextualizing Science Lesson Across The Curriculum in Culture-Based Teaching Lubang Elementary School Science 6Документ3 страницыLesson Exemplar On Contextualizing Science Lesson Across The Curriculum in Culture-Based Teaching Lubang Elementary School Science 6Leslie SolayaoОценок пока нет

- Ascension 2010 04Документ12 страницAscension 2010 04José SmitОценок пока нет

- Thermodynamics - Lectures b4 MidsemДокумент545 страницThermodynamics - Lectures b4 MidsemVismit Parihar100% (1)

- SplunkCloud-6 6 3-SearchTutorial PDFДокумент103 страницыSplunkCloud-6 6 3-SearchTutorial PDFanonymous_9888Оценок пока нет

- 5E Lesson Plan ScienceДокумент8 страниц5E Lesson Plan ScienceHanema MENORОценок пока нет

- Motenergy Me1507 Technical DrawingДокумент1 страницаMotenergy Me1507 Technical DrawingHilioОценок пока нет

- Notes On Unit - 4 - Employees Roles in Service MarketingДокумент3 страницыNotes On Unit - 4 - Employees Roles in Service MarketingSridhar Gowda67% (3)

- Handbook Fof Social MobilizationДокумент32 страницыHandbook Fof Social MobilizationAnith BaylisОценок пока нет

- Me-143 BcmeДокумент73 страницыMe-143 BcmekhushbooОценок пока нет

- Digital Image Processing System AbstractДокумент4 страницыDigital Image Processing System AbstractTelika RamuОценок пока нет

- SK08A Addressable Loop-Powered Siren Installation Sheet (Multilingual) R2.0Документ12 страницSK08A Addressable Loop-Powered Siren Installation Sheet (Multilingual) R2.0123vb123Оценок пока нет

- PESTEL Team Project (Group)Документ9 страницPESTEL Team Project (Group)Yadira Alvarado saavedraОценок пока нет

- Impact of K-Pop Music On The Academic PДокумент29 страницImpact of K-Pop Music On The Academic Pdave tayron paggao100% (1)

- Welcome To Word GAN: Write Eloquently, With A Little HelpДокумент8 страницWelcome To Word GAN: Write Eloquently, With A Little HelpAkbar MaulanaОценок пока нет

- Bangla Web AddressДокумент5 страницBangla Web Addressapi-3864412100% (5)

- Computational Chunking in Chess PDFДокумент211 страницComputational Chunking in Chess PDFTran VuОценок пока нет

- The Confidence Myth and What It Means To Your Career: by Tara MohrДокумент4 страницыThe Confidence Myth and What It Means To Your Career: by Tara MohrdargeniОценок пока нет

- Chemistry An Introduction To General Organic and Biological Chemistry Timberlake 12th Edition Test BankДокумент12 страницChemistry An Introduction To General Organic and Biological Chemistry Timberlake 12th Edition Test Banklaceydukeqtgxfmjkod100% (46)