Академический Документы

Профессиональный Документы

Культура Документы

Sum Adores

Загружено:

Angel ElizaldeАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Sum Adores

Загружено:

Angel ElizaldeАвторское право:

Доступные форматы

CARACTERIZACIN DE SUMADORES EN TECNOLOGAS FUERTEMENTE

SUBMICRNICAS1

Adrin Estrada, Carlos J. Jimnez, Manuel Valencia

Instituto de Microelectrnica de Sevilla Dpto. de Tecnologa Electrnica (Universidad de Sevilla)

estrada@imse.cnm.es, cjesus@imse.cnm.es, manolov@dte.us.es

En este trabajo estamos interesados en las

implementaciones microelectrnicas. La evolucin de las

tecnologas de integracin ha favorecido el diseo y la

implementacin de circuitos cada vez ms pequeos y

complejos. Cada nueva tecnologa de fabricacin reduce las

escalas de integracin precedentes al mismo tiempo que se

aumenta la densidad de integracin. Esta evolucin tiene

mltiples consecuencias entre las que nos interesa destacar:

ABSTRACT

En este trabajo se presentan los resultados de la

caracterizacin de las implementaciones integradas con

tecnologa fuertemente submicrnica de una amplia gama

de sumadores binarios. El objetivo bsico es comparar

sumadores paralelos clsicos con otros prefijos,

determinando cules proporcionan mejores caractersticas

al implementarlos en tecnologas de integracin

submicrnica. La caracterizacin se ha realizado siguiendo

una metodologa en la que hemos desarrollado los diseos

de los sumadores buscando la independencia tecnolgica y

en la que se efectan las medidas usando herramientas

CAD comerciales. Los resultados, que se han obtenido para

la tecnologa de UMC 013 m, muestran que las mejores

prestaciones corresponden a sumadores paralelos prefijo.

aunque no hay una estructura que pueda calificarse como

globalmente la mejor.

1.- El criterio de diseo basado en reducir el rea ya no es

tan determinante, sino que ahora es muy importante el

aumento de la velocidad de operacin, parmetro que

manifiesta un incesante y creciente inters. Ahora, pues,

deben tenerse en cuenta estructuras de alto coste en puertas

que antes fueron prohibitivas, aunque, por otra parte, siga

teniendo vigencia el criterio de diseo de reducir el coste.

2.- El aumento de la densidad de integracin y de la

velocidad de operacin han compensado el efecto de

disminucin del consumo de potencia debido a la

disminucin del tamao y de la bajada del valor de

alimentacin. El efecto global es que el consumo de

potencia es un parmetro que ha pasado de tenerse en

cuenta en slo algunos sistemas (como los porttiles o los

bioelectrnicos) a, hoy en da, ser esencial para cualquier

tipo de circuito, con el fin de evitar el exceso de

temperatura, que puede llegar a provocar su mal

funcionamiento durante la operacin normal.

1. INTRODUCCIN

Los circuitos sumadores paralelo de magnitudes binarias

son, probablemente, los tipos de circuito ms ampliamente

utilizados en los sistemas digitales [1]. Estn presentes

como subsistema esencial en procesadores de propsito

general, tanto en sus unidades aritmtico-lgicas de punto

fijo como en las de punto flotante, y en la mayora de

sistemas digitales de propsito especfico. Salvo en algunas

soluciones muy particulares para las operaciones complejas

(multiplicacin, divisin, etc.), son los sumadores paralelo,

ms que la implementacin especfica de los sumadores

completos de 1 bit (Full Adder, FA), los que determinan la

bondad del diseo en los circuitos que implementan dichas

operaciones. De aqu que en este trabajo nos hayamos

centrado en dichos sumadores paralelos.

1.

3.- Conforme decrecen las dimensiones mnimas de las

tecnologas, aparecen ms efectos que en las tecnologas

previas podan ser ignorados. As, en las tecnologas

fuertemente submicrnicas, hay que plantear la revisin del

comportamiento de los circuitos digitales con estas nuevas

tecnologas, por lo que es necesario una caracterizacin de

tanto de estructuras antiguas como nuevas, sobre todo en

circuitos tan importantes como los sumadores.

Este trabajo ha sido parcialmente financiado por el proyecto DOC (TEC 2004-01509/MIC).

1

la posicin 0 hasta la posicin i de manera que el sumador

completo correspondiente a esa posicin pueda generar el

resultado y el acarreo de salida correcto. Hay que esperar

que el acarreo se propague a travs de todos los sumadores

completos con el fin de obtener el resultado correcto de la

suma.

4/La tendencia incesante de cambios tecnolgicos, junto a

la cada vez mayor abstraccin de los diseos, debe

modificar los procedimientos de diseo hacia una menor

dependencia tecnolgica (en el sentido de que el resultado

de diseo pueda ser aplicado fcilmente a varias

tecnologas diferentes), as como al cada vez mayor apoyo

en las herramientas CAD comerciales.

Una forma de mejorar estos retrasos consiste en

acelerar la computacin de la red de acarreos. Existen

varias modificaciones sobre esta estructura que mejoran

este aspecto del sumador, como por ejemplo las estructuras

carry-skip adder, carry-completion adder y Manchester

adder [2], [4], [5].

En este trabajo se presentan nuestros resultados de

caracterizacin de implementaciones integradas con

tecnologa fuertemente submicrnica para una amplia gama

de sumadores binarios. Dada la existencia de una gran

cantidad de estructuras de sumadores en este trabajo,

necesariamente, hemos hecho una seleccin. El objetivo

bsico es comparar sumadores paralelos clsicos con otros

prefijos, determinando cules proporcionan mejores

caractersticas al implementarlos en tecnologas de

integracin submicrnica. La caracterizacin se ha

realizado siguiendo una metodologa en la que hemos

desarrollado los diseos de los sumadores buscando la

independencia tecnolgica y en la que se efectan las

medidas usando herramientas CAD comerciales, en

particular, la medicin de parmetros de rea, retraso y

consumo de potencia, utilizando siempre herramientas

comerciales de diseo semi-custom.

2.1.2. Sumador Manchester (Switched carry-ripple adder)

Este sumador es una optimizacin del sumador rizado,

consistente en incrementar la velocidad de clculo de la red

de acarreos mediante el empleo de una serie de funciones

lgicas y conmutadores. Para cada pareja de bits xi e yi se

generan una serie de seales que controlan el

funcionamiento de estos conmutadores. Estas seales son:

Pi, Gi y Ki, donde Pi se activa si se propaga el acarreo que

proviene de la etapa anterior, Gi se activa si se genera

acarreo en esta etapa i-sima y Ki que se activa en el caso de

que el acarreo sea cero. Estas seales se excluyen

mutuamente de manera que slo una de las seales est

activa en cada momento. Todos los conmutadores se fijan al

mismo tiempo y como resultado la propagacin del acarreo

slo sufre un retraso introducido por el conmutador en cada

etapa. La longitud de la red de acarreos est limitada por la

tecnologa utilizada para implementar los conmutadores.

Este artculo se estructura de la siguiente forma: en el

siguiente apartado se presentan las estructuras de

sumadores que se han caracterizado. A continuacin se

presenta la metodologa de caracterizacin que se ha

seguido y las pruebas y resultados de la caracterizacin

realizada. Finalmente se extraen las conclusiones.

2.1.3. Sumador con acarreo adelantado (Carry-lookahead

adder)

2. ESTRUCTURAS DE SUMADORES

Para la realizacin de la caracterizacin en tecnologas

submicrnicas, se han escogido ocho estructuras de

sumadores, cuatro de ellas ms clsicas y otras cuatro que

utilizan estructuras ms novedosas.

El siguiente paso para acelerar la computacin de la red de

acarreo es el uso del acarreo adelantado. Esta tcnica

consiste en calcular todos los acarreos intermedios en

paralelo, evitando as tener que esperar hasta que el acarreo

correcto se propague desde la etapa donde se ha generado

hasta la siguiente etapa. Este clculo puede realizarse

gracias a que toda la informacin necesaria est contenida

en los bits que componen los dos operadores. Mediante una

serie de operaciones lgicas simples y utilizando las

entradas del sumador es posible determinar qu etapa

generar un nuevo acarreo o lo propagar hacia la siguiente.

A continuacin se describen brevemente cada una de

las estructuras que se van a caracterizar.

2.1. Sumadores clsicos

2.1.1. Sumador rizado (Carry-ripple adder)

Conceptualmente, este es uno de los sumadores ms

simples. Se obtiene encadenando una secuencia de n

sumadores completos (FA, Full Adders) mediante las

salidas del acarreo de la etapa i a la entrada de acarreo de la

etapa i+1. El problema que plantea este tipo de estructura

reside en la propagacin del acarreo. En este tipo de

realizaciones el acarreo tiene que propagarse en serie desde

Sin embargo, aunque esta tcnica permite una mayor

velocidad a la hora de calcular el acarreo, para operandos

con un nmero de bits elevado, se necesita un gran nmero

de puertas con un alto fan-in [2]. Para solucionar este

problema, existen varias tcnicas, como puede ser el

particionado en varios bloques mas pequeos que

prefijo [6]. Estn orientados a aplicaciones de alto

rendimiento [7],[8],[9].

implementan el acarreo adelantado interconectados en

serie a travs de acarreos intermedios, como si de un

sumador rizado se tratara (ripple-block carry-lookahead)

[2].

Segn las definiciones de Pi, Gi y Ki, dadas

anteriormente, el clculo del acarreco es:

Otra tcnica que mejora la velocidad del sumador es

calcular los acarreos intermedios mediante un segundo

nivel de acarreo adelantado o generador de acarreo

adelantado (Block carry-lookahead adder). Variantes de

estas estructuras aaden ms niveles intermedios y ms

unidades de clculo de acarreo adelantado, como por

ejemplo, el sumador de acarreo adelantado con super

bloques (Superblock carry-lookahead adder), la versin

mejorada de ste (Improved superblock carry-lookahead

carry) o el sumador con acarreo adelantado con

superbloques en serie (Superblock-ripple carry-lookahead)

[2], [3].

ci + 1 = Gi + Pi ci

(P out,G out) = ( P i P i 1, G i + P i G i 1 )

(1)

La computacin del acarreo usando estas

expresiones puede verse como un problema recursivo que

puede ser resuelto de forma ms eficiente empleando la

computacin paralela prefija. Este tipo de computacin se

puede emplear con cualquier problema que use un operador

asociativo, como es el caso del operador fundamental de

carry [6], [7]. El esquema bsico de este tipo de problema

es, dadas n entradas y un operador asociativo cualquiera,

calcular n salidas, siendo cada una de estas salidas

dependiente de las entradas anteriores.

2.1.4. Sumador con seleccin de acarreo (Carry-select

adder)

Los sumadores basados en este tipo de estructuras

paralelas prefijas se denominan sumadores paralelos

prefijos y son bsicamente sumadores de acarreo

adelantado con un esquema diferente para el cmputo de la

red de acarreo. A continuacin se presentan algunas de las

estructuras paralelas prefijas ms significativas.

Este tipo de sumadores est compuesto por tres sumadores

de longitud k/2 que pueden ser de cualquier tipo, es decir,

acarreo anticipado, rizado, Manchester, etc., unidos para

formar un sumador de longitud k. Uno de los sumadores es

usado para calcular la parte baja de los k/2 bits de suma.

Los otros dos sumadores son utilizados para calcular los k/2

bits de la parte alta de la suma, con la caracterstica de que

uno de estos sumadores tiene como acarreo inicial C0 fijado

a uno y el otro sumador lo tiene fijado a cero. El resultado

correcto de la parte alta de la suma es seleccionado

mediante el acarreo de salida del sumador que calcula la

parte baja de la suma. Esta seleccin se realiza a travs de

un multiplexor controlado, como se ha mencionado antes

por el acarreo de salida del sumador encargado de computar

la parte baja de la suma.

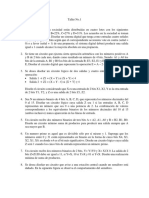

2.2.1. Sumador paralelo prefijo de R.P. Brent y H.T. Kung

(Brent-Kung Adder)

La Figura 1 muestra el rbol de computacin de acarreos de

un sumador tipo Brent-Kung de 16-bits. Los crculos

blancos que aparecen constituyen la etapa denominada de

precomputacin, en la cual se calculan los bits de

propagacin y de generacin. Los crculos negros

representan el operador fundamental del carry. En cada

circulo negro se realiza la operacin descrita por la

ecuacin (1). Las lneas encadenan pares de grupos de

propagacin y generacin de una etapa con otra de una fase

siguiente, para construir un grupo mayor hasta llegar a

obtener el acarreo de salida i-simo.

Con esta estructura, aunque se obtiene una mejora en

los tiempos de clculo, sta es a costa de duplicar la

circuitera necesaria para calcular una parte de la suma.

2.2. Sumadores paralelo prefijo (Parallel prefix adders)

Por ejemplo, las ecuaciones para el clculo del

acarreo de salida C12, segn se muestra en la Figura 1, es la

siguiente:

Uno de los problemas que tienen los sumadores con acarreo

adelantado es que al aumentar el nmero de bits

considerablemente aumenta de forma considerable la

complejidad de las ecuaciones para calcular el acarreo y el

fan-in de las puertas implicadas en estas ecuaciones. Estos

sumadores se basan en las mismas ecuaciones que usan los

sumadores de acarreo adelantado, pero emplendolas de

una forma ms genrica, reduciendo esta complejidad y en

consecuencia el fan-in de las puertas basndose en el

calculo de los acarreos usando tcnicas de clculo paralelo

C 12 = (G 11:0,P 11:0) = (G 11:8,P 11:8) (G 7:0,P 7:0)

Donde el primero de los trminos se calcula, primero

en base a trminos intermedios y posteriormente a trminos

primarios:

2.2.3. Sumador paralelo prefijo de R.E. Ladner y M.J Fischer(Ladner-Fischer parallel prefix adder)

(G 11:8,P 11:8) = (G 11:10,P 11:10) (G 9:8,P 9:8) =

= ( g 11, p 11 ) ( g 10, p 10 ) ( g 9, p 9 ) ( g 8, p 8 )

Ladner y Fischer introducen una estructura que tiende a

reducir el nmero de etapas. Sin embargo y como se puede

apreciar en la Figura 3, esta reduccin es a costa de un fanout mucho mayor que el resto de las estructuras prefijas

presentadas.

Como se puede observar en la Figura 1, el nmero de

etapas para esta estructura prefija son 7. En la primera

mitad hasta la etapa 4 se calculan los acarreos C1, C2, C4,

C8, C16. El resto de las etapas hasta la sptima se utiliza

para calcular el resto de acarreos. Esta estructura, como se

puede comprobar, es bastante simple ya que los nodos

tienen un fan-out bastante bajo [10]. Sin embargo, esto

repercute de forma directa en una mayor profundidad de la

estructura prefija y en consecuencia en un mayor retraso.

Dado el escaso nmero de etapas que presenta,

resulta bastante atractivo para aplicaciones que necesitan

un alto rendimiento. Sin embargo, esta estructura plantea

un fan-out elevado que redunda en una mayor lentitud de

las puertas y en un aumento del consumo [9], [11].

2.2.2. Sumador paralelo prefijo de P.M Kogge y H.S. Stone

(Kogge-Stone prefix adder)

2.2.4. Sumador paralelo prefijo de T. Han y D.A Carlson

(Han-Carlson parallel prefix adder)

Este tipo de sumador plantea una estructura similar a la

anterior, pero incrementando el nmero de lneas en cada

etapa (Figura 2). El fan-out, al igual que en la estructura

anterior, se sigue manteniendo en la unidad. Al aumentar el

nmero de lneas por etapa, se consigue reducir el nmero

de stas, obteniendo un menor retraso a la hora de realizar

la operacin de suma.

Esta estructura es un hbrido de las estructuras prefijas

presentadas por Kogge-Stone y Ladner-Fischer. De nuevo

se produce un incremento del nmero de etapas, aunque

menor que en el propuesto por Brent-Kung, para reducir el

fan-out del circuito (Figura 4).

El esquema planteado por Han-Carlson es similar al

planteado por Brent-Kung haciendo las operaciones con los

acarreos slo con los bits pares. Las seales de propagacin

y generacin de los bits impares se propagan a travs del

rbol prefijo. En la ltima etapa se combinan con las

seales de acarreo impares para generara los acarreos pares.

Al igual que el esquema planteado por Brent-Kung, este

reduce la complejidad a costa de aadir etapas adicionales

al rbol prefijo (cinco en el caso de la Figura 4).

Esta estructura resulta muy atractiva para

aplicaciones de alto rendimiento. Sin embargo, debido a la

complejidad que ofrece el rbol, la implementacin de este

circuito tiene un alto coste en rea y en consumo. Por otra

parte, esta estructura genera un layout regular y un fan-out

controlado [9],[11].

p15 g15

p14 g14

p13 g13

p12 g12

p11 g11

p10 g10

p9 g9

p8 g8

p7 g7

p6 g6

p5 g5

p4 g4

p3 g3

p1 g1

p2 g2

p0 g0

p15g15

C1

G[15:14],P[15:14]

G[13:12],P[13:12]

G[11:10],P[11:10]

G[9:8],P[9:8]

G[7:6],P[7:6]

G[5:4],P[5:4]

G[3:2],P[3:2]

G[1:0],P[1:0]

p14g14

p13g13

p12g12

p11g11

p10g10

p9g9

p8g8

p7g7

p6g6

p5g5

p4g4

p3g3

p2g2

p1g1

C1

stage1

C2

G[15:14],P[15:14]G[14:13],P[14:13]G[13:12],P[13:12]G[12:11],P[12:11] G[11:10],P[11:10]G[10:9],P[10:9] G[9:8],P[9:8] G[8:7],P[8:7] G[7:6],P[7:6] G[6:5],P[6:5] G[5:4],P[5:4] G[4:3],P[4:3] G[3:2],P[3:2] G[2:1],P[2:1] G[1:0],P[1:0]

G[15:12],P[15:12]

G[11:8],P[11:8]

G[7:4],P[7:4]

G[15:8],P[15:8]

G[15:0],P[15:0]

G[7:0],P[7:0]

G[3:0],P[3:0]

C4

stage5

C12

G[15:0],P[15:0] G[14:0],P[14:0] G[13:0],P[13:0] G[12:0],P[12:0] G[11:0],P[11:0] G[10:0],P[10:0] G[9:0],P[9:0] G[8:0],P[8:0]

G[14:0],P[14:0]

stage2

G[15:12],P[15:12]G[14:11],P[14:11]G[13:10],P[13:10] G[12:9],P[12:9] G[11:8],P[11:8] G[10:7],P[10:7] G[9:6],P[9:6] G[8:5],P[8:5] G[7:4],P[7:4] G[6:3],P[6:3] G[5:2],P[5:2] G[4:1],P[4:1] G[3:0],P[3:0] G[2:0],P[2:0]

stage3

C8

C3

G[15:8],P[15:8] G[14:7],P[14:7] G[13:6],P[13:6] G[12:5],P[12:5] G[11:4],P[11:4] G[10:3],P[10:3] G[9:2],P[9:2] G[8:1],P[8:1] G[7:0],P[7:0] G[6:0],P[6:0] G[5:0],P[5:0] G[4:0],P[4:0]

C15

G[9:0],P[9:0]

C14

G[12:0],P[12:0]

C13

G[10:0],P[10:0]

C11

G[5:0],P[5:0]

C10

G[8:0],P[8:0]

C9

C2

C4

stage4

G[13:0],P[13:0]

stage1

stage2

C16

G[11:0],P[11:0]

p0g0

G[6:0],P[6:0]

C7

stage6

C16

C6

G[4:0],P[4:0]

C5

G[2:0],P[2:0]

C15

C14

C13

C12

C11

C10

C8

C7

C6

C5

C9

stage7

C3

Figura 1: Sumador paralelo prefijo de 16-bits propuesto por

R.P. Brent y H.T. Kung

Figura 2: Sumador paralelo prefijo de 16-bits propuesto por

P.M Kogge y H.S Stone.

stage3

stage4

3.1. Parmetros a caracterizar

3. METODOLOGA DE CARACTERIZACIN

El proceso de caracterizacin se va a centrar en la

obtencin el rea ocupada por el diseo, el retraso mximo

y el consumo de potencia. Este ltimo parmetro, que

tradicionalmente ha sido crtico nicamente en los sistemas

porttiles, ahora, se ha convertido en un parmetro crtico

para cualquier tipo de circuito independientemente de su

grado de portabilidad.

3.1.1. rea ocupada por el circuito

El primer parmetro a obtener para la caracterizacin de los

circuitos es el rea ocupada por el diseo una vez

sintetizado en una tecnologa concreta. El rea ocupada por

un diseo basado en celdas determinada se puede expresar

como la suma de las reas de las celdas que lo componen, y

del rea utilizada para realizar las interconexiones entre

stas.

Adems, la metodologa tiene las siguientes

caractersticas:

Es independiente de la tecnologa en las primeras

etapas del diseo.

Utiliza flujo de diseo comerciales.

En tecnologas con slo dos capas de metal las celdas

se organizan en filas dejando un espacio entre ellas para

poder realizar la interconexin entre las celdas. Sin

embargo, en las tecnologas submicrnicas, debido a la

disponibilidad de ms de dos capas de metal, no es

necesario dejar espacio entre las diferentes filas que

componen el diseo. Dependiendo del nmero de metales

empleados en el rutado, en algunos casos ser necesario

introducir ciertas celdas vacas por las que realizar rutado

adicional.

En los flujos de diseos comerciales es habitual

comenzar las descripciones de los diseos a partir del nivel

de transferencia de registros o RT mediante lenguajes de

descripcin de hardware (HDL, Hardware Description

Language). Esto proporciona una independencia de los

diseos de la tecnologa empleada, consiguiendo as la

primera de las caractersticas de la metodologa de

caracterizacin. Estas descripciones, cumpliendo las

restricciones de sntesis, pueden ser sintetizadas por las

diferentes herramientas comerciales de sntesis existentes,

con lo que se cumple la segunda de las caractersticas. Son

estas herramientas las que seleccionarn las tecnologas

objetivo, por lo que esta metodologa es vlida para todas

las tecnologas de fabricacin de circuitos integrados que

cuenten con libreras de diseo para herramientas de

sntesis.

p15g15

p14g14

p13g13

p12g12

p11g11

p10g10

p9g9

p8g8

p7g7

p6g6

p5g5

p4g4

p3g3

p2g2

p1g1

El espacio introducido para rutado adicional depende

fundamentalmente de la tecnologa utilizada para

implementar el diseo y en menor medida de la

complejidad del diseo. En este caso no se va a considerar

el rea reservada para rutado adicional, ya que representa el

mismo porcentaje para todos los diseos y en consecuencia

no va a tener ningn efecto en la comparacin.

El rea ocupada por el diseo puede obtenerse en

diferentes etapas del diseo, siendo la primera de ella

despus de la sntesis del diseo en HDL como suma del

rea ocupada por todas las celdas. Esto nos va a evitar tener

que realizar el layout completamente rutado para obtener

una estimacin del rea. La suma del rea de todas las

p15 g15

p0g0

p14 g14

p13 g13

p12 g12

p11 g11

p10 g10

p9 g9

p8 g8

p7 g7

p6 g6

p5 g5

p4 g4

p3 g3

p1 g1

p2 g2

p0 g0

C1

C1

G[15:14],P[15:14]

G[13:12],P[13:12]

G[11:10],P[11:10]

G[9:8],P[9:8]

G[7:6],P[7:6]

G[11:8],P[11:8] G ,P

[10:8] [10:8]

G[15:12],P[15:12] G[14:12],P[14:12]

G[5:4],P[5:4]

G[3:2],P[3:2]

G[7:4],P[7:4] G ,P

[6:4] [6:4]

C3

C7

C6

G[11:10],P[11:10]

G[9:8],P[9:8]

G[7:6],P[7:6]

G[5:4],P[5:4]

G[3:2],P[3:2]

G[15:12],P[15:12]

G[13:10],P[13:10]

G[11:8],P[11:8]

G[9:6],P[9:6]

G[7:4],P[7:4]

G[5:2],P[5:2]

G[3:0],P[3:0]

G[15:8],P[15:8]

G[13:6],P[13:6]

G[11:4],P[11:4]

G[9:2],P[9:2]

G[7:0],P[7:0]

G[15:0],P[15:0]

G[7:0],P[7:0] G[6:0],P[6:0] G[5:0],P[5:0] G[4:0],P[4:0]

C8

G[13:12],P[13:12]

G[1:0],P[1:0]

stage1

C2

C2

G[3:0],P[3:0] G ,P

[2:0] [2:0]

C4

G[15:8],P[15:8] G ,P G ,P G ,P

[14:8] [14:8] [13:8] [13:8] [12:8] [12:8]

G[1:0],P[1:0]

G[15:14],P[15:14]

C16

G[13:0],P[13:0]

C14

G[11:0],P[11:0]

C12

G[9:0],P[9:0]

C8

G[5:0],P[5:0]

stage2

C4

stage3

C6

stage4

C10

C5

G[14:0],P[14:0]

C15

G[12:0],P[12:0]

C13

G[10:0],P[10:0]

C11

G[8:0],P[8:0]

C9

G[6:0],P[6:0]

C7

G[4:0],P[4:0]

C5

G[2:0],P[2:0]

stage5

C3

G[15:0],P[15:0] G ,P G ,P G ,P G ,P G ,P G ,P G ,P

[14:0] [14:0] [13:0] [13:0] [12:0] [12:0] [11:0] [11:0] [10:0] [10:0]

[9:0] [9:0]

[8:0] [8:0]

C16

C15

C14

C13

C12

C11

C10

C9

Figura 3: Sumador paralelo prefijo de 16-bits de R.E Ladner y

M.J. Fischer.

Figura 4: Sumador paralelo prefijo de 16-bits propuesto por T.

Han y D.A. Carlson.

3.1.3. Potencia consumida

celdas puede obtenerse con la propia herramienta de

sntesis.

El consumo de potencia, adems de ser uno de los

parmetros que ms importancia ha ido adquiriendo

conforme se reduca la escala de integracin, es tambin

uno de los ms difciles de medir con precisin.

3.1.2. Retraso mximo

El valor del retraso mximo puede obtenerse usando una

herramienta de anlisis esttico o mediante el uso de

simuladores lgicos temporales. Los simuladores son

herramientas que ofrecen una gran precisin en la medicin

de retrasos. Sin embargo, la obtencin del retraso mximo,

necesita del conocimiento a priori del patrn de entradas

concreto que activan el camino crtico. Dado que a priori

no se conoce este patrn es necesario la realizacin de

simulaciones exhaustivas (con todos los patrones), la

medicin de todos los retrasos para cada patrn y la

obtencin del mayor de ellos. Este anlisis resulta bastante

costoso en tiempo y en esfuerzo.

La potencia consumida se puede dividir en potencia

esttica y potencia dinmica. La potencia esttica suele ser

calculada mediante la suma del consumo esttico de cada

una de las celdas que forman el diseo. Estos datos estn

incluidos en la librera de celdas. La potencia dinmica por

su parte contribuye de mayor manera a la potencia global

consumida. Su valor depende del nmero de transiciones en

todos los nodos del circuito. Por ello un clculo preciso de

esta potencia pasa necesariamente por un clculo preciso de

las transiciones en todos los nodos del circuito, para lo que

es necesario tener unos modelos de simulacin bastante

precisos de las celdas [11].

Por otra parte, las herramientas de anlisis esttico

estn especficamente diseadas para realizar esta tarea,

puesto que el clculo del retraso lo hacen para cada posible

ruta del diseo. Este tipo de anlisis puede tener el

problema de contabilizar rutas que no se lleguen a activar

nunca. Sin embargo, estas situaciones son ms crticas en

circuitos secuenciales donde la existencia de

retroalimentacin puede hacer que la medicin del retraso

llegue a ser bastante compleja. En los circuitos

combinacionales estas herramientas proporcionan buenos

resultados con un esfuerzo mnimo. Adems, la mayora de

las herramientas de sntesis que existen en el mercado

incorporan este tipo de analizadores que adems de

proporcionar informacin temporal sobre el diseo,

tambin son utilizadas para realizar las optimizaciones

temporales.

La actividad de conmutacin de los nodos internos

de circuitos realizados utilizando metodologas de diseo

semi-custom, tiene que ser calculada utilizando simuladores

lgicos, puesto que en general no se dispone de

descripciones a nivel de transistores de las celdas de

librera.

3.2. Procedimiento de caracterizacin empleado

La Figura 5 muestra el procedimiento de caracterizacin

empleado en este trabajo. El flujo sigue los siguientes

pasos:

El punto de partida es la realizacin de una

descripcin del diseo a nivel de transferencia de registros.

Simulacin

Funcional

Diseo

RTL

Simulacin

Temporal

Libreras

tecnolgicas

Informe de

rea

Herramienta de

sntesis

Informe de

Retrasos

Informe de

Actividad

Patrones

de

simulacin

Libreras

de modelos

Informe de

Consumo

Figura 5: Diagrama de flujo del procedimiento de caracterizacin seguido.

Cada uno de estos sumadores ha sido optimizado en

rea y consumo, fijando las restricciones de diseo para

rea, consumo dinmico y consumo por prdidas, a cero

con el fin de indicar a la herramienta que intente minimizar

estos valores lo mximo posible. Los valores de rea y

retraso mximo para estos circuitos, se han obtenido

utilizando la herramienta Design Analyzer Report.

Para realizar esta descripcin se ha usado el lenguaje de

descripcin de hardware VHDL. Estas descripciones son

independientes de la tecnologa.

Antes de realizar la sntesis del diseo con una

tecnologa determinada, se ha verificado que las

descripciones VHDL tienen un comportamiento funcional

correcto, mediante la realizacin de simulaciones

funcionales.

Al ser el consumo de potencia dependiente de las

transiciones que se producen en todos los nodos del circuito

y tener que realizar una simulacin para obtener estos

datos, ha sido necesario generar un conjunto de patrones de

simulacin. Para las pruebas realizadas se ha generado un

conjunto aleatorio de 104 patrones. La frecuencia de

operacin ha sido fijada a 10 MHz.

Una vez verificado el funcionamiento correcto de las

descripciones VHDL, se procedi a su sntesis mediante

una herramienta de sntesis. La herramienta de sntesis

instancia el diseo en una tecnologa concreta mediante el

uso de celdas estndar. Una vez sintetizados los diseos se

procede a la caracterizacin de los mismos.

4.1. Resultados obtenidos

La caracterizacin del rea ocupada y del retraso

mximo de cada una de las celdas puede hacerse en base a

los informes generados por la propia herramienta de

sntesis.

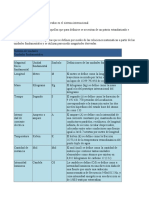

Las pruebas han sido realizadas para la tecnologa UMC

0.13 m. La Tabla 1, muestra los resultados obtenidos para

los parmetros de rea, retraso, potencia y consumo.

Para conocer con precisin el consumo dinmico es

necesario medir previamente la actividad de conmutacin

en los nodos internos, cosa que se hace empleando un

simulador lgico. Para ello el primer paso consiste en

exportar el diseo sintetizado a un formato susceptible de

ser importado por el simulador. Para la simulacin se

emplea un conjunto de patrones que no pretenden realizar

una comprobacin funcional del circuito, sino obtener una

estadistica o promedio, de manera que se usa un conjunto

de patrones generados de forma aleatoria. Con esto, el

simulador debe generar un fichero con la actividad de

conmutacin de cada nodo del circuito. Con este fichero, la

herramienta de sntesis es capaz de generar un informe del

consumo que tiene el circuito.

La Figura 6, muestra el consumo de rea para cada

uno de los sumadores empleados. Como se puede observar,

los sumadores paralelos prefijos son los que consumen

mayor rea, notandose an ms esta diferencia a medida

que aumenta el nmero de bits que conforman los

operandos de entrada del sumador. Esto es as, en este tipo

de sumadores debido a la complejidad que presentan los

rboles de computacin que los forman.

En la Figura 7 se ilustra la evolucin del consumo de

rea respecto al aumento de la longitud de los operandos,

mostrandose un crecimiento ms lineal en el caso de los

sumadores clasicos, a excepcin del sumador de Seleccin

de acarreo (carry select), que tiene un compartimento ms

parecido a los sumadores paralelos prefijos. Esto es debido

al elevado nmero de recursos que emplea para realizar la

operacin de suma, consecuencia de su naturaleza hibrida.

4. PRUEBAS REALIZADAS

El procedimiento de caracterizacin se ha aplicado a los

ocho sumadores descritos anteriormente. Para ello, en

primer lugar, se ha realizado una descripcin VHDL de

cada una de las estructuras de sumadores y se han

verificado funcionalmente. Estas pruebas se han realizado

para estructuras con 16, 32 y 64 bits.

8000

7000

6000

5000

4000

3000

2000

1000

Las herramientas empleadas para llevar a cabo las

pruebas de la metodologa han sido Synopsys y Modelsim.

De Synopsys se ha empleado la aplicacin Design Analyzer

para sintetizar las descripciones VHDL en la tecnologa

UMC 0.13 m. Modelsim ha sido utilizado para verificar la

funcionalidad de las descripciones VHDL y generar los

ndices de actividad de los nodos de cada una de las

estructuras seleccionadas.

R ip

p le

R.

Ca

T.

P.

R.

Ca

P.

Ha

M

r ry M a n

E.

r ry

.K

ch

Br

nLa

Lo

Se

Ca

og

en

es

dn

o

D.

kA

ge

l ec

trry

te r

er

A

H

t

he

.C

-H

-M

.T

ad

ar

.S

.K

.J

l

s

.S

.F

on

un

to n

i sc

g

he

e

1 6 - b its

3 2 - b its

6 4 - b its

Figura 6: Consumo de rea en funcin del nmero de bits.

rea (m2)

Retraso (ns)

Potencia*Retraso (fJ)*

Potencia (W)

16-bits

32-bits

64-bits

16-bits

32-bits

64-bits

16-bits

32-bits

64-bits

16-bits

32-bits

64-bits

Ripple Carry

665,28

1278

2823,5

4,89

7,67

13

14,19

20,91

49,92

69,4

160,4

649,6

Carry Look Ahead

573,69

1175

2358,7

2,95

5,87

17

7,3

11,54

30,18

21,7

67,8

513,5

Manchester

642,81

1257,9

2528

3,18

7,35

22,5

8,3

17,64

43,68

26,7

129,7

986,9

Carry Select

1047,1

2089,1

4143,7

2,11

3,93

11,6

13,1

28,57

73,76

27,7

112,3

858,6

Brent-Kung

1035

2151,3

3620,1

1,63

2,15

3,17

8,81

18,66

45,90

14,4

40,1

145,5

Han-Carlson

1149,1

2446,8

4843,5

1,36

1,77

3,29

9,33

19,33

44,25

12,7

34,2

145,6

Kogge-Stone

1468,8

3516,4

7756,9

1,42

1,63

2,21

10,8

25,32

54,91

15,4

41,3

121,4

Ladner-Fischer

1057,5

2583,3

5612,5

0,91

1,95

3,02

9,92

21,9

53,41

9,0

42,7

161,3

Tabla 1: rea, retraso y potencia para sumadores de 16, 32 y 64-bits. Tecnologa UMC 0.13m.

clsicos, los sumadores de Seleccin de acarreo (carry

select) y acarreo adelantado (carry look ahead) son los que

mejores prestaciones de velocidad ofrecen para el caso de

16-bits, as como para 32-bits. Sin embargo, para el caso de

64-bits, los sumadores de acarreo adelantado y los

sumadores Manchester son los que ofrecen un peor

rendimiento, siendo mejores los sumadores rizados (ripple

carry) y los sumadores basados en la seleccin de acarreo

(carry select). Respecto al conjunto de sumadores paralelos

prefijos, todos ofrecen un comportamiento lineal, de

manera que, en general, mantienen prcticamente las

mismas diferencias de velocidad al variar la longitud de sus

operandos. El ms rpido de todos ellos es el propuesto por

R.E. Ladner y M.J. Fischer para el caso de 16-bits, mientras

que el propuesto por P.M Kogge y H.S Stone es el ms

rpido para el caso de 32 y 64-bits (Figura 9).

El sumador que experimenta un mayor crecimiento

de rea al aumentar el nmero de bits es el propuesto por

P. M. Kogge y H. S. Stone, debido a que tiene el rbol de

computacin ms complejo de los de su clase. De los

sumadores evaluados, el que presenta un crecimiento

prcticamente lineal es el sumador paralelo prefijo

propuesto por R. P. Brent y H. T. Kung, lo que lo convierte

en un candidato ms que aceptable para aplicaciones que

tengan limitaciones de rea.

En relacin con el retraso, como se puede observar

en la Figura 8, los sumadores paralelos prefijos tienen un

comportamiento prcticamente lineal, siendo ideales para

aplicaciones que precisen de velocidad. Los sumadores

clsicos se ven afectados en mayor medida por los cambios

en la longitud de los operandos, siendo el sumador

Manchester el que peor se comporta. El sumador con

acarreo adelantado (carry look ahead), tiene un

comportamiento similar al sumador Manchester, debido al

crecimiento de la complejidad de sus expresiones para el

clculo del acarreo. Dentro del conjunto de sumadores

En relacin al consumo, para el caso de 16, 32 y 64bits el sumador que menos consumo presenta es el basado

en la estructura de acarreo adelantado, mientras que el que

ms consume es el sumador basado en la estructura con

Ripple Carry

25

9000

Ripp le Car r y

8000

Carry Look Ahead

20

Ca rr y L oo k A he a d

Manchester

7000

Ma n c h es te r

6000

15

Carry Select

Ca rr y Se le c t

5000

10

R. P. Br en t - H. T.

Ku ng

T. Ha n - D. A .

Ca rls on

P. M. Ko gg e - H. S.

Sto n e

R. E. La d ne r - M. J.

Fis c he r

4000

3000

2000

1000

0

16

-b

i ts

32

-b

i ts

64

-b

5

0

16

-bi

ts

32

-bi

ts

64

-bi

ts

R. P. Brent - H. T.

Kung

T. Han - D. A.

Carlson

P. M. Kogge - H. S.

Stone

R. E. Ladner - M.

J. Fischer

i ts

Figura 8: Evolucin del retraso respecto al tamao de los

operandos

Figura 7: Evolucin del consumo de rea respecto al tamao de

los operandos

Se puede concluir que los sumadores paralelos

prefijos, junto con las estructuras de acarreo adelantado,

son la mejor opcin para aplicaciones que requieran

velocidad y bajo consumo. Sin embargo, las estructuras

clsicas, son ideales para aplicaciones que tengan

restricciones de rea.

25

20

15

10

5

0

5. CONCLUSIONES

Rip C

R

M

ple arry anc Carry . P. T. Ha P. M R. E

Ca Lo hes Se Bre n - . Ko . La

rry ok

gg

dn

nt - D.

t

lec

e

r

Ah

t

H. A. C e - H er ea

M

T.

d

Ku arlso . S. S . J.

ng

n

ton Fisc

e

her

16-bits

32-bits

En este articulo se ha presentado una caracterizacin de

diversas estructuras de sumadores en tecnologas

fuertemente submicrnicas. La caracterizacin de dichos

circuitos se ha realizado en base a los tres parmetros ms

importantes: rea ocupada por el circuito, mximo retraso

entre las entradas y las salidas y la potencia consumida.

64-bits

Figura 9: Retraso en funcin de la longitud de los operandos

El procedimiento de caracterizacin seguido tiene las

siguientes caractersticas:

seleccin de acarreo, debido al elevado nmero de recursos

empleados para implementar esta estructura. Los

sumadores paralelos prefijos, ofrecen una variacin del

consumo similar para el mismo nmero de bits. En trmino

medio los sumadores paralelos prefijos ofrecen una buena

opcin para aplicaciones que requieran un bajo consumo de

potencia (Figura 10).

Utilizacin de herramientas de CAD comerciales.

Aplicable a diferentes tecnologas.

Empleo de flujos de diseo semi-custom.

Con todo esto, el procedimiento parte de la

descripcin de los circuitos usando lenguajes de

descripcin de hardware manteniendo adems las

restricciones impuestas por las principales herramientas de

sntesis. De esta forma se consigue mantener el diseo

independiente de la tecnologa en esta primera etapa del

diseo.

Como se puede observar en la Figura 11, los

sumadores paralelos prefijos presentan una relacin

prcticamente lineal frente al producto potencia retraso, de

manera que son la opcin a considerar en aplicaciones que

requieran un cierto equilibrio entre la potencia consumida y

la tiempo de respuesta. Los sumadores clsicos, sin

embargo, ofrecen en general una peor relacin entre ambos

parmetros, de manera pueden ser apropiados para

aplicaciones que requieran poco consumo o poco retraso,

pero no en aquellas que requieran un compromiso entre

ambos parametros.

80

70

60

50

40

30

20

10

0

El empleo de herramientas de sntesis comerciales

transforma esta descripcin en un netlist de celdas de una

tecnologa concreta. La propia herramienta de sntesis

permite la obtencin de los datos de rea ocupada y de

retraso mximo entre entradas y salidas.

Ripple Carry

A dder

Carry Look

A head A dder

Manc hester

A dder

Carry Select

A dder

Brent-Kung

A dder

Han-Carls on

A dder

LadnerFis cher A dder

R. E. Ladner M. J. Fis cher

3,5

3

2,5

2

1,5

1

Rip C

R.

ple arry Manc Carr

P T. H P. M R.

Ca Lo hes y Se . Bre an - . Ko E. La

rry ok

Ah ter lect nt - H D. A. gge - dner

ea

-M

. T. Ca

H

d

Ku rlso . S. S . J.

n

ng

ton Fisc

e

her

16-bits

32-bits

0,5

0

16

- bi

ts

32

- bi

ts

64

- bi

ts

64-bits

Figura 11: Evolucin del la relacin consumo-potencia.

Figura 10: Consumo en funcin de la longitud de los operandos.

[6] P. M. Kogge. Parallel Solutions of Recurrence

problems, I.B.M. Journal Research and Development,

March 1994.

Para la obtencin del consumo de potencia es

necesario el paso previo de calcular los ndices de actividad

de los nodos intermedios del circuito. Para ello el diseo

sintetizado es exportado y simulado en un simulador lgico

capaz de generar dicha informacin. Con este fichero, la

herramienta de sntesis genera el dato de consumo

dinmico del circuito.

[7] P. M. Kogge and H. S. Stone, A parallel Algorithm for

the efficient solution of general class of recurrence

equations, IEEE Transaction Computers, vol V-22, N8,

1973, pp 786-793.

La caracterizacin se ha llevado a cabo sobre

diferentes estructuras de sumadores propuestas en la

literatura, tanto clsicas como ms novedosas.

[8] H. Ling, High speed binary adders, I. B. M. Journal

Research and Develoment, vol 25, p.155-66, 1981.

[9] T. D. Han, D. A. Carlson. Fast area-efficient VLSI

adder, 8th Symposium on computer arithmetic, May 1987.

Se ha realizado una descripcin VHDL sintetizable

de todos los sumadores escogidos, algunas de las cuales son

parametrizables en cuanto al nmero de bits del sumador.

Para aquellos que no han podido ser parametrizados se han

realizado descripciones con 16 y 32 y 64 bits en los

operandos. Tras comprobar su comportamiento funcional

se ha procedido a su sntesis y a la obtencin de los

parmetros que los caracterizan.

[10] R. P. Brent and H. T. Kung, A regular layout for

parallel adders, IEEE Transaction on Computer, C-31,

Marzo 1982, pp 260-264.

[11] C. Baena, J. Juan Chico, M. J. Bellido, P. Ruiz de

Clavijo, C. J. Jimenez and M. Valencia, Measurement of

Switching Activity of CMOS Digital Circuits at Gate

Level, PATMOS 2002, pp. 353-362.

Finalmente se han analizado los datos con objeto de

obtener las recomendaciones de las estructuras analizadas

en funcin de los requerimientos de la aplicacin en la que

vayan a ser utilizados. Como conclusiones generales puede

extraerse que las estructuras de sumadores clsicas ofrecen,

en general, un menor consumo de rea pero presentan

tambin un retraso mucho mayor. Por otro lado, aunque las

estructuras ms novedosas tienen un mayor consumo de

potencia, los valores obtenidos para la figura de mrito

retraso*potencia son mejores para stas estructuras que

para las clsicas.

6. REFERENCIAS

[1] Ch. Nagendra, M. J. Irwin, R. M. Owens, Area-TimePower Tradeoffs in Parallel Adders, IEEE Trans. on

Circuits and Systems - II: Analog and Digital Signal

Processing, Vol. 43, N 10, octubre 1996, pp. 689-701.

[2] Amos R. Omondi, Computer Artihmetic Systems,

Prentice Hall International, 1994

[3] Milos D. Ercegovac, Thomas Lang, Ed. Morgan and

Kaufmann, Digital Aritmetic, 2004

[4] Behrooz Parhami, Computer Arithmetic Algorithms and

Hardware Design, Ed. Oxford University Press, 2000

[5] Haru Yamamoto, Shane Erikson, Design and

Comparison of Standard Adder Schemes, Haru Yamamoto,

Shane Erikson, Winter 2004, U.C.L.A.

10

Вам также может понравиться

- Televisión digital y telecomunicaciones en comunidades de propietariosОт EverandTelevisión digital y telecomunicaciones en comunidades de propietariosОценок пока нет

- Adder Brent y KoggeДокумент3 страницыAdder Brent y KoggeJONATHANОценок пока нет

- Lab 1-GPIOДокумент4 страницыLab 1-GPIOsantiago gomezОценок пока нет

- FinalДокумент15 страницFinalWilly Peres LopezОценок пока нет

- Informe 4Документ5 страницInforme 4Juan Camilo HerreraОценок пока нет

- CCNA 1 Capítulo 4 v5Документ11 страницCCNA 1 Capítulo 4 v5Karin Janett Santisteban Bances100% (1)

- Antenas - Cardama Jofre Rius Romeu Blanch FerrandoДокумент460 страницAntenas - Cardama Jofre Rius Romeu Blanch FerrandojjhuarteОценок пока нет

- Info. Filtro Pasa Bajas PDFДокумент2 страницыInfo. Filtro Pasa Bajas PDFLinda CastilloОценок пока нет

- Proyecto IntegradorДокумент26 страницProyecto IntegradorJhonatan Vegara Drigelio VergaraОценок пока нет

- Parte 1 Taller 1Документ25 страницParte 1 Taller 1Emily LopezОценок пока нет

- Practica 1 Histograma en ImagenДокумент2 страницыPractica 1 Histograma en ImagenDiego Armando Cruz SeguraОценок пока нет

- García Reig - Diseño y Fabricación de Un Brazo Robótico de 6 GDL de Bajo Coste Basado en ArduinoДокумент69 страницGarcía Reig - Diseño y Fabricación de Un Brazo Robótico de 6 GDL de Bajo Coste Basado en ArduinoSebastián Ferrer FerreОценок пока нет

- Maquinas de Estado AlgorítmicoДокумент7 страницMaquinas de Estado AlgorítmicoCristian BravoОценок пока нет

- Informe Laboratorio Ele Digital MultiplicadorДокумент5 страницInforme Laboratorio Ele Digital MultiplicadorDiego VargasОценок пока нет

- Contador Decimal de Dos Digigitos en 7 Segmentos Usando MultiplexacionДокумент7 страницContador Decimal de Dos Digigitos en 7 Segmentos Usando MultiplexacionPlc PlcОценок пока нет

- Práctica 5 Circuitos Lógicos CombinatoriosДокумент6 страницPráctica 5 Circuitos Lógicos CombinatoriosBayron A. Pérez AyalaОценок пока нет

- Dimensionamiento de ConductoresДокумент1 страницаDimensionamiento de Conductoreselectroramos2011100% (1)

- El Control de 2 Motores Con El TB6612FNGДокумент14 страницEl Control de 2 Motores Con El TB6612FNGValeria Hernandez ChavezОценок пока нет

- Practica AWRДокумент11 страницPractica AWRCARLOS EDUARDO JOVEN GARCIAОценок пока нет

- Innforme Practica VHDL ALUДокумент13 страницInnforme Practica VHDL ALUNatalia_meneses8Оценок пока нет

- Journal Práctica L-02Документ6 страницJournal Práctica L-02RED BOWОценок пока нет

- Tema 6 Teclado Digital DecimalДокумент4 страницыTema 6 Teclado Digital Decimal2mercedesОценок пока нет

- Ingenieria ElectronicaДокумент3 страницыIngenieria ElectronicaViviana Karen Lima Irigoyen100% (1)

- Hamming PDFДокумент5 страницHamming PDFEdwin RamirezОценок пока нет

- Problemas Diseño Combinacionales PDFДокумент7 страницProblemas Diseño Combinacionales PDFXiomaraОценок пока нет

- Examen de Sistemas DigitalesДокумент11 страницExamen de Sistemas DigitalesMax cuadrosОценок пока нет

- I EXAMEN PARCIAL - Economía GeneralДокумент8 страницI EXAMEN PARCIAL - Economía GeneralJhonny GómezОценок пока нет

- Deber 6 (Unif, Exp, Normal)Документ3 страницыDeber 6 (Unif, Exp, Normal)Martin PinzónОценок пока нет

- Simulación de ondas electromagnéticas de una antena dipoloДокумент2 страницыSimulación de ondas electromagnéticas de una antena dipoloBenja ApaquiОценок пока нет

- Convertidores analógicos y digitales: tipos, características y usosДокумент4 страницыConvertidores analógicos y digitales: tipos, características y usosAlber Lim GboОценок пока нет

- A4SD Ago 2017Документ7 страницA4SD Ago 2017Jaky GutierrezОценок пока нет

- Practica6 Organización y Arquitectura de ComputadorasДокумент17 страницPractica6 Organización y Arquitectura de ComputadorasEduardo RojasОценок пока нет

- Tema 2 - Sistemas Combinacionales IДокумент38 страницTema 2 - Sistemas Combinacionales Iwh0caresОценок пока нет

- Zonas de Servidumbre Ancho de Franja en Lineas de TransmisionДокумент1 страницаZonas de Servidumbre Ancho de Franja en Lineas de TransmisionAlejandro Arroyave100% (1)

- Simulacion de Un Puente Rectificador MonofasicoДокумент9 страницSimulacion de Un Puente Rectificador MonofasicoHugo Quezada AlegríaОценок пока нет

- Hoja Datos Termo Duo RTD 1035449Документ4 страницыHoja Datos Termo Duo RTD 1035449Alvaro Aniceto RomeroОценок пока нет

- Taller No.1Документ2 страницыTaller No.1MargellyОценок пока нет

- Tercer Laboratorio de Ingenieria de Control I.doc RenzoДокумент5 страницTercer Laboratorio de Ingenieria de Control I.doc RenzoEJ AlvarezОценок пока нет

- Compuertas LogicasДокумент27 страницCompuertas Logicaszzzxxx666Оценок пока нет

- 4.teorema de La Maxima Potencia de TransferenciaДокумент24 страницы4.teorema de La Maxima Potencia de TransferenciaLuis Chavez100% (1)

- A32 - Modelado en Espacio de EstadoДокумент11 страницA32 - Modelado en Espacio de EstadoLaura GonzalezОценок пока нет

- Practica 3 Contadores MODДокумент11 страницPractica 3 Contadores MODAlex Moreano AОценок пока нет

- 001 Exp. 7 El Amplificador de Emisor ComúnДокумент3 страницы001 Exp. 7 El Amplificador de Emisor ComúnERICK ADONIS ANAYA FLORESОценок пока нет

- Aplicaciones de Circuitos DigitalesДокумент15 страницAplicaciones de Circuitos DigitalesAlex Pomier AliagaОценок пока нет

- Prueba 1 IB RúbricaДокумент1 страницаPrueba 1 IB RúbricaEstefani columbaОценок пока нет

- Diodos y Transistores BJTДокумент16 страницDiodos y Transistores BJTHola MundoОценок пока нет

- Pic Servomotor AssemblerДокумент4 страницыPic Servomotor AssemblerAbraham SAROОценок пока нет

- Laboratorio n4 de Sumador Multiplexor y DemultiplexorДокумент11 страницLaboratorio n4 de Sumador Multiplexor y DemultiplexorSantos Zosimo Ocas GoicocheaОценок пока нет

- Laboratorio 8Документ8 страницLaboratorio 8luis smallОценок пока нет

- E3Документ3 страницыE3Linda Esmeralda Torres RiosОценок пока нет

- Actividad Tema 7 Guia de EjerciciosДокумент4 страницыActividad Tema 7 Guia de Ejerciciosmmorales44Оценок пока нет

- Alex Caiza-Organizador Grafico PDFДокумент2 страницыAlex Caiza-Organizador Grafico PDFEdissonmauricio Lalaleo100% (1)

- Matriz de IncidenciaДокумент2 страницыMatriz de Incidenciamahoma51100% (1)

- ISA ArquitecturaДокумент37 страницISA ArquitecturaPedro Miguel TxÇОценок пока нет

- Introducción a VHDLДокумент34 страницыIntroducción a VHDLAnel VallarinoОценок пока нет

- Introducción al amplificador operacional (OPAMДокумент16 страницIntroducción al amplificador operacional (OPAMDaniel Alberto Suárez MáynezОценок пока нет

- Medidor de ángulo de fase y factor de potencia monofásicoДокумент9 страницMedidor de ángulo de fase y factor de potencia monofásicoLil SeanОценок пока нет

- ALGORITMO DIAGNÓSTICO FALLAS MÁQUINAS ELÉCTRICASДокумент5 страницALGORITMO DIAGNÓSTICO FALLAS MÁQUINAS ELÉCTRICASKeviin JoelОценок пока нет

- Proyecto Banda Transportadora Motor DCДокумент39 страницProyecto Banda Transportadora Motor DCEDUARDO XAVIER ROMERO TOROОценок пока нет

- Contador de Pulzo para Servo MecanismosДокумент6 страницContador de Pulzo para Servo Mecanismoscarlosgabriel1971Оценок пока нет

- Calculo Primero y SiguienteДокумент6 страницCalculo Primero y SiguienteRodrigoxyzОценок пока нет

- Operaciones Complemento A 2Документ10 страницOperaciones Complemento A 2VíctorОценок пока нет

- Verilog Tutorial v1Документ23 страницыVerilog Tutorial v1jcudrisОценок пока нет

- ISEy VerilogДокумент36 страницISEy Verilogfabian_mastersОценок пока нет

- BVNVVДокумент13 страницBVNVVLauraRodríguezSagásteguiОценок пока нет

- Fisica 1 Guía 1 Verano 2021Документ16 страницFisica 1 Guía 1 Verano 2021MissleniaInocenteОценок пока нет

- Informe ConductometriaДокумент5 страницInforme ConductometriaAnn' KateeОценок пока нет

- Coordenadas geográficas: latitud y longitudДокумент3 страницыCoordenadas geográficas: latitud y longitudRodolfo Barbosa YoungОценок пока нет

- Informe Superposicion M.a.SДокумент2 страницыInforme Superposicion M.a.SStefany UrregoОценок пока нет

- Tema 1 Test de Evaluación de La Condición FísicaДокумент10 страницTema 1 Test de Evaluación de La Condición FísicaAlejandro Rodríguez Calzado100% (1)

- Tema 4Документ82 страницыTema 4Kevin RodriguezОценок пока нет

- 1 - Ecuación de Continuidad y BEMДокумент30 страниц1 - Ecuación de Continuidad y BEMLisandra Alvarez DiazОценок пока нет

- Amvdd 25Документ25 страницAmvdd 25Miguel Angel Cara RiosОценок пока нет

- Configuración en CascadaДокумент12 страницConfiguración en Cascadajorge gaspar gabrielОценок пока нет

- Manual de Reparacion de Cajas Renault1Документ36 страницManual de Reparacion de Cajas Renault1Jesus Salazar100% (3)

- 02.2. - Tema 01 Introduccion Al Diseño Estructural en Acero. 15 01 2021Документ37 страниц02.2. - Tema 01 Introduccion Al Diseño Estructural en Acero. 15 01 2021Jezsús KasTroОценок пока нет

- MT-024 Solucion PDFДокумент28 страницMT-024 Solucion PDFAlexander SosaОценок пока нет

- La Sistematizacion Una Forma de Investigar Las Practicas y Producir Saber y ConicimientoДокумент36 страницLa Sistematizacion Una Forma de Investigar Las Practicas y Producir Saber y ConicimientoValentinrojasОценок пока нет

- 8.1. - Latitud Por Meridiana de Sol PDFДокумент1 страница8.1. - Latitud Por Meridiana de Sol PDFJhonnatan Manrique0% (1)

- Clase 1 (Fisica)Документ13 страницClase 1 (Fisica)Oliver MichelОценок пока нет

- Talleres Bateria Arrancador y AlternadorДокумент39 страницTalleres Bateria Arrancador y AlternadorAguila RealОценок пока нет

- EL TEODOLITO. - Sus Partes.Документ5 страницEL TEODOLITO. - Sus Partes.Jerson EstelaОценок пока нет

- Isa CalculoДокумент32 страницыIsa Calculocatoperators100% (1)

- Corrientes de CortocircuitoДокумент19 страницCorrientes de CortocircuitoJ Jesus AradillasОценок пока нет

- Serie 1Документ4 страницыSerie 1miguelin_csОценок пока нет

- Tarea 2Документ2 страницыTarea 2Humberto D. ParrillaОценок пока нет

- METODOS DE DEMOSTRACIÓN (MATERIAl #2)Документ5 страницMETODOS DE DEMOSTRACIÓN (MATERIAl #2)nievesba92% (12)

- Practica - Vectores #03Документ3 страницыPractica - Vectores #03Hans Jheferson Nuñez Suxe50% (2)

- Trabajo Practica Ingenieria IndustrialДокумент24 страницыTrabajo Practica Ingenieria IndustrialJhoana A. Ficarra100% (1)

- Fogler Capitulo 1Документ7 страницFogler Capitulo 1Rafael FonsecaОценок пока нет

- DioptríaДокумент53 страницыDioptríaAnonymous yammW0RwОценок пока нет

- Guía de Laboratorio Nº3Документ4 страницыGuía de Laboratorio Nº3Lenin SalinasОценок пока нет

- 1769-SDN Modulo de Comunicacion Device-NetДокумент24 страницы1769-SDN Modulo de Comunicacion Device-NetIsraelОценок пока нет

- Influencia. La psicología de la persuasiónОт EverandInfluencia. La psicología de la persuasiónРейтинг: 4.5 из 5 звезд4.5/5 (14)

- Excel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másОт EverandExcel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másРейтинг: 2.5 из 5 звезд2.5/5 (3)

- Manual Técnico del Automóvil - Diccionario Ilustrado de las Nuevas TecnologíasОт EverandManual Técnico del Automóvil - Diccionario Ilustrado de las Nuevas TecnologíasРейтинг: 4.5 из 5 звезд4.5/5 (14)

- ChatGPT Ganar Dinero Desde Casa Nunca fue tan Fácil Las 7 mejores fuentes de ingresos pasivos con Inteligencia Artificial (IA): libros, redes sociales, marketing digital, programación...От EverandChatGPT Ganar Dinero Desde Casa Nunca fue tan Fácil Las 7 mejores fuentes de ingresos pasivos con Inteligencia Artificial (IA): libros, redes sociales, marketing digital, programación...Рейтинг: 5 из 5 звезд5/5 (4)

- Clics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaОт EverandClics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaРейтинг: 4.5 из 5 звезд4.5/5 (116)

- Estructuras de Datos Básicas: Programación orientada a objetos con JavaОт EverandEstructuras de Datos Básicas: Programación orientada a objetos con JavaРейтинг: 5 из 5 звезд5/5 (1)

- Inteligencia artificial: Lo que usted necesita saber sobre el aprendizaje automático, robótica, aprendizaje profundo, Internet de las cosas, redes neuronales, y nuestro futuroОт EverandInteligencia artificial: Lo que usted necesita saber sobre el aprendizaje automático, robótica, aprendizaje profundo, Internet de las cosas, redes neuronales, y nuestro futuroРейтинг: 4 из 5 звезд4/5 (1)

- Auditoría de seguridad informática: Curso prácticoОт EverandAuditoría de seguridad informática: Curso prácticoРейтинг: 5 из 5 звезд5/5 (1)

- Cómo Seducir Mujeres con tu Celular: Envía poderosos mensajes de texto que cautivarán a las mujeres que siempre has deseado tener en tu vidaОт EverandCómo Seducir Mujeres con tu Celular: Envía poderosos mensajes de texto que cautivarán a las mujeres que siempre has deseado tener en tu vidaРейтинг: 4 из 5 звезд4/5 (9)

- Lean: La Guía Fundamental para Lean Startup, Lean Six Sigma, Lean Analytics, Lean Enterprise, Lean Manufacturing, Scrum, Gestión Agile de Proyectos y KanbanОт EverandLean: La Guía Fundamental para Lean Startup, Lean Six Sigma, Lean Analytics, Lean Enterprise, Lean Manufacturing, Scrum, Gestión Agile de Proyectos y KanbanРейтинг: 5 из 5 звезд5/5 (1)

- Reparar (casi) cualquier cosa: Cómo ajustar los objetos de uso cotidiano con la electrónica y la impresora 3DОт EverandReparar (casi) cualquier cosa: Cómo ajustar los objetos de uso cotidiano con la electrónica y la impresora 3DРейтинг: 5 из 5 звезд5/5 (6)

- La biblia del e-commerce: Los secretos de la venta online. Más de mil ideas para vender por internetОт EverandLa biblia del e-commerce: Los secretos de la venta online. Más de mil ideas para vender por internetРейтинг: 5 из 5 звезд5/5 (7)

- Lean Seis Sigma: La guía definitiva sobre Lean Seis Sigma, Lean Enterprise y Lean Manufacturing, con herramientas para incrementar la eficiencia y la satisfacción del clienteОт EverandLean Seis Sigma: La guía definitiva sobre Lean Seis Sigma, Lean Enterprise y Lean Manufacturing, con herramientas para incrementar la eficiencia y la satisfacción del clienteРейтинг: 4.5 из 5 звезд4.5/5 (5)

- EL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.От EverandEL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.Рейтинг: 4 из 5 звезд4/5 (51)

- El trading online de una forma sencilla: Cómo convertirse en un inversionista online y descubrir las bases para lograr un trading de éxitoОт EverandEl trading online de una forma sencilla: Cómo convertirse en un inversionista online y descubrir las bases para lograr un trading de éxitoРейтинг: 4 из 5 звезд4/5 (30)

- AngularJS: Conviértete en el profesional que las compañías de software necesitan.От EverandAngularJS: Conviértete en el profesional que las compañías de software necesitan.Рейтинг: 3.5 из 5 звезд3.5/5 (3)

- LAS VELAS JAPONESAS DE UNA FORMA SENCILLA. La guía de introducción a las velas japonesas y a las estrategias de análisis técnico más eficaces.От EverandLAS VELAS JAPONESAS DE UNA FORMA SENCILLA. La guía de introducción a las velas japonesas y a las estrategias de análisis técnico más eficaces.Рейтинг: 4.5 из 5 звезд4.5/5 (54)

- Energía solar autónoma: Una guía práctica para entender e instalar sistemas fotovoltaicos y de bateríasОт EverandEnergía solar autónoma: Una guía práctica para entender e instalar sistemas fotovoltaicos y de bateríasОценок пока нет