Академический Документы

Профессиональный Документы

Культура Документы

Half-Bridge LLC Resonant Converter Design Using FSFR-Series Fairchild Power Switch (FPS™)

Загружено:

ihsanjuОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Half-Bridge LLC Resonant Converter Design Using FSFR-Series Fairchild Power Switch (FPS™)

Загружено:

ihsanjuАвторское право:

Доступные форматы

www.fairchildsemi.

com

AN-4151

Half-Bridge LLC Resonant Converter Design Using

FSFR-Series Fairchild Power Switch (FPS)

Introduction

The effort to obtain ever-increasing power density of

switched-mode power supply has been limited by the size

of passive components. Operation at higher frequencies

considerably reduces the size of passive components, such

as transformers and filters; however, switching losses have

been an obstacle to high-frequency operation. To reduce

switching losses and allow high-frequency operation,

resonant switching techniques have been developed.

These techniques process power in a sinusoidal manner

and the switching devices are softly commutated.

Therefore, the switching losses and noise can be

dramatically reduced [1-7].

Among various kinds of resonant converters, the simplest

and most popular resonant converter is the LC series

resonant converter, where the rectifier-load network is

placed in series with the L-C resonant network, as depicted

in Figure 1 [2-4]. In this configuration, the resonant network

and the load act as a voltage divider. By changing the

frequency of driving voltage Vd, the impedance of the

resonant network changes. The input voltage is split

between this impedance and the reflected load. Since it is a

voltage divider, the DC gain of a LC series resonant

converter is always <1. At light-load condition, the

impedance of the load is very large compared to the

impedance of the resonant network; all the input voltage is

imposed on the load. This makes it difficult to regulate the

output at light load. Theoretically, frequency should be

infinite to regulate the output at no load.

Q1

Lr

Vin

n:1

Vd

Ro

Q2

+

VO

-

Cr

Figure 1. Half-Bridge LC Series Resonant Converter

To overcome the limitation of series resonant converters,

LLC resonant converter has been proposed [8-12]. LLC

resonant converter is a modified LC series resonant

converter implemented by placing a shunt inductor across

the transformer primary winding as depicted in Figure 2.

When this topology was first presented, it did not receive

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

much attention due to the counterintuitive concept that

increasing the circulating current in the primary side with a

shunt inductor can be beneficial to circuit operation.

However, it can be very effective in improving efficiency

for high-input voltage application where the switching loss

is much more dominant than the conduction loss.

In most of the practical design, this shunt inductor is

realized using the magnetizing inductance of the

transformer. The circuit diagram of LLC resonant

converter looks much the same as the LC series resonant

converter: The only difference is the value of the

magnetizing inductor. While the series resonant converter

has a magnetizing inductance much larger than the LC

series resonant inductor (Lr), the magnetizing inductance

in LLC resonant converter is just 3~8 times Lr, which is

usually implemented by introducing an air gap in the

transformer.

Q1

Lr

Vin

Q2

n:1

Ro

Lshunt

+

VO

( Lm )

Cr

Figure 2. Half-bridge LLC Resonant Converter

An LLC resonant converter has many advantages over a

series resonant converter; it can regulate the output over

wide line and load variations with a relatively small

variation of switching frequency. It can achieve zero

voltage switching (ZVS) over the entire operating range.

All essential parasitic elements, including junction

capacitances of all semi-conductor devices and the leakage

inductance and magnetizing inductance of the transformer,

are utilized to achieve soft-switching.

This application note presents design considerations of an

LLC resonant half-bridge converter employing FSFRseries FPS. It includes explanation of LLC resonant

converter operation principle, designing the transformer

and resonant network, and selecting the components. The

step-by-step design procedure explained with a design

example helps design the LLC resonant converter.

www.fairchildsemi.com

AN-4151

APPLICATION NOTE

1. LLC Resonant Converter and

Fundamental Approximation

Ip

Figure 3 shows the simplified schematic of a half-bridge

LLC resonant converter, where Lm is the magnetizing

inductance that acts as a shunt inductor, Lr is the series

resonant inductor, and Cr is the resonant capacitor.

Figure 4 illustrates the typical waveforms of the LLC

resonant converter. It is assumed that the operation

frequency is same as the resonance frequency, determined

by the resonance between Lr and Cr. Since the magnetizing

inductor is relatively small, there exists considerable

amount of magnetizing current (Im), which freewheels in

the primary side without being involved in the power

transfer. The primary-side current (Ip) is sum of the

magnetizing current and the secondary-side current

referred to the primary.

IDS1

ID

Vin

Vd

Vgs1

In general, the LLC resonant topology consists of three

stages shown in Figure 3; square wave generator, resonant

network, and rectifier network.

Im

Vgs2

The square wave generator produces a square wave

voltage, Vd, by driving switches Q1 and Q2 alternately

with 50% duty cycle for each switch. A small dead

time is usually introduced between the consecutive

transitions. The square wave generator stage can be

built as a full-bridge or half-bridge type.

The resonant network consists of a capacitor, leakage

inductances, and the magnetizing inductance of the

transformer. The resonant network filters the higher

harmonic currents. Essentially, only sinusoidal current

is allowed to flow through the resonant network even

though a square wave voltage is applied to the

resonant network. The current (Ip) lags the voltage

applied to the resonant network (that is, the

fundamental component of the square wave voltage

(Vd) applied to the half-bridge totem pole), which

allows the MOSFETs to be turned on with zero

voltage. As shown in Figure 4, the MOSFET turns on

while the voltage across the MOSFET is zero by

flowing current through the anti-parallel diode.

The rectifier network produces DC voltage by

rectifying the AC current with rectifier diodes and

capacitor. The rectifier network can be implemented

as a full-wave bridge or center-tapped configuration

with capacitive output filter.

Figure 4. Typical Waveforms of Half-bridge LLC

Resonant Converter

The filtering action of the resonant network allows use of

the fundamental approximation to obtain the voltage gain

of the resonant converter, which assumes that only the

fundamental component of the square-wave voltage input

to the resonant network contributes to the power transfer to

the output. Because the rectifier circuit in the secondary

side acts as an impedance transformer, the equivalent load

resistance is different from actual load resistance. Figure 5

shows how this equivalent load resistance is derived. The

primary-side circuit is replaced by a sinusoidal current

source, Iac, and a square wave of voltage, VRI, appears at

the input to the rectifier. Since the average of |Iac| is the

output current, Io, Iac, is obtained as:

I ac

Io

2

sin(t )

and VRI is given as:

VRI Vo

if sin(t ) 0

VRI Vo

if sin(t ) 0

The fundamental component of VRI is given as:

4V

VRI F o sin(t )

Q1

resonant network

Vin

Q2

Ip

+

Lr

Vd

Im

Cr

(2)

where Vo is the output voltage.

Square wave generator

IDS1

(1)

n:1

Since harmonic components of VRI are not involved in the

power transfer, AC equivalent load resistance can be

calculated by dividing VRIF by Iac as:

Rectifier network

ID

Io

Ro

Lm

Rac

+

VO

VRI F

8 V

8

2 o 2 Ro

I ac

Io

(4)

Considering the transformer turns ratio (n=Np/Ns), the

equivalent load resistance shown in the primary side is

obtained as:

Figure 3. Schematic of Half-bridge LLC

Resonant Converter

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

(3)

Rac

8n

Ro

(5)

www.fairchildsemi.com

AN-4151

APPLICATION NOTE

By using the equivalent load resistance, the AC equivalent

circuit is obtained, as illustrated in Figure 6, where VdF and

VROF are the fundamental components of the driving voltage,

Vd and reflected output voltage, VRO (nVRI), respectively.

where:

Lp Lm Lr , Rac

Lr 1

Q

, o

Cr Rac

+

VRI

Iac

I ac

VRIF

Vo

VRI

Io

2

VRI F

sin( wt )

4Vo

Lr

sin( wt )

+

-

Np:Ns

Rac

8n 2

1

L p Cr

Ro

VRoF

Lm

Rac

2

2n Vo (m 1) p

1 at o (7)

o 2 p 2

Vin

The operating range of the LLC resonant converter is

limited by the peak gain (attainable maximum gain), which

is indicated with * in Figure 7. It should be noted that the

peak voltage gain does not occur at fo nor fp. The peak gain

frequency where the peak gain is obtained exists between

fp and fo, as shown in Figure 7. As Q decreases (as load

decreases), the peak gain frequency moves to fp and higher

peak gain is obtained. Meanwhile, as Q increases (as load

increases), the peak gain frequency moves to fo and the

peak gain drops; thus, the full load condition should be the

worst case for the resonant network design.

Ro

-

Lr

Cr

V dF

VO

VRI

Lm

n=Np/Ns

Lr

1

, p

Lr Cr

The gain of Equation 6 is plotted in Figure 7 for different

Q values with m=3, fo=100kHz, and fp=57kHz. As

observed in Figure 7, the LLC resonant converter shows

gain characteristics that are almost independent of the load

when the switching frequency is around the resonant

frequency, fo. This is a distinct advantage of LLC-type

resonant converter over the conventional series resonant

converter. Therefore, it is natural to operate the converter

around the resonant frequency to minimize the switching

frequency variation.

Figure 5. Derivation of Equivalent Load Resistance Rac

Vin

Lp

Equation 6 shows the gain is unity at resonant frequency

(o), regardless of the load variation, which is given as:

VO

Ro

Cr

Ro , m

As can be seen in Equation 6, there are two resonant

frequencies. One is determined by Lr and Cr, while the

other is determined by Lp and Cr.

Io

Vd

+

pk

I ac

Iac

8n 2

(nVRIF)

fp

Figure 6. AC Equivalent Circuit for LLC Resonant

Converter

1

2 L p Cr

fo

1

2 Lr Cr

2.0

Q=0.25

With the equivalent load resistance obtained in Equation 5,

the characteristics of the LLC resonant converter can be

derived. Using the AC equivalent circuit of Figure 6, the

voltage gain, M, is obtained as:

1.8

Lr / Cr

Rac

Q=1.0

1.6

Gain ( 2nVo / Vin )

Q=0.75

4n Vo

sin(t )

V F n VRI F

2n Vo

M ROF

F

4 Vin

Vd

Vd

Vin

sin(t )

(6)

2

2

) ( m 1)

o

2

2

( 2 1) j ( 2 1)( m 1)Q

p

o o

1.4

Q=0.50

Q=0.25

1.2

1.0

Q=1.0

M @ fo 1

0.8

0.6

40

50

60

70

80

90

100

110

120

130

140

freq (kHz)

Figure 7. Typical Gain Curves of LLC Resonant

Converter (m=3)

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

www.fairchildsemi.com

3

AN-4151

APPLICATION NOTE

2. Consideration for Integrated

Transformer

2n VO

M

Vin

For practical design, it is common to implement the

magnetic components (series inductor and shunt inductor)

using an integrated transformer; where the leakage

inductance is used as a series inductor, while the

magnetizing inductor is used as a shunt inductor. When

building the magnetizing components in this way, the

equivalent circuit in Figure 6 should be modified as shown

in Figure 8 because the leakage inductance exists, not only

in the primary side, but also in the secondary side. Not

considering the leakage inductance in the transformer

secondary side generally results in an incorrect design.

Cr

Vd

+

Vin

Llks

Llkp

where:

VinF

Cr

1: M V

Lr

Lp-Lr

(M V

Lp

1

, p

Lr Cr

1

L p Cr

Lp

Lp Lr

m

m 1

at o

(10)

L p Lr

ideal

transformer

Rac

The gain at the resonant frequency (o) is unity when

using individual core for series inductor, as shown in

Equation 7. However, when implementing the magnetic

components with integrated transformer, the gain at the

resonant frequency (o) is larger than unity due to the

virtual gain caused by the leakage inductance in the

transformer secondary side.

VROF

(nVRIF)

The gain of Equation 9 is plotted in Figure 10 for different

Qe values with m=3, fo=100kHz, and fp=57kHz. As observed

in Figure 9, the LLC resonant converter shows gain

characteristics almost independent of the load when the

switching frequency is around the resonant frequency, fo.

Figure 8. Modified Equivalent Circuit to Accommodate

the Secondary-side Leakage Inductance

In Figure 8, the effective series inductor (Lp) and shunt

inductor (Lp-Lr) are obtained by assuming n2Llks=Llkp and

referring the secondary-side leakage inductance to the

primary side as:

Lr Llkp Lm //(n 2 Llks ) Llkp Lm // Llkp

fp

2.2

1

2 L p Cr

fo

1

2 Lr Cr

Qe=0.25

Qe

2.0

(8)

Lr / Cr

Rac e

Qe=1.00

1.8

Qe=0.75

Gain ( 2nVo / Vin )

Lp Lm Llkp

When handling an actual transformer, equivalent circuit

with Lp and Lr is preferred since these values can be easily

measured with a given transformer. In an actual

transformer, Lp and Lr can be measured in the primary side

with the secondary-side winding open circuited and short

circuited, respectively.

Qe=0.50

1.6

Qe=0.25

1.4

1.2

M @ fo M V

Qe=1.0

1.0

In Figure 9, notice that a virtual gain MV is introduced,

which is caused by the secondary-side leakage inductance.

By adjusting the gain equation of Equation 6 using the

modified equivalent circuit of Figure 9, the gain equation

for integrated transformer is obtained:

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

Lr 1

, o

Cr Rac e

Qe

Ro

Lr Llkp Lm //( n 2 Llks )

L p Llkp Lm

L

8n 2 Ro

, m p

2 MV 2

Lr

M MV

n:1

Llkp Lm // Llkp

Rac e

The gain at the resonant frequency (o) is fixed regardless

of the load variation, which is given as:

VO

2

) m(m 1)

o 2

2

( 2 1) j ( ) ( 2 1) (m 1) Q e

p

o o

VRI

Lm

(9)

2

) (m 1) M V

o

2

2

( 2 1) j ( ) ( 2 1) (m 1)Q e

p

o o

(

0.8

40

50

60

70

80

90

100

110

120

130

140

freq (kHz)

Figure 9. Typical Gain Curves of LLC Resonant

Converter (m=3) Using an Integrated Transformer

www.fairchildsemi.com

4

AN-4151

APPLICATION NOTE

3. Consideration of Operation Mode

and Attainable Maximum Gain

Operation Mode

The LLC resonant converter can operate at frequency

below or above the resonance frequency (fo), as

illustrated in Figure 10. Figure 11 shows the waveforms

of the currents in the transformer primary side and

secondary side for each operation mode. Operation

below the resonant frequency (case I) allows the soft

commutation of the rectifier diodes in the secondary

side, while the circulating current is relatively large. The

circulating current increases more as the operation

frequency moves downward from the resonant

frequency. Meanwhile, operation above the resonant

frequency (case II) allows the circulating current to be

minimized, but the rectifier diodes are not softly

commutated. Below resonance operation is preferred for

high output voltage applications, such as Plasma Display

Panel (PDP) TV where the reverse recovery loss in the

rectifier diode is severe. Below resonance operation also

has a narrow frequency range with respect to the load

variation since the frequency is limited below the

resonance frequency even at no load condition.

Im

(I) fs < fo

1

2 fS

IDS1

IO

ID

(II) fs > fo

Ip

Im

IDS1

ID

IO

Figure 11. Waveforms of Each Operation Mode

Required Maximum Gain and Peak Gain

Above the peak gain frequency, the input impedance of

the resonant network is inductive and the input current of

the resonant network (Ip) lags the voltage applied to the

resonant network (Vd). This permits the MOSFETs to

turn on with zero voltage (ZVS), as illustrated in Figure

12. Meanwhile, the input impedance of the resonant

network becomes capacitive and Ip leads Vd below the

peak gain frequency. When operating in capacitive

region, the MOSFET body diode is reverse recovered

during the switching transition, which results in severe

noise. Another problem of entering into the capacitive

region is that the output voltage becomes out of control

since the slope of the gain is reversed. The minimum

switching frequency should be well limited above the

peak gain frequency.

On the other hand, above resonance operation has less

conduction loss than the below resonance operation. It can

show better efficiency for low output voltage applications,

such as Liquid Crystal Display (LCD) TV or laptop

adaptor, where Schottky diodes are available for the

secondary-side rectifiers and reverse recovery problems

are insignificant. However, operation at above the resonant

frequency may cause too much frequency increase at lightload condition. Above frequency operation requires

frequency skipping to prevent too much increase of the

switching frequency.

Gain (M)

1

2 fo

Ip

M

capacitive

region

peak gain

inductive

region

Load increase

fs

II

Below resonance

(fs<fo)

Above resonance

(fs>fo)

fo

Vd

Vd

Ip

Ip

IDS1

IDS1

fs

Figure 10. Operation Modes According to the Operation

Frequency

reverse recovery

ZVS

Figure 12. Operation Waveforms for Capacitive and

Inductive Regions

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

www.fairchildsemi.com

5

AN-4151

APPLICATION NOTE

The available input voltage range of the LLC resonant

converter is determined by the peak voltage gain. Thus, the

resonant network should be designed so that the gain curve

has an enough peak gain to cover the input voltage range.

However, ZVS condition is lost below the peak gain point,

as depicted in Figure 12. Therefore, some margin is required

when determining the maximum gain to guarantee stable

ZVS operation during the load transient and start-up.

Typically 10~20% of the maximum gain is used as a margin

for practical design, as shown in Figure 13.

2.2

2.1

1.9

1.8

peak gain

1.7

Gain (M)

peak gain

10~20% of

Mmax

1.6

1.5

m=2.25

1.4

m=2.5

maximum operation gain

(Mmax)

1.3

m=3.0

1.2

m=6.0

m=9.0 m=8.0 m=7.0

1.1

m=3.5

m=4.0

m=4.5

m=5.0

1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.1

1.2

1.3

1.4

fo

fs

Figure 14. Peak Gain (Attainable Maximum Gain) vs.

Q for Different m Values

Figure 13. Determining the Maximum Gain

Even though the peak gain at a given condition can be

obtained by using the gain in Equation 6, it is difficult to

express the peak gain in explicit form. To simplify the

analysis and design, the peak gains are obtained using

simulation tools and depicted in Figure 14, which shows

how the peak gain (attainable maximum gain) varies with

Q for different m values. It appears that higher peak gain

can be obtained by reducing m or Q values. With a given

resonant frequency (fo) and Q value, decreasing m means

reducing the magnetizing inductance, which results in

increased circulating current. Accordingly, there is a tradeoff between the available gain range and conduction loss.

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

www.fairchildsemi.com

6

AN-4151

APPLICATION NOTE

4. Features of FSFR-Series

Table 1.

FSFR-series is an integrated Pulse Frequency Modulation

(PFM) controller and MOSFETs specifically designed for

Zero Voltage Switching (ZVS) half-bridge converters with

minimal external components. The internal controller

includes an under-voltage lockout, optimized high-side /

low-side gate driver, temperature-compensated precise

current controlled oscillator, and self-protection circuitry.

Compared with discrete MOSFET and PWM controller

solution, FSFR-series can reduce total cost, component

count, size and weight, while simultaneously increasing

efficiency, productivity, and system reliability.

This pin is the drain of the high-side

MOSFET, typically connected to the input

DC link voltage.

This pin is for enable/disable and protection.

When the voltage of this pin is above 0.6V,

the IC operation is enabled. Meanwhile,

CON when the voltage of this pin drops below

0.4V, gate drive signals for both MOSFETs

are disabled. When the voltage of this pin

increases above 5V, protection is triggered.

This pin is to program the switching

frequency. Typically, opto-coupler and

RT

resistor are connected to this pin to regulate

the output voltage.

VDL

CS

This pin is to sense the current flowing

through the low-side MOSFET. Typically

negative voltage is applied on this pin.

SG

This pin is the control ground.

This pin is the power ground. This pin is

connected to the source of the low-side

MOSFET.

This pin is the supply voltage of the control

LVcc

IC.

PG

VDL

3 4 5 6 7 8

RT SG LVcc

CON CS PG

10

VCTR

HVcc

Pin Description

No connection.

NC

HVcc

10

VCTR

This pin is the supply voltage of the highside drive circuit.

This pin is the drain of the low-side

MOSFET. Typically transformer is

connected to this pin.

Figure 15. Package Diagram

LVcc

VDL

ICTC

2ICTC

3V

1V

-Q

11.3 / 14.5 V

LVcc good

Vref

8.7 / 9.2 V

HVcc good

Internal

Bias

ICTC

VREF

F/F

HVcc

10

VCTR

NC

PG

SG

2V

RT

Time

Delay

High-Side

Gate Drive

Level-Shift

350ns

Counter (1/4)

LVcc

Idelay

CON

Time

Delay

350ns

0.6V/0.4V

Low-Side

Gate Drive

Balancing

delay

5V

OLP

LVcc

OVP

LVcc good

-Q

Auto-restart

protection

23V

Shutdown without delay

-1

50ns delay

-Q

0.9V

VAOCP

TSD

Latch

protection

LVcc < 5V

delay

1.5 s

VOCP

0.6V

CS

Figure 16. Functional Block Diagram of FSFR-series

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

www.fairchildsemi.com

7

AN-4151

APPLICATION NOTE

Llks

Cr

Rdamp Dboot

LVcc

Vcc C

LVcc

Llkp

Vin

(From PFC

output)

Ns

HVcc

Lm

Ns

RSS

CB

CSS

RLPF

Rbias

CHVcc

CON

Control

IC

VCTR

Integrated Llks D2

transformer

CLPF

SG

Vo

Rd

CF RF

KA431

CS

CDL

Co

VDL

RT

Rmax Rmin

Np

D1

PG

Rsense

Figure 17. Reference Circuit for Design Example of LLC Resonant Half-bridge Converter

5. Design Procedure

In this section, a design procedure is presented using the

schematic in Figure 17 as a reference. An integrated

transformer with center tap, secondary side is used and

input is supplied from power factor correction (PFC) preregulator. A DC/DC converter with 192W/24V output has

been selected as a design example. The design

specifications are as follows:

requirement is given as:

Vin min VO. PFC 2

(13)

where VO.PFC is the nominal PFC output voltage, THU is a

hold-up time, and CDL is the DC link bulk capacitor.

- Nominal input voltage: 400VDC (output of PFC stage)

- Output: 24V/8A (192W)

- Hold-up time requirement: 20ms (50Hz line freq.)

- DC link capacitor of PFC output: 220F

(Design Example) Assuming the efficiency is 92%,

P

192

209W

Pin o

0.92

E ff

Vin max VO.PFC 400V

[STEP-1] Define the system specifications

Vin min VO. PFC 2

As a first step, define the following specification.

Estimated efficiency (Eff): The power conversion

efficiency must be estimated to calculate the maximum

input power with a given maximum output power. If no

reference data is available, use Eff = 0.88~0.92 for lowvoltage output applications and Eff = 0.92~0.96 for highvoltage output applications. With the estimated efficiency,

the maximum input power is given as:

Po

2 PinTHU

CDL

4002

2 PinTHU

CDL

2 209 20 103

349V

220 106

[STEP-2] Determine the Maximum and

Minimum Voltage Gains of the Resonant

Network

(12)

As discussed in the previous section, it is typical to operate

the LLC resonant converter around the resonant frequency

(fo) to minimize switching frequency variation. Since the

input of the LLC resonant converter is supplied from PFC

output voltage, the converter should be designed to operate

at fo for the nominal PFC output voltage.

Even though the input voltage is regulated as constant by

PFC pre-regulator, it drops during the hold-up time. The

minimum input voltage considering the hold-up time

As observed in Equation 10, the gain at fo is a function of

m (m=Lp/Lr). The gain at fo is determined by choosing that

value of m. While a higher peak gain can be obtained with

a small m value, too small m value results in poor coupling

Pin

E ff

(11)

Input voltage range (Vinmin and Vinmax): The maximum

input voltage would be the nominal PFC output voltage as:

Vin max VO.PFC

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

www.fairchildsemi.com

8

AN-4151

APPLICATION NOTE

of the transformer and deteriorates the efficiency. It is

typical to set m to be 3~7, which results in a voltage gain

of 1.1~1.2 at the resonant frequency (fo).

[STEP-4] Calculate the Equivalent Load

Resistance

With the transformer turns ratio obtained from Equation

16, the equivalent load resistance is obtained as:

With the chosen m value, the voltage gain for the nominal

PFC output voltage is obtained as:

min

m @f=f

o

m 1

Rac

(14)

Rac

The maximum voltage gain is given as:

8n 2 Vo 2 8 9.02 242

197

2 Po

2 192

[STEP-5] Design the Resonant Network

max

Vin

M min

min

Vin

With m value chosen in STEP-2, read proper Q value from

the peak gain curves in Figure 14 that allows enough peak

gain. Considering the load transient and stable zerovoltage-switching (ZVS) operation, 10~20% margin

should be introduced on the maximum gain when

determining the peak gain. Once the Q value is

determined, the resonant parameters are obtained as:

(15)

(Design Example) The ratio (m) between Lp and Lr is

chosen as 5. The minimum and maximum gains are

obtained as:

VRO

m

5

M min max

1.12

Vin

2

m 1

5 1

M max

1

2 Q f o Rac

1

Lr

(2 f o ) 2 Cr

Cr

max

V

400

in min M min

1.12 1.28

Vin

349

Gain (M)

1.28

MV

(20)

As calculated in STEP-2, the maximum voltage gain

(M max) for the minimum input voltage (Vinmin) is 1.28.

With 15% margin, a peak gain of 1.47 is required. m

has been chosen as 5 in STEP-2 and Q is obtained as

0.4 from the peak gain curves in Figure 19. By

selecting the resonant frequency as 100kHz, the

resonant components are determined as:

1

1

Cr

20.2nF

2 Q f o Rac 2 0.4 100 103 197

1

1

Lr

126 H

2

3 2

(2 f o ) Cr (2 100 10 ) 20.2 109

for Vinmax

( VO.PFC )

m

1.12

m 1

fo

(19)

(Design Example)

for Vinmin

1.12

Mmin

(18)

Lp m Lr

Peak gain (available maximum gain)

Mmax

(17)

(Design Example)

which would be the minimum gain because the nominal

PFC output voltage is the maximum input voltage (Vinmax).

M max

8n 2 Vo 2

2 Po

fs

Lp m Lr 630 H

Figure 18. Maximum Gain / Minimum Gain

1.7

1.6

[STEP-3] Determine the Transformer Turns

Ratio (n=Np/Ns)

1.5

Np

Vin max

n

M min

N s 2(Vo VF )

peak gain

With the minimum gain (Mmin) obtained in STEP-2, the

transformer turns ratio is given as:

(16)

1.3

1.2

where VF is the secondary-side rectifier diode voltage

drop.

m=6.0

m=9.0 m=8.0 m=7.0

1.1

m=4.0

m=4.5

m=5.0

(Design Example) assuming VF is 0.9V,

0.2

Np

Vin max

400

n

M min

1.12 9.00

N s 2(Vo VF )

2(24 0.9)

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

1.4

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.1

Figure 19. Resonant Network Design Using the Peak

Gain (Attainable Maximum Gain)

Curve for m=5

www.fairchildsemi.com

9

AN-4151

APPLICATION NOTE

[STEP-6] Design the Transformer

The worst case for the transformer design is the minimum

switching frequency condition, which occurs at the

minimum input voltage and full-load condition. To obtain

the minimum switching frequency, plot the gain curve

using gain Equation 9 and read the minimum switching

frequency. The minimum number of turns for the

transformer primary-side is obtained as:

N p min

n(Vo VF )

2 f s M V B Ae

(21)

min

where Ae is the cross-sectional area of the transformer core

in m2 and B is the maximum flux density swing in Tesla,

as shown in Figure 20. If there is no reference data, use

B =0.3~0.4 T. Notice that a virtual gain MV is introduced,

which is caused by the secondary-side leakage inductance

(Refer to Figure 8).

n (Vo+VF)/MV

VRI 1/(2fs)

[STEP-7] Transformer Construction

-n (Vo+VF)/MV

Figure 20. Flux Density Swing

Choose the proper number of turns for the secondary side

that results in primary-side turns larger than Npmin as:

N p n Ns N p

min

Figure 21. Gain Curve

Parameters Lp and Lr of the transformer were determined in

STEP-5. Lp and Lr can be measured in the primary side

with the secondary-side winding open circuited and short

circuited, respectively. Since LLC converter design

requires a relatively large Lr, a sectional bobbin is

typically used, as shown in Figure 22, to obtain the desired

Lr value. For a sectional bobbin, the number of turns and

winding configuration are the major factors determining

the value of Lr, while the gap length of the core does not

affect Lr much. Lp can be easily controlled by adjusting the

gap length. Table 2 shows measured Lp and Lr values with

different gap lengths. A gap length of 0.10mm obtains

values for Lp and Lr closest to the designed parameters.

Np

N s2

(22)

N s1

(Design Example) EER3542 core (Ae=107mm ) is

selected for the transformer. From the gain curve of

Figure 21, the minimum switching frequency is

obtained as 78kHz. The minimum primary-side turns

of the transformer is given as

N p min

n(Vo VF )

2 f s min B 1.12 Ae

Figure 22. Sectional Bobbin

9.0 24.9

30.4 turns

2 77 103 0.4 1.12 107 106

Table 2. Measured Lp and Lr with Different Gap Lengths

Choose Ns so that the resultant Np should be larger

than Npmin:

N p n N s 1 9.0 9 N p min

N p n N s 2 9.0 18 N p min

N p n N s 3 9.0 27 N p min

N p n N s 4 9.0 36 N p

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

Gap length

Lp

Lr

0.0mm

0.05mm

2,295H

943H

123H

122H

0.10mm

630H

118H

0.15mm

488H

117H

0.20mm

419H

115H

0.25mm

366H

114H

min

www.fairchildsemi.com

10

AN-4151

APPLICATION NOTE

(Design Example)

VCr nom

Final Resonant Network Design

Even though the integrated transformer approach in

LLC resonant converter design can implement the

magnetic components in a single core and save one

magnetic component, the value of Lr is not easy to

control in real transformer design. Resonant network

design sometimes requires iteration with a resultant Lr

value after the transformer is built. The resonant

capacitor value is also changed since it should be

selected among off-the-shelf capacitors. The final

resonant network design is summarized in Table 3

and the new gain curves are shown in Figure 23.

Vin max

2 I Cr RMS

2

2 f o Cr

(24)

However, the resonant capacitor voltage increases much

higher than this at overload condition or load transient.

Actual capacitor selection should be based on the OverCurrent Protection (OCP) trip point. With the OCP level,

IOCP, the maximum resonant capacitor voltage is obtained as:

VCr max

Vin max

I OCP

2

2 f S min Cr

(25)

The minimum switching frequency is used in the equation

because the frequency is typically forced to the minimum

value by the feedback loop when output is overloaded.

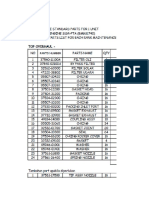

Table 3. Final Resonant Network Design Parameters

Parameters

Lp

Lr

Cr

fo

m

Q

Initial design

630H

126H

20nF

100kHz

5

0.4

Final design

630H

118H

22nF

99kHz

5.34

0.36

M@fo

Minimum freq

1.12

78kHz

1.11

72kHz

(Design Example)

I Cr RMS

1

E ff

Io

2 2n

]2 [

n(Vo VF )

]2

4 2 fo M V ( Lp Lr )

1

8 2

9.0 (24 0.9)

[

] [

]2

0.92 2 2 9.0

4 2 99 103 1.11 512 106

1.32 A

The peak current in the primary side in normal

operation is:

2.0

I Cr peak 2 I Cr rms 1.86 A

100% load

1.8

min

80% load

normal

60% load

OCP level is set to 3.0A with 50% margin on ICrpeak:

40% load

1.6

20% load

VCr nom

1.4

max

min

1.2

VCr max

0.8

0.6

50

60

70

80

90

100

110

120

400

2 1.32

336V

2

2 99 103 22 109

V max

I OCP

in

2

2 f S min Cr

1.0

40

Vin max

2 I Cr RMS

2

2 f o Cr

130

140

freq (kHz)

Figure 23. Gain Curve of the Final Resonant

Network Design

400

3

502V

2

2 72 103 22 109

630V rated low-ESR film capacitor is selected for the

resonant capacitor.

[STEP-8] Select the Resonant Capacitor

When choosing the resonant capacitor, the current rating

should be considered because a considerable amount of

current flows through the capacitor. The RMS current

through the resonant capacitor is given as:

I Cr RMS

1

E ff

Io 2

n(Vo VF )

] [

]2 (23)

2 2n

4 2 f o M V ( Lp Lr )

The nominal voltage of the resonant capacitor in normal

operation is given as:

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

[STEP-9] Rectifier Network Design

When the center tap winding is used in the transformer

secondary side, the diode voltage stress is twice the output

voltage expressed as:

VD 2(Vo VF )

(26)

The RMS value of the current flowing through each

rectifier diode is given as:

www.fairchildsemi.com

11

AN-4151

APPLICATION NOTE

I D RMS

f max (

(27)

Io

5.2k 4.68k

) 100(kHz )

Rmin

Rmax

Meanwhile, the ripple current flowing through output

capacitor is given as:

I Co RMS (

Io

2 2

)2 I o 2

2 8

8

LVcc

Rmax

I o RC

PLoss.Co ( I Co RMS )2 RC

stress of the rectifier diode are:

VD 2(Vo VF ) 2(24 0.9) 49.8

I o 6.28 A

4

The 100V/20A Schottky diode is selected for the

rectifier considering the voltage overshoot caused by

the stray inductance.

The RMS current of the output capacitor is:

Io

2 2

)2 I o 2

2 8

8

I o 3.857 A

When two electrolytic capacitors with ESR of 80m

are used in parallel, the output voltage ripple is given

as:

0.08

) 0.50V

Vo I o RC 8 (

2

2

2

The loss in electrolytic capacitors is:

PLoss.Co ( I Co

Control

IC

External S/S

SG

Soft-start: To prevent excessive inrush current and

overshoot of output voltage during start-up, increase the

voltage gain of the resonant converter progressively. Since

the voltage gain of the resonant converter is reversely

proportional to the switching frequency, the soft-start is

implemented by sweeping down the switching frequency

from an initial high frequency (f ISS) until the output

voltage is established as illustrated in Figure 25. The softstart circuit is made by connecting RC series network on

the RT pin as shown in Figure 24. FSFR-series also has an

internal soft-start for 3ms to reduce the current overshoot

during the initial cycles, which adds 40kHz to the initial

frequency of the external soft-start circuit, as shown in

Figure 25. The actual initial frequency of the soft-start is

given as:

f ISS (

5.2k 5.2k

) 100 40 (kHz ) (33)

Rmin

RSS

It is typical to set the initial frequency of soft-start (f ISS) as

2~3 times of the resonant frequency (fo).

The soft-start time is determined by the RC time constant:

) RC 3.857 0.04 0.60W

RMS 2

PG

Figure 24. Typical Circuit Configuration for RT Pin

(30)

(Design Example) The voltage stress and current

I Co RMS (

CSS

(29)

where RC is the effective series resistance (ESR) of the

output capacitor and the power dissipation is the output

capacitor is:

I D RMS

RSS

Rmin

The voltage ripple of the output capacitor is:

Vo

VDL

RT

(28)

Io

(32)

TSS 3 ~ 4 times of RSS CSS

(34)

fs

f ISS

[STEP-10] Control Circuit Configuration

Figure 24 shows the typical circuit configuration for RT pin

of FSFR-series, where the opto-coupler transistor is

connected to the RT pin to control the switching frequency.

The minimum switching frequency occurs when the optocoupler transistor is fully tuned off, which is given as:

Control loop

take over

3ms

5.2k

(31)

100(kHz )

Rmin

Assuming the saturation voltage of opto-coupler transistor is

0.2V, the maximum switching frequency is determined as:

f min

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

40kHz

3~4 times of RC time constant

time

Figure 25. Frequency Sweep of the Soft-start

www.fairchildsemi.com

12

AN-4151

APPLICATION NOTE

(Design Example) The minimum frequency is 72kHz

I DS

in STEP-6. Rmin is determined as:

Rmin

100 kHz

5.2k 7.2k

f min

VCS

Considering the output voltage overshoot during

transient (10%) and the controllability of the

feedback loop, the maximum frequency is set as

140kHz. Rmax is determined as:

Rmax

Cr

VCS

4.68k

f o 1.40 5.2k

(

)

100 kHz

Rmin

Np

CS

PG

SG

Rsense

4.68k

7.1k

99kHz 1.4 5.2k

(

)

100 kHz

7.2k

Ns

Ns

IDS

Figure 27. Full-wave Sensing

Setting the initial frequency of soft-start as 250kHz

(2.5 times of the resonant frequency), the soft-start

resistor RSS is given as:

RSS

Control

IC

(Design Example) Since the OCP level is

determined as 3A in STEP-8 and the OCP threshold

voltage is -0.6V, a sensing resistor of 0.2 is used.

The RC time constant is set to 100ns (1/100 of

switching period) with 1k resistor and 100pF

capacitor.

5.2k

f ISS 40kHz 5.2k

(

)

100kHz

Rmin

5.2k

3.8k

250kHz 40kHz 5.2k

(

)

100kHz

7.2k

[STEP-11] Current Sensing and Protection

FSFR-series senses low-side MOSFET drain current as a

negative voltage, as shown in Figure 26 and Figure 27.

Half-wave sensing allows low-power dissipation in the

sensing resistor, while full-wave sensing has less

switching noise in the sensing signal. Typically, RC lowpass filter is used to filter out the switching noise in the

sensing signal. The RC time constant of the low-pass filter

should be 1/100~1/20 of the switching period.

Cr

Np

Ns

Ns

Control

IC

VCS

I DS

CS

SG

PG

Rsense

IDS

VCS

Figure 26. Half-wave Sensing

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

www.fairchildsemi.com

13

AN-4151

APPLICATION NOTE

Design Summary

Figure 28 shows the final schematic of the LLC resonant half-bridge converter design example. EER3542 core with

sectional bobbin is used for the transformer. The efficiency at full load condition is around 94%.

D211

FYP2010DN

C102

22nF/

630V

JP1

10

Vcc

R106

27

LVcc

C105

22F/

50V

Vin=400Vdc

D101

1N4937

Np

R104

7.2k

Ns

R201

10k

C106

150nF

CON

R107

3.9k

Control

IC

R202

1k

R206

2k

U3

KA431

C102

100pF

R102

1k

SG

C204

12nF

R204

62k

D212

FYP2010DN

VCTR

CS

C101

220F/

450V

Vo

Ns

HVcc

C107

6.8F

C108

12nF

C202

2200F/

35V

VDL

RT

R105

7.2k

C201

2200F/

35V

C203

47nF

R203

33k

R205

7k

PG

R101

0.2

Figure 28. Final Schematic of Half-bridge LLC Resonant Converter

- Core: EER3542 (Ae=107 mm2)

- Bobbin: EER3542 (Horizontal/section type)

EER3542

1

16

Np

Np

Ns1

N s2

1

3

1

2

N s1

Ns2

8

Figure 29. Transformer Structure

Pin(S F)

Wire

Turns

Winding Method

Np

81

0.1230 (Litz wire)

36

Section winding

Ns1

16 13

0.1100 (Litz wire)

Section winding

Ns2

12 9

0.1100 (Litz wire)

Section winding

Pin

Specification

Remark

Primary-side Inductance (Lp)

18

630H 5%

Secondary windings open

100kHz, 1V

Equivalent Leakage Inductance (Lr)

18

118H Max.

Short one of the secondary windings

100kHz, 1V

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

www.fairchildsemi.com

14

AN-4151

APPLICATION NOTE

6. Experimental Verification

To show the validity of the design procedure presented in

this application note, the converter of the design example

has been built and tested. All the circuit components are

used as designed in the design example.

Figure 30 and Figure 31 show the operation waveforms at

full-load and no-load conditions for nominal input voltage.

As observed, the MOSFET drain-to-source voltage (VDS)

drops to zero by resonance before the MOSFET is turned

on and zero voltage switching is achieved.

Figure 32 shows the waveforms of the resonant capacitor

voltage and primary-side current at full load condition.

The peak values of the resonant capacitor voltage and

primary-side current are 325V and 1.93A, respectively,

which are well matched with the calculated values in

STEP-8 of design procedure section. Figure 33 shows the

waveforms of the resonant capacitor voltage and primaryside current at output short condition. For output short

condition, over current protection (OCP) is triggered when

the primary-side current exceeds 3A. The maximum

voltage of the resonant capacitor is a little bit higher than

the calculated value of 419V because the OCP trips at a

level little bit higher than 3A, due to the shutdown delay

time of 1.5s (refer to the FSFR2100 datasheet).

Figure 31. Operation Waveforms at No-load Condition

Figure 34 shows the rectifier diode voltage and current

waveforms at full-load and no-load conditions. Due to the

voltage overshoot caused by stray inductance, the voltage

stress is a little bit higher than the value calculated in

STEP-9. Figure 35 shows the output voltage ripple at fullload and no-load conditions. The output voltage ripple is

well matched with the designed value in STEP-9.

Figure 32. Resonant Capacitor Voltage and Primaryside Current Waveforms at Full-load Condition

Figure 36 shows the measured efficiency for different load

conditions. Efficiency at full-load condition is about 94%.

Figure 33. Resonant Capacitor Voltage and Primaryside Current Waveforms for Output Short Protection

Figure 30. Operation Waveforms at Full-load Condition

Figure 34. Rectifier Diode Voltage and Current

Waveforms at Full-load Condition

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

www.fairchildsemi.com

15

AN-4151

APPLICATION NOTE

Figure 35. Output Voltage Ripple and Primary-Side

Current Waveforms at Full-Load Condition

Figure 37. Measured Efficiency

Figure 36. Soft-start Waveforms

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

www.fairchildsemi.com

16

AN-4151

APPLICATION NOTE

7. References

[1] Robert L. Steigerwald, A Comparison of Half-bridge

resonant converter topologies, IEEE Transactions on

Power Electronics, Vol. 3, No. 2, April 1988.

[2] A. F. Witulski and R. W. Erickson, Design of the series

resonant converter for minimum stress, IEEE Transactions

on Aerosp. Electron. Syst., Vol. AES-22, pp. 356-363,

July 1986.

[3] R. Oruganti, J. Yang, and F.C. Lee, Implementation of

Optimal Trajectory Control of Series Resonant Converters,

Proc. IEEE PESC 87, 1987.

[4] V. Vorperian and S. Cuk, A Complete DC Analysis of the

Series Resonant Converter, Proc. IEEE PESC82, 1982.

[5] Y. G. Kang, A. K. Upadhyay, D. L. Stephens, Analysis and

design of a half-bridge parallel resonant converter operating

above resonance, IEEE Transactions on Industry

Applications Vol. 27, March-April 1991, pp. 386 395.

[6] R. Oruganti, J. Yang, and F.C. Lee, State Plane Analysis of

Parallel Resonant Converters, Proc. IEEE PESC 85, 1985.

[7] M. Emsermann, An Approximate Steady State and Small

Signal Analysis of the Parallel Resonant Converter Running

Above Resonance, Proc. Power Electronics and Variable

Speed Drives 91, 1991, pp. 9-14.

[8] Yan Liang, Wenduo Liu, Bing Lu, van Wyk, J.D, " Design

of integrated passive component for a 1 MHz 1 kW halfbridge LLC resonant converter", IAS 2005, pp. 2223-2228.

[9] B. Yang, F.C. Lee, M. Concannon, "Over current protection

methods for LLC resonant converter" APEC 2003, pp. 605 - 609.

[10] Yilei Gu, Zhengyu Lu, Lijun Hang, Zhaoming Qian,

Guisong Huang, "Three-level LLC series resonant DC/DC

converter" IEEE Transactions on Power Electronics Vol.20,

July 2005, pp.781 789.

[11] Bo Yang, Lee, F.C, A.J Zhang, Guisong Huang, "LLC

resonant converter for front end DC/DC conversion" APEC

2002. pp.1108 1112.

[12] Bing Lu, Wenduo Liu, Yan Liang, Fred C. Lee, Jacobus D.

Van Wyk, Optimal design methodology for LLC Resonant

Converter, APEC 2006. pp.533-538.

Author

Hangseok Choi, Ph. D

Strategic R&D / Fairchild Semiconductor

Email: hangseok.choi@fairchildsemi.com

Related Datasheets

FSFR2100 FSFR2100 for 450W - Fairchild Power Switch (FPS) for Half-Bridge Resonant Converters

Important Notice

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS

HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF

THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE

UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR

SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

CORPORATION.

As used herein:

1.

2.

Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body, or

(b) support or sustain life, or (c) whose failure to perform

when properly used in accordance with instructions for use

provided in the labeling, can be reasonably expected to

result in significant injury to the user.

2007 Fairchild Semiconductor Corporation

Rev. 1.0.1 5/15/12

A critical component is any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

17

Вам также может понравиться

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Рейтинг: 2.5 из 5 звезд2.5/5 (3)

- Self Oscillating Class-D Audio Amplifier Circuit DesignДокумент29 страницSelf Oscillating Class-D Audio Amplifier Circuit DesignnicchioОценок пока нет

- Wiring NSXДокумент9 страницWiring NSXAsepta Surya WardhanaОценок пока нет

- Switched Mode Power SupplyДокумент153 страницыSwitched Mode Power SupplyIvan222244Оценок пока нет

- Audio Handbook No.3 - The Use of Audio Frequency Transformers - Norman H. Crowhurst (1953) ClearscanДокумент66 страницAudio Handbook No.3 - The Use of Audio Frequency Transformers - Norman H. Crowhurst (1953) Clearscanjimmy67music100% (2)

- AN1114 - Switch Mode Power Supply (SMPS) Topologies (Part I) - MicrochipДокумент48 страницAN1114 - Switch Mode Power Supply (SMPS) Topologies (Part I) - MicrochipbmmostefaОценок пока нет

- An Introduction to Switched Mode Power Supply TopologiesДокумент21 страницаAn Introduction to Switched Mode Power Supply Topologiesseahate100% (1)

- 1000w Inverter PURE SINE WAVE Schematic DiagramДокумент153 страницы1000w Inverter PURE SINE WAVE Schematic Diagramjeevapillay100% (4)

- Microcontroller EMC Design Guidelines for PCB LayoutДокумент63 страницыMicrocontroller EMC Design Guidelines for PCB LayoutMr CdtОценок пока нет

- AN108A Inductive Load Arc SuppressionДокумент3 страницыAN108A Inductive Load Arc SuppressionihsanjuОценок пока нет

- Electrical Machine and Control II, EP-52014Документ33 страницыElectrical Machine and Control II, EP-52014Kyaw LayОценок пока нет

- EE201 Tutorial-7 Transformer 23sep19 PDFДокумент61 страницаEE201 Tutorial-7 Transformer 23sep19 PDFSrikarОценок пока нет

- Small LF loop antenna for direction finding radio stations 10-600 kHzДокумент4 страницыSmall LF loop antenna for direction finding radio stations 10-600 kHzsuanmdОценок пока нет

- Two-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingДокумент8 страницTwo-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingRakeshconclaveОценок пока нет

- FairchildДокумент17 страницFairchildshounakroyОценок пока нет

- Fairchild AnДокумент17 страницFairchild AnhvhОценок пока нет

- An-9067 LCC Failure ModeДокумент12 страницAn-9067 LCC Failure ModeRon HuangОценок пока нет

- Conference-201410-Shahzad-LLC Series Resonant Converter With PID Controller For Battery Charging ApplicationДокумент6 страницConference-201410-Shahzad-LLC Series Resonant Converter With PID Controller For Battery Charging ApplicationTocean DuongОценок пока нет

- Journal Jpe 7-1 1597982850Документ8 страницJournal Jpe 7-1 1597982850Lê Trần Bích HằngОценок пока нет

- Application Note AN-1160: Design of Resonant Half-Bridge Converter Using IRS2795 (1,2) Control ICДокумент32 страницыApplication Note AN-1160: Design of Resonant Half-Bridge Converter Using IRS2795 (1,2) Control ICcumshotОценок пока нет

- Prekidačka NapajanjaДокумент48 страницPrekidačka NapajanjaDamir PranjkovicОценок пока нет

- Switch Mode Power Supply (SMPS) Topologies (Part I) - MicrochipДокумент48 страницSwitch Mode Power Supply (SMPS) Topologies (Part I) - MicrochipGhulam AbbasОценок пока нет

- Current Ripple Factor of A Buck Converter: Application NoteДокумент5 страницCurrent Ripple Factor of A Buck Converter: Application Noteصدام حسینОценок пока нет

- ZvsДокумент29 страницZvsSandy RonaldoОценок пока нет

- ClampДокумент8 страницClampGaetano GaetanoОценок пока нет

- Design Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED LightingДокумент13 страницDesign Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED Lightingshiva1luОценок пока нет

- Power Harvester Design For Semi-Passive UHF RFID Tag Using A Tunable Impedance TransformationДокумент5 страницPower Harvester Design For Semi-Passive UHF RFID Tag Using A Tunable Impedance TransformationM AОценок пока нет

- An 1162Документ36 страницAn 1162naniknanikОценок пока нет

- Amplificadores RFДокумент20 страницAmplificadores RFpinocleОценок пока нет

- Speedam 2008 FINAL Mag IntДокумент9 страницSpeedam 2008 FINAL Mag IntbiswajitntpcОценок пока нет

- V/F Converter Ics Handle Frequency-To-Voltage Needs: The Art of CompromiseДокумент8 страницV/F Converter Ics Handle Frequency-To-Voltage Needs: The Art of CompromiseAlim SheikhОценок пока нет

- Leakage Flux TransformerДокумент5 страницLeakage Flux TransformerVishnu PillaiОценок пока нет

- LLC Resonant Converter Design GuideДокумент9 страницLLC Resonant Converter Design GuideBOLFRAОценок пока нет

- Class E Amp Design PDFДокумент12 страницClass E Amp Design PDFAshutoshSharmaОценок пока нет

- Design Considerations for Asymmetric Half-Bridge ConvertersДокумент16 страницDesign Considerations for Asymmetric Half-Bridge ConvertersGuilhermeFerreiraОценок пока нет

- Design of Zeta Converter Based Electronic Ballast For Fluorescent LampsДокумент7 страницDesign of Zeta Converter Based Electronic Ballast For Fluorescent LampscamiloОценок пока нет

- BMECEE 307 - ELECTRICAL AND ELECTRONICS TECHNOLOGYДокумент5 страницBMECEE 307 - ELECTRICAL AND ELECTRONICS TECHNOLOGYashwen30Оценок пока нет

- Bi-Frequency Control of Auxiliary Resonant Snubber For Forward Converter Using Pic ControllerДокумент5 страницBi-Frequency Control of Auxiliary Resonant Snubber For Forward Converter Using Pic ControllerNithinОценок пока нет

- Centre Tapped Transformer SpecificationsДокумент4 страницыCentre Tapped Transformer SpecificationsALNATRON GROUPSОценок пока нет

- Decentralized Control Strategy For Input-Series-Output-Parallel Modular LLC Resonant DC/DC ConvertersДокумент5 страницDecentralized Control Strategy For Input-Series-Output-Parallel Modular LLC Resonant DC/DC ConvertersRaja ReddyОценок пока нет

- High Power Factor Soft SwitchedДокумент7 страницHigh Power Factor Soft SwitchedMohan KrishnaОценок пока нет

- Sideband Emission (ISB) and Is Treated Fully in Section 4-4.3. It Is Used For HFДокумент6 страницSideband Emission (ISB) and Is Treated Fully in Section 4-4.3. It Is Used For HFचौकीदार गोपाल भार्गवОценок пока нет

- Am DSBFC Systems (By Larry E. Gugle K4rfe)Документ9 страницAm DSBFC Systems (By Larry E. Gugle K4rfe)rascalangelОценок пока нет

- Single Phase Reduced Order Ac-Ac Resonant - Frequency ConverterДокумент10 страницSingle Phase Reduced Order Ac-Ac Resonant - Frequency ConverterIJAR JOURNALОценок пока нет

- Transformer Design Consideration For Off Line Flyback Converters Using Fairchild Power Switch (FPS™)Документ10 страницTransformer Design Consideration For Off Line Flyback Converters Using Fairchild Power Switch (FPS™)StefanvnvОценок пока нет

- basic dc to dcДокумент36 страницbasic dc to dcstrelectronicsОценок пока нет

- CLC103, CLC200, CLC206, CLC400, CLC401, CLC425: OA-11 A Tutorial On Applying Op Amps To RF ApplicationsДокумент24 страницыCLC103, CLC200, CLC206, CLC400, CLC401, CLC425: OA-11 A Tutorial On Applying Op Amps To RF ApplicationsTelemetroОценок пока нет

- A Reactance ModulatorДокумент17 страницA Reactance ModulatorAldrin Sagum100% (1)

- ZVSДокумент28 страницZVS12BACAUОценок пока нет

- Bridgeless PFCДокумент18 страницBridgeless PFCsolid690Оценок пока нет

- How To Measure RF TransformersДокумент16 страницHow To Measure RF Transformersعلاء الليبيОценок пока нет

- An 7517Документ9 страницAn 7517MallickarjunaОценок пока нет

- Operation of the LCC-Type Parallel Resonant Converter as a Low Harmonic RectifierДокумент12 страницOperation of the LCC-Type Parallel Resonant Converter as a Low Harmonic RectifierJie99Оценок пока нет

- Implementation and Simulation of Half Bridge Series Resonant Inverter in Zero Voltage SwitchingДокумент5 страницImplementation and Simulation of Half Bridge Series Resonant Inverter in Zero Voltage Switchingwhite_lonelinessОценок пока нет

- Transformer and Inductor Design Handbook Chapter 16Документ13 страницTransformer and Inductor Design Handbook Chapter 16aysandeepОценок пока нет

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsОт EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsОценок пока нет

- Deep Cycle Gel RangeДокумент9 страницDeep Cycle Gel RangeihsanjuОценок пока нет

- MultiPlus inverter/charger provides powerful backup and battery chargingДокумент2 страницыMultiPlus inverter/charger provides powerful backup and battery chargingihsanjuОценок пока нет

- SLD 200MPD PDFДокумент1 страницаSLD 200MPD PDFihsanjuОценок пока нет

- G D G D: New Datasheet Database - Now Searching 1000+ Scanned Data BooksДокумент1 страницаG D G D: New Datasheet Database - Now Searching 1000+ Scanned Data BooksihsanjuОценок пока нет

- LV429434 Datasheet PDFДокумент2 страницыLV429434 Datasheet PDFihsanjuОценок пока нет

- LV429434 motor mechanism data sheetДокумент2 страницыLV429434 motor mechanism data sheetihsanjuОценок пока нет

- 20 Kva Perkins Meccalte Acoustic Diesel Generator: DimensionsДокумент2 страницы20 Kva Perkins Meccalte Acoustic Diesel Generator: DimensionsihsanjuОценок пока нет

- Manual Hd-Cvi Tvi AhdДокумент2 страницыManual Hd-Cvi Tvi AhdihsanjuОценок пока нет

- Batre Lithium PDFДокумент1 страницаBatre Lithium PDFihsanjuОценок пока нет

- SR4850 Rectifier DatasheetДокумент9 страницSR4850 Rectifier DatasheetihsanjuОценок пока нет

- Exhaust System GuideДокумент6 страницExhaust System GuideihsanjuОценок пока нет

- Spec Sheet M4860P2SДокумент1 страницаSpec Sheet M4860P2SihsanjuОценок пока нет

- Batre LithiumДокумент7 страницBatre LithiumihsanjuОценок пока нет

- Everlight Electronics Co., LTD.: Device Number: DHI-092-003 Rev: 1.0 Model No: HI400 Ecn: 1/6Документ6 страницEverlight Electronics Co., LTD.: Device Number: DHI-092-003 Rev: 1.0 Model No: HI400 Ecn: 1/6ihsanjuОценок пока нет

- 2SC4139Документ5 страниц2SC4139ihsanjuОценок пока нет

- Footprint Solar Support 1 KWДокумент1 страницаFootprint Solar Support 1 KWihsanjuОценок пока нет

- Maintenanace PartДокумент1 страницаMaintenanace PartihsanjuОценок пока нет

- Silicon N-Channel MOS FET: ApplicationДокумент5 страницSilicon N-Channel MOS FET: ApplicationihsanjuОценок пока нет

- Quantum SMR3000W SpecsДокумент6 страницQuantum SMR3000W Specsihsanju100% (1)

- FASTRON TECHNO 10W-40 API SN Engine OilДокумент2 страницыFASTRON TECHNO 10W-40 API SN Engine OilihsanjuОценок пока нет

- BT168GWFДокумент14 страницBT168GWFihsanjuОценок пока нет

- 1093100Документ1 страница1093100ihsanjuОценок пока нет

- 2SC4139Документ5 страниц2SC4139ihsanjuОценок пока нет

- BT151 500R PDFДокумент11 страницBT151 500R PDFKristell SolisОценок пока нет

- FGH60N60SMDДокумент10 страницFGH60N60SMDihsanjuОценок пока нет

- Nu Data EngДокумент8 страницNu Data EngihsanjuОценок пока нет

- Higher Algebra - Hall & KnightДокумент593 страницыHigher Algebra - Hall & KnightRam Gollamudi100% (2)

- Choosing An AC or DC Coil For A Solenoid Valve - Tameson PDFДокумент4 страницыChoosing An AC or DC Coil For A Solenoid Valve - Tameson PDFeakonakosОценок пока нет

- Physics Chapter 23 SolutionsДокумент15 страницPhysics Chapter 23 Solutionsalkalkindin119284849Оценок пока нет

- PPTДокумент7 страницPPTanupnaskar naskarОценок пока нет

- DC motor speed control using magnetic amplifierДокумент8 страницDC motor speed control using magnetic amplifierNexus GoddОценок пока нет

- BTechSyllabus EC PDFДокумент140 страницBTechSyllabus EC PDFHHОценок пока нет

- Power Stage Designer™: User's GuideДокумент29 страницPower Stage Designer™: User's GuideChiến TrầnОценок пока нет

- 8 Alternating-Currentexericse PDFДокумент51 страница8 Alternating-Currentexericse PDFIndranilОценок пока нет

- Lecture 5 (Chaptr 3)Документ58 страницLecture 5 (Chaptr 3)Eti'el Films / ኢትኤል ፊልሞችОценок пока нет

- Lecture 2Документ26 страницLecture 2Ano Ni MousОценок пока нет

- Translation Radio Direction Finding PDFДокумент73 страницыTranslation Radio Direction Finding PDFKevin WoodОценок пока нет

- Infineon-Design Guide Boost Type CCM PFC ICE3PCSxx-AN-v02 00-EN PDFДокумент26 страницInfineon-Design Guide Boost Type CCM PFC ICE3PCSxx-AN-v02 00-EN PDFThai Anh NguyenОценок пока нет

- Electrical Machines Lab Project Proposal: Objective: Mutual Induction PrincipleДокумент2 страницыElectrical Machines Lab Project Proposal: Objective: Mutual Induction PrincipleMuhammad HuzaifaОценок пока нет

- Nonlinear Model & Controller Design For Magnetic Levitation SystemДокумент6 страницNonlinear Model & Controller Design For Magnetic Levitation SystemHoàng GiangОценок пока нет

- Lecture Planner - Physics - LAKSHYA JEE 2022 PLANNER - PhysicsДокумент7 страницLecture Planner - Physics - LAKSHYA JEE 2022 PLANNER - PhysicsprekshaОценок пока нет

- Eddy Current Brake (PDFDrive)Документ146 страницEddy Current Brake (PDFDrive)AlejandroОценок пока нет

- Ieee 90Документ7 страницIeee 90Junior Pucuhuanca SullcaОценок пока нет

- T200 2 DataSheet PDFДокумент1 страницаT200 2 DataSheet PDFJose DanielОценок пока нет

- Permanent Magnet Synchronous Machine ModelДокумент4 страницыPermanent Magnet Synchronous Machine ModelJulian De MarcosОценок пока нет

- De ApplicationsFirstOrderДокумент58 страницDe ApplicationsFirstOrderMerv Derek CamadoОценок пока нет

- Principles of Electromechanical Energy ConversionДокумент77 страницPrinciples of Electromechanical Energy Conversionanil1216kumar50% (2)

- Designing a Simple High-Voltage SMPSДокумент31 страницаDesigning a Simple High-Voltage SMPSLuiz Clemente PimentaОценок пока нет

- Model-Based Current Control of AC Machines Using IMCДокумент9 страницModel-Based Current Control of AC Machines Using IMCJoel ParrОценок пока нет

- SNVA761Документ18 страницSNVA761bookreader1968Оценок пока нет

- Experiment 4 AC Measurents RC A RL Ckts 210330Документ7 страницExperiment 4 AC Measurents RC A RL Ckts 210330MK MillyОценок пока нет