Академический Документы

Профессиональный Документы

Культура Документы

Guia 5 Ctos II

Загружено:

Hector ValdiviaОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Guia 5 Ctos II

Загружено:

Hector ValdiviaАвторское право:

Доступные форматы

UNIVERSIDAD PARTICULAR CATLICA DE SANTA MARA DE AREQUIPA

PROGRAMA PROFESIONAL DE INGENIERA MECANICA, MECANICA ELECTRICA Y

MECATRONICA

CDIGO:

ASIGNATURA:

4E06035

CIRCUITOS ELECTRONICOS II

SEGUNDA FASE: LOGICA SECUENCIAL

CIRCUITOS SECUENCIALES

GUA DE LABORATORIO NRO 05

Docente(s):

Ing. RONALD P. COAGUILA

GMEZ

Fecha: 2011.09.12.

I. OBJETIVO:

Analizar las caractersticas electrnicas de un circuito SECUENCIAL

II. MARCO TEORICO

A diferencia de los sistemas combinacionales, en los sistemas secuenciales, los valores de las

salidas, en un momento dado, no dependen exclusivamente de los valores de las entradas en

dicho momento, sino tambin dependen del estado anterior o estado interno. El sistema

secuencial ms simple es el biestable, de los cuales, el de tipo D (o cerrojo) es el ms utilizado

actualmente.

La mayora de los sistemas secuenciales estn gobernados por seales de reloj. A stos se los

denomina "sncronos" o "sincrnicos", a diferencia de los "asncronos" o "asincrnicos" que son

aquellos que no son controlados por seales de reloj.

A continuacin se indican los principales sistemas secuenciales que pueden encontrarse en forma

de circuito integrado o como estructuras en sistemas programados:

Contador

Registros

En todo sistema secuencial nos encontraremos con:

a) Un conjunto finito, n, de variables de entrada (X1, X2,..., Xn).

b) Un conjunto finito, m, de estados internos, de aqu que los estados secuenciales

tambin sean denominados autmatas finitos. Estos estados proporcionarn m variables

internas (Y1,Y2,..., Ym).

c) Un conjunto finito, p, de funciones de salida (Z1, Z2,..., Zp).

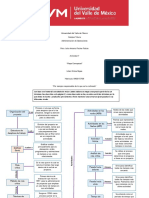

Dependiendo de como se obtengan las funciones de salida, Z, los sistemas secuenciales pueden

tener dos estructuras como las que se observan el la siguiente figura, denominadas Mquina de

Moore, a), y Mquina de Mealy, b).

Laboratorio de Circuitos Electrnicos II - PPIMMEYM

III.

Sexto Semestre UCSM

2011

INFORME PREVIO:

a) Analizar y sealar las caractersticas elctricas y electrnicas de los CI FF: 74LS76,

74LS74, 74LS73, 74LS168, 74LS374, 74LS90, 74LS92, 74LS193, 74LS196, en base a las

hojas de datos.

b) Explicar brevemente los tipos de CI FF y Contadores que operan como Flip-Flop y

Contadores.

c) Explicar las diferencias internas y de Ambos CI: 74LS90, 74LS193

d) Como se obtiene los FF RS y T , ya que no existen CI para estos FF. Hacer los diagramas

equivalentes

e) Sealar y explicar los diferentes tipos de Contadores que se usan para las funciones de

reloj, RPM, tacometro, etc

f) Disear un contador en anillo de 4 estados en base a FF JK y compuertas TTL

IV. MATERIAL Y EQUIPO:

- Fuentes de Almentacin.

- 01 Osciloscopio

- Multmetros

- CI . TTL: 74LS76 (dos unidades) , 74LS168, 74LS47, 74LS193 (dos unidades)

- Timer LM555 , - 4 Dip switch de 4 y 8 contactos - Resistencias (por lo menos cuatro cada

tipo): 220, 330, 560, 1 Kohm - Un display nodo comn y un display ctodo comn

- 10 Leds de colores variados

- Protoboard, cables de conexin

V. PROCEDIMIENTO

1.- Implementar el circuito diseado en el item F del informe previo

2.-Implementar el siguiente circuito 2, anotar las caractersticas de comportamiento del

contador. Probar con todas las alternativas del dip switch .

Nota: El display tiene que ser implementado con su decodificador correspondiente 7447

Circuito 2

2.- Realizar la implementacin del circuito 3 , teniendo en cuenta las especificaciones sgtes:

Ing. Ronald Coaguila Gmez

Arequipa

2011

Laboratorio de Circuitos Electrnicos II - PPIMMEYM

Sexto Semestre UCSM

2011

Contador ascendente/descendente preiniciable 74193. a) Smbolo lgico, b) Descripcin entrada/salida

y c) Tabla de seleccin de modos.

Circuito 3. Contador binario de 0 a 255

Observar el conteo binario ascendente en los 8 LED., anotar

Realizar las conexiones necesarias para que el conteo binario sea descendente (de 255 a

0)

Ing. Ronald Coaguila Gmez

Arequipa

2011

Laboratorio de Circuitos Electrnicos II - PPIMMEYM

Sexto Semestre UCSM

2011

VI. INFORME FINAL:

1) Fundamentar cmo funciona el primer circuito2 del procedimiento.

2) Fundamentar cmo funciona el ultimo circuito del procedimiento

Qu sucede al aumentar la resistencia en el preset?

Qu sucede al disminuir la resistencia en el preset?

Cul es la cantidad mxima que aparece en los exhibidores (display)?

3) Respecto al contador de CI : 74193

Qu utilidad tienen las entradas preiniciables?

Qu relacin tienen CPU y TC'D?

Qu relacin tienen CPD y TC'D?

Qu relacin tienen CPU y TC'D?

Qu utilidades se le puede dar a este contador? Mencionar tres de ellas.

4) Que caractersticas debe tener el circuito de clock. Que caractersticas de pulso son

recomendables para el buen sincronismo con toso el sistema secuencial.

VII.

CONCLUSIONES Y OBSERVACIONES

Enunciar sus conclusiones y observaciones de la experiencia

VIII.

BIBLIOGRAFIA:

Tocci Ronald: SISTEMAS DIGITALES PRINCIPIOS Y APLICACIONES. Prentice Hall 2002 Mxico

M.Morris Mano : DISEO DIGITAL Pearson Educacin 2003 Mxico

Floyd Tomas L.: FUNDAMENTOS DE ELECTRONICA DIGITAL Edit. Mac.Graw Hill Mxico 2005

Wakerly Jhon F.: DISEO DIGITAL PRINCIPIOS Y PRACTICAS Marcombo 2005 Mxico

http://electronica.ugr.es/~amroldan/asignaturas/curso04-05/ftc/pdf/trab_familia_cmos.pdf

http://es.wikipedia.org/wiki/Archivo:AutomataMooreMealy.PNG

TIEMPO : 1 sesin de laboratorio

Ing. Ronald Coaguila Gmez

RPCG 10-2011

Arequipa

2011

Вам также может понравиться

- Arreglos en SwiftДокумент2 страницыArreglos en SwiftHector ValdiviaОценок пока нет

- Tablas de SoldaduraДокумент9 страницTablas de SoldaduraHector ValdiviaОценок пока нет

- Cap 3a Uniones SoldadasДокумент22 страницыCap 3a Uniones SoldadasHector ValdiviaОценок пока нет

- Experiencia #5Документ18 страницExperiencia #5Hector ValdiviaОценок пока нет

- Evaluación de Lineas de TransmisiónДокумент1 страницаEvaluación de Lineas de TransmisiónHector ValdiviaОценок пока нет

- Problemas Sobre Sistemas de Bombeo Fluidos IIДокумент7 страницProblemas Sobre Sistemas de Bombeo Fluidos IIHector ValdiviaОценок пока нет

- Contadores y MemoriasДокумент26 страницContadores y MemoriasHector ValdiviaОценок пока нет

- Rele A DistanciaДокумент56 страницRele A DistanciaHector ValdiviaОценок пока нет

- Memorias SemiconductorasДокумент23 страницыMemorias SemiconductorasHector Valdivia0% (1)

- Dokumen Verificacion-Viga-Debil-Columna-Fuerte-Etabs PDFДокумент11 страницDokumen Verificacion-Viga-Debil-Columna-Fuerte-Etabs PDFJulian ParraОценок пока нет

- 01 Introduction To GCP Es-419 PDFДокумент19 страниц01 Introduction To GCP Es-419 PDFVictor Hugo MoralesОценок пока нет

- Informes de Laboratorio Química - Unidad 1Документ32 страницыInformes de Laboratorio Química - Unidad 1Farid Augusto Daza MalaverОценок пока нет

- Construcción de Un PiqueДокумент25 страницConstrucción de Un PiqueYemer MaucaylleОценок пока нет

- Perdidas de Calor en Un Secador de Bandejas PDFДокумент36 страницPerdidas de Calor en Un Secador de Bandejas PDFPaoiittaaSteffyОценок пока нет

- Avance Ventiladores y CompresoresДокумент2 страницыAvance Ventiladores y CompresoresEduard GiancarlommОценок пока нет

- Examen de Fisica 9-2Документ1 страницаExamen de Fisica 9-2JERSY PAOLA DIAZ ESCOBARОценок пока нет

- A7 LorДокумент4 страницыA7 LorLiliánn ReyesОценок пока нет

- Componentes Estructurales de Las AeronavesДокумент10 страницComponentes Estructurales de Las AeronavesAndres Felipe Ospino CatañoОценок пока нет

- Ejercicios Dinámica RotacionalДокумент2 страницыEjercicios Dinámica RotacionalJavier David Ruiz GutierrezОценок пока нет

- Cultivos CelularesДокумент14 страницCultivos CelularesSsergioArmataMedinaОценок пока нет

- Mediafire (Como Subir Archivos)Документ5 страницMediafire (Como Subir Archivos)RJGuerreroОценок пока нет

- Solidificacion y AleacionДокумент18 страницSolidificacion y Aleacionshirley levano davilaОценок пока нет

- Tesis Cedeño LuqueДокумент104 страницыTesis Cedeño LuquespeОценок пока нет

- Junio (Problema)Документ6 страницJunio (Problema)Laura Encinas EscobarОценок пока нет

- MacromoleculasДокумент5 страницMacromoleculasClaudia Patricia Paredes GonzalezОценок пока нет

- Empaquetadura Enfriador Aceite MotorДокумент2 страницыEmpaquetadura Enfriador Aceite MotorhenotharenasОценок пока нет

- Apunte Condiciones de Link IBM 370Документ17 страницApunte Condiciones de Link IBM 370SebasFIUBAОценок пока нет

- Exposición SISTEMA DE ECUACIONES NO LINEALESДокумент5 страницExposición SISTEMA DE ECUACIONES NO LINEALESNadia Cruz SantiagoОценок пока нет

- Instalaciones HidraulicasДокумент18 страницInstalaciones HidraulicasFrancia Blue skyОценок пока нет

- Manual de Instalacion F2 64 BitsДокумент15 страницManual de Instalacion F2 64 BitsyokelitoОценок пока нет

- Seis SigmaДокумент21 страницаSeis SigmaJulian GonzalezОценок пока нет

- Unidad 1 TEMAДокумент44 страницыUnidad 1 TEMAAndrea MedranoОценок пока нет

- 19 Detalles Mecanismo de ValvulasДокумент2 страницы19 Detalles Mecanismo de ValvulasMarcot TomayllahОценок пока нет

- DISPOSITIVOS PERIFERICOS ResumidoДокумент2 страницыDISPOSITIVOS PERIFERICOS Resumidorudy_batenОценок пока нет

- 01 - Acople Elastico AДокумент12 страниц01 - Acople Elastico AAnonymous 52DDvGtvОценок пока нет

- Práctica de Monitorización Con EasyIDSДокумент6 страницPráctica de Monitorización Con EasyIDShilbert69Оценок пока нет

- Actividades PDFДокумент0 страницActividades PDFVictor Manuel Villafuerte PeñaОценок пока нет

- Función Del Depósito o Tanque HidráulicoДокумент2 страницыFunción Del Depósito o Tanque HidráulicoPatricio Sabetta0% (1)

- Informe-Final-De-Simulacion - Produccion de Butadieno 01Документ98 страницInforme-Final-De-Simulacion - Produccion de Butadieno 01CRISTHIAN NUÑEZ LIMACHE100% (1)