Академический Документы

Профессиональный Документы

Культура Документы

Final Project

Загружено:

BOBАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Final Project

Загружено:

BOBАвторское право:

Доступные форматы

Oct.

26, 2016

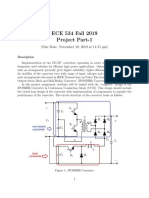

ECEN 325

Final Project

Instructor: Sebastian Hoyos

This project must be tested in the laboratory, with a working design shown to the TA or

instructor. Single person or groups of 2 are allowed, no groups of 3 or more.

Design a three-stage amplifier with Bipolar and CMOS transistors to satisfy the following constraints. Note,

the design should use standard value resistors (no potentiometers).

AV 50

Rin 200k

3 dB Bandwidth > 200kHz

Harmonic distortion below -30dB with vimax = 5mVpk (10mVpp) measured at 10kHz input sine signal

VCC = minimum required, but absolute max=5V

Rload = 8. Note, you may have to use multiple transistors in parallel in the output stage to drive

this load. Check the power ratings of the transistors.

Use a minimum of 3 MOSFETs in your design. Note, if desired you can use more and also BJTS,

but the intent is the MOSFETs are a key part of your design.

Your report should describe the design procedure stage-by-stage, beginning with the output stage. Use the

graphical approach outlined in class to choose initial bias points for all stages.

Provide sufficient theoretical and quantitative justification on the VCC choice. Try to optimize VCC on

a per-stage basis to achieve the lowest power.

Both the preliminary and final report should include the following simulation results:

DC operating points (voltages & currents) for each stage

AC Plots from 100Hz to 100kHz: AV, Rin

Transient plot of output signal with input 10kHz sine wave of 5mV amplitude

Frequency domain plot of above transient which shows the harmonic distortion. Note, to verify

the -30dB harmonic distortion spec, the harmonic distortion for a given harmonic is the ratio of the

harmonic power over the fundamental power.

Include the text output of the Fourier Analysis which states the Total Harmonic Distortion (THD).

Total power dissipation

The report should include the following measurement results:

Bode plot showing the amplifier gain. Note, you may have to scale the plot to account for the input

voltage divider.

Rin measurement

Transient plot of output signal with input 10kHz sine wave of 5mV amplitude

Frequency domain plot of above transient which shows the harmonic distortion.

Important Dates

Nov. 21

Preliminary Report Due*. Email your lab TA your report by

10AM.

Nov. 21-Nov. 25

Dedicated lab time (need TA coordination) to complete design and get

results for the report

Nov. 28

Project Report Due*. Email your lab TA your report by

10AM.

Nov. 28-Dec. 2

Project demonstrations in lab. Note, be prepared to answer questions

over your design.

Dec. 6th

5 minute presentations with testing results. Send by email Power-Point

presentation to Prof. Hoyos by Dec. 7, 5PM.

*Note the design should be finalized by Nov. 28 when you turn in the report. The demonstration on Nov.

28 Dec. 2 is to verify the design that you have in the report. The 5 min presentation is to further discuss

the results. I suggest investing in your own breadboard, such that you dont have to reconstruct the circuit

every time you go to the lab.

Project Grading*

Preliminary Report

20%

Lab Performance

30%

Report**

50%

*Note that all components are necessary to get any credit for the project

**The final report should be a comprehensive professional document. The report must include a

summary of the key specifications, a discussion of the architecture, and a detailed design procedure. In

addition to the measured results discussed earlier, a summary table of specifications, simulated, and

measured results is required.

Extra Credit Opportunities (Up to an additional 20%)

Use an advanced technique

o Darlington pair, Boot-Strapped Follower, etc

Use a MOSFET stage

Best measured performance while meeting all specifications

o Highest Gain, Best Distortion, Lowest Power, Best Overall

Вам также может понравиться

- EEE 52: Electronic Circuits Laboratory I Project: Multi-Stage Amplifier With Adjustable GainДокумент3 страницыEEE 52: Electronic Circuits Laboratory I Project: Multi-Stage Amplifier With Adjustable GainJaniessy ZozobradoОценок пока нет

- 2310 Lab3Документ2 страницы2310 Lab3tarottaurus54Оценок пока нет

- Lab3.Design Project - Ee140.s12.v1Документ4 страницыLab3.Design Project - Ee140.s12.v1frankongОценок пока нет

- Two StageДокумент6 страницTwo StageSiphosethuSidloyiОценок пока нет

- ECE 5540 Homework 2 - AlДокумент8 страницECE 5540 Homework 2 - AltrimcaoОценок пока нет

- Design Project: (Due: Friday, December 8, 2006, 5pm PT)Документ6 страницDesign Project: (Due: Friday, December 8, 2006, 5pm PT)Ibrahim MuhammedОценок пока нет

- Final Project (1) of PowerДокумент2 страницыFinal Project (1) of PowerLea Jean ConsigoОценок пока нет

- EE 342 Design Project I: DescriptionДокумент1 страницаEE 342 Design Project I: DescriptionLucas GodoiОценок пока нет

- EE477L-Final Project Phase 3Документ3 страницыEE477L-Final Project Phase 3Amandeep VaishОценок пока нет

- EE240 Proj2Документ2 страницыEE240 Proj2SaliiKiruosiОценок пока нет

- HomeworkДокумент4 страницыHomework1dmsrufОценок пока нет

- Receiver AssignmentДокумент8 страницReceiver AssignmentMilupa7Оценок пока нет

- EAT238 Control and Instrumentation Lab 1: Differential Amplifier Laboratory ExperimentДокумент2 страницыEAT238 Control and Instrumentation Lab 1: Differential Amplifier Laboratory ExperimentJackKulchОценок пока нет

- E0007e Lab1Документ7 страницE0007e Lab1fabianmozart16Оценок пока нет

- Course: Electronic Circuit Design Lab No: 10 Title: CMOS Amplifier Design CID: - DateДокумент4 страницыCourse: Electronic Circuit Design Lab No: 10 Title: CMOS Amplifier Design CID: - DateAamir ChohanОценок пока нет

- You Should Try To MinimizeДокумент5 страницYou Should Try To MinimizeSunwoo LeeОценок пока нет

- Lab1 Ee140 s13 v1Документ6 страницLab1 Ee140 s13 v1Mohd YasirОценок пока нет

- ECE 534 Project 1 F19Документ6 страницECE 534 Project 1 F19JAY CHHEDAОценок пока нет

- ADVD Analog Assignment - 2023ssДокумент36 страницADVD Analog Assignment - 2023ssNimit JainОценок пока нет

- Applied Analogue Electronics QuestionsДокумент5 страницApplied Analogue Electronics QuestionsKerera DeograciousОценок пока нет

- Assignment 1 Computer-Aided Design of Analog Circuits: InstructionsДокумент4 страницыAssignment 1 Computer-Aided Design of Analog Circuits: Instructionsabhishek raoОценок пока нет

- TH ND 0: Late Assignments Are NOT Accepted Copied Reports Are Assigned A 0 GradeДокумент2 страницыTH ND 0: Late Assignments Are NOT Accepted Copied Reports Are Assigned A 0 GradejulioОценок пока нет

- TH ND 0: Late Assignments Are NOT Accepted Copied Reports Are Assigned A 0 GradeДокумент2 страницыTH ND 0: Late Assignments Are NOT Accepted Copied Reports Are Assigned A 0 GradejulioОценок пока нет

- ECE100 Lab 2Документ3 страницыECE100 Lab 2Ahmed HamoudaОценок пока нет

- 442 Revised Lab Manual w07Документ51 страница442 Revised Lab Manual w07srinu247Оценок пока нет

- Design 1 - Hw1Документ1 страницаDesign 1 - Hw1Devleena GhoshОценок пока нет

- Isscc2022 000002CLДокумент16 страницIsscc2022 000002CLdashuai huaОценок пока нет

- LAB3 Design of Differential LNAДокумент4 страницыLAB3 Design of Differential LNAMichael GrahamОценок пока нет

- Lab 5Документ8 страницLab 5Rekha YadavОценок пока нет

- HW 2Документ1 страницаHW 2KypiОценок пока нет

- Systematic Design of A 200 MSs 8-Bit Interpolating AD ConverterДокумент5 страницSystematic Design of A 200 MSs 8-Bit Interpolating AD ConverterThanos van RamОценок пока нет

- EE 230 - Analog Circuits Lab - 2021-22/I (Autumn) Experiment 1: Familiarization With NGSPICE Circuit Simulator and Lab EquipmentДокумент7 страницEE 230 - Analog Circuits Lab - 2021-22/I (Autumn) Experiment 1: Familiarization With NGSPICE Circuit Simulator and Lab EquipmentTanmay JainОценок пока нет

- Isscc2022 000046CLДокумент16 страницIsscc2022 000046CLdashuai huaОценок пока нет

- Lab 1:introduction To Signals, Passive RC Filters and OpampsДокумент7 страницLab 1:introduction To Signals, Passive RC Filters and Opampsmrcinek01Оценок пока нет

- Class AbДокумент7 страницClass Abdemos2011Оценок пока нет

- 5-Band Graphic Equalizer: EE 410 Final Linear Electronic Design Spring 2008Документ13 страниц5-Band Graphic Equalizer: EE 410 Final Linear Electronic Design Spring 2008Zeeshan JohnОценок пока нет

- ExamДокумент13 страницExamHamed GhanbariОценок пока нет

- Birla Institute of Technology and Science Pilani, Pilani Campus (Raj.)Документ3 страницыBirla Institute of Technology and Science Pilani, Pilani Campus (Raj.)Arihant JainОценок пока нет

- Equency Response of A Common-Emitter BJT AmplifierДокумент5 страницEquency Response of A Common-Emitter BJT AmplifierThomas SmithОценок пока нет

- EEE3602 AssignmentДокумент5 страницEEE3602 AssignmentUmair NazeerОценок пока нет

- 6.012 ST13 Design ProjectДокумент5 страниц6.012 ST13 Design Projectarthur5689791Оценок пока нет

- Massachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceДокумент7 страницMassachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceFernando Sánchez HernándezОценок пока нет

- DSP Lab PDF 16252Документ8 страницDSP Lab PDF 16252awdfasdОценок пока нет

- EC2 Exp2 F09Документ17 страницEC2 Exp2 F09Nurul Hanim HashimОценок пока нет

- CND201 MidtermДокумент4 страницыCND201 MidtermEngy AhmedОценок пока нет

- Devendra Singh Kushwaha: Topic-A Novel Approach To Designing of Low Power Operational AmplifierДокумент31 страницаDevendra Singh Kushwaha: Topic-A Novel Approach To Designing of Low Power Operational AmplifierHarish KumarОценок пока нет

- Butterworth FilterДокумент6 страницButterworth FilterSauravAbidRahmanОценок пока нет

- Breadboard Experiments NImyDAQ and MultisimДокумент84 страницыBreadboard Experiments NImyDAQ and MultisimmadangkОценок пока нет

- Practical: - Transmission and AttenuationДокумент4 страницыPractical: - Transmission and AttenuationasithОценок пока нет

- California State Polytechnic Univerity, Pomona: Multi-Stage Amplifier DesignДокумент1 страницаCalifornia State Polytechnic Univerity, Pomona: Multi-Stage Amplifier DesignEmmanuel Bautista-DizonОценок пока нет

- Final Project Definition 2016Документ3 страницыFinal Project Definition 2016AnhTamОценок пока нет

- ELE341 Project OPAmpДокумент4 страницыELE341 Project OPAmpbabycryyОценок пока нет

- HW 3Документ3 страницыHW 3ansarixxxОценок пока нет

- Ee414 The4Документ1 страницаEe414 The4Asif SiddiqueОценок пока нет

- Use The Process Data Given at The End of The Exam Sheet For All ProblemsДокумент4 страницыUse The Process Data Given at The End of The Exam Sheet For All ProblemsBasem Abd ElazizОценок пока нет

- Intel Processor Power Delivery DesignДокумент13 страницIntel Processor Power Delivery DesignE.I.OSEОценок пока нет

- Lab ExamДокумент8 страницLab ExamNehal GuptaОценок пока нет

- ECE - Lab ReportsДокумент58 страницECE - Lab ReportsSamОценок пока нет

- Electronic Physics Lab 2011Документ22 страницыElectronic Physics Lab 2011최재혁Оценок пока нет

- ECEN 248 Introduction To Digital Systems DesignДокумент7 страницECEN 248 Introduction To Digital Systems DesignBOBОценок пока нет

- CSCE121 10-IostreamsДокумент33 страницыCSCE121 10-IostreamsBOBОценок пока нет

- 9assignment Fall2014Документ2 страницы9assignment Fall2014BOBОценок пока нет

- 16f Hmwk9Документ2 страницы16f Hmwk9BOBОценок пока нет

- 7assignment Summer2015Документ1 страница7assignment Summer2015BOBОценок пока нет

- Instructor's Guide Programming: Bjarne StroustrupДокумент36 страницInstructor's Guide Programming: Bjarne StroustrupbernasekОценок пока нет

- Assignment 8Документ4 страницыAssignment 8BOBОценок пока нет

- Exam ReviewДокумент20 страницExam ReviewBOBОценок пока нет

- Mosfet NotesДокумент46 страницMosfet NotesBOBОценок пока нет

- ADFSDFSDFДокумент7 страницADFSDFSDFBOBОценок пока нет

- Lectures #8 & #9Документ30 страницLectures #8 & #9BOBОценок пока нет

- LASERSДокумент26 страницLASERSBOBОценок пока нет

- HW Due 041116Документ1 страницаHW Due 041116BOBОценок пока нет

- Transistions Between StatesДокумент13 страницTransistions Between StatesBOBОценок пока нет

- Fourier TransformДокумент12 страницFourier TransformBOBОценок пока нет

- Schedule Through Spring BreakДокумент1 страницаSchedule Through Spring BreakBOBОценок пока нет

- Spring 2016 HW 5Документ1 страницаSpring 2016 HW 5BOBОценок пока нет

- Relativity: Einstein Published Two Theories of Relativity in 1905Документ48 страницRelativity: Einstein Published Two Theories of Relativity in 1905BOBОценок пока нет

- Lecture #8Документ21 страницаLecture #8BOBОценок пока нет

- Frank HertzДокумент5 страницFrank HertzFelipe Moncada AlbarránОценок пока нет

- Lecture #8Документ21 страницаLecture #8BOBОценок пока нет

- Step PotentialДокумент34 страницыStep PotentialBOBОценок пока нет

- FFFFДокумент10 страницFFFFBOBОценок пока нет

- Lab 3Документ1 страницаLab 3BOBОценок пока нет

- Final Exam Print Name 6, 2011Документ7 страницFinal Exam Print Name 6, 2011BOBОценок пока нет

- A. The Photons Gain Higher Speeds B. The Energy of The Photons Is Increased C. The Number ofДокумент11 страницA. The Photons Gain Higher Speeds B. The Energy of The Photons Is Increased C. The Number ofBOBОценок пока нет

- Reading Assignments SPRING 2015Документ1 страницаReading Assignments SPRING 2015BOBОценок пока нет

- Prac Exam 1 StudyДокумент15 страницPrac Exam 1 StudyBOBОценок пока нет

- LasersДокумент31 страницаLasersSarika KhoslaОценок пока нет

- RN Program Guide DataДокумент2 страницыRN Program Guide DatascotОценок пока нет

- Codes and Conventions of Musical FilmsДокумент5 страницCodes and Conventions of Musical Filmsapi-295273247Оценок пока нет

- Chapter 6 PPT - NewДокумент66 страницChapter 6 PPT - NewkalehiwotkoneОценок пока нет

- La 1800Документ9 страницLa 1800A Daniel LazarescuОценок пока нет

- Student Design Competition: Title: Low Phase Noise X-Band OscillatorДокумент5 страницStudent Design Competition: Title: Low Phase Noise X-Band OscillatorSaad MohsinОценок пока нет

- Cheat SheetДокумент50 страницCheat SheetAnubhav ChaturvediОценок пока нет

- A Drawing Exercise: 28 by Hand & EyeДокумент4 страницыA Drawing Exercise: 28 by Hand & EyeImml TasbiОценок пока нет

- Arcadia High School 1985 Olympian YearbookДокумент224 страницыArcadia High School 1985 Olympian YearbookJohn Telleria100% (2)

- NNRMS Bulletin 2013 PDFДокумент164 страницыNNRMS Bulletin 2013 PDFladpsОценок пока нет

- Saxo ConcertoДокумент11 страницSaxo ConcertoSebastian Torrejon GodoyОценок пока нет

- DTQ 29s4fc Chasis CN 011nДокумент36 страницDTQ 29s4fc Chasis CN 011nLeonardo GuzmanОценок пока нет

- The Late Shift - Analysis - RowieДокумент7 страницThe Late Shift - Analysis - RowieRowie007Оценок пока нет

- Early Development: Edit EditДокумент2 страницыEarly Development: Edit EditKishor RaiОценок пока нет

- Projet - M2 GNSS Processing Report - SummaryДокумент10 страницProjet - M2 GNSS Processing Report - SummaryguisseОценок пока нет

- Manual en Yg3Документ1 страницаManual en Yg3vygosОценок пока нет

- Curt SachsДокумент2 страницыCurt SachsAnonymous J5vpGuОценок пока нет

- Sternberg Press - November 2019Документ9 страницSternberg Press - November 2019ArtdataОценок пока нет

- A Fully Adjustable Compressor / Limiter: THAT Corporation Design Note 115Документ3 страницыA Fully Adjustable Compressor / Limiter: THAT Corporation Design Note 115wlinartОценок пока нет

- 4-20ma and Loop PoweredДокумент6 страниц4-20ma and Loop Poweredawuawu86Оценок пока нет

- VAASA WILDLIFE FESTIVAL - Official Selection 2018Документ58 страницVAASA WILDLIFE FESTIVAL - Official Selection 2018Wildlife Vaasa Festival / Ilias MissyrisОценок пока нет

- Christmas Recital 2023 One On One - PowerpointДокумент51 страницаChristmas Recital 2023 One On One - PowerpointShiela Advincula - JornalesОценок пока нет

- User ManualDrakan PS2Документ20 страницUser ManualDrakan PS2Daniel MartínОценок пока нет

- 01 - Full Score - Jag VäntarДокумент2 страницы01 - Full Score - Jag VäntarMarkzillaОценок пока нет

- EER ETD 1 Ferrite TransformerДокумент2 страницыEER ETD 1 Ferrite Transformerhason06Оценок пока нет

- Complex Sentences WorksheetsДокумент6 страницComplex Sentences WorksheetsTatik HandayaniОценок пока нет

- Practice DVD Notes - Todd Sucherman I 1Документ3 страницыPractice DVD Notes - Todd Sucherman I 1Gökmen Nacaroğlu100% (1)

- Ilya Kaminsky, Susan Harris-The Ecco Anthology of International Poetry-Ecco (2010) PDFДокумент295 страницIlya Kaminsky, Susan Harris-The Ecco Anthology of International Poetry-Ecco (2010) PDFAsijit Datta83% (12)

- Airs de Ballet (Flauta) - Saint-SaensДокумент11 страницAirs de Ballet (Flauta) - Saint-SaensAlma Libre100% (5)

- (Free Scores - Com) - Coste Napoleon Les Cloches 17826 PDFДокумент6 страниц(Free Scores - Com) - Coste Napoleon Les Cloches 17826 PDFtommasoОценок пока нет

- Seven Shades of Music (Free Sample)Документ6 страницSeven Shades of Music (Free Sample)suidivoОценок пока нет