Академический Документы

Профессиональный Документы

Культура Документы

Compal La-9912p r1.0 Schematics

Загружено:

Wong LaliИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Compal La-9912p r1.0 Schematics

Загружено:

Wong LaliАвторское право:

Доступные форматы

A

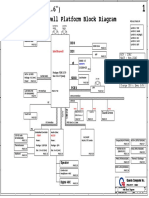

Compal Confidential

VAWGA/B Schematics Document

2

AMD "Kabini" Platform

AMD 25W APU With Jaguar Core and Integrated Yangtze FCH + ATI Sun

LA-9912P REV: 1.0

2013-04-01

2012/04/22

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2015/04/22

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

B

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

COVER PAGE

Document Number

Rev

1.0

VAWGA/GB

Monday, April 01, 2013

Sheet

E

of

37

Compal Confidential

Model Name : VAWGA/B

1

AMD Kabini

Memory BUS(DDR3)

204pin DDRIII-SO-DIMM X2

Single Channel

P.8~P.9

BANK 0, 1, 2

1.5V DDRIII 1600MHz

GFX

LVDS Conn.

HDMI Conn.

P11

DP0

P10

DP1

P12

DAC

CMOS P.11

Camera

AMD FT3 APU

CRT Conn.

GPP

GPP2

MINI Card

(WLAN/BT)

P16

Jaguar Core

Integrated Yangtze FCH

Int.KBD

HDA

SPI

Touch

Screen

Port 4

P.16

Port 1

Port 0

2

MB P.17

3.0 Conn. LP2

Port 1

USB3.0

HD Audio

SATA

Gen3 Port 0

Port 1

HDD

Conn.

ODD

Conn.

P.18

PS2

P.13

Audio

Conexant

CX20757

P.13

P.21

P.4~P.7

Touch Pad

P.17

S/B

2.0 Conn.

Port 9

Port 0

LPC

ENE

KBC9012

P.20

Port 8

USB

P15

P.5

USB2.0

Card P.20

Reader

Port 5

MB P.17

3.0 Conn. LP1

BGA 769-balls

P14

Transformer

RJ45

BIOS (4M)

Port 3

USB

GPP1

LAN

Atheros

AR8162/8172

WLAN P.16

BT Combo

Thermal Sensor

P.19

P.20

Int. MIC

Int. Speaker Conn.

page 21

Audio Combo Jacks

HP & MIC

page 21

page 21

Sub-borad

15"

14"

ODD/B

IO/B

LS9634P

LS9633P

page 13

page 20

Power/B

LS9631P

page 20

LED/B

LS9635P

page 20

USB/B

2012/04/22

Issued Date

page 17

Compal Electronics, Inc.

Compal Secret Data

Security Classification

LS9632P

2015/04/22

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

B

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

BLOCK DIAGRAMS

Document Number

Rev

1.0

VAWGA/GB

Thursday, March 28, 2013

Sheet

E

of

37

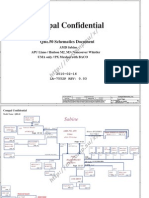

Voltage Rails

Description

S0

S3

S5

VIN

Adapter power supply (19V)

ON

ON

ON

B+

AC or battery power rail for power circuit.

ON

ON

ON

+APU_CORE

Core voltage for APU

ON

OFF

OFF

+APU_CORE_NB

Voltage for On-die VGA of APU

ON

OFF

OFF

+VGA_CORE

0.95-1.2V switched power rail

ON

OFF

OFF

+VDDCI

0.95-1.2V switched power rail

ON

OFF

OFF

3.3V always on power rail

ON

ON

OFF

+3VS

3.3V switched power rail

ON

OFF

OFF

+1.8VALW

1.8V always on power rail

ON

ON

ON*

+1.8VS

1.8V switched power rail

ON

OFF

OFF

+0.95VALW

0.95V always on power rail

ON

OFF

OFF

+0.95VS

0.95V switched power rail

ON

OFF

OFF

Board ID

+1.5V

1.5V power rail for APU and DDR

ON

ON

OFF

+1.5VS

1.5V switched power rail

ON

OFF

OFF

+3VGS

3.3V switched power rail for VGA

ON

OFF

OFF

+1.8VGS

1.8V switched power rail for VGA

ON

OFF

OFF

+1.5VGS

1.5V switched power rail for VGA

ON

OFF

OFF

+0.95VGS

0.95V switched power rail for VGA

ON

OFF

OFF

+5VALW

5V always on power rail

ON

ON

ON

+5VS

5V switched power rail

ON

OFF

OFF

0

1

2

3

4

5

6

7

+VSB

VSB always on power rail

ON

ON

ON

+RTC_APU

RTC power

ON

ON

ON

+0.75VS

0.75V switched power rail for DDR terminator

ON

OFF

OFF

SMBUS Control Table

APU_SCLK0

APU_SDATA0

SMB_EC_CK2

3

SMB_EC_DA2

SOURCE

VGA

BATT

KB9012

KB9012

+3VALW

+3VALW

WLAN

SODIMM WWAN

+3VS

APU

+3VS

+3VS

KB9012

+3VS

+3VS

X

X

V

+3VS

SIGNAL

+VALW

+V

+VS

Full ON

HIGH

HIGH

ON

ON

ON

ON

S1(Power On Suspend)

HIGH

HIGH

ON

ON

ON

LOW

S3 (Suspend to RAM)

HIGH

HIGH

ON

ON

OFF

OFF

S4 (Suspend to Disk)

LOW

HIGH

ON

OFF

OFF

OFF

S5 (Soft OFF)

LOW

LOW

ON

OFF

OFF

OFF

STATE

Board ID / SKU ID Table for AD channel

Vcc

R1562

Thermal

Sensor FCH

PCB Revision

MP

PVT

DVT

EVT

Board ID

0

1

2

3

4

5

6

7

+3VALW

SMB_EC_CK1

SMB_EC_DA1

BOARD ID Table

Power Plane

3.3V +/- 5%

100K +/- 5%

R1564

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

NC

APU

+3VS

OC#

V AD_BID min

0 V

0.216 V

0.436 V

0.712 V

1.036 V

1.453 V

1.935 V

2.500 V

RTD2132

V AD_BID typ

0 V

0.250 V

0.503 V

0.819 V

1.185 V

1.650 V

2.200 V

3.300 V

V AD_BID max

0 V

0.289 V

0.538 V

0.875 V

1.264 V

1.759 V

2.341 V

3.300 V

0

1

2

3

Port

EC SM Bus2 address

LAN

WLAN

Device

Address

HEX

Device

Address

HEX

Smart Battery

0001 011X b

16H

Thermal Sensor

1001 101X b

9AH

SB-TSI (APU)

1001 100X b

98H

VGA Internal Thermal

USB 2.0 USB 3.0

1000 001X b

82H

APU

SM Bus address

XHCI

Device

Address

HEX

DDR DIMM1

1010 000Xb

A0H

DDR DIMM2

1010 001Xb

A2H

Port

0

1

USB20 port1,2,8,9

3 External

USB Port

RIGHT USB

Touch Screen

Camera

CardReader

WLAN/BT Combo

LEFT USB (for colay)

LEFT USB (for colay)

LEFT USB3.0

LEFT USB3.0

A6@

A4@

E2@

E1@

E1PC@

X4@

X5@

X2@

EMICU@

EMICP@

EMIUSB2RU@

EMIUSB2RP@

USB2R@

SUN@

MARS@

14@

15@

PX@

CMOS@

HDMI@

EMIGASP@

8162@

8172@

SWR@

LDO@

THERMAL@

ME@

UMA@

@

ZODD@

TS@

EMIP@

EMIU@

ESDP@

ESDU@

2012/04/22

2015/04/22

Deciphered Date

Date:

BTO Item

2

A6 R3 BGA APU

A4 R3 BGA APU

E2 R3 BGA APU

E1 R3 BGA APU

E1 PC BGA APU

X4 ES2 BGA APU

X5 ES2 BGA APU

X2 ES2 BGA APU

CardReader EMI Un pop

CardReadear EMI pop

Right USB2.0 port EMI un pop

Right USB2.0 port EMI pop

Right USB2.0 port component

SUN PRO GPU (R3 compal part)

MARS XT GPU (R1 compal part)

for 14" componect

for 15" componect

Common VGA circuit

CMOS Camera part

HDMI part

Gastube

Ateros AR8162 LAN Chip

Ateros AR8172 LAN Chip

LAN Switching mode

LAN LDO mode

Lenovo Thermal Sensor

ME part

UMA part

Unpop

Zero Power ODD part

Touch Screen

EMI pop component

EMI Un pop component

ESD pop component

ESD Un pop component

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

B

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

USB30 port0,1

Compal Electronics, Inc.

Compal Secret Data

Security Classification

Issued Date

0

1

2

3

4

5

6

7

8

9

USB Port

USB20 port0

BOM Structure

Device

0

1

2

3

BOM Structure Table

APU PCIE PORT LIST

Clock

USB OC MAPPING

USB Port Table

EC SM Bus1 address

SLP_S3# SLP_S5#

NOTES LIST

Document Number

Rev

1.0

VAWGA/GB

Monday, April 01, 2013

Sheet

E

of

37

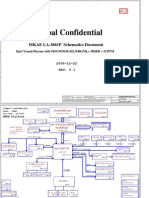

M_DATA0

M_ADD1

M_DATA1

M_ADD2

M_DATA2

M_ADD3

M_DATA3

M_ADD4

M_DATA4

M_ADD5

M_DATA5

M_ADD6

M_DATA6

M_ADD7

M_DATA7

M_ADD9

M_DATA8

M_ADD10

M_DATA9

M_ADD11

M_DATA10

M_ADD12

M_DATA11

M_ADD13

M_DATA12

M_ADD14

M_DATA13

M_ADD15

M_DATA14

M_BANK1

M_DATA16

M_BANK2

M_DATA17

M_DM0

M_DATA19

M_DM1

M_DATA20

M_DM2

M_DATA21

M_DM3

M_DATA22

M_DM4

M_DATA23

M_DM6

M_DATA24

M_DM7

M_DATA25

M_DM8

M_DATA26

M_DQS_H0

M_DATA28

M_DQS_L0

M_DATA29

M_DQS_H1

M_DATA30

M_DQS_L1

<8,9>

<8,9>

M_DATA31

M_DQS_L2

M_DATA32

M_DQS_H3

M_DATA33

M_DQS_L3

M_DATA34

M_DQS_H4

M_DATA35

M_DQS_L4

M_DATA36

M_DQS_H5

M_DATA37

M_DQS_L5

M_DATA38

M_DQS_H6

M_DATA39

M_DQS_H7

M_DATA40

M_DQS_L7

M_DATA41

M_DQS_H8

M_DATA42

M_DQS_L8

M_DATA43

DDRA_CKE0

DDRA_CKE1

DDRB_CKE0

DDRB_CKE1

M_DATA45

M_CLK_L0

M_DATA46

M_CLK_H1

M_DATA47

DDRA_ODT0

DDRA_ODT1

DDRB_ODT0

DDRB_ODT1

<8>

<8>

<9>

<9>

DDRA_SCS0#

DDRA_SCS1#

DDRB_SCS0#

DDRB_SCS1#

AF40

AF41

AK40

AK41

AE40

AE41

AJ40

AJ41

DDRAB_SDQ32

DDRAB_SDQ33

DDRAB_SDQ34

DDRAB_SDQ35

DDRAB_SDQ36

DDRAB_SDQ37

DDRAB_SDQ38

DDRAB_SDQ39

AM41

AN40

AT41

AU40

AL40

AM40

AR40

AT40

DDRAB_SDQ40

DDRAB_SDQ41

DDRAB_SDQ42

DDRAB_SDQ43

DDRAB_SDQ44

DDRAB_SDQ45

DDRAB_SDQ46

DDRAB_SDQ47

AV41

AW40

BA38

AY37

AU41

AV40

AY39

AY38

DDRAB_SDQ48

DDRAB_SDQ49

DDRAB_SDQ50

DDRAB_SDQ51

DDRAB_SDQ52

DDRAB_SDQ53

DDRAB_SDQ54

DDRAB_SDQ55

BA36

AY35

BA32

AY31

BA37

AY36

BA33

AY32

DDRAB_SDQ56

DDRAB_SDQ57

DDRAB_SDQ58

DDRAB_SDQ59

DDRAB_SDQ60

DDRAB_SDQ61

DDRAB_SDQ62

DDRAB_SDQ63

<10>

<10>

DP2_TXP3

DP2_TXN3

<11>

<11>

LVDS_A2

LVDS_A2#

<11>

<11>

LVDS_A1

LVDS_A1#

LVDS

<11>

<11>

LVDS_A0

LVDS_A0#

<11>

<11>

LVDS_ACLK

LVDS_ACLK#

AJ37

AL34

AL35

+MEM_VREF

+VREF_DQ

1

R576

AD40

2

AC38

0_0402_5%

M_DATA48

M_CLK_L2

M_DATA49

M_CLK_H3

M_DATA50

M_CLK_L3

M_DATA51

M_RESET_L

M_DATA53

M_EVENT_L

M_DATA54

ZZZ

A11

B11

TDP1_TXP2

A12

B12

TDP1_TXP3

TDP1_TXN1

TDP1_TXN2

TDP1_TXN3

M0_CKE1

M_DATA56

M1_CKE0

M_DATA57

M1_CKE1

M_DATA58

M0_ODT0

M_DATA60

M0_ODT1

M_DATA61

M1_ODT0

M_DATA62

M1_ODT1

M_DATA63

M0_CS_L0

M_CHECK0

M0_CS_L1

M_CHECK1

M1_CS_L0

M_CHECK2

M1_CS_L1

M_CHECK3

M_RAS_L

M_CHECK5

M_CAS_L

M_CHECK6

M_WE_L

M_CHECK7

V41

W40

AB40

AC40

U41

V40

AA41

AB41

APU_SVT

APU_SVC

APU_SVD

R124 1

R127 1

EC_SMB_CK2

EC_SMB_DA2

<29>

LTDP0_AUXP

LTDP0_AUXN

D15

E15

A5

B5

LTDP0_TXP1

LTDP0_HPD

H17

DAC_RED

B14

LTDP0_TXP2

LTDP0_TXN2

DAC_GREEN

A14

A7

B7

LTDP0_TXP3

DAC_BLUE

B15

DAC_HSYNC

G19

E19

APU_SIC

APU_SID

B22

B21

<29>

H_PROCHOT#

DAZ0Y600201

M_ZVDDIO_MEM_S

AD41

DISP_CLKIN_H

B20

A20

APU_RST#

LDT_RST#

DAC_SDA

D19

D21

SVD

DAC_ZVSS

A16

<10,12>

<10,12>

HDMI_DET

<10>

EDID_CLK

EDID_DATA

<11>

<11>

DAC_RED

<12>

DAC_GRN

<12>

DAC_BLU

<12>

CRT_HSYNC

CRT_VSYNC

<12>

<12>

CRT_DDC_CLK

CRT_DDC_DATA

<12>

<12>

CRT

2 499_0402_1%

THERMDA

SID

THERMDC

APU_RST_L

R118 1

R120 1

2 0_0402_5% APU_PROCHOT#

APU_ALERT#

PROCHOT_L

A22

B18

D29

D31

D35

D33

G27

B25

A25

D23

G23

E25

E23

A6@

UAPU

LDT_RST_L

LDT_PWROK

ALERT_L

TDI

TDO

APU_BP0

APU_BP1

APU_BP2

APU_BP3

APU_PLLTEST1

APU_PLLTEST0

APU_BPCLK_H

APU_BPCLK_L

EDID_CLK

EDID_DATA

R255 2

R256 2

RP23

8

7

6

5

T39

T40

T41

A29

FREE_2

GIO_TSTDTM0_SERIALCLK H21

TRST_L

DBRDY

GIO_TSTDTM0_CLKINIT

DAC_BLU

DAC_GRN

DAC_RED

DP_150_ZVSS

T42

APU_SCLK

APU_CLKINT

H25

1

2

3

4

150_0804_8P4R_1%

TCK

TMS

1 4.7K_0402_5%

1 4.7K_0402_5%

DBREQ_L

VDDCR_NB_SENSE

USB_ATEST1

VDDCR_CPU_SENSE

M_ANALOGIN

VDDIO_MEM_S_SENSE

M_ANALOGOUT

VSS_SENSE

TMON_CAL

AJ10

AJ8

R32

N32

AP29

HDMI_EN/DP_STEREOSYNCE21

VDD_095_FB_H

T45

T43

T44

T46

T47

DP_STEREOSYNC

VDD_095_FB_L

A4@

X4@

A4 PR KABINI AM5000IBJ44HM 1.5G BGA 769P APU

E1@

APU_PWRGD

C1270

ESDU@

1

2

100P_0402_50V8J

APU_RST#

E2@

C1273

ESDU@

2

100P_0402_50V8J

M_ZVDDIO

X2@

UAPU

3

5

APU_TRST#

@ RP11

11

1

2

3

4

APU_ALERT#

APU_SID

APU_PROCHOT#

APU_SIC

8

7

6

5

13

15

17

19

+MEM_VREF

10

11

12

13

14

15

16

19

R80

R82

R18

1

1

1

8

7

6

5

1K_0804_8P4R_5%

2 300_0402_5%

2 300_0402_5%

2 511_0402_1%

+1.8VS

17

APU_RST#

APU_PWRGD

APU_BPCLK_L

+1.8VS

RP5 @

1

2

3

4

APU_SVT

APU_SVC

APU_SVD

E1 PC 2M101082J2361 1G BGA 769P

PU +1.8VS + PD

8

7

6

5

1K_0804_8P4R_5%

PU +1.8VS

For HDMI Need

+3VS

RP4

1

2

3

4

R113

1K_0402_5%

DP_STEREOSYNC

CRT_HSYNC

E1PC@

2

+1.5V

R74

39.2_0402_1%

X2 ES2 KABINI ZMA5B078J2360 1.65G BGA CPU

ESDP@ C195

0.1U_0402_16V7K

2

@

@

C342

C164

1U_0402_6.3V6K

0.1U_0402_16V7K

2

1

PU +3VS

+3VS

R114

1K_0402_5%

E2 PR KABINI EM3000IBJ23HM 1.65G BGA 769P APU

+1.8VS

FT3_BGA769

E1 PR KABINI EM2100ICJ23HM 1G BGA769P APU

X5 ES2 ZM201079J4460 2G BGA 769P

18

20

APU_TCK

APU_TMS

APU_TDI

APU_TDO

RP6

APU_TDI

APU_TMS

APU_TCK

APU_DBREQ#

1

2

3

4

APU_SCLK

APU_CLKINT

APU_SCLK

APU_CLKINT

1K_0804_8P4R_5%

10

APU_PWRGD

12

APU_RST#

14

APU_DBRDY

16

APU_DBREQ#

18

APU_PLLTEST0

20

APU_PLLTEST1

+1.8VS

RP3 @

8

7

6

5

1

2

3

4

8

7

6

5

1K_0804_8P4R_5%

PD

RP7 @

APU_BP2

APU_BP3

APU_BP0

APU_BP1

1

2

3

4

APU_TRST#

APU_PLLTEST0

APU_PLLTEST1

1

2

3

4

8

7

6

5

1K_0804_8P4R_5%

RP8

+1.8VS

8

7

6

5

4

1K_0804_8P4R_5%

RP11, RP6 will @ when MP

R19 1

APU_BPCLK_H

2 511_0402_1%

MEM_MAB_EVENT#

1

1K_0804_8P4R_1%

2

2

C337

1U_0402_6.3V6K

@ SAMTE_ASP-136446-07-B

C163

0.1U_0402_16V7K

2012/04/22

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2015/04/22

Deciphered Date

Title

FT3 DDR3/DISP/MISC//HDT+

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

+3VS

H27

H29

D25

BP0 A27

BP1 B27

BP2 A26

BP3 B26

PLLTEST1 B28

PLLTEST0 A28

BYPASSCLK_H B24

BYPASSCLK_L A24

PLLCHRZ_H AV35

PLLCHRZ_L AU35

M_TEST E33

SIC

R416 1

DAC_ZVSS

FT3_BGA769

10K_0804_8P4R_5%

8

7

6

5

HDMI_CLK

HDMI_DATA

FT3 REV 0.51

X5@

RP2

1

2

3

4

CRT_HSYNC

SVC

APU_PWROK

A6 PR KABINI AM5200IAJ44HM 2G BGA769P APU

+1.5V

DAC_VSYNC

SVT

B19

APU_PWRGD

2 0_0402_5%

LDT_PWRGD A19

AV33

AU33

UAPU

FT3 REV 0.51

+VREF_DQ

<18>

<11>

<11>

+3VS

DISP_CLKIN_L

2 0_0402_5%

APU_VDD_RUN_FB_L

UAPU

M_VREFDQ

DAZ0Y700201

MEMORY VREF

2 100K_0402_5%

LTDP0_TXN3

APU_VDDNB_SEN

APU_VDD_SEN

UAPU

R897 1

ENBKL

APU_ENVDD

APU_INVT_PWM

LTDP0_TXN1

A6

B6

G31

D27

E29

JHDT2

15@

H19

LTDP0_TXN0

APU_SVT

APU_SVC

APU_SVD

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

<29>

<29>

2 2K_0402_1%

DIECRACKMON

APU_PWRGD

<18,24,29,6>

2 0_0402_5%

2 0_0402_5%

@

@

R117 1

M_VREF

UAPU

LA9912P

TDP1_HPD

LTDP0_TXP0

+1.8VS

14@

D17

E17

A4

B4

HDT+

LA9912P

TDP1_AUXN

TDP1_AUXP

DAC_SCL

<18,19>

<18,19>

R400 1

M0_CKE0

X4@

ZZZ

TDP1_TXP1

USB_ATEST0

M_CLK_H2

M_CHECK4

DDRAB_SRAS#

DDRAB_SCAS#

DDRAB_SWE#

A10

B10

K15

H15

<29>

<29>

<29>

DP_150_ZVSS

DP_2K_ZVSS

DP_BLON

UAPU

AJ34

AR38

AL38

AN35

DP_2K_ZVSS

M_CLK_L1

M_DATA59

AN38

AU38

AN37

AR37

<8>

<8>

<9>

<9>

<8,9>

<8,9>

<8,9>

M_CLK_H0

M_DATA55

L34

J38

J37

J34

DDRAB_SDQ24

DDRAB_SDQ25

DDRAB_SDQ26

DDRAB_SDQ27

DDRAB_SDQ28

DDRAB_SDQ29

DDRAB_SDQ30

DDRAB_SDQ31

DP2_TXP2

DP2_TXN2

M_DQS_L6

M_DATA52

G38

MEM_MAB_EVENT# AE34

MEM_MAB_RST#

MEM_MAB_EVENT#

<8>

<8>

<9>

<9>

AC35

AC34

AA34

AA32

AE38

AE37

AA37

AA38

DDRA_CLK0

DDRA_CLK0#

DDRA_CLK1

DDRA_CLK1#

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#

M41

N40

T41

U40

L40

M40

R40

T40

<10>

<10>

HDMI

M_DQS_H2

M_DATA44

<8>

<8>

<8>

<8>

<9>

<9>

<9>

<9>

DDRAB_SDQ16

DDRAB_SDQ17

DDRAB_SDQ18

DDRAB_SDQ19

DDRAB_SDQ20

DDRAB_SDQ21

DDRAB_SDQ22

DDRAB_SDQ23

DP2_TXP1

DP2_TXN1

B16

A21

B17

DP_DIGON A17

DP_VARY_BL A18

DP_150_ZVSS

TDP1_TXN0

B33

A33

B40

A40

H41

H40

P41

P40

AH41

AH40

AP41

AP40

BA40

AY41

AY33

BA34

AA40

Y41

DDRAB_SDQS0

DDRAB_SDQS0#

DDRAB_SDQS1

DDRAB_SDQS1#

DDRAB_SDQS2

DDRAB_SDQS2#

DDRAB_SDQS3

DDRAB_SDQS3#

DDRAB_SDQS4

DDRAB_SDQS4#

DDRAB_SDQS5

DDRAB_SDQS5#

DDRAB_SDQS6

DDRAB_SDQS6#

DDRAB_SDQS7

DDRAB_SDQS7#

F40

F41

K40

K41

E40

E41

J40

J41

<10>

<10>

UAPUC

DISPLAY/SVI2/JTAG/TEST

TDP1_TXP0

M_DM5

M_DATA27

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

<8,9>

DDRAB_SDQ8

DDRAB_SDQ9

DDRAB_SDQ10

DDRAB_SDQ11

DDRAB_SDQ12

DDRAB_SDQ13

DDRAB_SDQ14

DDRAB_SDQ15

A9

B9

DP2_TXP0

DP2_TXN0

B32

B38

G40

N41

AG40

AN41

AY40

AY34

Y40

B37

A38

D40

D41

B36

A37

B41

C40

<10>

<10>

M_BANK0

M_DATA18

DDRAB_SDM0

DDRAB_SDM1

DDRAB_SDM2

DDRAB_SDM3

DDRAB_SDM4

DDRAB_SDM5

DDRAB_SDM6

DDRAB_SDM7

DDRAB_SDQ0

DDRAB_SDQ1

DDRAB_SDQ2

DDRAB_SDQ3

DDRAB_SDQ4

DDRAB_SDQ5

DDRAB_SDQ6

DDRAB_SDQ7

M_ADD8

M_DATA15

AJ38

AG35

N34

DDRAB_SBS0#

DDRAB_SBS1#

DDRAB_SBS2#

DDRAB_SDM[7..0]

B30

A32

B35

A36

B29

A30

A34

B34

M_ADD0

HDMI & LVDS should be reverse in KABINI:

APU TX0 to Connector TX2 ; APU TX1 to Connector TX1

APU TX2 to Connector TX0 ; APU TX3 to Connector CLK

<8,9>

DDRAB_SDQ[63..0]

MEMORY

DDRAB_SMA0 AG38

DDRAB_SMA1 W35

DDRAB_SMA2 W38

DDRAB_SMA3 W34

DDRAB_SMA4 U38

DDRAB_SMA5 U37

DDRAB_SMA6 U34

DDRAB_SMA7 R35

DDRAB_SMA8 R38

DDRAB_SMA9 N38

DDRAB_SMA10 AG34

DDRAB_SMA11 R34

DDRAB_SMA12 N37

DDRAB_SMA13 AN34

DDRAB_SMA14 L38

DDRAB_SMA15 L35

<8,9>

<8,9>

<8,9>

<8,9>

UAPUA

DDRAB_SMA[15..0]

<8,9>

Rev

1.0

VAWGA/GB

Monday, April 01, 2013

Sheet

E

of

37

UAPUB

APU POWER SEQUENCE

PCIE

<14>

<14>

LAN

<16>

<16>

WLAN

PCIE_DTX_C_ARX_P1

PCIE_DTX_C_ARX_N1

PCIE_DTX_C_ARX_P2

PCIE_DTX_C_ARX_N2

R10

R8

P_GPP_RXP0

P_GPP_TXP0

P_GPP_RXN0

P_GPP_TXN0

R5

R4

P_GPP_RXP1

P_GPP_TXP1

P_GPP_RXN1

P_GPP_TXN1

N5

N4

P_GPP_RXP2

P_GPP_TXP2

P_GPP_RXN2

P_GPP_TXN2

N10

N8

P_GPP_RXP3

P_GPP_TXP3

P_GPP_RXN3

P_GPP_TXN3

L2

L1

+RTC

G-A

K2

K1

PCIE_ATX_DRX_P1

PCIE_ATX_DRX_N1

C19

C20

1

1

2

2

0.1U_0402_16V7K

0.1U_0402_16V7K

J2

J1

PCIE_ATX_DRX_P2

PCIE_ATX_DRX_N2

C17

C18

1

1

2

2

0.1U_0402_16V7K

0.1U_0402_16V7K

EC_ON

PCIE_ATX_C_DRX_P1 <14>

PCIE_ATX_C_DRX_N1 <14>

LAN

PCIE_ATX_C_DRX_P2 <16>

PCIE_ATX_C_DRX_N2 <16>

WLAN

+3VALW/+5VALW

G-B

H2

H1

+1.8VALW

+0.95VALW

1

+0.95VS_APU_GFX

2 P_TX_ZVDD_095

R404

1.69K_0402_1%

W8

P_RX_ZVDD_095 W7

P_TX_ZVDD_095

L5

L4

P_GFX_RXP0

P_GFX_TXP0

P_GFX_RXN0

P_GFX_TXN0

J5

J4

P_GFX_RXP1

P_GFX_TXP1

P_GFX_RXN1

P_GFX_TXN1

G5

G4

P_GFX_RXP2

P_GFX_TXP2

P_GFX_RXN2

P_GFX_TXN2

D7

E7

P_GFX_RXP3

P_GFX_TXP3

P_GFX_RXN3

P_GFX_TXN3

P_RX_ZVDD_095

1

R73

1K_0402_1%

+0.95VS_APU_GFX

SYSON

+1.5V

G-C

G2

G1

SUSP#

F2

F1

+3VS

G-D

+1.8VS

E2

E1

+1.5VS

D2

D1

+0.95VS

VR_ON

+APU_CORE

G-E

FT3 REV 0.51

X4@

+APU_CORE_NB

FT3_BGA769

UAPUE

2

CLK/SATA/USB/SPI/LPC

R90

R96

2

2

AL4

AL5

SATA_RX0P

SATA_TX1N

USB_HSD1P

AY17

BA17

SATA_RX1N

AR19

AP19

SATA_ZVSS

BA30

SATA_ACT_L/GPIO67

AY12

SATA_X1

SATA_RX1P

USB_HSD2P

USB_HSD2N

SATA_ZVDD_095

USB_HSD3P

USB_HSD3N

T48

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

BA12

SATA_X2

USB_HSD6P

USB_HSD6N

U4

U5

0_0402_5%

2

@

2

@

0_0402_5%

2

R125 1

@

2

R126 1

@

0_0402_5%

LAN

<14>

<14>

<16>

<16>

R116 1

R119 1

CLK_PCIE_LAN

CLK_PCIE_LAN#

CLK_PCIE_WLAN

CLK_PCIE_WLAN#

GFX_CLKP

USB_HSD7P

GFX_CLKN

USB_HSD7N

AC8

AC10

GPP_CLK0P

USB_HSD8P

GPP_CLK0N

USB_HSD8N

GPP_CLK1P AE4

GPP_CLK1N AE5

GPP_CLK1P

USB_HSD9P

GPP_CLK1N

USB_HSD9N

GPP_CLK2P AC4

GPP_CLK2NAC5

GPP_CLK2P

AA5

AA4

GPP_CLK3P

USB_SS_0TXP

GPP_CLK3N

USB_SS_0TXN

X14M_25M_48M_OSC

USB_SS_0RXP

WLAN

AP13

USB_SS_ZVSS

USB_SS_1TXN

N1

X48M_X2

USB_SS_1RXP

R103 R104 for EMI

<18,6>

<6>

R103 1

R104 1

LPC_CLK0_EC

LPC_CLK1

<18>

<18>

<18>

<18>

<18,6>

<18>

USB_SS_1RXN

@

@

2 0_0402_5%

2 0_0402_5%

AY2

AW2

SERIRQ

T50

AT2

AT1

AR2

AR1

AP2

AP1

AV29

AP25

AV2

USB20_P1

USB20_N1

<16>

<16>Touch

USB20_P3

USB20_N3

<11>

<11>CAMERA

USB20_P4

USB20_N4

<20>

<20>CardReader

USB20_P5

USB20_N5

<16>

<16>WLAN/BT

USB20_P6

USB20_N6

<17>

<17>USB2.0

LP1

USB20_P7

USB20_N7

<17>

<17>USB2.0

LP2

USB30_P8

USB30_N8

<17>

<17>MB

USB3.0 port0

USB30_P9

USB30_N9

<17>

<17>MB

USB3.0 port1

USB port

Screen

AG1

AG2

AF1

AF2

AE1

AE2

AD1

AD2

AC1

AC2

AB1

AB2

AA1

AA2

AE10

USBSS_ZVSS R644 1

USBSS_ZVDD R645 1

T2

T1

2 1K_0402_1%

2 1K_0402_1%

48MHz CRYSTAL

combo

48M_X2

R938

1M_0402_5%

+0.95VALW

RP12

APU_SPI_AISO

APU_SPI_AOSI_U

APU_SPI_CLK_U

APU_SPI_CS1#_U

USB30_MRX_DTX_P0<17>

USB30_MRX_DTX_N0<17>

R1

R2

<17>

USB30_MTX_C_DRX_P1

<17>

USB30_MTX_C_DRX_N1

W1

W2

1

2

3

4

8

7

6

5

EC_SPI_AISO

EC_SPI_AOSI

EC_SPI_CLK

EC_SPI_CS1#

SPI_CLK/GPIO162

AU7

APU_SPI_CLK

APU_SPI_CS1#

SPI_CS2_L/GPIO166 AR4

LAD0

AR11

SPI_DI/GPIO164 AR7

SPI_HOLD_L/GEVENT9_LAU11

SPI_WP_L/GPIO161 AU9

LAD1

SPI_DO/GPIO163

LAD2

LAD3

LFRAME_L

APU_SPI_AOSI

APU_SPI_AISO

APU_SPI_HOLD#

APU_SPI_WP#

T51

R110 1

R111 1

2 33_0402_5%

2 33_0402_5%

APU_SPI_CLK_U

APU_SPI_CS1#_U

R109 1

2 33_0402_5%

APU_SPI_AOSI_U

APU_SPI_AISO

LDRQ0_L

X4@

FT3_BGA769

EC_SPI_AISO

EC_SPI_AOSI

EC_SPI_CLK

EC_SPI_CS1#

<18>

<18>

<18>

<18>

C794

6P_0402_50V8

C795

6P_0402_50V8

+3VALW

R108 1

R614

10K_0402_5%

1

2APU_SPI_CS1#_U

APU_SPI_AISO_U

1

2APU_SPI_WP#

R616

10K_0402_5%

2 33_0402_5%

2

U56

1

2

3

4

CS#

SO/SIO1

WP#

GND

VCC

HOLD#

SCLK

SI/SIO0

8

7

6

5

APU_SPI_HOLD#

APU_SPI_CLK_U

APU_SPI_AOSI_U

APU->EC->ROM must route as

W25Q32FVSSIG SOIC 8P SPI ROM

Daisy Chain for Share ROM quality

APU_SPI_CLK_U 1

(RP12 was request to added for the recoverable solution

as original method--backup)

2012/04/22

1

C635

0.1U_0402_16V4Z

2

R615

10K_0402_5%

4

2

1

2

R617 EMIU@

10_0402_5%

C636 EMIU@

10P_0402_50V8J

Compal Electronics, Inc.

Compal Secret Data

Security Classification

Issued Date

+3VALW

LPC_CLKRUN_L

LPC_PD_L/GEVENT5_L/SPI_TPM_CS_L

4MB SPI ROM

(Current Share mode)

R108 close to ROM

SERIRQ/GPIO48

0_0804_8P4R_5%

USB30_MRX_DTX_P1<17>

USB30_MRX_DTX_N1<17>

R109,R110,R111 close to APU

LPCCLK1

Y20

48MHZ_8PF_X3S048000D81H-W

<17>

USB30_MTX_C_DRX_P0

<17>

USB30_MTX_C_DRX_N0

V2

V1

48M_X1

LPCCLK0

FT3 REV 0.51

<17>

<17>Right

AG7

AG8

SPI_CS1_L/GPIO165 AW9

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

USB20_P0

USB20_N0

X48M_X1

USB_SS_1TXP

48M_X2

AJ4

AJ5

AE8

USB_SS_ZVDD_095_USB3_DUAL

GPP_CLK2N

USB_SS_0RXN

N2

48M_X1

2 11.8K_0402_1%

SATA_TX1P

USB_HSD1N

1 1K_0402_1% SATA_ZVSS

1 1K_0402_1% SATA_ZVDD

R641 1

AY19

BA19

<13> SATA_DTX_C_ARX_N1

<13> SATA_DTX_C_ARX_P1

+0.95VS

USB_HSD0P

USB_ZVSS

SATA_RX0N

USB_HSD0N

<13> SATA_ATX_DRX_P1

<13> SATA_ATX_DRX_N1

ODD

USB_ZVSS

AG4

BA16

AY16

<13> SATA_DTX_C_ARX_N0

<13> SATA_DTX_C_ARX_P0

SATA_TX0N

HDD

W4

USBCLK/14M_25M_48M_OSC

SATA_TX0P

BA14

AY14

<13> SATA_ATX_DRX_P0

<13> SATA_ATX_DRX_N0

2015/04/22

Deciphered Date

Title

FT3 PCIE/SATA/CLK/USB/SPI

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev

1.0

VAWGA/GB

Date:

Thursday, March 28, 2013

Sheet

E

of

37

ACPI/SD/AZ/GPIO/RTC/MISC

EC_RSMRST#_R

AY4

AY9

LPC_RST_L

AY5

RSMRST_L

SD_PWR_CTRL

PCIE_RST_L

SD_CLK/GPIO73

SD_CMD/GPIO74

SD_CD/GPIO75

<18>

<16>

PBTN_OUT#

PWR_GOOD_APU

T36

APU_PCIE_WAKE#

APU_PCIE_WAKE#

<18>

<18>

PWR_BTN_L

SD_WP/GPIO76

AY3

BA5

TEST0

CS_JTAG_TMS_TEST1

TEST2

AU13

AY10

AY6

AR23

AR31

AN5

AL7

KBRST#

GATEA20

EC_SCI#

EC_SMI#

SD_DATA3/GPIO80

BA22

AY21

AY24

BA24

SD_LED/GPIO45

AY25

TEST1/TMS

SCL0/GPIO43

TEST2

SDA0/GPIO47

AU25

AV25

SYS_RESET_L/GEVENT19_L

SD_DATA0/GPIO77

WAKE_L/GEVENT8_L

SD_DATA1/GPIO78

SLP_S3_L

KBRST_L

SCL1/GPIO227

GA20IN/GEVENT0_L

<14>

<16>

<17>

<17>

<21>

LAN_CLKREQ#

WLAN_CLKREQ#

USB_OC0#

USB_OC1#

T52

T54

HDA_SDIN0

T55

T56

T57

AY8

AW1

AV1

AY1

AN2

AN1

AK2

AK1

AM1

AL2

AM2

AL1

HDA_BITCLK

HDA_SDOUT

HDA_SDIN0

HDA_SDIN1

HDA_SDIN2

HDA_SDIN3

HDA_SYNC

HDA_RST#

32K_X1

AJ2

32K_X2

AJ1

C912

150P_0402_50V8J

SDA1/GPIO228

APU_SCLK0

APU_SDATA0

AY11

BA11

LPC_SMI_L/GEVENT23_L

GPIO49

AC_PRES/IR_RX0/GEVENT16_L

GPIO55

IR_TX0/GEVENT21_L

GPIO57

IR_TX1/GEVENT6_L

GPIO58

IR_RX1/GEVENT20_L

GPIO59

IR_LED_L/LLB_L/GPIO184

GPIO64

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/GPIO60

GPIO68

CLK_REQ1_L/GPIO61

GPIO69

CLK_REQ2_L/GPIO62

GPIO70

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/GPIO63

GPIO71

CLK_REQG_L/GPIO65/OSCIN

GPIO174

AP27

AY28

BA28

AV23

AP21

BA26

AV19

AY27

BA27

AU21

AY26

AV21

AM21

BA3

USB_OC2_L/TCK/GEVENT14_L

USB_OC3_L/TDO/GEVENT15_L

AZ_BITCLK

AZ_SDOUT

AZ_SDIN0/GPIO167

EC_LID_OUT#

AZ_SDIN1/GPIO168

AZ_SDIN2/GPIO169

GENINT1_L/GPIO32

AZ_SDIN3/GPIO170

GENINT2_L/GPIO33

BT_OFF#

<16>

WL_OFF#

ODD_EN

<16>

<13>

APU_SPKR

<21>

If use as SMBUS :

Pulled-up to VDD_33(port0) , VDD_33_ALW(port1) with a resistor of:

Qty: 1; Value: 2.2 K; Tol: 5%

If no use :

Pulled-up to VDD_33(port0) , VDD_33_ALW(port1) with a resistor of:

Qty: 1; Value: 10 K; Tol: 5%

+3VS

UMA@

Function

<18,24,29,4>

H_PROCHOT#

PX5.5

UMA

PX@ R912

10K_0402_5%

32.768KMHz CRYSTAL

<18>

EC_LID_OUT#

BA29

AP23

32K_X1

1

AZ_SYNC

AZ_RST_L

FANIN0/GPIO56

AV31

AU31

RTCCLK

AV11

FANOUT0/GPIO52

R911

10K_0402_5%

Board_ID1

GEVENT2#

GEVENT2_L

USB_OC1_L/TDI/GEVENT13_L

Board_ID1

2 0_0402_5%

R661 1

@

APU_GPIO174

<14,16>

Board_ID1

AV17

GEVENT4_L BA4

GEVENT7_L AR15

GEVENT10_L AP17

GEVENT11_L AP11

GEVENT17_L AN8

BLINK/GEVENT18_L AU17

GEVENT22_L BA6

USB_OC0_L/SPI_TPM_CS_L/TRST_L/GEVENT12_L

APU_PCIE_RST#

1

<16,8,9>

<16,8,9>

APU_SCLK0

APU_SDATA0

APU_SCLK1

APU_SDATA1

LPC_PME_L/GEVENT3_L

SPKR/GPIO66

AU29

AW29

AR27

AV27

AY29

2

R907

33_0402_5%

TEST0

GPIO51

LAN_CLKREQ#

WLAN_CLKREQ#

T53

APU_PCIE_RST#_BUF

SLP_S5_L

GPIO50

AP15

AV13

BA9

BA10

AV15

AY23

AY20

BA20

PWR_GOOD

SD_DATA2/GPIO79

SLP_S3#

SLP_S5#

<18>

<18>

<18>

<18>

BA8

AM19

AY7

AW11

BA23

AY22

LPC_RST_A#

APU_PCIE_RST#_BUF

2

R602

33_0402_5%

LPC_RST#

UAPUD

C615

150P_0402_50V8J

<18>

32K_X2

R914

20M_0402_5%

<16>

BT_DISABLE#

X32K_X1

Y3

32.768KHZ_12.5P_1TJF125DP1A000D

X32K_X2

<18>

RTC_CLK

FT3 REV 0.51

X4@

FT3_BGA769

PU +3VALW + PD

1

C682

22P_0402_50V8J

C686

18P_0402_50V8J

+3VALW

RP13

2 10K_0402_5%

<21>

<21>

<21>

<21>

1

2

3

4

HDA_RST#_AUDIO

HDA_SYNC_AUDIO

HDA_BITCLK_AUDIO

HDA_SDOUT_AUDIO

8

7

6

5

HDA_RST#

HDA_SYNC

HDA_BITCLK

HDA_SDOUT

STRAPS OF APU

33_0804_8P4R_5%

LPC_FRAME#

PU +3VALW

APU_SCLK1

APU_SDATA1

APU_PCIE_WAKE#

EC_RSMRST# , POWER_GOOD

follow CRB

(APU side 1.8V power rail)

R345

47K_0402_5%

NORMAL POWR

UP/RESET TIMING

(DEFAULT)

LPC ROM

BOOT FAIL TIMER

DISABLED

(DEFAULT)

CLKGEN

DISABLED

3.3V SPI ROM

(DEFAULT)

FAST POWER

UP/RESET TIMING

FOR SIMULATION

R685

10K_0402_5%

<18,5>

<18,5>

<5>

RB751V-40TE17_SOD323-2

2 8.2K_0402_5%

WLAN_CLKREQ#

R621 1

R673 1

R674 1

2 8.2K_0402_5%

2 2.2K_0402_5%

2 2.2K_0402_5%

LAN_CLKREQ#

APU_SCLK0

APU_SDATA0

PU +3VALW + PD

R684 1

2 10K_0402_5%

HDA_BITCLK

R688 1

2 10K_0402_5%

HDA_SDIN0

1U_0402_6.3V6K

C212

LPC_FRAME#

LPC_CLK0_EC

LPC_CLK1

GEVENT2#

RTC_CLK

+3VALW

RP9 @

1

2

3

4

@

R903

2K_0402_5%

8

7

6

5

R622 1

1U_0402_6.3V6K

C209

+3VS

R949

10K_0402_5%

2

PWR_GOOD_APU

@

R950

2.2K_0402_5%

R929

2.2K_0402_5%

@

R927

2K_0402_5%

R926

2K_0402_5%

SYS_PWRGD_EC

@

R928

10K_0402_5%

R925

10K_0402_5%

<18>

@

R904

10K_0402_5%

R902

10K_0402_5%

RB751V-40TE17_SOD323-2

PU +3VS

1K_0804_8P4R_5%

RP10 @

TEST0

CS_JTAG_TMS_TEST1

TEST2

1

2

3

4

8

7

6

5

15K_0804_8P4R_5%

2012/04/22

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2015/04/22

Deciphered Date

Title

FT3 GPIO/AZ/MISC

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Rev

1.0

VAWGA/GB

Date:

+3VALW

EC_RSMRST#_R

EC_RSMRST#

<18>

EC_LID_OUT#

USB_OC0#

USB_OC1#

D5

PD

RTC_CLK

2 100K_0402_5%

2 100K_0402_5%

2 100K_0402_5%

1.8V SPI ROM

D3

1

+1.8VALW

Must connected to 10 ms RC delay

circuit on +1.8-V S5 power rail.

10K_0804_8P4R_5%

R656 1

R650 1

R651 1

GEVENT2_L

CLKGEN

ENABLE

(DEFAULT)

8

7

6

5

LPC_CLK1

BOOT FAIL TIMER

ENABLED

RP14

+3VALW

1

2

3

4

LPC_CLK0_EC

SPI ROM

(DEFAULT)

APU_GPIO174

2 10K_0402_5%

R686 1

R691 1

Thursday, March 28, 2013

Sheet

E

of

37

RTC OF APU

CORE POWER OF APU

VDDBT_RTC_G

+RTCBATT

VDDCR_CPU

+RTCBATT_R

180P_0402_50V8J

W=20mils

1

C166

0.22U_0402_10V6K

R93

2 10K_0402_5%

C190

1U_0402_6.3V6K

C189

1U_0402_6.3V6K

1U_0402_6.3V6K

C188

C187

1U_0402_6.3V6K

C186

1U_0402_6.3V6K

1U_0402_6.3V6K

C184

C183

1U_0402_6.3V6K

1U_0402_6.3V6K

C182

C181

1U_0402_6.3V6K

1U_0402_6.3V6K

C180

C179

+APU_CORE

CLRP1 J@

SHORT PADS

Need OPEN

1

for Clear CMOS

INTEGRATED GPU POWER OF APU

+3VALW/+3VS OF APU

VDDCR_NB

+APU_CORE_NB

+3VALW

+3VS

@

+3VALW_APU

UAPUH

1U_0402_6.3V6K

2

UAPUF

C232

180P_0402_50V8J

1U_0402_6.3V6K

180P_0402_50V8J

1U_0402_6.3V6K

C233

1U_0402_6.3V6K

C240

C239

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

C238

C237

10U_0603_6.3V6M

1U_0402_6.3V6K

10U_0603_6.3V6M

C236

+0.95VALW

AL10

AL11

+1.5VS

B1

B2

+1.8VALW

AL13

AM13

AR5

AU4

AV7

AW5

C245

C248

AE11

AE13

AJ11

AJ13

+0.95VALW

2

180P_0402_50V8J

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

4.7U_0603_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

VDD_095_USB3_DUAL

1U_0402_6.3V6K

180P_0402_50V8J

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0603_6.3V6M

10U_0603_6.3V6M

VDDIO_MEM_S_6

VDDIO_MEM_S_7

VDDIO_MEM_S_8

VDDIO_MEM_S_9

VDDIO_MEM_S_10

VDDIO_MEM_S_11

VDDIO_MEM_S_12

VDDIO_MEM_S_13

VDDIO_MEM_S_14

VDDIO_MEM_S_15

VDDIO_MEM_S_16

VDDIO_MEM_S_17

VDDIO_MEM_S_18

VDDIO_MEM_S_19

VDDIO_MEM_S_20

VDDIO_MEM_S_21

VDDIO_MEM_S_22

VDDIO_MEM_S_23

L13

VDDCR_NB_2 L17

VDDCR_NB_3 N11

VDDCR_NB_4 N13

VDDCR_NB_5 N17

VDDCR_NB_6 R11

VDDCR_NB_7 R13

VDDCR_NB_8 R17

VDDCR_NB_9 U13

VDDCR_NB_10 U17

VDDCR_NB_11 W13

VDDCR_NB_12 W17

VDDCR_NB_13 AA13

VDDCR_NB_14 AA17

VDDCR_NB_15 AC13

VDDCR_NB_16 AC17

VDDCR_NB_17 AE15

VDDCR_NB_18 AE17

VDDCR_NB_19 AE19

VDDCR_NB_20 AG17

VDDCR_NB_21 AG21

VDDIO_AZ_ALW_1

VDD_18_ALW_1

VDD_18_1

VDD_18_ALW_2

VDD_18_2

VDD_33_ALW_1

VDD_33_1

VDD_33_ALW_2

VDD_33_2

VDD_095_1

VDD_095_USB3_DUAL_2

VDD_095_USB3_DUAL_3

VDD_095_USB3_DUAL_4

VDD_095_ALW_1

VDD_095_ALW_2

VDD_095_ALW_3

VDD_095_ALW_4

VDD_095_GFX_2 W10

AN4

+APU_CORE_NB

+1.8VS

+3VS

+0.95VS

A8

A13

A23

A31

A35

A39

B8

B13

B23

B31

B39

C1

C2

C5

C7

C9

C11

C13

C15

C17

C19

C21

C23

C25

C27

C29

C31

C33

C35

C37

C39

C41

D9

D11

D13

E3

E4

E9

E11

E13

E27

E31

E35

E38

E39

G3

G7

G11

G13

G15

G17

G21

G25

G29

G35

G37

G39

G41

H11

H13

H23

H31

GND

VSS_1

VSS_63

VSS_2

VSS_64

VSS_3

VSS_65

VSS_4

VSS_66

VSS_5

VSS_67

VSS_6

VSS_68

VSS_7

VSS_69

VSS_8

VSS_70

VSS_9

VSS_71

VSS_10

VSS_72

VSS_11

VSS_73

VSS_12

VSS_74

VSS_13

VSS_75

VSS_14

VSS_76

VSS_15

VSS_77

VSS_16

VSS_78

VSS_17

VSS_79

VSS_18

VSS_80

VSS_19

VSS_81

VSS_20

VSS_82

VSS_21

VSS_83

VSS_22

VSS_84

VSS_23

VSS_85

VSS_24

VSS_86

VSS_25

VSS_87

VSS_26

VSS_88

VSS_27

VSS_89

VSS_28

VSS_90

VSS_29

VSS_91

VSS_30

VSS_92

VSS_31

VSS_93

VSS_32

VSS_94

VSS_33

VSS_95

VSS_34

VSS_96

VSS_35

VSS_97

VSS_36

VSS_98

VSS_37

VSS_99

VSS_38

VSS_100

VSS_39

VSS_101

VSS_40

VSS_102

VSS_41

VSS_103

VSS_42

VSS_104

VSS_43

VSS_105

VSS_44

VSS_106

VSS_45

VSS_107

VSS_46

VSS_108

VSS_47

VSS_109

VSS_48

VSS_110

VSS_49

VSS_111

VSS_50

VSS_112

VSS_51

VSS_113

VSS_52

VSS_114

VSS_53

VSS_115

VSS_54

VSS_116

VSS_55

VSS_117

VSS_56

VSS_118

VSS_57

VSS_119

VSS_58

VSS_120

VSS_59

VSS_121

VSS_60

VSS_122

VSS_61

VSS_123

VSS_62

VSS_124

J3

J7

J8

J39

K11

K13

K17

K19

K21

K23

K25

K27

K29

K31

L3

L7

L8

L10

L11

L15

L19

L31

L39

L41

M1

M2

N3

N7

N15

N19

N25

N29

N31

N39

P1

P2

R3

R7

R15

R19

R25

R29

R39

R41

U1

U2

U3

U7

U8

U11

U15

U19

U25

U29

U31

U39

W3

W5

W11

W15

W19

W25

W29

W39

W41

Y1

Y2

AA3

AA7

AA8

AA11

AA15

AA19

AA25

AA29

AA39

AC3

AC7

AC11

AC15

AC19

AC25

AC29

AC31

AC39

AC41

AE3

AE7

AE25

AE29

AE32

AE39

AG3

AG5

AG10

AG11

AG13

AG15

AG19

AG25

AG29

AG31

AG39

AG41

AH1

AH2

AJ3

AJ7

AJ15

AJ17

AJ19

AJ23

AJ25

AJ29

AJ31

AJ32

AJ39

AL3

AL8

AL15

AL17

AL19

AL25

AL29

VSS_188

VSS_127

VSS_189

VSS_128

VSS_190

VSS_129

VSS_191

VSS_130

VSS_192

VSS_131

VSS_193

VSS_132

VSS_194

VSS_133

VSS_195

VSS_134

VSS_196

VSS_135

VSS_197

VSS_136

VSS_198

VSS_137

VSS_199

VSS_138

VSS_200

VSS_139

VSS_201

VSS_140

VSS_202

VSS_141

VSS_203

VSS_142

VSS_204

VSS_143

VSS_205

VSS_144

VSS_206

VSS_145

VSS_207

VSS_146

VSS_208

VSS_147

VSS_209

VSS_148

VSS_210

VSS_149

VSS_211

VSS_150

VSS_212

VSS_151

VSS_213

VSS_152

VSS_214

VSS_153

VSS_215

VSS_154

VSS_216

VSS_155

VSS_217

VSS_156

VSS_218

VSS_157

VSS_219

VSS_158

VSS_220

VSS_159

VSS_221

VSS_160

VSS_222

VSS_161

VSS_223

VSS_162

VSS_224

VSS_163

VSS_225

VSS_164

VSS_226

VSS_165

VSS_227

VSS_166

VSS_228

VSS_167

VSS_229

VSS_168

VSS_230

VSS_169

VSS_231

VSS_170

VSS_232

VSS_171

VSS_233

VSS_172

VSS_234

VSS_173

VSS_235

VSS_174

VSS_236

VSS_175

VSS_237

VSS_176

VSS_238

VSS_177

VSS_239

VSS_178

VSS_240

VSS_179

VSS_241

VSS_180

VSS_242

VSS_181

VSSBG_DAC

VSS_182

VBURN

VSS_183

PSEN

AL39

AL41

AM11

AM27

AM31

AN3

AN7

AN39

AP31

AR3

AR13

AR17

AR21

AR25

AR29

AR39

AR41

AU1

AU2

AU3

AU15

AU19

AU23

AU27

AU39

AV9

AW3

AW7

AW13

AW15

AW17

AW19

AW21

AW23

AW25

AW27

AW31

AW33

AW35

AW37

AW39

AW41

AY13

AY15

AY18

AY30

BA2

BA7

BA13

BA15

BA18

BA21

BA25

BA31

BA35

BA39

A15

AL31

AM29

VSS_184

VSS_185

VSS_186

FT3 REV 0.51

FT3 REV 0.51

X4@

X4@

FT3_BGA769

FT3_BGA769

+0.95VS_APU_GFX

FT3_BGA769

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2012/04/22

2015/04/22

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

VSS_187

VSS_126

FT3 REV 0.51

Issued Date

VSS_125

VDD_095_GFX_3 AA10

VDDBT_RTC_G

X4@

VDD_18_ALW

AM15

AM17

AG23

VDD_095_2 AG27

VDD_095_3 AJ21

VDD_095_4 AJ27

VDD_095_5 AL21

VDD_095_6 AL23

VDD_095_7 AL27

VDD_095_8 AM23

VDD_095_9 AM25

VDD_095_USB3_DUAL_1

VDD_095_ALW

A2

A3

B3

C3

VDD_095_GFX_1 U10

+RTCBATT_R

+APU_CORE

VDDIO_AZ_ALW_2

VDD_18_4

C246

C250

C244

C160

C222

VDDIO_MEM_S_5

VDD_18_3

+1.8VALW

C219

C217

C220

C218

C221

C214

VDDIO_MEM_S_4

+3VALW_APU

C216

C938

C937

VDDIO_MEM_S_3

VDD_18

+1.8VS

+0.95VALW

VDDIO_MEM_S_2

VDDCR_NB_1

+0.95VALW

VDDCR_CPU_2 L23

VDDCR_CPU_3 L25

VDDCR_CPU_4 L27

VDDCR_CPU_5 L29

VDDCR_CPU_6 N21

VDDCR_CPU_7 N23

VDDCR_CPU_8 N27

VDDCR_CPU_9 R21

VDDCR_CPU_10 R23

VDDCR_CPU_11 R27

VDDCR_CPU_12 U21

VDDCR_CPU_13 U23

VDDCR_CPU_14 U27

VDDCR_CPU_15 W21

VDDCR_CPU_16 W23

VDDCR_CPU_17 W27

VDDCR_CPU_18 AA21

VDDCR_CPU_19 AA23

VDDCR_CPU_20 AA27

VDDCR_CPU_21 AC21

VDDCR_CPU_22 AC23

VDDCR_CPU_23 AC27

VDDCR_CPU_24 AE21

VDDCR_CPU_25 AE23

VDDCR_CPU_26 AE27

+1.8VALW/+1.8VS OF APU

C933

C203

L22

2

1

FBMA-L11-201209-121LMA50T_0805

VDDCR_CPU_1 L21

VDDIO_MEM_S_1

VDD_095_GFX

1U_0402_6.3V6K

1U_0402_6.3V6K

C255

C254

4.7U_0603_6.3V6K

C256

C161

UAPUG

GND

POWER

J35

L32

L37

N35

R31

R37

U32

U35

W31

W32

W37

AA31

AA35

AC32

AC37

AE31

AE35

AG32

AG37

AJ35

AL32

AL37

AR35

+1.5V

+1.5VS

C936

180P_0402_50V8J

180P_0402_50V8J

C259

180P_0402_50V8J

C258

C231

180P_0402_50V8J

C230

180P_0402_50V8J

180P_0402_50V8J

@

C207

180P_0402_50V8J

1U_0402_6.3V6K

C213

C260

1U_0402_6.3V6K

C206

1U_0402_6.3V6K

1U_0402_6.3V6K

C204

1U_0402_6.3V6K

C205

1U_0402_6.3V6K

10U_0603_6.3V6M

C199

+0.95VS_APU_GFX

VDD_095

C198

10U_0603_6.3V6M

C934

C935

+0.95VALW/+0.95VS OF APU

+0.95VS

180P_0402_50V8J

180P_0402_50V8J

C208

C210

0.1U_0402_16V7K

C211

0.1U_0402_16V7K

C932

C930

0.1U_0402_16V7K

C931

0.1U_0402_16V7K

0.1U_0402_16V7K

C929

C928

0.1U_0402_16V7K

C927

0.1U_0402_16V7K

C926

0.1U_0402_16V7K

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

C923

C949

C925

C924

VDDIO_AZ_ALW

(Could be S0 or S5 power rail)

VDDIO_MEM_S

1

1

0_0603_5%

VDD_33_ALW

PLANE SPLIT

+1.5V

1U_0402_6.3V6K

C253

VDD_33

+1.5V/+1.5VS OF APU

C252

180P_0402_50V8J

C257

1U_0402_6.3V6K

C249

180P_0402_50V8J

1U_0402_6.3V6K

C197

C194

1U_0402_6.3V6K

1U_0402_6.3V6K

C193

C191

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

C192

C202

1U_0402_6.3V6K

C201

C200

2

R582

FT3 PWR/GND

Rev

1.0

VAWGA/GB

Thursday, March 28, 2013

Sheet

E

of

37

+1.5V

DDRAB_SDQ16

DDRAB_SDQ17

DDRAB_SDQS4#

DDRAB_SDQS4

DDRAB_SDQS4#

DDRAB_SDQS4

DDRAB_SDQ34

DDRAB_SDQ35

DDRAB_SDQ40

DDRAB_SDQ41

DDRAB_SDM5

DDRAB_SDQ42

DDRAB_SDQ43

DDRAB_SDQ48

DDRAB_SDQ49

<4,9>

<4,9>

DDRAB_SDQS6#

DDRAB_SDQS6

DDRAB_SDQS6#

DDRAB_SDQS6

DDRAB_SDQ50

DDRAB_SDQ51

DDRAB_SDQ56

DDRAB_SDQ57

DDRAB_SDM7

DDRAB_SDQ58

DDRAB_SDQ59

R69

10K_0402_5%

1

2

+3VS

R70

+3VS

2

10K_0402_5%

C135

2.2U_0603_6.3V6K

C136

0.1U_0402_16V4Z

205

G1

G2

DDRAB_SMA6

DDRAB_SMA4

+1.5V

R65

20K_0402_1%

DDRAB_SMA2

DDRAB_SMA0

DDRA_ODT1

VREF for DIMM1,2

+1.5V

DDRA_SCS0#

DDRA_ODT0

DDRAB_SMA11

DDRAB_SMA7

DDRAB_SBS1#

DDRAB_SRAS#

4.7U_0603_6.3V6K

<4,9>

<4,9>

<4>

DDRA_CKE1

DDRAB_SMA15

DDRAB_SMA14

DDRA_CLK1

DDRA_CLK1#

0.1U_0402_16V4Z

DDRAB_SDQ32

DDRAB_SDQ33

C127

DDRAB_SMA13

DDRA_SCS1#

C126

DDRA_SCS1#

0.1U_0402_16V4Z

<4>

0.1U_0402_16V4Z

DDRAB_SWE#

DDRAB_SCAS#

DDRAB_SWE#

DDRAB_SCAS#

C123

<4,9>

<4,9>

DDRAB_SMA10

DDRAB_SBS0#

0.1U_0402_16V4Z

DDRAB_SBS0#

C122

<4,9>

DDRA_CLK0

DDRA_CLK0#

DDRA_CKE1

0.1U_0402_16V4Z

DDRA_CLK0

DDRA_CLK0#

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

C121

<4>

<4>

0.1U_0402_16V4Z

DDRAB_SMA3

DDRAB_SMA1

CKE1

VDD2

A15

A14

VDD4

A11

A7

VDD6

A6

A4

VDD8

A2

A0

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

S0#

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

DDRAB_SDQ30

DDRAB_SDQ31

C120

DDRAB_SMA8

DDRAB_SMA5

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

<4,9>

<4,9>

DDRAB_SDQS3#

DDRAB_SDQS3

0.1U_0402_16V4Z

DDRAB_SMA12

DDRAB_SMA9

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

DDRAB_SDQS3#

DDRAB_SDQS3

C119

DDRAB_SBS2#

DDRAB_SDQ28

DDRAB_SDQ29

0.1U_0402_16V4Z

DDRAB_SBS2#

DDRA_CKE0

DDRAB_SDQ22

DDRAB_SDQ23

C118

DDRA_CKE0

<4,9>

+0.75VS

0.1U_0402_16V4Z

<4>

2

+1.5V

DDRAB_SDM2

C117

DDRAB_SDQ26

DDRAB_SDQ27

DDRAB_SDQ20

DDRAB_SDQ21

0.1U_0402_16V4Z

DDRAB_SDM3

+1.5V/+0.75VS OF DIMM1

0.1U_0402_16V4Z

DDRAB_SDQ24

DDRAB_SDQ25

<4,9>

MEM_MAB_RST#

DDRAB_SDQ14

DDRAB_SDQ15

C116

DDRAB_SDQ18

DDRAB_SDQ19

DDRAB_SDM1

MEM_MAB_RST#

C115

DDRAB_SDQS2#

DDRAB_SDQS2

DDRAB_SDQ12

DDRAB_SDQ13

C114

<4,9>

<4,9>

DDRAB_SDQS2#

DDRAB_SDQS2

<4,9>

DDRAB_SDQ6

DDRAB_SDQ7

DDRAB_SDQ10

DDRAB_SDQ11

<4,9>

DDRAB_SMA[0..15]

DDRA_CLK1

DDRA_CLK1#

<4>

<4>

DDRAB_SBS1#

DDRAB_SRAS#

<4,9>

<4,9>

DDRA_SCS0#

DDRA_ODT0

<4>

<4>

DDRA_ODT1

<4>

+VREF_DQ

R66

1K_0402_1%

+VREF_CA

DDRAB_SDQS1#

DDRAB_SDQS1

DDRAB_SMA[0..15]

<4,9>

DDRAB_SDQS1#

DDRAB_SDQS1

DDRAB_SDQS0#

DDRAB_SDQS0

DDRAB_SDQ[0..63]

DDRAB_SDM[0..7]

R67

20K_0402_1%

R68

1K_0402_1%

1

<4,9>

<4,9>

<4,9>

<4,9>

DDRAB_SDQ8

DDRAB_SDQ9

DDRAB_SDM[0..7]

DDRAB_SDQS0#

DDRAB_SDQS0

DDRAB_SDQ[0..63]

DDRAB_SDQ4

DDRAB_SDQ5

DDRAB_SDQ2

DDRAB_SDQ3

VSS1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

RESET#

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

DDRAB_SDM0

VREF_DQ

VSS2

DQ0

DQ1

VSS4

DM0

VSS5

DQ2

DQ3

VSS7

DQ8

DQ9

VSS9

DQS#1

DQS1

VSS11

DQ10

DQ11

VSS13

DQ16

DQ17

VSS15

DQS#2

DQS2

VSS18

DQ18

DQ19

VSS20

DQ24

DQ25

VSS22

DM3

VSS23

DQ26

DQ27

VSS25

15mil

+VREF_CA

DDRAB_SDQ36

DDRAB_SDQ37

DDRAB_SDM4

DDRAB_SDQ38

DDRAB_SDQ39

DDRAB_SDQ44

DDRAB_SDQ45

DDRAB_SDQS5#

DDRAB_SDQS5

C167

DDRAB_SDQ0

DDRAB_SDQ1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

C134

C142

C176

JDIMM1

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

0.1U_0402_16V4Z

1000P_0402_50V7K

0.1U_0402_16V4Z

+1.5V

15mil

1000P_0402_50V7K

+VREF_DQ

1

3

DDRAB_SDQS5#

DDRAB_SDQS5

<4,9>

<4,9>

DDRAB_SDQS7#

DDRAB_SDQS7

<4,9>

<4,9>

MEM_MAB_EVENT#

APU_SDATA0

APU_SCLK0

<4,9>

<16,6,9>

<16,6,9>

DDRAB_SDQ46

DDRAB_SDQ47

DDRAB_SDQ52

DDRAB_SDQ53

DDRAB_SDM6

DDRAB_SDQ54

DDRAB_SDQ55

DDRAB_SDQ60

DDRAB_SDQ61

DDRAB_SDQS7#

DDRAB_SDQS7

DDRAB_SDQ62

DDRAB_SDQ63

MEM_MAB_EVENT#

+0.75VS

4

206

FOX_AS0A626-U8SN-7F

ME@

2012/04/22

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

DIMM_A H:8mm

2015/04/22

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

<Address: 00>

Date:

DDR3 SODIMM-I Socket

Rev

1.0

VAWGA/GB

Thursday, March 28, 2013

Sheet

E

of

37

+VREF_DQ

+1.5V

DDRAB_SDQS1#

DDRAB_SDQS1

DDRAB_SDQS1#

DDRAB_SDQS1

DDRAB_SDQ10

DDRAB_SDQ11

DDRAB_SDQ16

DDRAB_SDQ17

DDRAB_SDQ40

DDRAB_SDQ41

DDRAB_SDM5

DDRAB_SDQ42

DDRAB_SDQ43

DDRAB_SDQ48

DDRAB_SDQ49

<4,8>

<4,8>

DDRAB_SDQS6#

DDRAB_SDQS6

DDRAB_SDQS6#

DDRAB_SDQS6

DDRAB_SDQ50

DDRAB_SDQ51

DDRAB_SDQ56

DDRAB_SDQ57

DDRAB_SDM7

DDRAB_SDQ58

DDRAB_SDQ59

R71

10K_0402_5%

1

2

+3VS

1

R72

2

10K_0402_5%

205

G1

4.7U_0603_6.3V6K

DDRAB_SDQ34

DDRAB_SDQ35

0.1U_0402_16V4Z

DDRAB_SDQS4#

DDRAB_SDQS4

C158

DDRAB_SDQS4#

DDRAB_SDQS4

C175

<4,8>

<4,8>

0.1U_0402_16V4Z

DDRAB_SDQ32

DDRAB_SDQ33

0.1U_0402_16V4Z

DDRB_SCS1#

DDRAB_SMA13

DDRB_SCS1#

C172

<4>

DDRAB_SWE#

DDRAB_SCAS#

DDRAB_SWE#

DDRAB_SCAS#

DDRB_CKE1

0.1U_0402_16V4Z

<4,8>

<4,8>

DDRAB_SBS0#

DDRAB_SMA10

DDRAB_SBS0#

C171

<4,8>

DDRB_CLK0

DDRB_CLK0#

<4,8>

<4,8>

DDRAB_SDQS3#

DDRAB_SDQS3

DDRAB_SDQ30

DDRAB_SDQ31

0.1U_0402_16V4Z

<4>

<4>

DDRB_CLK0

DDRB_CLK0#

DDRAB_SDQS3#

DDRAB_SDQS3

C170

DDRAB_SMA3

DDRAB_SMA1

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

CKE1

VDD2

A15

A14

VDD4

A11

A7

VDD6

A6

A4

VDD8

A2

A0

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

S0#

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

DDRAB_SDQ28

DDRAB_SDQ29

0.1U_0402_16V4Z

DDRAB_SMA8

DDRAB_SMA5

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

DDRAB_SDQ22

DDRAB_SDQ23

C169

DDRAB_SMA12

DDRAB_SMA9

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

+0.75VS

0.1U_0402_16V4Z

DDRAB_SBS2#

+1.5V

+1.5V

DDRAB_SDM2

C168

DDRAB_SBS2#

DDRB_CKE0

DDRAB_SDQ20

DDRAB_SDQ21

0.1U_0402_16V4Z

DDRB_CKE0

+1.5V/+0.75VS OF DIMM2

C165

<4,8>

<4,8>

MEM_MAB_RST#

DDRAB_SDQ14

DDRAB_SDQ15

0.1U_0402_16V4Z

<4>

DDRAB_SDM1

MEM_MAB_RST#

C162

DDRAB_SDQ26

DDRAB_SDQ27

<4,8>

0.1U_0402_16V4Z

DDRAB_SDM3

<4,8>

DDRAB_SMA[0..15]

DDRAB_SDQ12

DDRAB_SDQ13

0.1U_0402_16V4Z

DDRAB_SDQ24

DDRAB_SDQ25

DDRAB_SDM[0..7]

DDRAB_SDQ6

DDRAB_SDQ7

C132

DDRAB_SDQ18

DDRAB_SDQ19

DDRAB_SMA[0..15]

C155

DDRAB_SDQS2#

DDRAB_SDQS2

DDRAB_SDQS0#

DDRAB_SDQS0

C133

<4,8>

<4,8>

DDRAB_SDQS2#

DDRAB_SDQS2

<4,8>

<4,8>

1

C644

DDRAB_SDQ8

DDRAB_SDQ9

DDRAB_SDQ[0..63] <4,8>

DDRAB_SDM[0..7]

DDRAB_SDQS0#

DDRAB_SDQS0

+

2

220U_6.3V_M

DDRAB_SDQ2

DDRAB_SDQ3

DDRAB_SDQ[0..63]

DDRAB_SDQ4

DDRAB_SDQ5

<4>

DDRB_CKE1

DDRAB_SMA15

DDRAB_SMA14

DDRAB_SMA11

DDRAB_SMA7

DDRAB_SMA6

DDRAB_SMA4

DDRAB_SMA2

DDRAB_SMA0

DDRB_CLK1

DDRB_CLK1#

DDRAB_SBS1#

DDRAB_SRAS#

DDRB_SCS0#

DDRB_ODT0

DDRB_ODT1

DDRB_CLK1

DDRB_CLK1#

<4>

<4>

DDRAB_SBS1#

DDRAB_SRAS#

<4,8>

<4,8>

DDRB_SCS0#

DDRB_ODT0

<4>

<4>

DDRB_ODT1

<4>

15mil

+VREF_CA

DDRAB_SDQ36

DDRAB_SDQ37

DDRAB_SDM4

DDRAB_SDQ38

DDRAB_SDQ39

DDRAB_SDQ44

DDRAB_SDQ45

DDRAB_SDQS5#

DDRAB_SDQS5

C174

VSS1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

RESET#

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

C139

DDRAB_SDM0

VREF_DQ

VSS2

DQ0

DQ1

VSS4

DM0

VSS5

DQ2

DQ3

VSS7

DQ8

DQ9

VSS9

DQS#1

DQS1

VSS11

DQ10

DQ11

VSS13

DQ16

DQ17

VSS15

DQS#2

DQS2

VSS18

DQ18

DQ19

VSS20

DQ24

DQ25

VSS22

DM3

VSS23

DQ26

DQ27

VSS25

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

0.1U_0402_16V4Z

DDRAB_SDQ0

DDRAB_SDQ1

C143

C177

+1.5V

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

1000P_0402_50V7K

<4,8>

<4,8>

1000P_0402_50V7K

0.1U_0402_16V4Z

1

JDIMM2

15mil

1

3

DDRAB_SDQS5#

DDRAB_SDQS5

<4,8>

<4,8>

DDRAB_SDQS7#

DDRAB_SDQS7

<4,8>

<4,8>

MEM_MAB_EVENT#

APU_SDATA0

APU_SCLK0

<4,8>

<16,6,8>

<16,6,8>

DDRAB_SDQ46

DDRAB_SDQ47

DDRAB_SDQ52

DDRAB_SDQ53

DDRAB_SDM6

DDRAB_SDQ54

DDRAB_SDQ55

DDRAB_SDQ60

DDRAB_SDQ61

DDRAB_SDQS7#

DDRAB_SDQS7

DDRAB_SDQ62

DDRAB_SDQ63

MEM_MAB_EVENT#

+0.75VS

4

206

G2

FOX_AS0A626-U4SN-7F

ME@

2012/04/22

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

DIMM_B H:4mm

2015/04/22

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

<Address: 10>

Date:

DDR3 SODIMM-II Socket

Rev

1.0

VAWGA/GB

Thursday, March 28, 2013

Sheet

E

of

37

+5V_Display

U73

+3VS

+5VS

OUT

1

C543

GND

<4>

<4>

DP2_TXP1

DP2_TXN1

<4>

<4>

DP2_TXP2

DP2_TXN2

<4>

<4>

DP2_TXP3

DP2_TXN3

HDMI_TX2P

HDMI_TX2N

DP2_TXP1

DP2_TXN1

C53 HDMI@ 1

C54 HDMI@ 1

2 0.1U_0402_16V7K

2 0.1U_0402_16V7K

HDMI_TX1P

HDMI_TX1N

DP2_TXP2