Академический Документы

Профессиональный Документы

Культура Документы

Register Description Guideline

Загружено:

Mai KhoaАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Register Description Guideline

Загружено:

Mai KhoaАвторское право:

Доступные форматы

ARRIVE TECHNOLOGIES

REGISTER DESCRIPTION

GUIDELINE

This controlled document is the proprietary of Arrive

Technologies Inc. Any duplication, reproduction, or

transmission to unauthorized parties is prohibited.

Copyright 2015

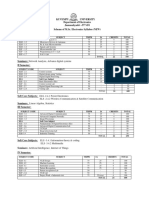

Contents

Revision History

Scope

1 What is a Arrive Technologies Register description file?

2 Guideline for naming atreg file

3 Partition the whole chip registers

3.1 Partition the whole chip registers to small block registers

3.2 Register types

4 Arrive Technologies Register description file

4.1 Specical characters

4.1.1 Comment out by key words # or //#

4.1.2 Delimiter character between parameters by %%

4.2 Indicate Start of a new register declared by key word Begin:

4.3 Register Full Name

4.4 RTL Instant Name

4.5 Address

4.6 Formula

4.7 Where

4.8 Option

4.9 Description

4.10 HDL_PATH

4.11 Width

4.12 Register Type

4.13 Field

4.14 Indicate End of register by key word End:

5 addrmap file

1

2

3

4

5

5

5

6

6

6

7

7

7

7

7

8

9

9

11

12

13

14

14

16

17

Revision History

Revision History

Revision

Date

Author

Description

1.0

Oct.30,

2014

dienlc@atvn.com.vn

First Edition

1.1

Aug.05,

2015

dienlc@atvn.com.vn

Added HDL_PATH declaration for register, which will be used for

backdoor configuration. Update format for addrmap file to add

more options

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 3 of 20

Scope

Scope

An Arrive Technologies Register description file (atreg file) is a source file which will be fed to the following

generators to generate database for some environments

SDK database Generator: Generate Macros, data structs for SDK.

Register Model Generator: Generate database (Register Model) for TestBench environement.

Register Description Docement Generator.

Because the Generators are automatic tools, so atreg MUST BE FOLLOWED template. This is guideline about

how to create an Arrive Technologies Register description file (atreg file).

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 4 of 20

1 What is a Arrive Technologies Register description file?

1 What is a Arrive Technologies Register description

file?

That is a file with extension .atreg which contains registers defined for a sub-block/block/chip.

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 5 of 20

2 Guideline for naming atreg file

2 Guideline for naming atreg file

A file name MUST satisfy all the following rules:

File name should convey general infomartion of the sub-block/block/chip which the file represent for.

Recommendation format should be: <product>_<block>_<subblock>*_RD.atreg

Only combined by these characters {A-Z, a-z, 09, _}

No any space character

The first character must be a literal character or underscore (_)

File extension MUST be atreg

Example: af5top_pklut_rd.atreg

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 6 of 20

3 Partition the whole chip registers

3 Partition the whole chip registers

3.1 Partition the whole chip registers to small block registers

A chip may be from hundreds to several hundred thousand registers

A chip can be divided into several blocks by functions. So its a good idea to partition the whole chip

registers to small parts based on their functions, each part is contained in a file that we call a register

description file. Here are guidelines for this partition

Each file just contains registers for only one block/sub-block.

Each file MUST be defined an address offset (MIN_ADDRESS) (this actually is address offset of

block/sub-block from view of top level). This address offset will be added to address of every register in

the file to create final address.

Each file MUST be defined an MAX_ADDRESS. The final address of any register in the file MUST

not be more than this MAX_ADDRESS. Thus we have range of address for the file is

[MIN_ADDRESS:MAX_ADDRESS]

The range address of register file [MIN_ADDRESS:MAX_ADDRESS] MUST not overlap range of

address of any another.

3.2 Register types

A register can be a single type of mixed multiple types from the list below.

TYPE_LIST=[Reset, Config, Status, Interrupt]

Reset: Registers are used for chip/block soft reset purpose. We should collect all block soft reset

bits and put into a same register.

Config: Registers are used for setting up operation of chip.

Status: As counters, or status of chip at a time.

Interrupt: Registers are used for requesting interrupt.

But with a design where the registers are well organized, register should be included one and only

one type for all fields. Should not mix multiple types. This will brings some benefits

Create a good sense of intuition.

Easier to build up/organize SDK and Testbench environment.

Optimize SDK and Testbench environment.

Reduce CPU access time during operation.

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 7 of 20

4 Arrive Technologies Register description file

4 Arrive Technologies Register description file

Identifying a new register defined by a line started with the string Begin:. A register defined is wrapped by

couple key words (Begin: End:)

The format of a resiter looks like below:

######################################################################################

// Begin:

# Some description

// Register Full Name: Device Version ID

// RTL Instant Name: VersionID

//# {FunctionName,SubFunction_InstantName_Description}

//# RTL Instant Name and Full Name MUST be unique within a register description

file

// Address : 0x00_0000

//# Address is relative address, will be sum with Base_Address for each function

block

// Formula : Address + $portid

// Where : {$portid(07): port identification}

// Description : This register indicates the module name and version.

// HDL_PATH : Define an HDL_PATH for option backdoor access to register

// Width: 32

// Register Type: {Status}

//# Field: [Bit:Bit] %% Name %% Description %% Type %% Reset %% Default

// Field: [31:24] %% Year %% 2013 %% RO %% 0x0D %% 0x0D

// Field: [23:16] %% Week %% Week Synthesized FPGA %% RO %% 0x0C %%

0x0C

// Field: [15:8] %% Day %% Day Synthesized FPGA %% RO %% 0x16 %%

0x16

// Field: [7:4] %% VerID %% FPGA Version %% RO %% 0x0 %% 0x0

// Field: [3:0] %% NumID %% Number of FPGA Version %% RO %% 0x1 %%

0x1

//End:

######################################################################################

Define some key words which will be used in the next sections

Every OPTION/KEY_WORD will be put in the square bracket []

[MUST]: Indicate field/option MUST be defined

[OPTION]: Indicate field/option MAY be defined

[SYNTAX]: Where to define syntax/format of attribute

4.1 Specical characters

4.1.1 Comment out by key words # or //#

Comment out by inserting # or //# at beginning of the line. Lines comment out will be ignored from parsers.

EXAMPLE

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 8 of 20

4 Arrive Technologies Register description file

#-

# This is line which is commented out by key word #

//# This is line which is commented out by key word //#

#-

4.1.2 Delimiter character between parameters by %%

EXAMPLE

//Address: addr1 %% addr2

4.2 Indicate Start of a new register declared by key word Begin:

[MUST]

This is a single line which contain key word Begin:.

[SYNTAX]

//[Begin:] [any string, dont care]

[Begin:] is KEW_WORD: to identify a new register defined

NOTE:

The currenlt parser tools also support detecting line Register Full Name: as beginning register declared. But

you SHOULD NOT use this option, you SHOULD use couple key words (Begin:End:) for more

explicitly.

4.3 Register Full Name

[MUST]

This is a single line to define full/long name of register

[SYNTAX]

//[Register Full Name:] [any string]

[Register Full Name:] is KEW_WORD, to identify a new register defined

[any string] is the full/long name of register. This full name may be used to generated the PDF file

later

4.4 RTL Instant Name

[MUST]

This is a single line to define instance/short name of register

[SYNTAX]

//[RTL Instant Name:] [register_instance_name]

[RTL Instant Name:] is KEY_WORD, to identify register instantiated name

[register_instance_name] is instatiated name of the register. This name will be used to define class

name of register. The register_instance_name MUST FOLLOW syntax of signal in verilog

4.5 Address

[MUST]

This is a single line to define address of register

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 9 of 20

4 Arrive Technologies Register description file

[SYNTAX]

Format 1: For a single register -> single address

//[Address:] [min_address]

Format 2: For an array of registers -> range of address

//[Address:] [min_address - max_address]

[Address:] is KEY_WORD: to identify address of register declared

(min_address, max_address) are hexadecimal numbers, prefixed with 0x

Can use underscore. Ex: 0x35_0000

Can be a single address. Ex: 0x35_0000

Can be a range of address. Ex: 0x35_00000x35_FFFF

These three extra-formats below are supported, but not recommended to use (Because every register can

be declared by Format1 and Format2):

Format 3: For a single register and access policy is pre-declared

//[Address:] [min_address(access_policy)]

access_policy is as defined in the table [Pre-defined Field Access Policies][Pre-defined Field

Access Policies] in section [4.12][4.12]

For this format this access policy will override access policy declared in field [4.12][4.12]

Example:

//Address: 0x35_0000(RO)

Format 4: For a single register but can be accessed through many addresses. This is called a shared

address register

//[Address:] [min_address1(access_policy)] %% [min_address2(access_policy)]

access_policy is as defined in the table [Pre-defined Field Access Policies][Pre-defined Field

Access Policies] in section [4.12][4.12]

Example:

//Address: 0x35_0000(RO) %% 0x70_000(RC)

Format 5: Shared address register for an array

//[Address:] [min_address1 - max_address1(access_policy1)] %% [min_address2 max_address2(access_policy)]

access_policy is as defined in the table [Pre-defined Field Access Policies][Pre-defined Field

Access Policies] in section [4.12][4.12]

Example:

//Address: 0x35_00000x35_00FF(RO) %% 0x70_00000x70_00FF(RC)

4.6 Formula

[OPTION]

This is a single line to define address of register which is obtained by a formula.

If the Fomula is present, then the final address of register will be obtained from this Formula.

If the keyword Address is present in the Formula, then this Address will be replaced by [min_address}

value in the section 4.5.

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 10 of 20

4 Arrive Technologies Register description file

Else the address defined in the section 4.5 will be ignore.

[SYNTAX]

//[Formula:][address_formula]

[Formula:] is KEY_WORD: to identify if a formula present

[address_formula:] currently supporting only {+,-,,/}* operators

In the formula we can use variables/index/iterate, and if these variables are present then they MUST

be defined in the Where: area as defined in the section 4.7

[EXAMPLE]

//Formula: Address+port_id

4.7 Where

[OPTION]

This is a single line to define variables/index/iterate which are used in the formula in 4.6

[SYNTAX]

//[Where:][{$var1(min_value-max_value): var1 description}] [ %% {$var2(min_value-max_value): var2

description}][%% more ...]

[Where:] is KEY_WORD: to identify if a Where line is present

We dont limit number of variables

Informaton of a variable is put inside {}

Delimiter character between variables by %%

4.8 Option

[OPTION]

This is a single line to define modality which is used to access to register.

Currently we define 2 modalities to access register:

Direct access mode for direct access registers

Indirect access mode for indirect access registers

Direct registers:

Registers are mapped in the address map and can be accessed directly from address mapped.

Indirect registers:

Some registers are not mapped in the address map and can only be accessed indirectly. In other words,

reading and writing of unmapped registers is done through mapped registers. For example, you could read

from an unmapped register by writing the address into a mapped address register and then reading the data

from a data register.

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 11 of 20

4 Arrive Technologies Register description file

Figure 6-1 - Indirect Register

Defaultly If missing this line then the register will be accessed direct mode. If this is present then a indirect

register is defined

[SYNTAX]

//[Option:] [:indirect_register: <indirect_addr_register> %%

<addr_field_name_in_indirect_address_register> %% <indirect_data_register>]

[Option:] is KEY_WORD: to identify if a extra option present

<:indirect_register:> is KEY_WORD to indicate that this is an indirect access register

<indirect_addr_register> is instance name of indirect address register

<addr_field_name_in_indirect_address_register>: This is field name of <indirect_addr_register>

which will be used to contain address of indirect access regiter

<indirect_data_register> is instance name of indirect data register

Use %% delimiter character to split parameters

[EXAMPLE]

The hash table 65Kx64bits of the classifier block is implemted with indirect access mode. The table can be

accessed use two register.

Indirect Address Register is declared as below.

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 12 of 20

4 Arrive Technologies Register description file

######################################################################################

// Begin:

// Register Full Name: Hash Table Indirect Address Register

// RTL Instant Name: hash_indrect_addr

// Address : 0x30_0000

// Description : Indirect Address Register for accessing HASH table of Classifier

block

// Width: 32

// Register Type: {Status}

// Field: [31:18] %% Reserved %% Reserved %% RO %% 0x0C %% 0x0C

// Field: [17:17] %% Done %% 0: Not done, 1: Done %% RO %% 0x16 %%

0x16

// Field: [16:16] %% Read_Not_Write %% 0: Read, 1: Write %% RW %% 0x0

%% 0x0

// Field: [15:0] %% hash_idx %% hash index for access table %% RW %% 0x0

%% 0x0

//End:

######################################################################################

Indirect Data Register name: hash_indirect_data

######################################################################################

// Begin:

// Register Full Name: Hash Table Indirect Data Register

// RTL Instant Name: hash_indrect_data

// Address : 0x30_0001

// Description : Indirect Data for accessing HASH table of Classifier block

// Width: 64

// Register Type: {Status}

// Field: [63:0] %% info %% info %% RW %% 0x0 %% 0x0

//End:

######################################################################################

Then we can declare the hash table as below:

######################################################################################

// Begin:

// Register Full Name: Hash Table Indirect Data Register

// RTL Instant Name: hash_indrect_data

// Address : 0x00_0000 - 0x00_FFFF

// Description : Indirect Data for accessing HASH table of Classifier block

// Option: indirect_register: hash_indirect_addr %% hash_index %%

hash_indirect_data

// Width: 64

// Register Type: {Config}

// Field: [63:0] %% hash_entry %% hash entry %% RW %% 0x0 %% 0x0

//End:

######################################################################################

4.9 Description

[OPTION]

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 13 of 20

4 Arrive Technologies Register description file

This is a single line or multiple line to put more description about this register

[NOTE]: Identifying description in the next line by key word %% at the end of current line

[SYNTAX]

//[Description:] [Any description]

[Description:] is KEY_WORD: to identify if a Description of register present

[Any description] is where to put description for this register

This information may be used to generate RD file

4.10 HDL_PATH

[OPTION]

This is a single line to declare an relative HDL_PATH of register. This HDL_PATH will be concatenated with

HDL_ROOT_PATH to form a FULL_PATH for register. HDL_ROOT_PATH is declared in the addrmap file for

every block.

We split HDL_PATH of any register/ram/array into to three sub-HDL_PATH, and they will be constructed to

create a full HDL_PATH from top module down to that register/ram/array

FULL_HDL_PATH=RGM_HDL_ROOT_PATH.CORE_HDL_PATH.REG_HDL_PATH

TOP_HDL_PATH: is defined by a verilog defined macro that will be fed to Simulator. Commonly we

add `RGM_HDL_ROOT_PATH macro to proj_top_ben.f. Example: proj_top_ben.f:-define

RGM_HDL_ROOT_PATH=testtop.AF6CCI0012.af6cci0012rtlcore

CORE_HDL_PATH: is defined per (RTL block/RD file) under the design top-core, this parameter is

defined in proj_top.addrmap file . Example: inst_type:AF5ACC_CE08_RD_GLBR

hdl_path:GLBL_INST[].glbl

REG_HDL_PATH: is defined per register/ram/array in the RD file by field HDL_PATH and is

described as below

[SYNTAX]

//[HDL_PATH:] [hierarchy path]

EXAMPLE 1 Single register

OCN block has module core with name module ocnrtlcore

Block module framer is instantiated in the ocnrtlcore module with name: iocn_framer

Inside the framer module we have a register interrupt enable which is instantiated with name

reg_interrupt_enable

Then the HDL_PATH for this register will be declared as below:

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 14 of 20

4 Arrive Technologies Register description file

#################################################################################

# ************

# * Diagnostic DDR Error Counter*

# ************

// Register Full Name: OCN Interrupt Enable

// RTL Instant Name : ddr_status_cnt

// Address : 0x12

// Formula :

// Where :

// Description : this register is number of value error data when compare between

data read & data has been written, and indicate valid counter data

//HDL_PATH: icon_framer.reg_insterrupt_enable

// Width : 32

// Register Type: {Counter}

//#Field: [Bit:Bit] %% Name %% Description %% Type %% Reset %% Default

// Field: [31:0] %% interrupt_en %% interrupt enable %% RW %% 0x0 %% 0x0

The OCN block is instantiated in the module rtltop with name iocncore

The rtltop is instantiated in testtop module with name irtltop

Then finally the FULL_HDL_PATH will be: testtop.irtltop.iocncore.icon_framer.reg_insterrupt_enable

EXAMPLE 2: Array of registers

#################################################################################

# ************

# * Diagnostic DDR Error Counter*

# ************

// Register Full Name: Diagnostic Error & Valid DDR Counter

// RTL Instant Name : ddr_status_cnt

// Address : 0x12

// Formula : {0x12 + $DID}

// Where : {$DID(03): ID DDR}

// Description : this register is number of value error data when compare between

data read & data has been written, and indicate valid counter data

// HDL_PATH : ddr_status_cnt.array[$DID]

// Width : 32

// Register Type: {Counter}

//#Field: [Bit:Bit] %% Name %% Description %% Type %% Reset %% Default

// Field: [31:16] %% err_data_cnt %% value of error data counter %% R_O %%

0x0 %% 0x0

// Field: [15:0] %% valid_data_cnt %% value of error data counter, if valid

counter doesnt have value 0, DDR is running %% R_O %% 0x0 %% 0x0

EXAMPLE 3: Array in Array registers

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 15 of 20

4 Arrive Technologies Register description file

#################################################################################

# ************

# * PACKET EDITOR By Pass Configuration*

# ************

// Register Full Name: PACKET EDITOR By Pass Configuration

// RTL Instant Name : icfg_editbypass

// Address : 0x17

// Formula : {0x17 + idx164 + idx28 + idx3}

// Where : {$idx1(03): index 1} %% {$idx2(07): index 2} %% {$idx3(07):

index 3}

// Description : this register is used to enable the By Pass mode for Packet Editor

// HDL_PATH : icfg_editbypass.block_A[$idx1].block_B[$idx2].ram.ram[$idx3]

// Width : 32

// Register Type: {Config}

//#Field: [Bit:Bit] %% Name %% Description %% Type %% Reset %% Default

// Field: [31:01] %% Unused %% NA %% RW %% 0x0 %% 0x0

// Field: [0] %% PktEditByPassEn %% ByPass Packet Editor Enable %% R/W

%% 0x0 %% 0x0

4.11 Width

[MUST]

This is a single line to indicate size in bit of the register. The number of bit MUST be multiple of 16

[SYNTAX]

//[Width:] [decimal_number]

[Width:] is KEY_WORD: to identify Width defined

[decimal_number] This is number of bits of this register. The number of bit MUST be multiple of 16

4.12 Register Type

[MUST]

This is a single line to indicate types of register. It can be a single type or mixed many types in the list below

as indicated in 3.2. Use cases and mapping field access policy to Register Type is as indicated in the table

[Table Pre-defined Field Access Policies][Table Pre-defined Field Access Policies]

[SYNTAX]

//[Register Type:] [{Type1|Type2|}]

[Register Type:] is KEY_WORD: to identify a Register Type defined

Type1,Type2: A single type in the TYPE_LIST above

EXAMPLE

Register is defined with a single type:

//Register Type: {Config}

Register is defined with a mixed multiple of types:

//Register Type: {Reset|Config|Status|Interrupt}

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 16 of 20

4 Arrive Technologies Register description file

4.13 Field

[MUST]

This is a single line or muliple lines to define a field. A register may include a single or multiple fields. A

searching machine will search untill found 5 keys of %%

[SYNTAX]

//[Field:] [bit_range] %% [field_name] %% [field_description] %% [access_policy] %%

[field_soft_reset_value] %% [field_hard_reset_value]

Any field defined MUST be included all parameters as above

[Field:] is KEY_WORD: to identify a Field defined

[bit_range]: is bit range of this field in the register. There are 2 formats of this field that will be

explained further as below.

For a single bit then format is: [bit], Ex: [15], or [15:15]

For a range of bit then format is: [high:low], Ex: [15:13]

[field_name] is name of field, need follow verilog signal name syntax. The field_name SHOULD BE

NAMED same as actual signal name in RTL code. This is a good definition that we can use this name

for searching RTL code in debug later on

[field_description]: Should put at least a short descripton for field

[access_policy]: Current access policy is supported as the list below

[field_soft_reset_value]: This is software reset value (loaded by software write).

[field_hard_reset_value]: This is hardware reset value (loaded when reset signal).

Table Pre-defined Field Access Policies

Description

Effect of a Write on Current

Field Value

Effect of a

Read on

Current

Field Value

Status

Read Only

No effect

No effect

RW

Config

Read, Write

Changed to written value

No effect

RC

Status

Read Clears

All

No effect

RS

UNKNOW

Read Sets All

No effect

WRC

UNKNOW

WRS

UNKNOW

WC

Status

Write, Read

Clears All

Write, Read

Sets All

Write Clears

All

WS

Status

Write Sets All

WSRC

UNKNOW

WCRS

UNKNOW

Access

Policy

Use

Case

RO

Write Sets

All, Read

Clears All

Write Clears

All,Read Sets

All

2015 Arrive All Rights Reserved

Changed to written value

Changed to written value

Sets

0s

Sets

1s

Sets

0s

Sets

1s

all bits to

all bits to

all bits to

all bits to

Readback

Value

Current

Value

Current

value

Current

value

Current

value

Current

value

Current

value

Current

value

Current

value

Sets all bits to 0s

No effect

Sets all bits to 1s

No effect

Sets all bits to 1s

Sets all bits to

0s

Current

value

Sets all bits to 0s

Sets all bits to

1s

Current

value

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 17 of 20

4 Arrive Technologies Register description file

Access

Policy

Use

Case

Description

W1C

Interrupt

Write 1 to

Clear

W1S

Interrupt

Write 1 to

Set

W1T

UNKNOW

Write 1 to

Toggle

W0C

Interrupt

Write 0 to

Clear

W0S

Interrupt

Write 0 to

Set

W0T

UNKNOW

Write 0 to

Toggle

W1SRC

UNKNOW

Write 1 to

Set, Read

Clears All

W1CRS

UNKNOW

Write 1 to

Clear, Read

Sets All

W0SRC

UNKNOW

Write 0 to

Set, Read

Clears All

W0CRS

UNKNOW

Write 0 to

Clear, Read

Sets All

WO

Config

WOC

UNKNOW

WOS

UNKNOW

W1

UNKNOW

Write Once

WO1

UNKNOW

Write Only,

Once

Write Only

Write Only

Clears All

Write Only

Sets All

Effect of a

Read on

Current

Field Value

Readback

Value

No effect

Current

Value

No effect

Current

value

No effect

Current

value

No effect

Current

value

No effect

Current

value

No effect

Current

value

Sets all bits to

0s

Current

value

Sets all bits to

1s

Current

value

Sets all bits to

0s

Current

value

Sets all bits to

1s

Current

value

No effect

Undefined

Sets all bits to 0s

No effect

Undefined

Sets all bits to 1s

No effect

Undefined

No effect

Current

value

No effect

Undefined

Effect of a Write on Current

Field Value

If the bit in the written value is a 1,

the cor-responding bit in the field is

set to 0. Other-wise, the field bit is not

affected

If the bit in the written value is a 1,

the cor-responding bit in the field is

set to 1. Other-wise, the field bit is not

affected

If the bit in the written value is a 1,

the cor-responding bit in the field is

inverted. Other-wise, the field bit is not

affected

If the bit in the written value is a 0,

the cor-responding bit in the field is

set to 0. Other-wise, the field bit is not

affected

If the bit in the written value is a 0,

the cor-responding bit in the field is

set to 1. Other-wise, the field bit is not

affected

If the bit in the written value is a 0,

the cor-responding bit in the field is

inverted. Other-wise, the field bit is not

affected

If the bit in the written value is a 1,

the cor-responding bit in the field is

set to 1. Other-wise, the field bit is not

affected

If the bit in the written value is a 1,

the cor-responding bit in the field is

set to 0. Other-wise, the field bit is not

affected

If the bit in the written value is a 0,

the cor-responding bit in the field is

set to 1. Other-wise, the field bit is not

affected

If the bit in the written value is a 0,

the cor-responding bit in the field is

set to 0. Other-wise, the field bit is not

affected

Changed to written value

Changed to written value if this is the

first write operation after a hard reset.

Otherwise, has no effect

Changed to written value if this is the

first write operation after a hard reset.

Otherwise, has no effect

Example

// Field: [15:8] %% Day %% Day Synthesized FPGA %% R_O %% 0x16 %% 0x16

4.14 Indicate End of register by key word End:

[MUST]

This is a single line which contains key word End:.

[SYNTAX]

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 18 of 20

4 Arrive Technologies Register description file

//[End:] [any string, dont care]

[End:] is KEW_WORD: to identify a end of register declared

NOTE

The current parser tools also support detecting line ##############.############# as end of register

declared. But you SHOULD not use this. SHOULD use couple key words (Begin:End:) for more

explicitly.

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 19 of 20

5 addrmap file

5 addrmap file

This is a file with extension addrmap. File will be defined an address map for atreg source files. It looks like

below. File will be used by Register Model Generator of TestBench environment to generate register model

database. So files need to be followed template.

The file has 3 sections

Section 1: Including all atreg files. Note that comment out any line by inserting // at the beginning

of lines

Section 2: Defining typename for each register file (block/sub-block name). This will be hooked to

register instance name to create register class or register address macro

Section 3: Define address map for all register files

2015 Arrive All Rights Reserved

PRELIMINARY VERSION - FOR

INTERNAL USE ONLY

Page 20 of 20

Вам также может понравиться

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Verilog and Test Bench Code For FlipflopsДокумент11 страницVerilog and Test Bench Code For FlipflopsKeith Fernandes67% (3)

- Verilog Interview Questions With Answers!Документ42 страницыVerilog Interview Questions With Answers!Vinod Lk95% (56)

- LN 06 Hierarchical ModelingДокумент37 страницLN 06 Hierarchical ModelingChauHuynhОценок пока нет

- 1 Leda General Coding RulesДокумент116 страниц1 Leda General Coding Ruleskrishna chaitanyaОценок пока нет

- Vlsi Interview QuestionsДокумент26 страницVlsi Interview Questionschintu333Оценок пока нет

- Chip Synthesis Workshop 1392Документ493 страницыChip Synthesis Workshop 1392RohitKandula100% (2)

- SDFDLM, SDFNET, or SDFNEP Message - Causes and CuresДокумент6 страницSDFDLM, SDFNET, or SDFNEP Message - Causes and CuresBharathi Mahadevachar100% (1)

- Verilog HDL Lab CodesДокумент30 страницVerilog HDL Lab CodesImrannkhanОценок пока нет

- Milkyway FAQДокумент11 страницMilkyway FAQBhai BaiОценок пока нет

- FPGA Implementation of MIMO System Using Xilinx System Generator For Efficient Hardware/ Software Co-DesignДокумент9 страницFPGA Implementation of MIMO System Using Xilinx System Generator For Efficient Hardware/ Software Co-Designsreekanthreddy peramОценок пока нет

- Ece5440 Topic3 VerilogCombinationalLogicДокумент40 страницEce5440 Topic3 VerilogCombinationalLogicharoldo-garciaОценок пока нет

- VHDL Module 2020 - 1 PDFДокумент50 страницVHDL Module 2020 - 1 PDFRoger AbucejoОценок пока нет

- Altera Epf8282alc84 4Документ62 страницыAltera Epf8282alc84 4lim hyОценок пока нет

- General Lab InstructionsДокумент3 страницыGeneral Lab InstructionsJATIN AGGARWALОценок пока нет

- Module 5 PDFДокумент133 страницыModule 5 PDFDeepak KumarОценок пока нет

- Arun Kumar Paper Tcs ComaniesДокумент68 страницArun Kumar Paper Tcs ComaniesDanielle DeanОценок пока нет

- PG Electronics 2020Документ23 страницыPG Electronics 2020hmanghh2000Оценок пока нет

- ALINT User GuideДокумент578 страницALINT User GuideppdabholkarОценок пока нет

- Verilog Modeling of Wi-Fi MAC Layer For TransmitterДокумент6 страницVerilog Modeling of Wi-Fi MAC Layer For TransmitterIJSTEОценок пока нет

- Basic VHDL Programming Using Xilinx FpgaДокумент6 страницBasic VHDL Programming Using Xilinx FpgaantmonibrittoОценок пока нет

- Lab Assignment 4 Enhanced Priority EncoderДокумент2 страницыLab Assignment 4 Enhanced Priority EncoderSaОценок пока нет

- Lec 38Документ31 страницаLec 38sk_sulabhОценок пока нет

- Madhuri ResumeДокумент4 страницыMadhuri Resumedeepakk_alpineОценок пока нет

- SystemC Questa TutorialДокумент11 страницSystemC Questa TutorialmanavalaОценок пока нет

- IverilogДокумент7 страницIverilogDũng TrầnОценок пока нет

- 01 - Xcelium, Nlint, Nwave, VerdiДокумент90 страниц01 - Xcelium, Nlint, Nwave, Verdi조동올Оценок пока нет

- Verilog HDL - Samir PalnitkarДокумент403 страницыVerilog HDL - Samir PalnitkarNguyên NiОценок пока нет

- Systemverilog Made Easy: A Perl Interface To A Full Ieee 1800 Compliant ParserДокумент5 страницSystemverilog Made Easy: A Perl Interface To A Full Ieee 1800 Compliant ParsersattarsekharОценок пока нет

- Sandesh V Borgaonkar FV 2015Документ6 страницSandesh V Borgaonkar FV 2015sandyiitkgpОценок пока нет

- Exp 10 63Документ5 страницExp 10 63TOB3Y 09Оценок пока нет