Академический Документы

Профессиональный Документы

Культура Документы

Diseño de circuito sumador BCD

Загружено:

Rulo RodríguezОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Diseño de circuito sumador BCD

Загружено:

Rulo RodríguezАвторское право:

Доступные форматы

Jess Ral Rodrguez Higuera.

Diseo Lgico

23 de junio de 2016

BCDADDER.

Objetivos:

Disear un circuito que represente la suma de dos nmeros, en formato binario, en el display

de un decodificador BCD a 7 segmentos (salida con formato decimal).

Compilar y enlazar los archivos que describen el circuito as como el ambiente de pruebas para

la creacin de un archivo ejecutable.

Ejecutar el proyecto y visualizar los resultados.

Introduccin:

Precedente a detallar la funcionalidad y estructura del circuito, es necesario especificar las

condiciones de las que constar ste. A continuacin se describen las condiciones del circuito:

-

El rango de entrada de los nmeros binarios al circuito ser: [0, 9]. Teniendo como valor

mximo y mnimo de la suma 18 y 0 respectivamente.

Con base al rango de los nmeros de entrada, stos slo podrn ser nmeros de 4 bits.

El circuito slo tendr validez para nmeros sin signo.

La representacin del display del circuito estar conformada por 8 leds, los cuales tienen su ctodo

en comn. Es por eso que los segmentos encendern al obtener 1 lgico.

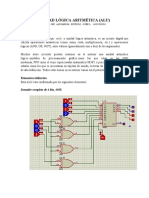

Las conexiones de un decodificador BCD-7 segmentos con un display se observa en la Ilustracin 1.

Ilustracin 1. Conexiones del display con BCD-7 segmentos.

Jess Ral Rodrguez Higuera.

Diseo Lgico

23 de junio de 2016

Para nuestro circuito, el segmento denominado dot ser renombrado por h. Adems de que la

representacin del display ser de tipo bit_vector (7 downto 0) en vez de 8 salidas de un bit.

Teniendo presente lo dicho anteriormente, en la Tabla 1 se muestran los valores del display para

cada valor de entrada:

Valor numrico en decimal Representacin en display

0

11111100

1

01100000

2

11011010

3

11110010

4

01100110

5

10110110

6

10111110

7

11100000

8

11111110

9

11100111

E*

10011110

r*

10001100

Tabla 1. Valores del display para valores de entrada.

* Las representaciones de E y r sern utilizadas posteriormente como indicadores cuando se

sobrepase el rango de los nmeros de entrada.

Diagrama y funcionalidad de cada componente:

Para satisfacer la condicin de que las entradas sean nmeros entre 0 y 9, se cre el componente

compare en el cul se hace un criterio de los tres primeros bits ms significativos de cada

nmero. Esto con la finalidad de ver si son o no mayor a 9.

Dicho componente cuenta con 2 entradas y 4 salidas. En 2 de las salidas se tendrn las entradas

intactas, mientras que en las restantes (err y err1) se tendr un 0 cuando uno o ambos nmeros

sean menores a 9 y 1 en el caso opuesto.

El diagrama del componente compare se muestra en la ilustracin 2.

Jess Ral Rodrguez Higuera.

Diseo Lgico

23 de junio de 2016

compare

b

err

err1

Ilustracin 2. Diagrama del componente compare.

El cdigo correspondiente al componente compare se muestra en la Ilustracin 3.

Ilustracin 3. Cdigo correspondiente al componente compare.

Posteriormente, se cre el componente adders, en el cul se harn la suma de las dos entradas y

despus sumarle 0110 (6 en decimal) al resultado de dicha suma.

Jess Ral Rodrguez Higuera.

Diseo Lgico

23 de junio de 2016

La primera suma de las entradas se realizar en un adder4. Despus, el resultado entrar a otro

adder4 junto con una seal con valor de 0110.

Lo anterior tiene el propsito de generar un acarreo de 1 para resultados iguales o mayores a 10 y

con esto evitarnos el alambrado de dos decodificadores. Esta correccin slo es til para

resultados de suma mayores o iguales a 10. Para resultados menores a 10, es necesario conservar

el resultado obtenido en el primer adder4.

Para resolver el problema anterior, fue necesario crear el componente mplex (dentro del

componente adders) a fin de decidir qu entrada se volver salida con base a los criterios de error

(en el componente compare) y el acarreo final de la suma del segundo addder4.

El diagrama de este componente se presenta en la Ilustracin 4.

adders

u0: adder4

co

r

seis

b

u0: adder4

r

u0: adder4

Ilustracin 4. Diagrama del componente adders.

Jess Ral Rodrguez Higuera.

Diseo Lgico

23 de junio de 2016

En la Ilustracin 5 se muestra el diagrama del circuito bcdadder.

bcdadder

y

d0

d1

u0:compare

a

c

err

err1

d4

d5

d3

d2

d6

u0:compare

co1

d9

co

f

u2:mplex1

a b

d7

u3:deco

ent

c d

f

f

f

f1

Ilustracin 2. Diagrama de bcdadder.vhdl

La finalidad de los componentes mplex y mplex1 es decidir qu salida tendr el componente con

base a una serie de criterios. En este caso los criterios corresponden a acarreos finales y errores.

Вам также может понравиться

- Razonamiento cuantitativo, 2ª edición: Notas de claseОт EverandRazonamiento cuantitativo, 2ª edición: Notas de claseРейтинг: 5 из 5 звезд5/5 (1)

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208От EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Оценок пока нет

- Ejercicios Resueltos de Diagramas de SecuenciaДокумент106 страницEjercicios Resueltos de Diagramas de SecuenciaJohn Raver50% (2)

- Apuntes Navegadores y Buscadores (Cecyteslp)Документ18 страницApuntes Navegadores y Buscadores (Cecyteslp)Jessica Hernández100% (1)

- Electrónica Digital 1Документ8 страницElectrónica Digital 1Düväń Mõńtāñō100% (1)

- Últimas Tecnologías de Discos Duros para Laptop.Документ10 страницÚltimas Tecnologías de Discos Duros para Laptop.Alexander RivasОценок пока нет

- Actividad 6 Analisis y Diseño de Sistemas - Jose Antonio Aguirre TiradoДокумент4 страницыActividad 6 Analisis y Diseño de Sistemas - Jose Antonio Aguirre TiradoJosé AguirreОценок пока нет

- Sistemas DigitalesДокумент35 страницSistemas DigitalesDione Huaman Borda100% (1)

- Sistemas DigitalesДокумент10 страницSistemas DigitalesIsrael SologurenОценок пока нет

- Practica 5Документ10 страницPractica 5Lenin Pardo SalazarОценок пока нет

- Practica 5Документ10 страницPractica 5HomeroOjedaОценок пока нет

- Ejemplo de Diseño Del Proyecto #1 PDFДокумент6 страницEjemplo de Diseño Del Proyecto #1 PDFBill GonzálezОценок пока нет

- Calculadora en Fpga Con Circuitos LógicosДокумент10 страницCalculadora en Fpga Con Circuitos LógicosJhon Abraham Bonilla100% (1)

- Sumador-Restador de 4 bits con visualización en displays 7 segmentosДокумент9 страницSumador-Restador de 4 bits con visualización en displays 7 segmentosalbertwillyОценок пока нет

- Circuito Lógico para Desbordamiento Del SumadorДокумент6 страницCircuito Lógico para Desbordamiento Del SumadorJuan DiegoОценок пока нет

- CADENA - ESCORZA MultiplicadorДокумент14 страницCADENA - ESCORZA MultiplicadorEddy Cadena GrandaОценок пока нет

- P3 PseДокумент30 страницP3 Psemarosmeiden123Оценок пока нет

- Sumador Binario de 4 BitsДокумент10 страницSumador Binario de 4 BitsBere Ramírez AguileraОценок пока нет

- Tipos de CircuitosДокумент11 страницTipos de Circuitosalonsoalex25Оценок пока нет

- Circuito calculadora digital de dos dígitos binariosДокумент16 страницCircuito calculadora digital de dos dígitos binariosLuis Gerardo Jesús Sánchez EspinozaОценок пока нет

- Display de 7 Segmentos y Contador Del 0 Al 9Документ5 страницDisplay de 7 Segmentos y Contador Del 0 Al 9Hévy PsicodeliaОценок пока нет

- Marco Teorico MultiplexorДокумент4 страницыMarco Teorico MultiplexorAngel Zepeda PichardoОценок пока нет

- Multiplicador BinarioДокумент9 страницMultiplicador BinarioJulioMarinОценок пока нет

- Comparadores y multiplexores digitalesДокумент7 страницComparadores y multiplexores digitalesMarcOs AlexanderОценок пока нет

- Funciones de La Logica CombinacionalДокумент27 страницFunciones de La Logica CombinacionalJuan David Acosta DangondОценок пока нет

- 10) Sumador y ComparadorДокумент7 страниц10) Sumador y Comparadorjaja1978100% (1)

- Informe SumadorДокумент12 страницInforme SumadorKarlaОценок пока нет

- Codificadores y DecodificadoresДокумент14 страницCodificadores y DecodificadoresAidinCastroОценок пока нет

- Trabajo Autonomo 1 PAO12021Документ2 страницыTrabajo Autonomo 1 PAO12021Gabriel SanchoОценок пока нет

- Tema5 2Документ10 страницTema5 2FerchoОценок пока нет

- Diseño de un circuito comparador de 2 a n bitsДокумент15 страницDiseño de un circuito comparador de 2 a n bitsJorge ArcadioОценок пока нет

- Tarea2 - Códigos. Barrios.C.Dulce.AДокумент13 страницTarea2 - Códigos. Barrios.C.Dulce.ADULCE ALEJANDRA BARRIOS CALVILLOОценок пока нет

- Conversor Analógico Digital - Adc: Usted Puede Ver Los 4 Niveles en La Siguiente IlustraciónДокумент6 страницConversor Analógico Digital - Adc: Usted Puede Ver Los 4 Niveles en La Siguiente IlustraciónLeira Nahitsirc IhcamilОценок пока нет

- Prac13 Contador Ascendente DescendenteДокумент8 страницPrac13 Contador Ascendente DescendenteStiva DarcyОценок пока нет

- COMPARADOR_8BITSДокумент7 страницCOMPARADOR_8BITSElice Fernández AymeОценок пока нет

- Qdoc - Tips Sistemas-Digitales PDFДокумент35 страницQdoc - Tips Sistemas-Digitales PDFLuisa FernandaОценок пока нет

- Informe de Simulación en ProteusДокумент5 страницInforme de Simulación en ProteusBustamanteHectorОценок пока нет

- Concepto Bit, ByteДокумент20 страницConcepto Bit, BytePaola dell androОценок пока нет

- Arquitectura de Computadoras PDFДокумент30 страницArquitectura de Computadoras PDFLuis JaramilloОценок пока нет

- Informe Circuito SumadorДокумент8 страницInforme Circuito SumadorBrandon CalderonОценок пока нет

- Sistemas Numericos TeoríaДокумент5 страницSistemas Numericos TeoríaCa MinanteОценок пока нет

- TEMA 07 - Circuitos AritméticosДокумент47 страницTEMA 07 - Circuitos AritméticosEli BarrientosОценок пока нет

- Comparador de 4 BitsДокумент15 страницComparador de 4 BitsAnonymous EinafeoB46Оценок пока нет

- Ladsjlkjla Ldaksj Dlakjldak Laksj Dlak Lkjs DlkasjДокумент26 страницLadsjlkjla Ldaksj Dlakjldak Laksj Dlak Lkjs DlkasjRonald PeñaОценок пока нет

- Practica 2.1 - Codificadores y DecodificadoresДокумент7 страницPractica 2.1 - Codificadores y DecodificadoresFabián Calzada DelgadoОценок пока нет

- Informe 7 Sistemas DigitalesДокумент12 страницInforme 7 Sistemas DigitalesXavier GuanoОценок пока нет

- Informe Practica 4 SimuladaДокумент9 страницInforme Practica 4 SimuladaJuan Jose Eraso DelgadoОценок пока нет

- Multiplicadores, comparadores, decodificadores y multiplexoresДокумент10 страницMultiplicadores, comparadores, decodificadores y multiplexoresJCesar Cusi AlvaradoОценок пока нет

- Arquitectura de ComputadorasДокумент14 страницArquitectura de ComputadorasJesus NoyolaОценок пока нет

- Unidad Lógica AritméticaДокумент11 страницUnidad Lógica AritméticaMadeline ReynosoОценок пока нет

- 01 Representacion Binario Examenes AW2009Документ8 страниц01 Representacion Binario Examenes AW2009Victor Manuel Sanz LazaroОценок пока нет

- Sumador Restador de 4bitsДокумент14 страницSumador Restador de 4bitsgreomerОценок пока нет

- 8051 Del Conjunto de InstruccionesДокумент29 страниц8051 Del Conjunto de InstruccionesRain Atrapa Sueños Mamani CruzОценок пока нет

- AyOCI-TP-Repaso-Apuntes-2021Документ6 страницAyOCI-TP-Repaso-Apuntes-2021merchanf6Оценок пока нет

- Unidad 4. Lógica Combinacional CircuitosДокумент17 страницUnidad 4. Lógica Combinacional CircuitosAlejandro PerezОценок пока нет

- Suma en BCDДокумент4 страницыSuma en BCDYamil Alberto Peña LoayzaОценок пока нет

- Trabajo Practico Sobre MSIДокумент19 страницTrabajo Practico Sobre MSImigofОценок пока нет

- Sistemas Digitales - Conversiones BCD - Binario - GrayДокумент7 страницSistemas Digitales - Conversiones BCD - Binario - GraySilva FerchoОценок пока нет

- Practica - Reporte LCDДокумент6 страницPractica - Reporte LCDsara yessenia ramirez hernandezОценок пока нет

- Conseptos Basicos de Base de DatosДокумент12 страницConseptos Basicos de Base de DatosAngel EspinosaОценок пока нет

- Taller Practico N°3 Sistema Operativo Linux - Instalacion RED HATДокумент11 страницTaller Practico N°3 Sistema Operativo Linux - Instalacion RED HATgverdugobОценок пока нет

- CANSAT equipo misiónДокумент3 страницыCANSAT equipo misiónCaro TochiОценок пока нет

- Hardware-SoftwareДокумент13 страницHardware-SoftwareJose Antonio Valdez LebronОценок пока нет

- Introducción A JMeter y Pruebas de CargaДокумент8 страницIntroducción A JMeter y Pruebas de CargaAugusto C. SilОценок пока нет

- MALWAREДокумент5 страницMALWAREDaniel CuevaОценок пока нет

- Cuadro Comparativo de Softwere CAD.Документ6 страницCuadro Comparativo de Softwere CAD.David PalaciosОценок пока нет

- Enfora-GSM1218-Guia Del Usuario MCIДокумент110 страницEnfora-GSM1218-Guia Del Usuario MCILuis Antonio Mella ReyesОценок пока нет

- Cisco Packet Tracer Guia 2Документ4 страницыCisco Packet Tracer Guia 2Xps MvaОценок пока нет

- Laboratorio 02 Aplicación de Google Drive PresentaciónДокумент8 страницLaboratorio 02 Aplicación de Google Drive PresentaciónAldairОценок пока нет

- VTA-84635 ManualДокумент12 страницVTA-84635 Manualjofes14Оценок пока нет

- Instalación y configuración de IP-PBX con Asterisk en ElectroCar S.AДокумент13 страницInstalación y configuración de IP-PBX con Asterisk en ElectroCar S.AJuanPa CortezОценок пока нет

- Manual de PHPДокумент28 страницManual de PHPL.S.C.A Carlos Pastrana GarcíaОценок пока нет

- Tema 5 - Esquemas en Oracle (Curso 2011)Документ10 страницTema 5 - Esquemas en Oracle (Curso 2011)Ana BorobioОценок пока нет

- Topologías de RedДокумент4 страницыTopologías de RedJUAN CAMILO SUAREZОценок пока нет

- DNS en Sistemas Linux PDFДокумент7 страницDNS en Sistemas Linux PDFMario Laglera BarcoОценок пока нет

- Proyecto DBДокумент46 страницProyecto DB:v jejejejejeОценок пока нет

- Guia IMPLEMENTAR LA ESTRUCTURA DE LA RED DE ACUERDO CON UN DISEÑO PREESTABLECIDO A PARTIR DE NORMAS TÉCNICASДокумент11 страницGuia IMPLEMENTAR LA ESTRUCTURA DE LA RED DE ACUERDO CON UN DISEÑO PREESTABLECIDO A PARTIR DE NORMAS TÉCNICASRodrríguezz Zulvarán Alexsander AllberttoОценок пока нет

- Laboratorio 1 RedesДокумент5 страницLaboratorio 1 RedesGersonBravoОценок пока нет

- Ficha POSДокумент2 страницыFicha POSVictor SarmientoОценок пока нет

- Bases de datos: evolución e importancia organizacionalДокумент2 страницыBases de datos: evolución e importancia organizacionallina CRОценок пока нет

- Computación Básica Unidades 1-2-3-4Документ91 страницаComputación Básica Unidades 1-2-3-4Paul SangopantaОценок пока нет

- Guia de Acceso EsiosДокумент17 страницGuia de Acceso EsiosLowo EduardoОценок пока нет

- Evidencia de Conocimientos Informatica BasicaДокумент4 страницыEvidencia de Conocimientos Informatica BasicaJheison Tovar MogollónОценок пока нет

- Actividades Tema 4 MyMEДокумент39 страницActividades Tema 4 MyMESamuel Puerta MerinoОценок пока нет