Академический Документы

Профессиональный Документы

Культура Документы

Board Games AA V9 I3

Загружено:

Maria Lavinia IordacheАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Board Games AA V9 I3

Загружено:

Maria Lavinia IordacheАвторское право:

Доступные форматы

HIGH-TECH

BOARD GAMES

ANSYS Electronics Desktop saves hundreds of

thousands of dollars and months of time in the design

of a high-speed printed circuit board.

By Stephen P. Zinck, President, Interconnect Engineering, Inc., North Berwick, U.S.A.

T

o support the vast amounts of data transfer required period (the time allotted to send a bit) has shrunk to below 40

by the Internet of Things and Big Data requires high- picoseconds. This is considerably less than the time required for

speed networking technologies, such as 100 gigabit the bit to travel from transmitter to receiver. The insertion loss

Ethernet. This creates enormous challenges for equipment sup- incurred by the printed circuit board (PCB) materials increases

pliers. On-board, high-speed communication channels are now with frequency, expanding the potential for eye closure (a

being pushed to 2528 Gb/s and beyond nearly double the reduced signal) in the channel due to physical losses and reflec-

state of the art about a year ago. As data rates increase, the bit tions. Achieving a reliable link under these conditions would be

2015 ANSYS, INC. ANSYS ADVANTAGE Volume IX | Issue 3 | 2015 21

HIGH-TECH

ANSYS INTRODUCES NEW ELECTRONICS

signaling rates, it is almost impossible to

DESKTOP WITH 3-D EM COMPONENT do any level of design, verification and test

LIBRARIES FOR NEXT-GENERATION

WIRELESS INTEGRATION (DVT). Areas where a measurement can be

ansys.com/93board

taken on the board will result in a closed

eye because testing cannot be performed

demanding, even if cost and time to mar- at the end of the transmission line, which

ket were not a concern. Yet, in todays is deep inside the package and device.

cost-competitive environment, manufac- If designers only guess at the required

turers cannot afford to use exotic, pre- changes for a re-spin, the whole expen-

mium materials and components except sive cycle begins anew and will likely be

when absolutely necessary. repeated. Several small networking equip-

ment startup companies have gone out

HIGH-SPEED INTERCONNECT of business because they were unable to

DESIGN CHALLENGES produce robust designs within time and ANSYS HFSS 3-D layout of cutout section of one of 28

6-inch Gb channels

Traditional methods leave designers cost constraints.

with questions like whether a design will In stark contrast to this guesswork

be functional and robust under all possible and rule-of-thumb approach, simulation

conditions; whether we should have chosen brings confidence and science to the engi- might produce an eye diagram that shows

a more expensive board material; whether neering process. The marriage of time that the channel works, but the frequency

strip-line transmission lines or micro- domain and frequency domain simu- domain reveals a notch that is unex-

strip transmission lines will be needed to lations, during early design phases or pected. By examining, through simu-

meet the design spec. Building a physi- even late in the development cycle, pro- lation, each of the circuit elements that

cal test prototype to assess just one design vides the deepest insight into whether or comprise the system channel, it becomes

approach could cost more than $100,000 not an interface or channel will be robust. possible to identify which aspect of the

and take months to develop. At these high For example, a time-domain simulation design (the vias, a differential pair too

In contrast to the guesswork and rule-of-thumb approach, simulation

brings confidence and science to the engineering process.

-2.50

m1

-5.00

-7.50

-10.00

-12.50

0.00 5.00 10.00 15.00 20.00 25.00

F (GHz)

ANSYS HFSS S21 insertion loss plot of the extracted channel

2015 ANSYS, INC. ANSYS ADVANTAGE Volume IX | Issue 3 | 2015 22

An example of notch behavior and resulting eye diagram that shows margin

close to a ground void, a component

placement issue or a material problem) is

ANSYS Electronics Desktop integrates EM

causing the notch. tools, circuit/system simulation, ECAD links

100-GIGABIT ETHERNET and compliance reporting.

NETWORKING PRODUCT

Interconnect Engineering Inc. is an

independent consulting company with

clients ranging from startups to Fortune

500 businesses. One of Interconnect easily attainable based on the physi- the opportunity to put the new ANSYS

Engineerings clients is a networking cal layout that the customer design sup- Electronics Desktop to the test. This tool pro-

equipment supplier that builds multiple ported. To avoid risking the company on vided a major advantage in this application

100-gigabit Ethernet networking prod- a series of board spins that would have by reducing the amount of time required

ucts. One particular design features four potentially cost hundreds of thousands to analyze the design in both the time and

channel-bonded, 28 Gb/s links running of dollars and taken months to com- the frequency domains. The Electronics

bidirectionally from a ball grid array plete the supplier asked Interconnect Desktop integrates EM tools, circuit/

(BGA) device to a quad small-form-fac- Engineering to simulate the design prior system simulation, ECAD links and

tor pluggable (QSFP) optical module. to building a prototype.

The risks involved in this design were While Interconnect Engineering Inc.

increased because vendor-supplied has long used and supported ANSYS elec- ANSYS HFSS 3-D COMPONENTS

ansys.com/93board2

guidelines and constraints were not tronic design tools, this project provided

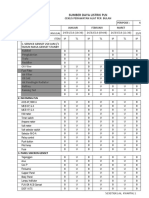

IBIS-AMI schematic of the 28 Gb interface shown in the circuit simulator

2015 ANSYS, INC. ANSYS ADVANTAGE Volume IX | Issue 3 | 2015 23

HIGH-TECH

specifications. He considered alternative

board materials and identified the least-

expensive material that would comfortably

meet IL and RL specs. Overall, Interconnect

Engineering identified areas in which cor-

ners could be safely cut to reduce manu-

facturing costs, along with areas in which

money needed to be spent, such as back-

drilling to ensure a robust design.

TIME DOMAIN SIMULATION

IBIS-AMI models for the BGA inter-

face device and optical transceiver mod-

ule were also acquired. These models

were imported into ANSYS Electronics

Desktop. Engineers then performed

time domain simulations by creat-

Statistical eye diagram plot of the 28 Gb interface shown in the circuit simulator

ing a circuit simulation environment

using one instance of the several four-

port S-parameter models of the com-

The networking supplier saved hundreds plete channel generated in the frequency

domain. The eye diagram showed prob-

of thousands of dollars and months of lems in one channel, so the engineer

time that potentially would have been reconfigured transmitter and receiver set-

tings, including pre-emphasis, equaliza-

required to develop a working product tion, output amplitude, process case and

voltage settings, to maximize the open-

without simulation. ing of the eye. When simulations were

complete, the eye correlated to a bit error

rate of better than 1 x 10-12 (less than one

error in a trillion bits), indicating that the

channel was compliant in the time

compliance reporting. This new tech- Engineering with the PCB design in domain. Finally, the engineer reviewed

nology delivers a single desktop for Allegro .brd file format. An engineer the frequency domain to make sure that

ANSYS HFSS, HFSS 3D Layout, HFSS-IE, imported the databases into ANSYS the design changes, based on the time

Q3D Extractor and HFSS Planar EM cir- Electronics Desktop, extracted the rel- domain simulations, did not have any

cuit and system simulation design evant channels using the cutout sub- adverse effects.

types. Users can insert HF/SI analyses design function, and selected the The entire project was completed

into projects that co-exist, with drag- traces from the silicon device to the in about four weeks. During this time,

and-drop dynamic links between elec- optical module. The engineer created Interconnect Engineering investigated

tromagnetic and circuit simulations port excitations based on component dozens of potential solutions. The com-

for simple problem setup and reliable specifications then set up solder-ball pany recommended a design that pro-

performance. Working within a single models for the silicon device and sur- vided sufficient positive margin to

graphical user interface, rather than face roughness models for the traces ensure that the channel will work under

moving back and forth between sev- to add fidelity and accuracy. Engineers any foreseeable circumstances, while

eral different programs, eliminates the then ran frequency domain simulations keeping manufacturing costs at the low-

need to export data from one program to with ANSYS HFSS and generated the est practical levels. The network equip-

another. For example, users can insert S-parameter results for each of the mul- ment supplier built the prototype based

S-parameter elements or IBIS-AMI mod- tiple iterations. The simulations took on the simulation results, and it worked

els into a circuit simulation with simple about three days to run on multiple as predicted. The result was that the

import features. Overall, the Electronics 24-core machines, as the area was quite networking supplier saved hundreds

Desktop provides significant efficiency large for the solvers to mesh. of thousands of dollars and months of

gains and ease-of-use for solving com- The engineer modified the via char- time that potentially would have been

plex problems. acteristics and anti-pad structures and required to develop a working product

re-arranged the PCB layers to address without simulation. This vendor also

FREQUENCY DOMAIN some potential issues. The engineer kept manufacturing costs at or near the

SIMULATION then went through several iterations lowest possible levels and saved cus-

In this project, the network equip- until a design was found that met the tomer relationships by meeting product

ment supplier provided Interconnect insertion loss (IL) and return loss (RL) time-to-market goals.

2015 ANSYS, INC. ANSYS ADVANTAGE Volume IX | Issue 3 | 2015 24

Вам также может понравиться

- Doamnei Director A Colegiului Naţional Spiru Haret" BucureştiДокумент1 страницаDoamnei Director A Colegiului Naţional Spiru Haret" BucureştiMaria Lavinia IordacheОценок пока нет

- Ansys q3d Extractor Brochure PDFДокумент8 страницAnsys q3d Extractor Brochure PDFMaria Lavinia IordacheОценок пока нет

- 2011 - Alanson Sample - Cutting The Last Cord With Wireless PowerДокумент160 страниц2011 - Alanson Sample - Cutting The Last Cord With Wireless PowerMaria Lavinia IordacheОценок пока нет

- InTech-Equivalent Circuit and Calculation of Its Parameters of Magnetic Coupled Resonant Wireless Power Transfer PDFДокумент17 страницInTech-Equivalent Circuit and Calculation of Its Parameters of Magnetic Coupled Resonant Wireless Power Transfer PDFMaria Lavinia IordacheОценок пока нет

- M4164-C 06-15 - Etrinsa Technical Manual - MN031r2hq PDFДокумент142 страницыM4164-C 06-15 - Etrinsa Technical Manual - MN031r2hq PDFMaria Lavinia IordacheОценок пока нет

- Parker Electronics Update 160316 PDFДокумент71 страницаParker Electronics Update 160316 PDFMaria Lavinia IordacheОценок пока нет

- Ab Wireless Power Transfer PDFДокумент2 страницыAb Wireless Power Transfer PDFMaria Lavinia IordacheОценок пока нет

- Maple Dsolve NumericДокумент36 страницMaple Dsolve NumericMaria Lavinia IordacheОценок пока нет

- Sip Design and Verification Using AdsДокумент34 страницыSip Design and Verification Using AdsMaria Lavinia IordacheОценок пока нет

- SI PI EMI EMC ANSYS Solution PDFДокумент49 страницSI PI EMI EMC ANSYS Solution PDFMaria Lavinia IordacheОценок пока нет

- Manual Program Tina 8Документ11 страницManual Program Tina 8Maria Lavinia IordacheОценок пока нет

- Ansoft Q3D TraningДокумент24 страницыAnsoft Q3D TraningleivajОценок пока нет

- Dynamics 70 WorkshopsДокумент74 страницыDynamics 70 WorkshopsZain Ul Islam ButtОценок пока нет

- Dynamics 70 M8 AdvModalДокумент50 страницDynamics 70 M8 AdvModalMaria Lavinia IordacheОценок пока нет

- Dynamics 7.0: Training ManualДокумент4 страницыDynamics 7.0: Training ManualMaria Lavinia IordacheОценок пока нет

- Dynamics 70 M1 IntroДокумент40 страницDynamics 70 M1 IntroJuhi SinghОценок пока нет

- Dynamics 70 M7 ModesupДокумент26 страницDynamics 70 M7 ModesupMaria Lavinia IordacheОценок пока нет

- In Curs de AfisareДокумент2 страницыIn Curs de AfisareMaria Lavinia IordacheОценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5795)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- ZMD31050 Datasheet Rev1 03Документ19 страницZMD31050 Datasheet Rev1 03d5969660Оценок пока нет

- Parts Catalog: Revision 1Документ269 страницParts Catalog: Revision 1Yesenia GonzalezОценок пока нет

- Ir2301 (S) & (PBF) : High and Low Side DriverДокумент18 страницIr2301 (S) & (PBF) : High and Low Side DriverDr Zeljko DespotovicОценок пока нет

- Millis For ArduinoДокумент13 страницMillis For Arduinogsvijay57100% (1)

- Classes of Pole Based On Horizontal Loads Ansi 05Документ2 страницыClasses of Pole Based On Horizontal Loads Ansi 05JosePinosОценок пока нет

- FT Series /FTB12-150 12V150Ah: Advantages ApplicationДокумент2 страницыFT Series /FTB12-150 12V150Ah: Advantages ApplicationluisgarizaoОценок пока нет

- Experiment 4Документ9 страницExperiment 4mohammed_524176180Оценок пока нет

- Four Basic Parts of Cellular Phones: Mobile TelephonyДокумент7 страницFour Basic Parts of Cellular Phones: Mobile TelephonyCj LlemosОценок пока нет

- Ge Avr PDFДокумент24 страницыGe Avr PDFdinesh kumarОценок пока нет

- Science SOL 4.3 - Electricity: Lightning Is Caused by Static ElectricityДокумент3 страницыScience SOL 4.3 - Electricity: Lightning Is Caused by Static ElectricityKrishnaKumar PodagatlapalliОценок пока нет

- K46 ManualДокумент8 страницK46 ManualDavid KasaiОценок пока нет

- Cummins DFCC Operators Manual PCC3100 ControllerДокумент62 страницыCummins DFCC Operators Manual PCC3100 ControllerkareemОценок пока нет

- 3.ceb Pkg7 Bi 43 Ar01 - Transformer Online Monitoring System ArchitectureДокумент3 страницы3.ceb Pkg7 Bi 43 Ar01 - Transformer Online Monitoring System ArchitectureEdciel EbuenОценок пока нет

- Eca Lab Manual PDFДокумент56 страницEca Lab Manual PDFrppvch100% (5)

- 1600KVA ស្វាយជ្រុំRMU, LVDBДокумент4 страницы1600KVA ស្វាយជ្រុំRMU, LVDBmain mydriveОценок пока нет

- Brown Final PPT FinalДокумент36 страницBrown Final PPT FinalDarshan100% (2)

- BS en 60243232Документ30 страницBS en 60243232RoverОценок пока нет

- Status Code Possible Cause Solution: Troubleshooting - Installation and Commissioning Manual - 1SFC132081M0201Документ1 страницаStatus Code Possible Cause Solution: Troubleshooting - Installation and Commissioning Manual - 1SFC132081M0201Yesenia Jaime RoaОценок пока нет

- Sumber Daya Listrik PLN: Ceklis Perawatan Alat Per BulanДокумент14 страницSumber Daya Listrik PLN: Ceklis Perawatan Alat Per BulanmaryantoОценок пока нет

- Schneider NS800Документ64 страницыSchneider NS800Anonymous Lh3Yh8basIОценок пока нет

- VSN400 User Guide enДокумент62 страницыVSN400 User Guide enTuấn Nguyễn VănОценок пока нет

- Guide Lines: Field Component ManualДокумент21 страницаGuide Lines: Field Component ManualOsman ElmaradnyОценок пока нет

- RU1H140R: N-Channel Advanced Power MOSFETДокумент8 страницRU1H140R: N-Channel Advanced Power MOSFETJose Manuel Campo RodriguezОценок пока нет

- Multitester: Instruction ManualДокумент27 страницMultitester: Instruction ManualEga Nuresa Ega NuresaОценок пока нет

- ME812u Control Module: Technical InstructionsДокумент34 страницыME812u Control Module: Technical InstructionsEОценок пока нет

- Ij UxДокумент308 страницIj UxRagdex RockОценок пока нет

- Cell Reselection ProcedureДокумент4 страницыCell Reselection ProcedureAbhay U. NagraleОценок пока нет

- Electrical Engineering Department: Title Introduction To L-Edit Software Practical Number 1 / 2 / 3 / 4 / 5 / 6 ClassДокумент13 страницElectrical Engineering Department: Title Introduction To L-Edit Software Practical Number 1 / 2 / 3 / 4 / 5 / 6 Classfaiz yusriОценок пока нет

- ZorcДокумент15 страницZorcputrasejahtraОценок пока нет

- Aerial Catalog 2 - 8 Alumoweld PDFДокумент1 страницаAerial Catalog 2 - 8 Alumoweld PDFsb_al20Оценок пока нет