Академический Документы

Профессиональный Документы

Культура Документы

MIDAS A110 A PDF

Загружено:

bardf2Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

MIDAS A110 A PDF

Загружено:

bardf2Авторское право:

Доступные форматы

A110 MIDAS: Multi-standard Integrated

Devices for broadband DSL Access and

www.medeaplus.org

home powerline communicationS

Objectives

. Consortium &. Organization

To develop new wireline communication systems and architectures with

increased bandwidth, capacity, security and QoS

New DSL: ADSL2, ADSL2+, symmetric DSL (10MDSL, Ethernet over DSL)

New broadband PLC for in-home networking

To work on mechanisms, protocols and associated architectures for

MAC, QoS, Security/Safety and user Privacy

To develop and manufacture low-power and cost-effective components

for wireline communication devices

To develop wireline integrated platforms bridging xDSL and PLC and

demonstrate these platforms in the field

To participate to international standardization and promote the

technologies and concepts developed in the project Pisa

To work on the convergence of wireline communication technologies

Value . chain

16 partners

Universities Research institutes Start date: 1 July 2003

End date: 30 June 2005

KULeuven,

KULeuven, LTH, IMEC, Project leader

ENS, IMSE-

IMSE-CNM France Telecom R&D PCC STM Belgium

Budget : 177 person.years

Algorithms,

Algorithms, architecture concepts,

feasibility studies Countries involved:

Belgium, France, Spain, Sweden

System

System

requirements

requirements

System Equipment Target DS2 Alcatel STM B Thomson B

Manufacturers Enabling design

Multi-standard

Security/Safety Building blocks

methodologies & Next generation

Alcatel, Thomson, Ericsson, Veyado, & & platform

flexible SoC xDSL and PLC

Seba service, Upzide Labs,

Labs, LEA Feedback on System Quality of Service chipsets demonstrators

design tools

Test chips, chip sets performances

System Platforms and soft generation of analog next generation xDSL & PLC security/safety issues related line drivers integrated access platforms

requirements and Specs demonstrators IP blocks systems and architectures to life-line support, remote and gateways

high speed converters

powering and maintenance

versatile Application novel advanced DSP demonstration and tests

integrated analogue front-ends

Specific Signal Processor algorithms network traffic models

Real time VDSL loop emulator

digital building blocks

Fast prototyping advanced error correction spectrum regulation and based on digital techniques

active splitters

Design houses and Operators Co-emulation codes for improved

performances

management

bonding & inverse multiple

chipmakers France Telecom

access

higher layer protocols

DS2, Target, ST, Thomson

Activities. in WP1

Enabling design methodologies and tools for Graphical

the design of flexible Wireline IPs and SoC debugger on

host computer

Contributors:

Contributors:

Target (B), ST (B), ESAT-

ESAT-KUL (B), IMSE-

IMSE-CNM (SP), DS2 (SP)

Responsible:

Responsible: API (Tcl/TK, C++)

Target (B) ISS JTAG bit streams

kernel

Activities:

Activities:

TCP/IP socket

A.1.1: Methodologies and tools for soft generation of analog IP blocks

A.1.2: Methodologies and tools for design of versatile Application Specific

JTAG

Signal Processor (ASSP) ctrler

A.1.3: Methodologies and tools for fast-

fast-prototyping and co-

co-emulation Hardware

Debug Target

ctrler core

On chip debugging support Co-simulation environment

Activities. in WP2

Next generation xDSL and PLC, new advanced DSP algorithms and Tester

Noise injection (ANSI norm)

error correction codes for DSL and PLC improved performances Noise File

Twisted copper wire

Noise Generator50

120

1k 1k

Contributors:

Contributors: liaison SDSL

Customer SDSL modem

DS2 (SP), ST (B), Ericsson (Sw), France Telecom R&D (F), LTH (Sw), Impulsive noise injection for xDSL transmission

ENS (F), Thomson (B), LEA (F) SNR with RFI loop 54

Data rate 30

Responsible:

Responsible: [Mbits/sec]

25

DS2 (Spain

(Spain)) 60

Activities:

Activities: 20

A2.1: Study of next generation xDSL systems and architectures

dB

15

VDSL

A2.2: Study of next generation PLC systems and architectures ADSL2+ 10

ADSL2

8

A.2.3: Study of new advanced DSP algorithms and 5

ADSL

ADSL

advanced Error correction codes 24

48

for DSL and PLC improved performances 2 SHDSL ADSL/R 0

dec24

120 130 140 150 160 170 180 190 200 210

tone

1 km 2 km 3 km 4 km 5 km RFI cancellation by powerfull PTEQ In-home scenario for next generation PLC

STMicroelectronics Belgium N.V. For further information,

Industriepark Keiberg please contact Project Leader:

Excelsiorlaan 44-46 Patrick Wouters

B-1930 Zaventem, Belgium patrick.wouters@st.com

http://www.st.com

With thanks to all MIDAS partners

MEDEA+ Forum 2004, 23-24 November, Paris, France

Вам также может понравиться

- A Design Guide For Standing Seam Roof PanelsДокумент44 страницыA Design Guide For Standing Seam Roof Panelskkozak99100% (1)

- Telecom Design Engineer - Ronaldo - Romero - DrakeДокумент9 страницTelecom Design Engineer - Ronaldo - Romero - DrakeOchie RomeroОценок пока нет

- FTTX Designing Best Practices: Digisol Systems LTDДокумент11 страницFTTX Designing Best Practices: Digisol Systems LTDمحمد فاضلОценок пока нет

- Data Center Design GuideДокумент123 страницыData Center Design Guidealaa678100% (1)

- Enterprise Design GuideДокумент214 страницEnterprise Design Guidec_simosОценок пока нет

- Configure RHCE Exam QuestionsДокумент3 страницыConfigure RHCE Exam QuestionsRaJu SinGh100% (3)

- Locuz Enterprise Solutions LTDДокумент29 страницLocuz Enterprise Solutions LTDruchiirОценок пока нет

- BSR Notes IctadДокумент14 страницBSR Notes IctadDavid Web100% (4)

- History of Architecture-Settings and Rituals - Spiro KostofДокумент42 страницыHistory of Architecture-Settings and Rituals - Spiro Kostofdgreen899100% (5)

- Jasmine MotifДокумент25 страницJasmine MotifHunar Lamba100% (2)

- Fibre Optic Network Design GuideДокумент30 страницFibre Optic Network Design GuideunbrandedОценок пока нет

- Overhead Transmission & Distribution: Aluminium & High Performance ConductorsДокумент32 страницыOverhead Transmission & Distribution: Aluminium & High Performance ConductorsKishore SarkarОценок пока нет

- Concise Guide to OTN optical transport networksОт EverandConcise Guide to OTN optical transport networksРейтинг: 4 из 5 звезд4/5 (2)

- q214 Fitness JedKSAДокумент7 страницq214 Fitness JedKSAAThaddeusAntonio100% (1)

- CETA-RAM machine produces hollow cement blocksДокумент17 страницCETA-RAM machine produces hollow cement blockstoacaminho0% (1)

- Open Radio Access Network (O-RAN) Systems Architecture and DesignОт EverandOpen Radio Access Network (O-RAN) Systems Architecture and DesignОценок пока нет

- Design Guidelines Cheat SheetДокумент2 страницыDesign Guidelines Cheat SheetClaudio Lema FerrufinoОценок пока нет

- Challenge Networks PresentationДокумент17 страницChallenge Networks PresentationKamaldeep Singh DhanotaОценок пока нет

- RM Installation Guideline-2020Документ200 страницRM Installation Guideline-2020Nuno MagalhãesОценок пока нет

- Certified Fiber Optic Technician..ROOM SOLUTIONДокумент5 страницCertified Fiber Optic Technician..ROOM SOLUTIONahman shirazyОценок пока нет

- Core Network Engineer Eko Pradana ResumeДокумент4 страницыCore Network Engineer Eko Pradana ResumeEko PradanaОценок пока нет

- Can We Lever An IC AllianceДокумент24 страницыCan We Lever An IC AllianceVũ Thanh TùngОценок пока нет

- Telecom Egypt Senior Expert Seeks VP Telecommunications RoleДокумент4 страницыTelecom Egypt Senior Expert Seeks VP Telecommunications RoleGamal AhmedОценок пока нет

- 0 - Introduction - WiMAX and LTE Network Designer Certified Class November 2013 Rev3Документ24 страницы0 - Introduction - WiMAX and LTE Network Designer Certified Class November 2013 Rev3Randy DookheranОценок пока нет

- D1 Business Data CommunicationsДокумент15 страницD1 Business Data CommunicationsVikasОценок пока нет

- CV Thanseer - Telecom Engineer - Updated NewДокумент4 страницыCV Thanseer - Telecom Engineer - Updated NewBrett AtkinsОценок пока нет

- Ronaldo Romero Telecom Engineer Contact Details and ExperienceДокумент11 страницRonaldo Romero Telecom Engineer Contact Details and ExperienceOchie RomeroОценок пока нет

- Recent Advances of Communications Technology in ChinaДокумент50 страницRecent Advances of Communications Technology in ChinaShewan Alam SuhreedОценок пока нет

- Resume202002190402 2Документ4 страницыResume202002190402 2Gamal AhmedОценок пока нет

- TELECOMMUNICATIONS INFRASTRUCTURE SOLUTIONSДокумент2 страницыTELECOMMUNICATIONS INFRASTRUCTURE SOLUTIONSJoel ManuelОценок пока нет

- Bua Nters atДокумент2 страницыBua Nters atBakul ImpianОценок пока нет

- Fiber Optic Telecommunication: PrerequisitesДокумент55 страницFiber Optic Telecommunication: Prerequisitesgowtham_srinivasan_3Оценок пока нет

- DDI EBOOK 2022 v4Документ116 страницDDI EBOOK 2022 v4zillionpplОценок пока нет

- 08.1 Presentation of Nera NetworksДокумент25 страниц08.1 Presentation of Nera NetworksBlaise Jonathan VessahОценок пока нет

- An automated, widely distributed energy networkДокумент19 страницAn automated, widely distributed energy networkani9027Оценок пока нет

- A Tour Across SIMULIA Abaqus Applications - FINALДокумент75 страницA Tour Across SIMULIA Abaqus Applications - FINALFammy FanОценок пока нет

- Resume Examples by Real People - Network Engineer Resume Sample - KickresumeДокумент1 страницаResume Examples by Real People - Network Engineer Resume Sample - KickresumeAlisson LandaetaОценок пока нет

- Romain Boissat: - Network EngineerДокумент2 страницыRomain Boissat: - Network EngineerUmesh ShettyОценок пока нет

- Network & Communication Engineering: A Future inДокумент6 страницNetwork & Communication Engineering: A Future inYuki KoОценок пока нет

- Unit 1 - Introduction - V5Документ45 страницUnit 1 - Introduction - V5Aleix Cánovas EstebanОценок пока нет

- Sensing As A Service Thenewinternetofthingsiotbusinessmodel 59Документ22 страницыSensing As A Service Thenewinternetofthingsiotbusinessmodel 59anandsivОценок пока нет

- Transmission Network Planning For GSM UMTS LTEДокумент2 страницыTransmission Network Planning For GSM UMTS LTEDeepakNathОценок пока нет

- Midas A110 AДокумент1 страницаMidas A110 Abardf2Оценок пока нет

- Optical - Doc DWDMДокумент8 страницOptical - Doc DWDMSughra HaroonОценок пока нет

- Profile Neonet 2Документ32 страницыProfile Neonet 2neonetwirelessОценок пока нет

- Professional Radio Frequency EngineerДокумент3 страницыProfessional Radio Frequency EngineerManikantaswamyseeripiОценок пока нет

- OBO Cable Support SystemsДокумент840 страницOBO Cable Support SystemsMuhammad Adnan ShabbirОценок пока нет

- Kiran PatilДокумент4 страницыKiran Patilravi mittalОценок пока нет

- CV ExampleДокумент2 страницыCV ExampleUsama ArshadОценок пока нет

- Business Data CommunicationsДокумент15 страницBusiness Data CommunicationsESHAAN KULSHRESHTHAОценок пока нет

- Designing and Building Connectivity For The World's Most Advanced NetworksДокумент4 страницыDesigning and Building Connectivity For The World's Most Advanced Networksmedi yuhendraОценок пока нет

- Catalogo NexansДокумент40 страницCatalogo NexansAndrey MelsОценок пока нет

- Company & Products: AWE CommunicationsДокумент68 страницCompany & Products: AWE CommunicationsHabib MohammedОценок пока нет

- MMC 5 Module 18ec 743Документ25 страницMMC 5 Module 18ec 743sahanacsceОценок пока нет

- HFCL - Investor Presentation - BookДокумент26 страницHFCL - Investor Presentation - BookAnsh AnandОценок пока нет

- Brochure DiaДокумент2 страницыBrochure DiaAntonioОценок пока нет

- Samaple Telecoms Consult Company ProfileДокумент18 страницSamaple Telecoms Consult Company ProfiledawitОценок пока нет

- CV Canada2cДокумент2 страницыCV Canada2cPathmnathan Gopal PillayОценок пока нет

- Notes Automatic ComputingДокумент58 страницNotes Automatic ComputingPuneetShahОценок пока нет

- CATAN PresentationДокумент1 страницаCATAN PresentationAlexander Kim WaingОценок пока нет

- Techno-Economic Analysis of Telecommunication NetworksДокумент19 страницTechno-Economic Analysis of Telecommunication NetworksAsya OrhanОценок пока нет

- Embedded Deep Learning: Algorithms, Architectures and Circuits for Always-on Neural Network ProcessingОт EverandEmbedded Deep Learning: Algorithms, Architectures and Circuits for Always-on Neural Network ProcessingОценок пока нет

- Industrial Sensors and Controls in Communication Networks: From Wired Technologies to Cloud Computing and the Internet of ThingsОт EverandIndustrial Sensors and Controls in Communication Networks: From Wired Technologies to Cloud Computing and the Internet of ThingsОценок пока нет

- Using Artificial Neural Networks for Analog Integrated Circuit Design AutomationОт EverandUsing Artificial Neural Networks for Analog Integrated Circuit Design AutomationОценок пока нет

- Voicespector Datasheet AccessДокумент1 страницаVoicespector Datasheet Accessbardf2Оценок пока нет

- Voicespector Datasheet HomenetДокумент1 страницаVoicespector Datasheet Homenetbardf2Оценок пока нет

- MIDAS A110 B PDFДокумент1 страницаMIDAS A110 B PDFbardf2Оценок пока нет

- Midas A110 AДокумент1 страницаMidas A110 Abardf2Оценок пока нет

- Guide Skepticism FrenchДокумент16 страницGuide Skepticism Frenchbardf2Оценок пока нет

- Midas A110 BДокумент1 страницаMidas A110 Bbardf2Оценок пока нет

- Voicespector Datasheet HomenetДокумент1 страницаVoicespector Datasheet Homenetbardf2Оценок пока нет

- PR1988 11Документ40 страницPR1988 11bardf2Оценок пока нет

- SWEDEN-The Electronic Communications Act 2003 389Документ24 страницыSWEDEN-The Electronic Communications Act 2003 389Eddie Urenda TellezОценок пока нет

- Cours Triple Quadruple Play ISEPДокумент85 страницCours Triple Quadruple Play ISEPbardf2Оценок пока нет

- DG33BU SpecUpdate04 PDFДокумент6 страницDG33BU SpecUpdate04 PDFycabreragОценок пока нет

- ElotrixX Leveling & Farming ScriptДокумент4 страницыElotrixX Leveling & Farming ScriptCristian Bustamante CarrascoОценок пока нет

- Haries B. Garcia: Career SummaryДокумент3 страницыHaries B. Garcia: Career SummaryHaries Bugarin GarciaОценок пока нет

- Indian Institute of Tecnology, Roorkee: AUTUMN SEMESTER:-2016-17Документ20 страницIndian Institute of Tecnology, Roorkee: AUTUMN SEMESTER:-2016-17Allyne CristinaОценок пока нет

- Optimasi Parameter 3D Printing Terhadap Keakuratan Dimensi Dan Kekasaran Permukaan Produk Menggunakan Metode Taguchi GreyДокумент4 страницыOptimasi Parameter 3D Printing Terhadap Keakuratan Dimensi Dan Kekasaran Permukaan Produk Menggunakan Metode Taguchi GreyRoni SewikoОценок пока нет

- Oracle Nosql Database,: 12.1.3.5, COMMUNITY EDITIONДокумент5 страницOracle Nosql Database,: 12.1.3.5, COMMUNITY EDITIONCarlos Mario HerreraОценок пока нет

- Freescale Tower System Development Board PlatformДокумент4 страницыFreescale Tower System Development Board Platformb_dupОценок пока нет

- EOLO Mini Wall-Hung Boiler User ManualДокумент27 страницEOLO Mini Wall-Hung Boiler User ManualFlorian Leordeanu0% (1)

- Victims Analysis 2004-2009Документ47 страницVictims Analysis 2004-2009Peter HermannОценок пока нет

- SDR EssorДокумент41 страницаSDR EssorLee MarxОценок пока нет

- 3 Axially Loaded Vertical Piles and Pile Groups in Layered SoilДокумент15 страниц3 Axially Loaded Vertical Piles and Pile Groups in Layered SoilaОценок пока нет

- STAAD Pro V8i Analytic Service Structure AnalysisДокумент28 страницSTAAD Pro V8i Analytic Service Structure AnalysisramОценок пока нет

- Arcsight Connector Supported Products FlyerДокумент8 страницArcsight Connector Supported Products FlyerRamnesh DubeyОценок пока нет

- At Mega 8535Документ275 страницAt Mega 8535itmyОценок пока нет

- Multiplexing TechniquessДокумент37 страницMultiplexing TechniquessSahilPrabhakarОценок пока нет

- PO7-1 Yang, YaohuiДокумент1 страницаPO7-1 Yang, YaohuikrmcharigdcОценок пока нет

- Introduction To SOA-SOCДокумент13 страницIntroduction To SOA-SOCAdnan Kunic100% (1)

- DocuДокумент77 страницDocuDon'tAsK TheStupidOnesОценок пока нет

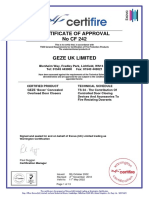

- Certificate of Approval No CF 242Документ13 страницCertificate of Approval No CF 242Florin RazvanОценок пока нет

- Beam Detectors Application Guide: System Sensor EuropeДокумент12 страницBeam Detectors Application Guide: System Sensor EuropeMohamed AdelОценок пока нет

- A Convention Center PDFДокумент71 страницаA Convention Center PDFMudita PiseОценок пока нет

- INSTALL AND SERVICE 21ST CENTURY LIGHTSДокумент84 страницыINSTALL AND SERVICE 21ST CENTURY LIGHTSAnonymous D9bqxF100% (1)