Академический Документы

Профессиональный Документы

Культура Документы

Tema 1 - Latch Flip Flop PDF

Загружено:

Elmer525Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Tema 1 - Latch Flip Flop PDF

Загружено:

Elmer525Авторское право:

Доступные форматы

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

ANALISIS y DISEO DE CIRCUITOS

CON BIESTABLES

Anlisis de circuitos de biestable R-S con puertas lgicas

Anlisis de otros biestables con puertas lgicas

Anlisis de biestables con puertas lgicas sincronizados

Representacin grfica de biestables como bloque funcional

Transformacin de un tipo de biestable en otro

Mquinas de estados modelos de Mealy y Moore

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 1

Circuito Secuencial

E

N S

Salida A

T

R Entrada CIRCUITO L

I

A Entrada D

D SECUENCIAL

Salida A

A S

S

Los circuitos secuenciales se caracterizan por que los

valores de la seal de salida en un instante determinado

dependen del valor de las entradas y del valor de la

salida en el instante anterior

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 2

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 1

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Biestable R-S con puertas NOR

R S Q(T) /Q(T) Q(t+1) /Q((T+1) RESUMEN

R

1 Q1

0 0 0 1 0 1

7402 Q(T)

0 0 1 0 1 0

0 1 0 1 1 0

0 1 1 0 1 0 1

1 0 0 1 0 1

0

2 Q2 1 0 1 0 0 1

S

1 1 0 1 0 0

7402

1 1 1 0 0 0 PROHIBIDO

Q1 = Q(T)

Q2 = /Q(T)

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 3

Biestable R-S (Puertas NOR)

Tabla de Transicin

Smbolo R S Q(T+1)

0 0 Q(t)

S 1S Q 0 1 1

1 0 0

1 1 *

Tabla de Excitacin

R 1R Q

Q(T) Q(T+1) R S

0 0 X 0

ANSI/IEEE 91-1984 0 1 0 1

1 0 1 0

1 1 0 X

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 4

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 2

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Cronograma de evolucin de un Biestable R-S

S 1S Q R

t

S

t

R 1R Q Q

t

Q

t

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 5

Biestable R-S con puertas NAND

R S Q(T) /Q(T) Q(t+1) /Q((T+1) RESUMEN

R 0 0 0 1 1 1

1 Q

PROHIBIDO

0 0 1 0 1 1

0 1 0 1 0 1

0 1 1 0 0 1 0

1 0 0 1 1 0

1 0 1 0 1 0 1

2 Q 1 1 0 1 0 1

S

1 1 1 0 1 0 Q(T)

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 6

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 3

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Biestable R-S (Puertas NAND)

Smbolo Tabla de Transicin

R S Q(T+1)

S S Q

0 0 *

0 1 0

1 0 1

1 1 Q(t)

R R Q

* = Estado Prohibido

ANSI/IEEE 91-1984

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 7

Biestabla J-K

Tabla de Transicin

Smbolo

J K Q(T+1)

0 0 Q(t)

J J Q

0 1 0

1 0 1

1 1 /Q(t)

K K Q Tabla de Excitacin

Q(T) Q(T+1) J K

0 0 0 X

ANSI/IEEE 91-1984 0 1 1 X

1 0 X 1

1 1 X 0

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 8

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 4

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

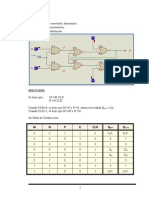

Biestable J-K con puertas lgicas

J K Q(T) /Q(T) Q(t+1) /Q((T+1) RESUMEN

0 0 0 1 0 1

J S

1 Q(T)

3 Q 0 0 1 0 1 0

7400 0 1 0 1 0 1

7400

0 1 1 0 0 1 0

1 0 0 1 1 0

1 0 1 0 1 0 1

4 Q 1 1 0 1 1 0

R

2 /Q(T)

K 1 1 1 0 0 1

7400

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 9

Cronograma de evolucin de un Biestable J-K

J

J J Q

t

K

t

K K Q Q

t

Q

t

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 10

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 5

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Biestable D puertas

R

1

2 Q

D Q(T) /Q(T) Q(t+1) /Q((T+1)

7402

7402 0 0 1 0 1

0 1 0 0 1

1 0 1 1 0

1 1 0 1 0

S 3 Q

D

7402

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 11

Biestable R-S (Puertas NOR)

Tabla de Transicin

Smbolo

D Q(T+1)

0 0

D 1D Q

1 1

Q Tabla de Excitacin

Q(T) Q(T+1) D

0 0 0

ANSI/IEEE 91-1984 0 1 1

1 0 0

1 1 1

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 12

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 6

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Cronograma de evolucin de un Biestable R-S

D 1D Q

t

Q

t

Q

Q

t

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 13

Biestable R-S Sincronizado por Nivel

R

Q

7408 R S CLK Q(t+1) /Q((T+1)

7402

CLK X X 0 Q(t+1) /Q(t+1)

0 0 1 Q(t+1) /Q(t+1)

Q 0 1 1 1 0

S 1 0 1 0 1

7402

7408 1 1 1 Prohibido

CIRCUITO DE BIESTABLE RS

SINCRONISMO ASNCRONO

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 14

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 7

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Cronograma de evolucin de un Biestable

J-K Sincronizado por nivel

S

t

S 1S Q R

t

C C1 CLK

t

R 1R Q Q

t

Q

t

ANSI/IEEE 91-1984

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 15

Biestable D Sincronizado por Nivel Alto

D S Tabla de Transicin

1

3 Q

7400 D CLK Q(t+1)

7400

0 0 Q(t)

1 0 Q(t)

0 1 0

1 1 1

R 4 Q

2

6

7404

7400

CLK 7400

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 16

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 8

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Circuito antirrebotes

VCC

Falsos contactos aleatorios

R2

10 k

+5 V 5V

2 Salida

0V

7400

A

Interruptor

2 Vout hacia la B

posicin 1

1

Interruptor 1 Salida

en reposo sobre

R la posicin 2

R1 7400

10 k

VCC

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 17

Biestable J-K Master-Slave

MASTER

J S Q0 SLAVE

R

S Q1 Q

K R Q0

S

R Q1 Q

CLK

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 18

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 9

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Diagrama de tiempos respecto a al seal de

sincronismo Master-Slave

Aislamiento entre Transferencia

el Master-Slave Master-Slave

Apertura del Cierre del

Master Master

2 3

50% 50%

1 4

tw

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 19

Cronograma de evolucin de un Biestable J-K

Master.Slave

CLK

t

J 1J Q J

t

C C1 K

t

K 1K Q Q(t)

t

Q(t)

t

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 20

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 10

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Biestable J-K Master-Slave con entradas

asncronas de Reset y Clear

PRESET (PR)

SLAVE

MASTER

J Q

CLK

K

Q

CLEAR (CLR)

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 21

Smbolo del Biestable J-K sincrono con

entradas de Preset y Clear

Smbolos

Tabla de Transicin CL

J Q

CL PR J K Q(T+1) CLK

0 1 X X 0 K Q

PR

1 0 X X 1

1 1 0 0 Q(t)

PRE

1 1 0 1 0

1 1 1 0 1 S

J J Q

1 1 1 /Q(t)

CLK C

K K Q

R

CLR

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 22

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 11

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Biestable D sincronizado por flanco de subida

1A

Tabla de Transicin

CLK D Q(T+1) 1B

S 3A

0 X Q(t) Q

1 X Q(t) CLK

0 0 2A

Q

1 1

R 3B

2B

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 23

Cronograma de evolucin de un Biestable D

Sincronizado por flanco de subida

Smbolo

D Q

CLK

D

Q

t

ANSI/IEEE 91-1973 CLK

t

D 1D 1Q Q

CLK C1

t

1Q

ANSI/IEEE 91-1984

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 24

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 12

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Cronograma de evolucin de un BiestableJ-K

Sincronizado por flanco de bajada

CL

J Q

CLK

K Q CLK

PR

t

J

PRE t

K

S t

J J Q

Q

t

CLK C

Q

t

K K Q

R

CLR

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 25

Parmetros de los biestables

tclk: Duracin mnima del impulso de reloj

tset-up: Tiempo mnimo que debe de estar presente

una entrada de excitacin antes del flanco activo de

FLANCO reloj

t clock ACTIVO thold: Tiempo mnimo que debe permanecer una

entrada de excitacin despus del flanco activo del

reloj.

CLK tpd : Tiempo de retardo de propagacin. Es el

tiempo transcurrido entre el flanco activo de l reloj

y la aparicin de la seal de salida

fmax: Frecuencia mxima. Es la mxima frecuencia

ENTRADA

t set-up que se puede aplicar a la entrada CLK de un

t hold biestable que asegure que ste se dispare.

tw(L) : Tiempo mnimo que la seal de reloj (CLK)

SALIDA

debe permanecer a nivel bajo antes de que pase a

nivel alto.

t pd tw(H) : Tiempo mnimo que la seal de reloj (CLK)

debe permanecer a nivel alto antes de que pase a

nivel bajo.

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 26

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 13

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Representacin de los biestables como

bloques funcinales

74L5112

ENTRADAS 1 PRE S 1Q

ENTRADAS ASNCRONAS PRE 1J 1J

SNCRONAS 1 CLK C1

S

J J Q 1K 1K

1 CLR R 1Q

CLK C

SALIDAS 2 PRE 2Q

K K Q 2J

R

2 CLK

RELOJ

2K

CLR

2 CLR 2Q

Biestable genrico Representacin del biestable 74112

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 27

Transformacin de un tipo de biestable en otro

S Q Q(t )

J

Circuito

combinacional

K

R Q Q(t )

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 28

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 14

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Transformacin de un biestable R-S en uno J-K

JK

Q(t) 00 01 11 10 S Q Q

J

0 1 1

7408

1 X X CLK

S = JQ(t) K R Q Q

JK 7408

Q(t) 00 01 11 10

0 X X Implementacin de un biestable

1 1 1 J-K a partir de un biestable R-S

R = KQ(t)

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 29

Clasificacin de los biestables por su forma de

disparo

Asncronos

Biestables

Por nivel

Sncronos

Master-Slave

Por flanco Disparo por flanco de subida

Disparo por flanco de bajada

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 30

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 15

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Mquina de estados de Moore

Entrada

Salida

Et

Circuito It + 1 Elemento It Circuito St

It combinacional de combinacional

de entrada memoria de salida

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 31

Mquina de estados de Mealy

Entrada

Et

Salida

Circuito It + 1 Elemento Circuito St +1

It combinacional de It combinacional

de entrada memoria de salida

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 32

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 16

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Divisor de frecuencia por 3. Modelo de Moore

Diagrama de flujos Diagrama de Tiempos

X=0

I1 / 0 Entrada

t

I0 I1 I2 I0

Salida

t

X=1

I0 / 1 I2 / 0

X=0 X=0

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 33

Divisor de frecuencia por 3. Modelo de Mealy

Diagrama de flujos

Diagrama de Tiempos

X=0/S=0

I1

Entrada

t

I2 I0 I1 I2

Salida

X=1/S=1

I0 I2 t

X=0/S=0 X=0/S=0

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 34

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 17

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Circuito del divisor de frecuencia por 3

con los modelos de Moore y Mealy

Salida de

Mealy

J0 Q0 J1 Q1

CLK CLK CLK

X K0 Q0 K1 Q1

Salida de

Moore

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 35

Circuito del divisor de frecuencia por 3

simplificado modelos de Moore y Mealy

S1

Entrada J0 Q0 J1 Q1

X = CLK Salida de

Mealy

K0 Q0 K1 Q1

1 1

Salida de

Moore

S2

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 36

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 18

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Divisor de frecuencias por 3 con arranque

asncrono e iniciacin en fri

Arranque

asncrono S1

Entrada J0 Q0 J1 Q1

X = CLK Salida de

Mealy

K0 Q0 K1 Q1

1 CL 1 CL

Salida de

Moore

S2

Inicializacin

Iniciacin

en fro

S1

Entrada J0 Q0 J1 Q1

X = CLK Salida de

Mealy

+ Vcc K0 Q0 K1 Q1

1 1

Salida de

Moore

10 k

S2

22 F

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 37

Diseo de un dado electrnico

Diagrama de Estados

X=0 X=0 X=0 X=0 X=0 X=0

X=1 X=1 X=1 X=1 X=1

I0 / 001 I1 / 010 I2 / 011 I3 / 100 I4 / 101 I5 / 110

X=1

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 38

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 19

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

Diseo de un dado electrnico

Circuito Mquina de Circuito

generador de Estados de

impulsos Visualizacin

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 39

Circuito Dado Electrnico

+ Vcc = 5 V

10 k

a b c d e f g

22 F

7448

BI/

1 2 4 8 RBO RBI LT

PR Q S2 PR Q S1 PR Q S0

J2 2(t) J1 1(t) J0 0(t)

CLK CLK CLK + Vcc

K2 Q2(t) K1 Q1(t) K0 Q0(t)

CL CL CL

7476 (1) 7476 (2) 7476 (3) 10 k

Impulsos

de clock

de 10 kHz

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 40

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 20

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables

0/ X=0/S=1

X=1/S=0 X=0/S=0 X=0/S=0 X=0/S=0

I0 I1 I2 I3 I4

=

X=1/S=1

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 41

Z0 Z1

Q0 Q1

J0 J1

CLK

C C

Q0 Q1

K0 K1

Capitulo 5: Anlisis y Diseo de Circuitos con Biestables 42

Lgica Digital y Microprogramable. Autor: Fernando Remiro Domnguez 21

Вам также может понравиться

- Reconocimiento de Materiales Peligrosos en 5 MinutosДокумент1 страницаReconocimiento de Materiales Peligrosos en 5 MinutosElmer525Оценок пока нет

- Archivo 1Документ50 страницArchivo 1Ivan Hermilio Mera IbarguenОценок пока нет

- MATPEL 2 IdentificaciónДокумент1 страницаMATPEL 2 IdentificaciónElmer525Оценок пока нет

- Tasas Tarifas Cts PDFДокумент1 страницаTasas Tarifas Cts PDFElmer525Оценок пока нет

- Estudio de La Tecnología de Comunicación Por Radiofrecuencia RFID y Su ImplementaciónДокумент110 страницEstudio de La Tecnología de Comunicación Por Radiofrecuencia RFID y Su ImplementaciónElmer525Оценок пока нет

- Tarea Academica - Simulacion de Sistemas - Upc PDFДокумент4 страницыTarea Academica - Simulacion de Sistemas - Upc PDFElmer525Оценок пока нет

- La Tecnologia RFID - HuidobroДокумент10 страницLa Tecnologia RFID - HuidobroGonzaloОценок пока нет

- Horarios Por Ciclos 2018 0 Electronica Vi X 06ene18Документ5 страницHorarios Por Ciclos 2018 0 Electronica Vi X 06ene18LuceroMilagrosCubaMirandaОценок пока нет

- Laboratorio Calificado N°2 - Viernes 24/05/19 - AdanaqueДокумент2 страницыLaboratorio Calificado N°2 - Viernes 24/05/19 - AdanaqueElmer525Оценок пока нет

- 2da Tarea de Circuitos Digitales 2 (2015-2)Документ8 страниц2da Tarea de Circuitos Digitales 2 (2015-2)Elmer5250% (1)

- Identificación Por Radiofrecuencia Fundamentos y Aplicaciones PDFДокумент10 страницIdentificación Por Radiofrecuencia Fundamentos y Aplicaciones PDFedgardoboieroОценок пока нет

- Examen Parcial 2017-1 - DISEÑO DIGITAL - FIEE - UNMSMДокумент3 страницыExamen Parcial 2017-1 - DISEÑO DIGITAL - FIEE - UNMSMElmer525Оценок пока нет

- C02 PDFДокумент37 страницC02 PDFElmer525Оценок пока нет

- Sistemas Digitales Problemas 2 PDFДокумент27 страницSistemas Digitales Problemas 2 PDFElmer525Оценок пока нет

- Control de Velocidad de Un Motor DC Con DacДокумент9 страницControl de Velocidad de Un Motor DC Con DacElmer525100% (1)

- Diseño Avanzado de Controladores SISO: Parte 4Документ24 страницыDiseño Avanzado de Controladores SISO: Parte 4Myriam Raquel Gaete GaeteОценок пока нет

- Informe #1 - Lab. Introducción A Las TelecomunicacionesДокумент22 страницыInforme #1 - Lab. Introducción A Las TelecomunicacionesElmer525Оценок пока нет

- Apuntes Medios de Transmisi NДокумент19 страницApuntes Medios de Transmisi NAnita GonzálezОценок пока нет

- Tema1 Circuitos Temporizadores 74121 74122 74123Документ21 страницаTema1 Circuitos Temporizadores 74121 74122 74123Julio David Vilca PizarroОценок пока нет

- Tarea Domiciliaria de Circuitos Digitales IIДокумент9 страницTarea Domiciliaria de Circuitos Digitales IIDaniel DzmОценок пока нет

- Control AutomaticoДокумент34 страницыControl AutomaticoJonathan Jara MontecinosОценок пока нет

- 1P SistCont I ExPa 2015-2Документ2 страницы1P SistCont I ExPa 2015-2Elmer525Оценок пока нет

- 2da Tarea Mestas 2016-2Документ11 страниц2da Tarea Mestas 2016-2Elmer525Оценок пока нет

- FisicaДокумент26 страницFisicawalterОценок пока нет

- Resonancia en ParaleloДокумент11 страницResonancia en ParaleloElmer525Оценок пока нет

- A5Документ46 страницA5edsg29Оценок пока нет

- Modelos de Organización Del Sector ElectricoДокумент5 страницModelos de Organización Del Sector ElectricoElmer525Оценок пока нет

- Mediciones Electronicas - Mestas 2016-2Документ14 страницMediciones Electronicas - Mestas 2016-2Elmer525Оценок пока нет

- Los Microcontroladores en La IndustriaДокумент5 страницLos Microcontroladores en La IndustriaElmer525Оценок пока нет

- Arias Barrera Cayambe Galarza Yanez U2 Trabajo2Документ27 страницArias Barrera Cayambe Galarza Yanez U2 Trabajo2Vanessa KatherineОценок пока нет

- ILANEДокумент98 страницILANEJorge Alberto Delgadillo CarpinteyroОценок пока нет

- Rs 232 Rs 485Документ2 страницыRs 232 Rs 485DanielaToaquizaОценок пока нет

- Pagina DBM A Wats y ViceversaДокумент3 страницыPagina DBM A Wats y ViceversaRICARDO ALEJANDRO MONTOYA ORTIZОценок пока нет

- Identificacion de ComponentesДокумент9 страницIdentificacion de Componentesmiguel-angel-tinesco-9633Оценок пока нет

- Especificaciones Generales Ii Electricas Rev1Документ30 страницEspecificaciones Generales Ii Electricas Rev1Thaiss Tupayachi VeneroОценок пока нет

- Practica #3 Lab. Fisica IIIДокумент4 страницыPractica #3 Lab. Fisica IIIAndy Alexander Lopez OvalleОценок пока нет

- Practica 8-Osciloscopio PDFДокумент31 страницаPractica 8-Osciloscopio PDFBRAYANОценок пока нет

- Mapa Mental de Componentes de PCДокумент3 страницыMapa Mental de Componentes de PCVivian Vargas100% (1)

- Túpac Katari 1 (87.2º W) - EDS en Español PDFДокумент7 страницTúpac Katari 1 (87.2º W) - EDS en Español PDFJairo Romero25% (4)

- Estandares RobóticaДокумент6 страницEstandares Robóticacarlos25878Оценок пока нет

- Bastidores de AbonadoДокумент35 страницBastidores de AbonadoFernando CornejoОценок пока нет

- Digital Signal Processing - Schaum - En.esДокумент447 страницDigital Signal Processing - Schaum - En.esjoseyumizaca100% (6)

- Planificación Anual 2DO AñoДокумент14 страницPlanificación Anual 2DO AñoWilfredo Evelio Durán MejíaОценок пока нет

- Quiz 1 - Semana 6 - CB - Segundo Bloque-Fisica IIДокумент5 страницQuiz 1 - Semana 6 - CB - Segundo Bloque-Fisica IIDavid Yaya0% (1)

- Técnicas Digitales Apunte 6 - Circuitos SecuencialesДокумент39 страницTécnicas Digitales Apunte 6 - Circuitos SecuencialesProf Matias GarciaОценок пока нет

- Component EsДокумент2 страницыComponent EsDeyf 88Оценок пока нет

- Motores de corriente continua en serie: características, usos y perdidasДокумент10 страницMotores de corriente continua en serie: características, usos y perdidasMarco Antonio Veranza VazquezОценок пока нет

- Circuito RC en SerieДокумент14 страницCircuito RC en SeriemiguelcaliОценок пока нет

- Semana 13 (1ra Parte) AAGP FISE UTP Máq Eléc Est y RotativasДокумент11 страницSemana 13 (1ra Parte) AAGP FISE UTP Máq Eléc Est y RotativasGonzalo SotoОценок пока нет

- Certificado de Mantenimiento de SubestacionesДокумент3 страницыCertificado de Mantenimiento de SubestacionesPablo Yaguillo100% (2)

- Practica 01 Sist ControlДокумент11 страницPractica 01 Sist ControlAlex CruzОценок пока нет

- Lab01 ArquitecturaДокумент9 страницLab01 ArquitecturaJhojam Fabian VitoОценок пока нет

- Rectificadores ControladosДокумент61 страницаRectificadores ControladosBERLY CHOQUE HUARAYAОценок пока нет

- Cómo Funciona HARTДокумент4 страницыCómo Funciona HARTCésar Chinguel Arrese100% (3)

- 5.1 Sensor de Oxigeno de Banda AnchaДокумент10 страниц5.1 Sensor de Oxigeno de Banda AnchaRonaldo Matias100% (1)

- TeslaДокумент18 страницTeslaELVIS VLADIMIR ACARAPI CALLISAYAОценок пока нет

- Comparadores analógicos PIC18F2550Документ6 страницComparadores analógicos PIC18F2550Lsknho KennyОценок пока нет

- WebSphere MQ SeriesДокумент121 страницаWebSphere MQ SeriesJuan López VillegasОценок пока нет

- Lab3 ElectrotecniaДокумент10 страницLab3 ElectrotecniaPatrick Hitedoshi Nakamura VillavicencioОценок пока нет