Академический Документы

Профессиональный Документы

Культура Документы

EE220 Lec7 KMaps PDF

Загружено:

SalaarОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

EE220 Lec7 KMaps PDF

Загружено:

SalaarАвторское право:

Доступные форматы

Adeel Pasha, LUMS, Spring 2017

CS/EE-220: Lecture 7

Two-Level Circuits Optimization using K-Maps

Quiz Time

2 CS/EE-220: Digital Logic Circuits 2/14/2017

Adeel Pasha, LUMS, Spring 2017

Two Level Circuit Optimization

Manual logic simplification can be done but it

is awkward

has no set of rules

such as what Boolean identity to be used and when?

has lower efficiency

have we reached the simplest form of the solution or not?

cannot be automated

Example? Simplify F = ABC+ABC+ABC+ABC+ABC

Done in class (in three different ways, there can still be others)

To do it systematically Kernaugh (K) Maps are used

Automation can be done!

3 CS/EE-220: Digital Logic Circuits 2/14/2017

K-Maps

4 CS/EE-220: Digital Logic Circuits 2/14/2017

Adeel Pasha, LUMS, Spring 2017

K-Maps

A diagram made of squares

Graphical representation of the truth table

Each square represent a Minterm

B 1

A 0

0 1

0

2 3

1

5 CS/EE-220: Digital Logic Circuits 2/14/2017

Adeel Pasha, LUMS, Spring 2017

K-Maps

Graphical representation of Sum of Minterms

Example: F(A, B) = m (0, 1, 3)

B 1

A 0

AB 0 AB 1

0 1 1

AB 2 AB 3

1

1

6 CS/EE-220: Digital Logic Circuits 2/14/2017

Adeel Pasha, LUMS, Spring 2017

K-Maps

No. of squares are equal to no. of minterms in truth table

2 variable K-Map: 2 2 Square Map

3 variable K-Map: 2 4 Rectangular Map

4 variable K-Map: 4 4 Square Map

7 CS/EE-220: Digital Logic Circuits 2/14/2017

Adeel Pasha, LUMS, Spring 2017

3-variable

BC

K-Maps

00 01 11 10

A

m0 m1 m3 m2

0

m4 m5 m7 m6

1

But WHY the funny placement?

We can observe that

Row-1 terms m0, m1, m3, m2 are adjacent

Row-2 terms m4, m5, m7, m6 are adjacent

All columns terms are adjacent as well

Even the boundary terms of each row [m0, m2] and [m4, m6] are

adjacent

8 CS/EE-220: Digital Logic Circuits 2/14/2017

Adeel Pasha, LUMS, Spring 2017

4-variable K-Maps

CD 01

AB 00 11 10

m0 m1 m3 m2

00

m4 m5 m7 m6

01

m12 m13 m15 m14

11

m8 m9 m11 m10

10

9 CS/EE-220: Digital Logic Circuits 2/14/2017

Adeel Pasha, LUMS, Spring 2017

4-variable K-Maps

We can observe that

All rows have terms that are adjacent

All columns have terms that are adjacent as well

Even the boundary terms of each row are adjacent

Can be wrapped to make a cylinder

And finally the boundary terms of each column are adjacent

Can be wrapped vertically to convert the cylinder into a

donut/tube shape

10 CS/EE-220: Digital Logic Circuits 2/14/2017

Adeel Pasha, LUMS, Spring 2017

Circuit Optimization using K-Maps

Step-1: Make a K-Map

Input Form1: Truth Table

Input Form2: Canonical form as Sum of Minterms (SoM)

What if not in standard form? Thats why in last lecture I taught you to

go from non-canonical to canonical form through expansion

Step-2: Identify the collection of squares that can be part of

final simplified solution

Form rectangles whose sides are in power of 2

1 1, 1 2, 2 1, 2 2 and so on (remember no 13, 23, etc.)

No such rectangle can contain an empty cell/box

No diagonal covering

Use the biggest rectangle as it will lead to minimum terms/cost

11 CS/EE-220: Digital Logic Circuits 2/14/2017

Adeel Pasha, LUMS, Spring 2017

Circuit Optimization using K-Maps

Step-3: Determine if any rectangle is redundant

The 1s in K-Map are already covered without it

If so, again keep the largest and drop the smaller redundant ones

Step-4: Read off the map to form a SoP

Examples: Done in class

12 CS/EE-220: Digital Logic Circuits 2/14/2017

3-variable K-Maps Examples

13 CS/EE-220: Digital Logic Circuits 2/14/2017

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- MIT7 29JS12 Lecture6Документ5 страницMIT7 29JS12 Lecture6SalaarОценок пока нет

- Spatio-Temporal Analysis of P300 Using ICA and SslofoДокумент4 страницыSpatio-Temporal Analysis of P300 Using ICA and SslofoSalaarОценок пока нет

- MIT7 29JS12 Lecture4Документ5 страницMIT7 29JS12 Lecture4SalaarОценок пока нет

- MIT7 29JS12 Lecture3Документ5 страницMIT7 29JS12 Lecture3SalaarОценок пока нет

- MIT7 29JS12 Lecture2Документ5 страницMIT7 29JS12 Lecture2SalaarОценок пока нет

- MIT7 29JS12 Lecture5Документ4 страницыMIT7 29JS12 Lecture5SalaarОценок пока нет

- Outline EE 340 LUMSДокумент4 страницыOutline EE 340 LUMSSalaarОценок пока нет

- 7 DNA DMG and RepairДокумент9 страниц7 DNA DMG and RepairSalaarОценок пока нет

- Solution Manual of Digital Logic and Computer Design (2nd Edition) Morris Mano PDFДокумент40 страницSolution Manual of Digital Logic and Computer Design (2nd Edition) Morris Mano PDFSadaf Rasheed0% (4)

- Microelectronic Circuits Sedra Smith 6th Edition Solution Manual For INTERNATIONAL EDITIONДокумент226 страницMicroelectronic Circuits Sedra Smith 6th Edition Solution Manual For INTERNATIONAL EDITIONEliab60% (42)

- CH 01Документ27 страницCH 01Abhay SinghОценок пока нет

- Chapter 02 and 03 and 04 PDFДокумент83 страницыChapter 02 and 03 and 04 PDFSalaarОценок пока нет

- Non-Coding RNA and Gene RegulationДокумент21 страницаNon-Coding RNA and Gene RegulationSalaarОценок пока нет

- Presentation Group9Документ13 страницPresentation Group9SalaarОценок пока нет

- A National Culture For PakistanДокумент23 страницыA National Culture For Pakistantoorie100% (1)

- Chatterjee - Nation and Fragments - PP 3-13Документ7 страницChatterjee - Nation and Fragments - PP 3-13juan manuel díaz pasОценок пока нет

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- CA Level 2Документ50 страницCA Level 2Cikya ComelОценок пока нет

- PUBLIC - Axie Origins Changelogs - Season 4Документ2 страницыPUBLIC - Axie Origins Changelogs - Season 4Alef CarlosОценок пока нет

- HSG 2023 KeyДокумент36 страницHSG 2023 Keyle827010Оценок пока нет

- F. Moyra Allen: A Life in Nursing, 1921-1996: Meryn Stuart, R.N., PH.DДокумент9 страницF. Moyra Allen: A Life in Nursing, 1921-1996: Meryn Stuart, R.N., PH.DRose Nirwana HandayaniОценок пока нет

- Simple Past and Past Perfect TensesДокумент13 страницSimple Past and Past Perfect TensesSincerly RevellameОценок пока нет

- Test 1801 New Holland TS100 DieselДокумент5 страницTest 1801 New Holland TS100 DieselAPENTOMOTIKI WEST GREECEОценок пока нет

- EIL 6-51-0051-Rev 06 - 1.1kv-Xlpe - Dimension Cat - B Armour-BbpДокумент2 страницыEIL 6-51-0051-Rev 06 - 1.1kv-Xlpe - Dimension Cat - B Armour-BbpShubham BaderiyaОценок пока нет

- Jurnal KORELASI ANTARA STATUS GIZI IBU MENYUSUI DENGAN KECUKUPAN ASIДокумент9 страницJurnal KORELASI ANTARA STATUS GIZI IBU MENYUSUI DENGAN KECUKUPAN ASIMarsaidОценок пока нет

- Gender and Patriarchy: Crisis, Negotiation and Development of Identity in Mahesh Dattani'S Selected PlaysДокумент6 страницGender and Patriarchy: Crisis, Negotiation and Development of Identity in Mahesh Dattani'S Selected Playsতন্ময়Оценок пока нет

- - Анализ текста The happy man для ФЛиС ЮФУ, Аракин, 3 курсДокумент2 страницы- Анализ текста The happy man для ФЛиС ЮФУ, Аракин, 3 курсJimmy KarashОценок пока нет

- A List of 142 Adjectives To Learn For Success in The TOEFLДокумент4 страницыA List of 142 Adjectives To Learn For Success in The TOEFLchintyaОценок пока нет

- Reviewer CSCДокумент22 страницыReviewer CSCChristopher CocalОценок пока нет

- Evolution of Management AccountingДокумент35 страницEvolution of Management AccountingNuqiah Fathiah Seri100% (1)

- A Meta Analysis of The Relative Contribution of Leadership Styles To Followers Mental HealthДокумент18 страницA Meta Analysis of The Relative Contribution of Leadership Styles To Followers Mental HealthOnii ChanОценок пока нет

- Northern Lights - 7 Best Places To See The Aurora Borealis in 2022Документ15 страницNorthern Lights - 7 Best Places To See The Aurora Borealis in 2022labendetОценок пока нет

- HSG Vs SonohysterographyДокумент4 страницыHSG Vs Sonohysterography#15Оценок пока нет

- Aits 2122 PT I Jeea 2022 TD Paper 2 SolДокумент14 страницAits 2122 PT I Jeea 2022 TD Paper 2 SolSoumodeep NayakОценок пока нет

- Madam Shazia PaperДокумент14 страницMadam Shazia PaperpervaizhejОценок пока нет

- Promoting Services and Educating CustomersДокумент28 страницPromoting Services and Educating Customershassan mehmoodОценок пока нет

- 3 HVDC Converter Control PDFДокумент78 страниц3 HVDC Converter Control PDFJanaki BonigalaОценок пока нет

- Design and Analysis of DC-DC Boost Converter: September 2016Документ5 страницDesign and Analysis of DC-DC Boost Converter: September 2016Anonymous Vfp0ztОценок пока нет

- Determination of Hydroxymethylfurfural (HMF) in Honey Using The LAMBDA SpectrophotometerДокумент3 страницыDetermination of Hydroxymethylfurfural (HMF) in Honey Using The LAMBDA SpectrophotometerVeronica DrgОценок пока нет

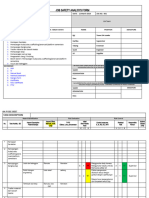

- JSA FormДокумент4 страницыJSA Formfinjho839Оценок пока нет

- Week1 TutorialsДокумент1 страницаWeek1 TutorialsAhmet Bahadır ŞimşekОценок пока нет

- English 8 q3 w1 6 FinalДокумент48 страницEnglish 8 q3 w1 6 FinalJedidiah NavarreteОценок пока нет

- Opening Checklist: Duties: Monday Tuesday Wednesday Thursday Friday Saturday SundayДокумент3 страницыOpening Checklist: Duties: Monday Tuesday Wednesday Thursday Friday Saturday SundayAlven BlancoОценок пока нет

- Glory in The Cross - Holy Thursday - Schutte PDFДокумент1 страницаGlory in The Cross - Holy Thursday - Schutte PDFsharon0murphyОценок пока нет

- CFodrey CVДокумент12 страницCFodrey CVCrystal N FodreyОценок пока нет

- Pharmacy System Project PlanДокумент8 страницPharmacy System Project PlankkumarОценок пока нет

- Mechanics of Materials 7th Edition Beer Johnson Chapter 6Документ134 страницыMechanics of Materials 7th Edition Beer Johnson Chapter 6Riston Smith95% (96)