Академический Документы

Профессиональный Документы

Культура Документы

Clase 04 - Puertos E - S

Загружено:

Marcos TiconaОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Clase 04 - Puertos E - S

Загружено:

Marcos TiconaАвторское право:

Доступные форматы

Puertos E/S de la Familia DSPIC33E/PIC24E

PUERTOS E/S

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Puertos de Entrada y Salida

Los puertos de E/S de propsito general permiten al dsPIC33EP256MU806

supervisar y controlar otros dispositivos. La mayora de los pines E/S son

multiplexados con funciones alternativas. La multiplexacin depende de las

funciones perifricas. En general, cuando un perifrico est funcionando el pin

no se puede usar como un pin de E/S de propsito general, Para este dsPIC se

tienen 6 puertos de E/S para un total de 51 pines :

Puerto B :16 pines (RB0-RB15)

Puerto C: 4 pines (RC12-RC15)

Puerto D: 12 pines (RD0-RD11)

Puerto E: 8 pines (RE0-RE7)

Puerto F: 5 pines (RF0-RF1, RF3-RF5)

Puerto G: 6 pines (RG2-RG3, RG6-RG9)

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

PUERTOS E/S

Todos los puertos de E / S tienen cuatro registros directamente

relacionados con la operacin del puerto, donde 'x' es una letra

que denota el puerto de E / S en particular:

TRISx: Registro de Direccin de Datos

PORTx: Registro del Puerto de E/S

LATx: Registro Latch de E/S

ODCx: Registro de control de drenador abierto

Cada pin de E / S en el dispositivo dispone de un bit asociado en

los registros TRIS, el puerto y LAT.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

PUERTOS E/S

Registro PORTx

Los datos sobre un pin de E/S se acceden a travs de un registro

PORTx. Una lectura del registro PORTx lee el valor del pin de E /S,

mientras que una escritura en el registro PORTx escribe el valor en

el latch del puerto.

Registro LATx

El LATx registro asociado con un pin de E/S elimina los problemas

que pueden ocurrir con bidireccionalidad. Una lectura del registro

LATx restaura los valores en el puerto de salida de los latchs en

lugar de los valores en los pines de E/S. Una operacin de

bidireccionalidad en el registro LAT asociado con un puerto de E/S

evita la posibilidad de escribir los valores pin de entrada en el

puerto de latch. Una escritura en el registro LATx tiene el mismo

efecto que una escritura en el registro PORTx.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

PUERTOS E/S

Registro TRISx

Los bits de control del registro TRISx determinan si cada pin

asociado con el puerto de E/S es una entrada o salida. Si el bit TRIS

para un pin de E/S es un '1 ', entonces el pin es una entrada. Si el

bit de TRIS para un pin de E/S es un '0 ', entonces el pin se

configura como una salida.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

PUERTOS E/S

Registro de control Open-Drain

Adems de los registros de control PORT, LAT, y TRIS, cada pin del

puerto tambin se puede configurar de forma individual, ya sea

para una salida digital o drenador abierto. Esto es controlado por

el registro ODCx, asociado con cada puerto. Seteando cualquiera

de los bits configura el pin correspondiente para actuar como una

salida de drenador abierto.

La funcin de drenador abierto permite la generacin de salidas

superiores a VDD (por ejemplo, 5V) en los pines de 5V tolerant

deseados mediante el uso externo resistencias pull-up. (La

caracterstica de drenador abierto no se admite en los pines que

no son 5V tolerant). El voltaje mximo permitido es igual a la

especificacin VIH. La funcin de salida de drenador abierto es

compatible con los pines del puerto a la vez y las configuraciones

de perifricos.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

DIAGRAMA DE BLOQUES DE UN PUERTO E/S

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

DIAGRAMA DE BLOQUES DE UN PUERTO E/S

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Selector de Pin de Perifrico (PPS)

Un reto importante en los dispositivos de propsito general es proporcionar el mayor

conjunto posible de funciones perifricas, adems de minimizar el conflicto de funciones

en los pines de E / S. El desafo es an mayor en los dispositivos de pin de bajo conteo. En

una aplicacin en la que ms de un perifrico necesita asignarse a un solo pin, soluciones

inconvenientes en el cdigo de aplicacin o un rediseo completo puede ser la nica

opcin.

Pines Disponibles

El nmero de pines disponibles depende del dispositivo y su nmero de pines. Los Pines

que soportan la funcin Peripheral Pin Select tienen la designacin "RPn" o Rpin, donde

"RP designa una funcin remapeable o reasignable para entrada o salida y "RPI" designa

una funcin remapeable o reasignables para la entrada solamente, y "n" es el nmero de

pin remapeable.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Asignacin de Entrada

Las entradas de los pines del PPS se asignan sobre la base del perifrico a usar, es decir,

un registro de control asociado con un perifrico dicta el pin que se le asignar , el

registros RPINRx se utiliza para configurar la asignacin de perifricos de entrada .

Cada registro contiene un campos de 7 bits, que est asociado con un perifrico

reasignable.

Programando un valor de 7 bits correspondiente a un perifrico permite seleccionar el

pin RPn o RPIn con el perifrico se conectar. Para cualquier determinado dispositivo, la

gama de valores vlidos para cualquier campo de bits se corresponde con el nmero

mximo de Selecciones de Pin de Perifricos compatibles con el dispositivo.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

AN29/PWM3H/PMD5/RP85/RE5

Multiplexacin AN30/PWM4L/PMD6/RPI86/RE6

de Pines AN31/PWM4H/PMD7/RP87/RE7

C1IN3-/SCK2/PMA5/RP118/RG6

C1IN1-/SDI2/PMA4/RPI119/RG7

C2IN3-/SDO2/PMA3/RP120/RG8

MCLR

C2IN1-/PMA2/RPI121/RG9

VDD

AN5/C1IN1+/VBUSON/VBUSST/RPI37/RB5

AN4/C1IN2-/USBOEN/RPI36/RB4

AN3/C2IN1+/VPIO/RPI35/RB3

AN2/C2IN2-/VMIO/RPI34/RB2

PGEC3/AN1/VREF-/RPI33/RB1

PGED3/AN0/VREF+/RPI32/RB0

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Entrada remapeable para U1RX

U1RXR <6.0>

RP0/RPI0

0

0

RP1/RPI1 1

RP2/RPI2 2

Entrada U1RX

RPn/RPIn n

Nota: Slo para la entrada, la funcin PPS no tiene prioridad sobre el registro

TRISx Por lo tanto, al configurar el pin de RPn como entrada, el bit

correspondiente en el registro TRISX debe estar configurado como entrada

(seteado a '1 ').

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Registros de Seleccin de Pin de Perifricos

Los siguientes registros se utilizan para configurar la funcionalidad de entrada y

de salida de los pines de los dsPIC33E/PIC24E:

RPINR0 a RPINR37: Registros de entrada de Seleccin de Pin de Perifricos

RPOR0 a PROR15: Registros de salida de Seleccin de Pin de Perifricos

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Fuentes de entrada seleccionables

Nombre Pin de Entrada Funcin del Pin Registro Bits de Configuracin

External Interrupt 1 INT1 RPINR0 INT1R<6:0>

External Interrupt 2 INT2 RPINR1 INT2R<6:0>

External Interrupt 3 INT3 RPINR1 INT3R<6:0>

External Interrupt 4 INT4 RPINR2 INT4R<6:0>

Timer2 External Clock T2CK RPINR3 T2CKR<6:0>

Timer3 External Clock T3CK RPINR3 T3CKR<6:0>

Timer4 External Clock T4CK RPINR4 T4CKR<6:0>

Timer5 External Clock T5CK RPINR4 T5CKR<6:0>

Timer6 External Clock T6CK RPINR5 T6CKR<6:0>

Timer7 External Clock T7CK RPINR5 T7CKR<6:0>

Timer8 External Clock T8CK RPINR6 T8CKR<6:0>

Timer9 External Clock T9CK RPINR6 T9CKR<6:0>

Input Capture 1 IC1 RPINR7 IC1R<6:0>

Input Capture 2 IC2 RPINR7 IC2R<6:0>

Input Capture 3 IC3 RPINR8 IC3R<6:0>

Input Capture 4 IC4 RPINR8 IC4R<6:0>

Input Capture 5 IC5 RPINR9 IC5R<6:0>

Input Capture 6 IC6 RPINR9 IC6R<6:0>

Input Capture 7 IC7 RPINR10 IC7R<6:0>

Input Capture 8 IC8 RPINR10 IC8R<6:0>

Output Compare Fault A OCFA RPINR11 OCFAR<6:0>

Output Compare Fault B OCFB RPINR11 OCFBR<6:0>

PMW Fault 1 FLT1 RPINR12 FLT1R<6:0>

PMW Fault 2 FLT2 RPINR12 FLT2R<6:0>

PMW Fault 3 FLT3 RPINR13 FLT3R<6:0>

PMW Fault 4 FLT4 RPINR13 FLT4R<6:0>

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Nombre Pin de Entrada Funcin del Pin Registro Bits de Configuracin

QEI1 Phase A QEA1 RPINR14 QEA1R<6:0>

QEI1 Phase A QEB1 RPINR14 QEB1R<6:0>

QEI1 Index INDX1 RPINR15 INDX1R<6:0>

QEI1 Home HOME1 RPINR15 HOM1R<6:0>

QEI2 Phase A QEA2 RPINR16 QEA2R<6:0>

QEI2 Phase A QEB2 RPINR16 QEB2R<6:0>

QEI2 Index INDX2 RPINR17 INDX2R<6:0>

QEI2 Home HOME2 RPINR17 HOM2R<6:0>

UART1 Receive U1RX RPINR18 U1RXR<6:0>

UART1 Clear To Send U1CTS RPINR18 U1CTSR<6:0>

UART2 Receive U2RX RPINR19 U2RXR<6:0>

UART2 Clear To Send U2CTS RPINR19 U2CTSR<6:0>

SPI1 Data Input SDI1 RPINR20 SDI1R<6:0>

SPI1 Clock Input SCK1IN RPINR20 SCK1R<6:0>

SPI1 Slave Select SS1IN RPINR21 SS1R<6:0>

SPI2 Data Input SDI2 RPINR22 SDI2R<6:0>

SPI2 Clock Input SCK2IN RPINR22 SCK2R<6:0>

SPI2 Slave Select SS2IN RPINR23 SS2R<6:0>

DCI Data Input CSDI RPINR24 CSDIR<6:0>

DCI Clock Input CSCKIN RPINR24 CSCKR<6:0>

DCI FSYNC Input COFSIN RPINR25 COFSR<6:0>

CAN1 Receive C1RX RPINR26 C1RXR<6:0>

CAN2 Receive C2RX RPINR26 C2RXR<6:0>

UART3 Receive U3RX RPINR27 U3RXR<6:0>

UART3 Clear To Send U3CTS RPINR27 U3CTSR<6:0>

UART4 Receive U4RX RPINR28 U4RXR<6:0>

UART4 Clear To Send U4CTS RPINR28 U4CTSR<6:0>

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Nombre Pin de Entrada Funcin del Pin Registro Bits de Configuracin

SPI3 Data Input SDI3 RPINR29 SDI3R<6:0>

SPI3 Clock Input SCK3IN RPINR29 SCK3R<6:0>

SPI3 Slave Select SS3IN RPINR30 SS3R<6:0>

SPI4 Data Input SDI4 RPINR31 SDI4R<6:0>

SPI4 Clock Input SCK4IN RPINR31 SCK4R<6:0>

SPI4 Slave Select SS4IN RPINR32 SS4R<6:0>

Input Capture 9 IC9 RPINR33 IC9R<6:0>

Input Capture 10 IC10 RPINR33 IC10R<6:0>

Input Capture 11 IC11 RPINR34 IC11R<6:0>

Input Capture 12 IC12 RPINR34 IC12R<6:0>

Input Capture 13 IC13 RPINR35 IC13R<6:0>

Input Capture 14 IC14 RPINR35 IC14R<6:0>

Input Capture 15 IC15 RPINR36 IC15R<6:0>

Input Capture 16 IC16 RPINR36 IC16R<6:0>

Output Compare Fault C OCFC RPINR37 OCFCR<6:0>

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Valor del registro de Entrada/Salida Pin Asignado Valor del registro de Entrada/Salida Pin Asignado

entrada del PPS entrada del PPS

000 0000 E VSS 001 1011 Reservado

000 0001 E C1OUT(1) 001 1100 Reservado

000 0010 E C2OUT(1) 001 1101 Reservado

000 0011 E C3OUT(1) 001 1110 E RPI30

000 0100 Reservado 001 1111 E RPI31

000 0101 Reservado 010 0000 E RPI32

000 0110 Reservado 010 0001 E RPI33

000 0111 Reservado 010 0010 E RPI34

000 1000 E FINDX1(1) 010 0011 E RPI35

000 1001 E FHOME1(1) 010 0100 E RPI36

000 1010 E FINDX2(1) 010 0101 E RPI37

000 1011 E FHOME2(1) 010 0110 E RPI38

000 1100 Reservado 010 0111 E RPI39

000 1101 Reservado 010 1000 E RPI40

000 1110 Reservado 010 1001 E RPI41

000 1111 Reservado 010 1010 E RPI42

001 0000 E RPI16 010 1101 E RPI45

001 0001 E RPI17 010 1110 E RPI46

001 0010 E RPI18 010 1111 E RPI47

001 0011 E RPI19 011 0000 Reservado

001 0100 E RPI20 011 0001 E RPI49

001 0101 E RPI21 011 0010 E RPI50

001 0110 E RPI22 011 0011 E RPI51

001 0111 E RPI23 011 0100 E RPI52

001 1000 Reservado 011 0101 Reservado

001 1001 Reservado 011 0110 Reservado

001 1010 Reservado 011 0111 Reservado

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Valor del registro de Entrada/Salida Pin Asignado Valor del registro de Entrada/Salida Pin Asignado

entrada del PPS entrada del PPS

011 1000 Reservado 101 0100 E/S RP84

011 1001 Reservado 101 0101 E/S RP85

011 1010 Reservado 101 0110 E RPI86

011 1011 Reservado 101 0111 E/S RP87

011 1100 E RPI60 010 1011 E RPI43

011 1101 E RPI61 010 1100 E RPI44

011 1110 E RPI62 101 1010 Reservado

011 1111 Reservado 101 1011 Reservado

100 0000 E/S RP64 101 1100 Reservado

100 0001 E/S RP65 101 1101 Reservado

100 0010 E/S RP66 101 1110 Reservado

100 0011 E/S RP67 101 1111 Reservado

100 0100 E/S RP68 110 0000 E/S RP96

100 0101 E/S RP69 110 0001 E/S RP97

100 0110 E/S RP70 110 0010 E/S RP98

100 0111 E/S RP71 110 0011 E/S RP99

100 1000 E RPI72 110 0100 E/S RP100

100 1001 E RPI73 110 0101 E/S RP101

100 1010 E RPI74 110 0110 E/S RP102

100 1011 E RPI75 110 0111 Reservado

100 1100 E RPI76 110 1000 E/S RP104

100 1101 E RPI77 110 1001 Reservado

100 1110 E RPI78 110 1010 Reservado

100 1111 E/S RP79 110 1011 Reservado

101 0000 E/S RP80 110 1100 E/S RP108

101 0001 E RPI81

101 0010 E/S RP82

101 0011 E RPI83

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Valor del registro de Entrada/Salida Pin Asignado

entrada del PPS

101 1000 E RPI88

101 1001 E RPI89

110 1101 E/S RP109

110 1110 Reservado

110 1111 Reservado

111 0000 E/S RP112

111 0001 E/S RP113

111 0010 Reservado

111 0011 Reservado

111 0100 Reservado

111 0101 Reservado

111 0110 E/S RP118

111 0111 E RPI119

111 1000 E/S RP120

111 1001 E RPI121

111 1010 Reservado

111 1011 Reservado

111 1100 E RPI124

111 1101 E/S RP125

111 1110 E/S RP126

111 1111 E/S RP127

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Conexiones virtuales

Los dsPIC33EPXXX (GP / MC / MU) 806/810/814 (GP / GU) 810/814 y los

PIC24EPXXX poseen conexiones internas a la salida de los mdulos comparadores

mdulos, CMP1OUT, CMP2OUT y CMP3OUT. Adems, admiten conexiones virtuales

a los mdulos QEI en los pines FINDX1, FHOME1, FINDX2 y FHOME2 .

Las conexiones virtuales proporcionan una forma sencilla de interconexin sin la

utilizacin de una conexin fsica entre pines. Por ejemplo, mediante la

configuracin de los bits FLT1R <6:0> del registro RPINR12 con el valor 'b0000001,

la salida del comparador analgico, CMP1OUT, ser conectado a la entrada del pin

de falla 1 del PWM, que permite que el comparador analgico dispare por falla el

PWM sin el uso de una conexin fsica real entre mdulos en el dispositivo

Ejemplos:

RPINR15 = 0x5600; /* Conecta la entrada QEI1/HOME1 a RP86 (pin 3) */

RPINR7 = 0x009; /* Conecta la entrada IC1 a la entrada FHOME1 */

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

REGISTRO 0 ENTRADA DE SELECCIN PIN DEL PERIFERICO

(RPINR0)

INT1R<6:0>

Bit 15 Bit 8

Bit 7 Bit 0

bit 15 no implementado: Leer como '0

INT1R <6:0>: Asignar interrupcin externa 1 (INT1) al correspondiente pin RPn / rpin

1111111 = Entrada conectada a RP127

...

0000001 = Entrada conectada a CMP1

0000000 = Entrada conectada a VSS

bits 7-0 no implementadas: Leer como '0 '

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

REGISTRO 1 ENTRADA ELECCIN DE PIN DEL PERIFERICO (RPINR1)

INT3R<6:0>

Bit 15 Bit 8

INT2R<6:0>

Bit 7 Bit 0

INT3R <6:0>: Asignar interrupcin externa 3 (INT3) al correspondiente pin RPn / rpin

1111111 = Entrada conectada a RP127

...

0000001 = Entrada conectada a CMP1

0000000 = Entrada conectada a VSS

INT2R <6:0>: Asignar interrupcin externa 2 (INT2) al correspondiente pin RPn / rpin

1111111 = Entrada conectada a RP127

...

0000001 = Entrada conectada a CMP1

0000000 = Entrada conectada a VSS

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Mapa de registros de entrada para la seleccin de pin de perifricos

(PPS) solo para dsPIC33EPXXXMU806

Nombre Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Reset

Fila

RPINR0 INT1R<6:0> 0

RPINR1 INT3R<6:0> INT2R<6:0> 0

RPINR2 INT4R<6:0> 0

RPINR3 T3CKR<6:0> T2CKR<6:0> 0

RPINR4 T5CKR<6:0> T4CKR<6:0> 0

RPINR5 T7CKR<6:0> T6CKR<6:0> 0

RPINR6 T9CKR<6:0> T8CKR<6:0> 0

RPINR7 IC2R<6:0> IC1R<6:0> 0

RPINR8 IC4R<6:0> IC3R<6:0> 0

RPINR9 IC6R<6:0> IC5R<6:0> 0

RPINR10 IC8R<6:0> IC7R<6:0> 0

RPINR11 OCFBR<6:0> OCFAR<6:0> 0

RPINR12 FLT2R<6:0> FLT1R<6:0> 0

RPINR13 FLT4R<6:0> FLT3R<6:0> 0

RPINR14 QEB1R<6:0> QEA1R<6:0> 0

RPINR15 HOME1R<6:0> INDX1R<6:0> 0

RPINR16 QEB2R<6:0> QEA2R<6:0> 0

RPINR17 HOME2R<6:0> INDX2R<6:0> 0

RPINR18 U1CTSR<6:0> U1RXR<6:0> 0

RPINR19 U2CTSR<6:0> U2RXR<6:0> 0

RPINR20 SCK1R<6:0> SDI1R<6:0> 0

RPINR21 SS1R<6:0> 0

RPINR22 SCK2R<6:0> SDI2R<6:0> 0

RPINR23 SS2R<6:0> 0

RPINR24 CSCKR<6:0> CSDIR<6:0> 0

RPINR25 COFSINR<6:0> 0

RPINR26 C2RXR<6:0> C1RXR<6:0> 0

RPINR27 U3CTSR<6:0> U3RXR<6:0> 0

RPINR28 U4CTSR<6:0> U4RXR<6:0> 0

RPINR29 SCK3R<6:0> SDI3R<6:0> 0

RPINR30 SS3R<6:0> 0

RPINR31 SCK4R<6:0> SDI4R<6:0> 0

RPINR32 SS4R<6:0> 0

RPINR33 IC10R<6:0> IC9R<6:0> 0

RPINR34 IC12R<6:0> IC11R<6:0> 0

RPINR35 IC14R<6:0> IC13R<6:0> 0

RPINR36 IC16R<6:0> IC15R<6:0> 0

RPINR37 SYNCI1R<6:0> OCFCR<6:0> 0

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Asignacin de salida

En contraste a las entradas, las salidas de las opciones PPS se asignan sobre

la base del pin. En este caso, un registro de control asociado con un pin en

particular dicta el perifrico salida que se asigna. Los registros RPORx se

utilizan para controlar la asignacin de salida. Al igual que el registro

RPINRx, cada registro contiene conjuntos de 6 bits, con cada conjunto

asociado con un pin de RPn. El valor del campo de bits se corresponde

a uno de los perifricos, y la salida del perifrico se correlaciona con el pin.

Una salida nula se asocia con el registro de salida al colocar valor de '0 '.

Esto se hace para asegurar que PPS por defecto permanezcan

desconectados de todas las terminales de salida.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Multiplexacin de salida remapeable para RPn

RPnR <5.0>

Puerto por Defecto

0

0

Salida U1TX 1

Salida de datos

Salida U1RTS 2

RPn

Salida REFCLK 49

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Fuentes de salidas seleccionables

Funcin RPnR<5:0> Nombre de la Salida

DEFAULT PORT 00 0000 RPn conectado a pin por defecto

U1TX 00 0001 RPn conectado a UART1 transmit

U1RTS 00 0010 RPn conectado a UART1 ready to send

U2TX 00 0011 RPn conectado a UART2 transmit

U2RTS 00 0100 RPn conectado a UART2 ready to send

SDO1 00 0101 RPn conectado a SPI1 data output

SCK1OUT 00 0110 RPn conectado a SPI1 clock output

SS1OUT 00 0111 RPn conectado a SPI1 slave select

SDO2 00 1000 RPn conectado a SPI2 data output

SCK2OUT 00 1001 RPn conectado a SPI2 clock output

SS2OUT 00 1010 RPn conectado a SPI2 slave select

CSDO 00 1011 RPn conectado a DCI data output

CSCKOUT 00 1100 RPn conectado a DCI clock output

COFSOUT 00 1101 RPn conectado a DCI FSYNC output

C1TX 00 1110 RPn conectado a CAN1 transmit

C2TX 00 1111 RPn conectado a CAN2 transmit

OC1 01 0000 RPn conectado a Output Compare 1 output

OC2 01 0001 RPn conectado a Output Compare 2 output

OC3 01 0010 RPn conectado a Output Compare 3 output

OC4 01 0011 RPn conectado a Output Compare 4 output

OC5 01 0100 RPn conectado a Output Compare 5 output

OC6 01 0101 RPn conectado a Output Compare 6 output

OC7 01 0110 RPn conectado a Output Compare 7 output

OC8 01 0111 RPn conectado a Output Compare 8 output

C1OUT 01 1000 RPn conectado a Comparator Output 1

C2OUT 01 1001 RPn conectado a Comparator Output 2

C3OUT 01 1010 RPn conectado a Comparator Output 3

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Funcin RPnR<5:0> Nombre de la Salida

U3TX 01 1011 RPn conectado a UART3 transmit

U3RTS 01 1100 RPn conectado a UART3 ready to send

U4TX 01 1101 RPn conectado a UART4 transmit

U4RTS 01 1110 RPn conectado a UART4 ready to send

SDO3 01 1111 RPn conectado a SPI3 data output

SCK3OUT 10 0000 RPn conectado a SPI3 clock output

SS3OUT 10 0001 RPn conectado a SPI3 slave select

SDO4 10 0010 RPn conectado a SPI4 data output

SCK4OUT 10 0011 RPn conectado a SPI4 clock output

SS4OUT 10 0100 RPn conectado a SPI4 slave select

OC9 10 0101 RPn conectado a Output Compare 9 output

OC10 10 0110 RPn conectado a to Output Compare 10 output

OC11 10 0111 RPn conectado a Output Compare 11 output

OC12 10 1000 RPn conectado a Output Compare 12 output

OC13 10 1001 RPn conectado a Output Compare 13 output

OC14 10 1010 RPn conectado a Output Compare 14 output

OC15 10 1011 RPn conectado a Output Compare 15 output

OC16 10 1100 RPn conectado a Output Compare 16 output

PSYNCO1 10 1101 RPn conectado a PWM primary time base sync output

PSYNCO2 10 1110 RPn conectado a PWM secondary time base sync output

QEI1CCMP 10 1111 RPn conectado a QEI1 counter comparator output

QEI2CCMP 11 0000 RPn conectado a QEI2 counter comparator output

REFCLK 11 0001 RPn conectado a Reference Clock output

Nota: En el DsPIC33EP256MU806 existen 20 pines RPn

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

REGISTRO 0 SALIDA SELECCIN DE PIN DEL PERIFERICO (RPOR0)

RP65R<5:0>

Bit 15 Bit 8

RP64R<5:0>

Bit 7 Bit 0

RP65R<5:0>: Bits del pin de salida RP65 es asignado a al perifrico designado por el

campo de bits (Ver tabla anterior).

RP64R<5:0>: >: Bits del pin de salida RP64 es asignado a al perifrico designado por el

campo de bits (Ver tabla anterior).

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Mapa de registros de salida para la seleccin de pin de perifricos

(PPS) solo para dsPIC33EPXXXMU806

Nombre Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Reset

RPOR0 RP65R<5:0> RP64R<5:0> 0

RPOR1 RP67R<5:0> RP66R<5:0> 0

RPOR2 RP69R<5:0> RP68R<5:0> 0

RPOR3 RP71R<5:0> RP70R<5:0> 0

RPOR4 RP80R<5:0> 0

RPOR5 RP84R<5:0> RP82R<5:0> 0

RPOR6 RP87R<5:0> RP85R<5:0> 0

RPOR7 RP97R<5:0> RP95R<5:0> 0

RPOR8 RP99R<5:0> 0

RPOR9 RP101R<5:0> RP100R<5:0> 0

RPOR13 RP118R<5:0>

RPOR14 RP120R<5:0> 0

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

REGISTRO DE BLOQUEO DE CONTROL

En condiciones de funcionamiento normal, escribir en los registros RPINRx y

RPORx no est permitidos. Al escribirse aparecer para ejecutar

normalmente, pero el contenido de los registros permanecern sin cambios.

Para cambiar estos registros, deben ser desbloqueados en el hardware. El

bloqueo de registro es controlado por el bit IOLOCK (OSCCON <6>).

Seteando el bit IOLOCK impide escribir en los registros de control, limpiando

IOLOCK permite la escritura.

Para setear o resetear IOLOCK, una secuencia de comandos especfica se

debe ejecutar:

1. Escribir 0x46 para OSCCON <7:0>.

2. Escribir 0x57 para OSCCON <7:0>.

3. Setear o resetear IOLOCK en una sola operacin.

IOLOCK permanece en un estado hasta que se cambie. Esto permite que

todo el Pin PPS sea configurado con una secuencia de desbloqueo nico

seguido de una actualizacin de todos los registros de control.

Entonces, IOLOCK se setear con una segunda secuencia de bloqueo

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

SEGUIMIENTO CONTINUO DEL ESTADO DEL PPS

Adems de ser protegido escrituras directas, el contenido de la RPINRx y RPORx

registros son constantemente monitoreados en el hardware por registros sombra. Si un

cambio inesperado en cualquiera de los registros se produce (tales como trastornos

celulares causados por eventos externos ESD o de otro tipo), un Reset discrepancia de

configuracin se activar (reset por configuracin mismatch).

BIT DE CONFIGURACIN DE BLOQUEO DE PPS

Como un nivel adicional de seguridad, el dispositivo se puede configurar para evitar que

se produzca ms de una sesin de escritura para los registros RPINRx y RPORx. El bit de

configuracin IOL1WAY (FOSC<5>) bloquea que el bit IOLOCK se borre despus de que se

ha seteado una vez.

En el estado por defecto (no programada), IOL1WAY es seteado, para restringir a usuarios

a una sesin de escritura.

La programacin de IOL1WAY permite a los usuarios acceso ilimitado (con el uso correcto

de la secuencia de desbloqueo) a los pines perifricos Seleccin de registros.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Registros de Control de Cambio (CN)

Tres registros de control estn asociados con el mdulo de CN: CNENx, CNPUx y CNPDx,

donde 'X' indica la letra del puerto.

Los registros CNENx contienen los bits de control CNIExy, donde 'y' denota el nmero de

pin del puerto. El Bit CNIExy debe setearse para que un pin de entrada del puerto

pueda interrumpir el CPU.

Cada pin CN tiene un dispositivo pull-up y pull-down conectado al pin, que puede ser

activado o desactivado con los bits de los registros CNPUx y CNPDx de manera de

aumentar la corriente con dispositivos de entradas y evitan el uso de resistencias externas.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Configuracin CN y Funcionamiento

CN ser configurado de la siguiente manera:

1. Asegrese de que el pin del puerto est configurado como una entrada digital seteando

el bit asociado en el registro TRISX respectivo.

2. Habilitar las interrupciones para los pines del puerto seleccionados mediante el seteo de

los bits correspondientes en el registro CNENx.

3. Active los Pull-up (si lo desea) para los pines del puerto seleccionados mediante el seteo

de los bits correspondiente en el registro CNPUx.

4. Active los Pull-Down (si lo desea) para los pines del puerto seleccionados mediante el

seteo de los bits apropiados en el registro CNPDx.

5. Borrar la bandera de interrupcin CNIF en el registro IFSx.

6. Seleccione la prioridad de interrupcin para interrupciones CN deseada utilizando elos

bits de control CNIP <2:0> en el registro el IPCx.

7. Habilitar interrupciones CN utilizando el bit de control CNIE en el registro IECx.

Cuando una interrupcin por CN ocurre, el software del usuario debe leer el registro del

puerto asociado con los pines de CN. Esto borrar la condicin de conflicto y establecer la

lgica CN para detectar el prximo cambio de nivel. El valor actual del puerto se puede

comparar con el valor ledo del PUERTO obtenido en la ltima interrupcin CN para

determinar que pin cambi.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Diagrama de bloques para la entrada de notificacin de

cambio en el pin RE5

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Configuracin y uso de la interrupcin CN

void configure CN(void)

{

CNENBbits.CNIB3 = 1; // Habilita el pin RB3 para interrupcin

IEC1bits.CNIE = 1; // Habilita Interrupcin CN

IFS1bits.CNIF = 0; // Resetea interrupcin CN

}

void __attribute__ ((__interrupt__)) _CNInterrupt(void)

{

// Cdigo aqui

IFS1bits.CNIF = 0; // Borra bandera interrupcin CN

}

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Registros de Notificacin de Cambio

Los siguientes registros se utilizan para activar y desactivar las interrupciones CN

correspondientes, y las resistencias pull-up y pull-down:

CNENx: Registro para habilitar interrupcin en la entrada CN.

CNPUDx: Registro para habilitar Pull-Up en la entrada CN.

CNPDx: Registro para habilitar Pull-Down en la entrada CN.

ANSELx: Registro de control de entrada analgica.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

REGISTRO DE HABILITACION DE INTERRUPCION POR NOTIFICACION DE

CAMBIO EN LA ENTRADA (CNENx)

CNIEx15 CNIEx14 CNIEx13 CNIEx12 CNIEx11 CNIEx10 CNIEx9 CNIEx8

Bit 15 Bit 8

CNIEx7 CNIEx6 CNIEx5 CNIEx4 CNIEx3 CNIEx2 CNIEx1 CNIEx0

Bit 7 Bit 0

CNIExy: Bit de habilitacin de interrupcin por notificacin de cambio en la entrada.

1 = Habilitada interrupcin por cambio en entrada.

0 = Desabilitada interrupcin por cambio en la Entrada.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

REGISTRO DE HABILITACION DE PULL-UP POR NOTIFICACION DE CAMBIO EN

LA ENTRADA (CNPUDx)

CNPUx15 CNPUx14 CNPUx13 CNPUx12 CNPUx11 CNPUx10 CNPUx9 CNPUx8

Bit 15 Bit 8

CNPUx7 CNPUx6 CNPUx5 CNPUx4 CNPUx3 CNPUx2 CNPUx1 CNPUx0

Bit 7 Bit 0

CNPUxy: Bit de habilitacin de pull-up por notificacin de cambio en la entrada

1 = Habilita pull-up por cambio en Entrada

0 = Desabilita pull-up por cambio en Entrada

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

REGISTRO DE HABILITACION DE PULL-DOWN POR NOTIFICACION DE CAMBIO

EN LA ENTRADA (CNPDx)

CNPDx15 CNPDx14 CNPDx13 CNPDx12 CNPDx11 CNPDx10 CNPDx9 CNPDx8

Bit 15 Bit 8

CNPDx7 CNPDx6 CNPDx5 CNPDx4 CNPDx3 CNPDx2 CNPDx1 CNPDx0

Bit 7 Bit 0

CNPDxy: Bits de habilitacin de pull-down por notificacin de cambio en la entrada

1 = Habilita pull-down por cambio en Entrada

0 = Desabilita pull-down por cambio en Entrada

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

REGISTRO DE CONTROL DE SELECCIN ANALOGICA (ANSELx)

ANSx15 ANSx14 ANSx13 ANSx12 ANSx11 ANSx10 ANSx9 ANSx8

Bit 15 Bit 8

ANSx7 ANSx6 ANSx5 ANSx4 ANSx3 ANSx2 ANSx1 ANSx0

Bit 7 Bit 0

ANSxy: Bits de habilitacin de Puerto Analgicos.

1 = Habilitacin de puertos como pines analgicos.

0 = Habilitacin de puertos como pines digitales.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

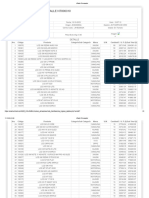

Mapa de registros del puerto B solo para dsPIC33EPXXXMU806

Nombre Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 resets

TRISB TRISB15 TRISB14 TRISB13 TRISB12 TRISB11 TRISB10 TRISB9 TRISB8 TRISB7 TRISB6 TRISB5 TRISB4 TRISB3 TRISB2 TRISB1 TRISB0 FFFF

PORTB RB15 RB14 RB13 RB12 RB11 RB10 RB9 RB8 RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 xxxx

LATB LATB15 LATB14 LATB13 LATB12 LATB11 LATB10 LATB9 LATB8 LATB7 LATB6 LATB5 LATB4 LATB3 LATB2 LATB1 LATB0 xxxx

ODCB 0

CNENB CNIEB15 CNIEB14 CNIEB13 CNIEB12 CNIEB11 CNIEB10 CNIEB9 CNIEB8 CNIEB7 CNIEB6 CNIEB5 CNIEB4 CNIEB3 CNIEB2 CNIEB1 CNIEB0 0

CNPUB CNPUB15 CNPUB14 CNPUB13 CNPUB12 CNPUB11 CNPUB10 CNPUB9 CNPUB8 CNPUB7 CNPUB6 CNPUB5 CNPUB4 CNPUB3 CNPUB2 CNPUB1 CNPUB0 0

CNPDB CNPDB15 CNPDB14 CNPDB13 CNPDB12 CNPDB11 CNPDB10 CNPDB9 CNPDB8 CNPDB7 CNPDB6 CNPDB5 CNPDB4 CNPDB3 CNPDB2 CNPDB1 CNPDB0 0

ANSELB ANSB15 ANSB14 ANSB13 ANSB12 ANSB11 ANSB10 ANSB9 ANSB8 ANSB7 ANSB6 ANSB5 ANSB4 ANSB3 ANSB2 ANSB1 ANSB0 FFFF

Mapa de registros del puerto C solo para dsPIC33EPXXXMU806

Nombre Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 resets

TRISC TRISC15 TRISC14 TRISC13 TRISC12 FFFF

PORTC RC15 RC14 RC13 RC12 xxxx

LATC LATC15 LATC14 LATC13 LATC12 xxxx

ODCC 0

CNENC CNIEC15 CNIEC14 CNIEC13 CNIEC12 0

CNPUC CNPUC15 CNPUC14 CNPUC13 CNPUC12 0

CNPDC CNPDC15 CNPDC14 CNPDC13 CNPDC12 0

ANSELC FFFF

Mapa de registros del puerto D solo para dsPIC33EPXXXMU806

Nombre Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 resets

TRISD TRISD11 TRISD10 TRISD9 TRISD8 TRISD7 TRISD6 TRISD5 TRISD4 TRISD3 TRISD2 TRISD1 TRISD0 FFFF

PORTD RD11 RD10 RD9 RD8 RD7 RD6 RD5 RD4 RD3 RD2 RD1 RD0 xxxx

LATD LATD11 LATD10 LATD9 LATD8 LATD7 LATD6 LATD5 LATD4 LATD3 LATD2 LATD1 LATD0 xxxx

ODCD ODCD11 ODCD10 ODCD9 ODCD8 ODCD5 ODCD4 ODCD3 ODCD2 ODCD1 ODCD0 0

CNEND CNIED11 CNIED10 CNIED9 CNIED8 CNIED7 CNIED6 CNIED5 CNIED4 CNIED3 CNIED2 CNIED1 CNIED0 0

CNPUD CNPUD11 CNPUD10 CNPUD9 CNPUD8 CNPUD7 CNPUD6 CNPUD5 CNPUD4 CNPUD3 CNPUD2 CNPUD1 CNPUD0 0

CNPDD CNPDD11 CNPDD10 CNPDD9 CNPDD8 CNPDD7 CNPDD6 CNPDD5 CNPDD4 CNPD3 CNPDD2 CNPDD1 CNPDD0 0

ANSELD FFFF

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Mapa de registros del puerto E solo para dsPIC33EPXXXMU806

Nombre Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 resets

TRISE TRISE7 TRISE6 TRISE5 TRISE4 TRISE3 TRISE2 TRISE1 TRISE0 FFFF

PORTE RE7 RE6 RE5 RE4 RE3 RE2 RE1 RE0 xxxx

LATE LATE7 LATE6 LATE5 LATE4 LATE3 LATE2 LATE1 LATE0 xxxx

ODCE 0

CNENE CNIEE7 CNIEE6 CNIEE5 CNIEE4 CNIEE3 CNIEE2 CNIEE1 CNIEE0 0

CNPUE CNPUE7 CNPUE6 CNPUE5 CNPUE4 CNPUE3 CNPUE2 CNPUE1 CNPUE0 0

CNPDE CNPDE7 CNPDE6 CNPDE5 CNPDE4 CNPDE3 CNPDE2 CNPDE1 CNPDE0 0

ANSELE ANSE7 ANSE6 ANSE5 ANSE4 ANSE3 ANSE2 ANSE1 ANSE0 FFFF

Mapa de registros del puerto F solo para dsPIC33EPXXXMU806

Nombre Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 resets

TRISF TRISF5 TRISF4 TRISF3 TRISF1 TRISF0 FFFF

PORTF RF5 RF4 RF3 RF1 RF0 xxxx

LATF LATF5 LATF4 LATF3 LATF1 LATF0 xxxx

ODCF ODCF5 ODCF4 ODCF3 ODCF1 ODCF0 0

CNENF CNIEF5 CNIEF4 CNIEF3 CNIEF1 CNIEF0 0

CNPUF CNPUF5 CNPUF4 CNPUF3 CNPUF1 CNPUF0 0

CNPDF CNPDF5 CNPDF4 CNPDF3 CNPDF1 CNPDF0 0

ANSELF FFFF

Mapa de registros del puerto G solo para dsPIC33EPXXXMU806

Nombre Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 resets

TRISG TRISG9 TRISG8 TRISG7 TRISG6 FFFF

PORTG RG9 RG8 RG7 RG6 RG3 RG2 xxxx

LATG LATG9 LATG8 LATG7 LATG6 xxxx

ODCG 0

CNENG CNIEG9 CNIEG8 CNIEG7 CNIEG6 CNIEG3 CNIEG2 0

CNPUG CNPUG9 CNPUG8 CNPUG7 CNPUG6 0

CNPDG CNPDG9 CNPDG8 CNPDG7 CNPDG6 0

ANSELG FFFF

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Librerias de puertos en Mikro C

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Unlock_IOLOCK

Puertos E/S de la Familia DSPIC33E/PIC24E

Unlock_IOLOCK

Prototipo void Unlock_IOLOCK();

Descripcin Desbloquea pines de E/S de

mapeo del pin del Perifrico.

Parmetros Ninguno

Valor que retorna Nada

Requerimientos Nada

Ejemplos Unlock_IOLOCK();

Notas Ninguna

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Unlock_IOLOCK

Puertos E/S de la Familia DSPIC33E/PIC24E

lock_IOLOCK

Prototipo void Lock_IOLOCK();

Descripcin Bloquea pines de E/S de mapeo

del pin del Perifrico.

Parmetros Ninguno

Valor que retorna Nada

Requerimientos Nada

Ejemplos lock_IOLOCK();

Notas Ninguna

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Unlock_IOLOCK

Puertos E/S de la Familia DSPIC33E/PIC24E

PPS_Mapping

Prototipo unsigned PPS_Mapping(unsigned short rp_num, unsigned short

direction, unsigned short funct_name);

Descripcin Configura mdulo interno del DSPIC para ser mapeado en el pin

seleccionado.

Parmetros rp_num: Numero del pin remapeable. Consulte el datasheet para

valores existentes.

direction: Configura pin deseado como entrada o salida. Ver Direction

Parameters para valores adecuados.

funct_name: Selecciona modulo interno del DSPIC para ser usado en

el pin. Ver Input Functions o Output Functions Para valores adecuados.

Valor que retorna 0 Si no existe pin seleccionado.

1 Si la funcin deseada no est implementado en el DSPIC.

2 Si algun registro RPOUT configura para salida el mdulo SCK1OUT

mientras SCK1CM es setado (solo para la familia P24FJ256GA110).

255 Si el mapeo fue exitoso.

Requerimientos Nada

Ejemplos PPS_Mapping(64, _INPUT, _U2RX); // Configura pin RP64 como

entrada, y conecta pin RX del UART2 a esta.

PPS_Mapping(99, _OUTPUT, _U2TX); // configura pin RP99 como

salida, y conecta Pin TX del UART2 a esta.

Notas Use esta rutina cuando el bit IOL1WAY este limpio.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Unlock_IOLOCK

Puertos E/S de la Familia DSPIC33E/PIC24E

PPS_Mapping_NoLock

Prototipo unsigned PPS_Mapping_NoLock(unsigned short rp_num, unsigned short

input_output, unsigned short funct_name);

Descripcin Configura mdulo interno del DSPIC para ser mapeado en el pin seleccionado.

Esta funcion no usa Unlock_IOLOCK ni Lock_IOLOCK el usuario puede llarmarlos

antes y despues de usar esta funcin ( necesario si el bit IOL1WAY es seteado,

cuando despues de la secuencia de bloqueo no se pueda desbloquear)

Parmetros rp_num: Numero del pin remapeable. Consulte el datasheet para valores existentes.

direction: Configura pin deseado como entrada o salida. Ver Direction Parameters

para valores adecuados.

funct_name: Selecciona modulo interno del DSPIC para ser usado en el pin. Ver

Input Functions o Output Functions Para valores adecuados.

Valor que retorna 0 Si no existe pin seleccionado.

1 Si la funcin deseada no est implementado en el DSPIC.

2 Si algun registro RPOUT configura para salida el mdulo SCK1OUT mientras

SCK1CM es setado (solo para la familia P24FJ256GA110).

255 Si el mapeo fue exitoso.

Requerimientos Nada

Ejemplos Unlock_IOLOCK();

PPS_Mapping_NoLock (64, _INPUT, _U2RX) // Configura pin RP64 como entrada, y

conecta pin RX del UART2 a esta.

PPS_Mapping_NoLock (99, _OUTPUT, _U2TX); // configura pin RP99 como salida, y

conecta Pin TX del UART2 a esta.

Lock_IOLOCK();

Notas Ninguna

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Aplicacin para los puertos de entrada y salida

Se desea realizar una aplicacin que permita el manejo de una matriz de leds mediante un

dsPIC33EP256MU806, en la cual se debern mostrar diversas letras dependiendo la opcin

seleccionada por el usuario.

Para la implementacin de esta aplicacin se utilizaron algunos pines de los puertos C, D, y F

como salidas digitales, as mismo se configuraron algunos pines del puerto F como entrada

digital. Las salidas se conectaron a un buffer y a un decodificador y estos a su vez se

conectaron a una matriz de diodos LED, las entradas se conectaron a un dip-switch. Para

realizar la conexin al dip-switch se utilizaron especficamente los pines 4 y 5 del puerto F

para as obtener 4 combinaciones, las cuales son: 00, 01, 10 y 11.

Para iniciar esta aplicacin se empez configurando los puertos como entradas y salidas

digitales. Una vez realizada la configuracin se establecieron condiciones en la

programacin para que la visualizacin en la matriz de diodos LED dependiera de la

combinacin vista desde el dip-switch.

En la matriz de LED se pueden visualizar las letras A, B, C o D segn las combinaciones

00, 01, 10 y 11 respectivamente.

La figura siguiente muestra la visualizacin de cada letra segn la combinacin dada por el

dip-switch. Para efectos de visualizacin, se utilizaron 8 pines con el fin de controlar el

buffer y el decodificador, para as, lograr la correcta visualizacin en la matriz de diodos LED.

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

Aplicacin para los puertos de entrada y salida

sbit A0 at LATD5_bit;

sbit A1 at LATF1_bit;

sbit A2 at LATD1_bit;

sbit A3 at LATC13_bit;

sbit A4 at LATD9_bit;

sbit O1 at LATE4_bit;

sbit O2 at LATD3_bit;

sbit O3 at LATD10_bit;

unsigned short i;

unsigned short letra_a[5][7]={

{0,0,1,1,1,0,0},

{0,1,0,0,0,1,0},

{0,1,1,1,1,1,0},

{0,1,0,0,0,1,0},

{0,1,0,0,0,1,0}};

unsigned short letra_b[5][7]={

{0,1,1,1,1,0,0},

{0,1,0,0,0,1,0},

{0,1,1,1,1,0,0},

{0,1,0,0,0,1,0},

{0,1,1,1,1,0,0}};

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

unsigned short letra_c[5][7]={

{0,0,1,1,1,1,0},

{0,1,0,0,0,0,0},

{0,1,0,0,0,0,0},

{0,1,0,0,0,0,0},

{0,0,1,1,1,1,0}};

unsigned short letra_d[5][7]={

{0,1,1,1,1,0,0},

{0,1,0,0,0,1,0},

{0,1,0,0,0,1,0},

{0,1,0,0,0,1,0},

{0,1,1,1,1,0,0}};

void contador(unsigned short n)

{ O1= n & 0x01;

O2= (n & 0x02)>>1;

O3= (n & 0x04)>>2; }

void main() {

ANSELC=0;

ANSELD=0;

ANSELE=0;

TRISFbits.TRISF4=1; //s0

TRISFbits.TRISF5=1; //s1

TRISDbits.TRISD5=0; //a0

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

TRISFbits.TRISF1=0; //a1

TRISDbits.TRISD1=0; //a2

TRISCbits.TRISC13=0; //a3

TRISDbits.TRISD9=0; //a4

TRISEbits.TRISE4=0; //o1

TRISDbits.TRISD3=0; //o2

TRISDbits.TRISD10=0; //o3

while(1)

{ if(PORTFbits.RF4==0 && PORTFbits.RF5==0)

{ for(i=0;i<7;i++)

{ A0=letra_a[0][i];

A1=letra_a[1][i];

A2=letra_a[2][i];

A3=letra_a[3][i];

A4=letra_a[4][i];

contador(i);

Delay_ms(2);

}

}

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

else if(PORTFbits.RF4==0 && PORTFbits.RF5==1)

{ for(i=0;i<7;i++)

{ A0=letra_b[0][i];

A1=letra_b[1][i];

A2=letra_b[2][i];

A3=letra_b[3][i];

A4=letra_b[4][i];

contador(i);

Delay_ms(2);

}

}

else if(PORTFbits.RF4==1 && PORTFbits.RF5==0)

{ for(i=0;i<7;i++)

{ A0=letra_c[0][i];

A1=letra_c[1][i];

A2=letra_c[2][i];

A3=letra_c[3][i];

A4=letra_c[4][i];

contador(i);

Delay_ms(2);

}

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

}

else if(PORTFbits.RF4==1 && PORTFbits.RF5==1)

{ for(i=0;i<7;i++)

{ A0=letra_d[0][i];

A1=letra_d[1][i];

A2=letra_d[2][i];

A3=letra_d[3][i];

A4=letra_d[4][i];

contador(i);

Delay_ms(2);

}

}

}

}

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Puertos E/S de la Familia DSPIC33E/PIC24E

UNEXPO-Pto.Ordaz Prof. Rafael Surga MICROPROCESADORES

Вам также может понравиться

- SasasaДокумент5 страницSasasaMarcos TiconaОценок пока нет

- Cartas de Presentacion y Postulacion (Editables)Документ2 страницыCartas de Presentacion y Postulacion (Editables)Marcos TiconaОценок пока нет

- Fundamentos de La Tecnica de AutomatizacionДокумент106 страницFundamentos de La Tecnica de AutomatizacionFREDY ROBINSON GIL ZEA0% (1)

- Carta ExplicativaДокумент1 страницаCarta ExplicativaMarcos TiconaОценок пока нет

- Contextualización Del ProblemaДокумент5 страницContextualización Del ProblemaMarcos TiconaОценок пока нет

- Teoria Control PDFДокумент213 страницTeoria Control PDFAngel CastilloОценок пока нет

- Contextualización Del ProblemaДокумент5 страницContextualización Del ProblemaMarcos TiconaОценок пока нет

- Trabajo de DiliaДокумент10 страницTrabajo de DiliaMarcos TiconaОценок пока нет

- Conceptos RuidoДокумент28 страницConceptos RuidoSergio TarcayaОценок пока нет

- Conceptos RuidoДокумент1 страницаConceptos RuidoMarcos TiconaОценок пока нет

- Sistemas EstablesДокумент6 страницSistemas Establesmamd1993Оценок пока нет

- Sistemas EstablesДокумент6 страницSistemas Establesmamd1993Оценок пока нет

- 2 Diodos PDFДокумент50 страниц2 Diodos PDFJorge Luis Ramos CuipaОценок пока нет

- PROCEDIMIENTOДокумент2 страницыPROCEDIMIENTOMarcos TiconaОценок пока нет

- República Bolivariana de VenezuelaДокумент10 страницRepública Bolivariana de VenezuelaMarcos TiconaОценок пока нет

- Capitulo 2 LdetxДокумент23 страницыCapitulo 2 LdetxFernando Alberto Salgado AmadoОценок пока нет

- Prueba EscritaДокумент17 страницPrueba EscritaMarcos TiconaОценок пока нет

- Guia 2 Electiva IVДокумент3 страницыGuia 2 Electiva IVMarcos TiconaОценок пока нет

- República Bolivariana de VenezuelaДокумент19 страницRepública Bolivariana de VenezuelaMarcos TiconaОценок пока нет

- República Bolivariana de VenezuelaДокумент10 страницRepública Bolivariana de VenezuelaMarcos TiconaОценок пока нет

- República Bolivariana de VenezuelaДокумент10 страницRepública Bolivariana de VenezuelaMarcos TiconaОценок пока нет

- Carta de Smith EjerciciosДокумент28 страницCarta de Smith EjerciciosFidel Andres Vargas CallejasОценок пока нет

- PLC Primer Guia 1er CorteДокумент18 страницPLC Primer Guia 1er CorteMarcos TiconaОценок пока нет

- República Bolivariana de VenezuelaДокумент10 страницRepública Bolivariana de VenezuelaMarcos TiconaОценок пока нет

- GuÃ-a # 3 Microondas PDFДокумент108 страницGuÃ-a # 3 Microondas PDFMarcos TiconaОценок пока нет

- InformeДокумент7 страницInformeMarcos TiconaОценок пока нет

- Guã-A #2. Introducciã"n A La MicroondasДокумент18 страницGuã-A #2. Introducciã"n A La MicroondasMarcos TiconaОценок пока нет

- Diseño de Un Enlace Con AntenasДокумент32 страницыDiseño de Un Enlace Con AntenasMarcos TiconaОценок пока нет

- Clase 05 - InterrupcionesДокумент49 страницClase 05 - InterrupcionesMarcos TiconaОценок пока нет

- Temporizadores DspicДокумент41 страницаTemporizadores DspicGerardo Antonio TrejoОценок пока нет

- Requisitos para La Instalación de Los S.O. de WindowsДокумент11 страницRequisitos para La Instalación de Los S.O. de Windowsanon_655498895Оценок пока нет

- Perturbaciones de La TransmisionДокумент33 страницыPerturbaciones de La TransmisionDARWIN RODOLFO DAVILA FERNANDEZОценок пока нет

- Práctica 5. ZenerДокумент9 страницPráctica 5. ZenerOliver TorresОценок пока нет

- Hardwarre y TiposДокумент13 страницHardwarre y TiposĚrick Päpeletas MartinezОценок пока нет

- DEFINICIÓN DE CPU Y ELEMENTOS Tema 2Документ7 страницDEFINICIÓN DE CPU Y ELEMENTOS Tema 2Erick EspinaОценок пока нет

- Memoria Virtual, Mmu, PaginacionДокумент30 страницMemoria Virtual, Mmu, PaginacionMoises Trigueros100% (1)

- 2020-01 Rocket S-1412HDДокумент4 страницы2020-01 Rocket S-1412HDsuperpuestoОценок пока нет

- Verificación de Componentes ElectrónicosДокумент24 страницыVerificación de Componentes ElectrónicosRafael AngelОценок пока нет

- Practica3 2011Документ4 страницыPractica3 2011Jorge SabioОценок пока нет

- Factura Merca 11-10Документ5 страницFactura Merca 11-10Luifer DevozОценок пока нет

- Laboratorio Polarización de Transistores BJTДокумент13 страницLaboratorio Polarización de Transistores BJTEdrich PachecoОценок пока нет

- Diferencia Entre AM Y FM y Modelo Osi CapasДокумент6 страницDiferencia Entre AM Y FM y Modelo Osi CapasAmaury Castillo GonzalezОценок пока нет

- Nº P001-454HM PDFДокумент1 страницаNº P001-454HM PDFFellman MéndezОценок пока нет

- Fundamentos de Electronica PDFДокумент22 страницыFundamentos de Electronica PDFalitasinfanteОценок пока нет

- Electronic A Cap 11 Al 20Документ108 страницElectronic A Cap 11 Al 20William Rico CobaОценок пока нет

- Rectificadores ControladosДокумент9 страницRectificadores Controladosk hernandezОценок пока нет

- ELECTRONICA 1 Labo 6 Alba Uriona MijaelДокумент5 страницELECTRONICA 1 Labo 6 Alba Uriona Mijaelvladimir quispe condoriОценок пока нет

- 900MHz Frente A 2.4GHz en Enlaces de Larga Distancia PDFДокумент3 страницы900MHz Frente A 2.4GHz en Enlaces de Larga Distancia PDFe09081110Оценок пока нет

- 4 Medidas Antenas PDFДокумент64 страницы4 Medidas Antenas PDFAntero CasaniОценок пока нет

- Laboratorio Par DiferencialДокумент4 страницыLaboratorio Par DiferencialChristian Alejandro Pineda TorresОценок пока нет

- UD 3 Act. 3.2 ISFV Red InversoresДокумент27 страницUD 3 Act. 3.2 ISFV Red InversoresViktor StarkОценок пока нет

- Notebook Inspiron 14 3000 Core I3-5005u 4GB 500GB 14Документ2 страницыNotebook Inspiron 14 3000 Core I3-5005u 4GB 500GB 14Nico InfanteОценок пока нет

- Comunitarios Tramite 48Документ52 страницыComunitarios Tramite 48Javier Osorio100% (1)

- Informe Tacómetro FinalДокумент12 страницInforme Tacómetro FinalJosé Rafael VegasОценок пока нет

- Ondas de Radio y TelevisiónДокумент11 страницOndas de Radio y TelevisiónLeobacardiОценок пока нет

- Alarm AДокумент3 страницыAlarm AAlex SaarОценок пока нет

- Calculo de Transformador Proyecto de Maquinas 1Документ6 страницCalculo de Transformador Proyecto de Maquinas 1RamiroОценок пока нет

- Receptor FM MiniaturaДокумент5 страницReceptor FM MiniaturaAlexander Peña Alvarado0% (1)

- Lab06 - Control de Fase de Triac Culminado DiegoДокумент19 страницLab06 - Control de Fase de Triac Culminado Diegoanon_843632677Оценок пока нет

- Guia Cyclone IIДокумент28 страницGuia Cyclone IIPedro LandaetaОценок пока нет