Академический Документы

Профессиональный Документы

Культура Документы

E719020250 12F2 PDF

Загружено:

laoraculo0 оценок0% нашли этот документ полезным (0 голосов)

12 просмотров2 страницыОригинальное название

E719020250-12F2.pdf

Авторское право

© © All Rights Reserved

Доступные форматы

PDF или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

12 просмотров2 страницыE719020250 12F2 PDF

Загружено:

laoraculoАвторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF или читайте онлайн в Scribd

Вы находитесь на странице: 1из 2

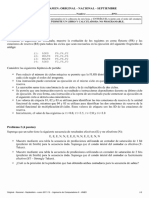

TIPO DE EXAMEN: 2" SEMANA - NACIONAL Y UNION EUROPEA - FEBRERO

Apellido:

fombre

DN

INSTRUCCIONES: Complete sus datos personales en la cabecera de esta hoja, y ENTREGUELA junto con el resto del examen,

Lea atentamente todos los enunciados.

Problema 1 (2 puntos)

Un procesador sin segmentacién necesita 150 nseg. para procesar una instruccién. Con respecto a este

procesador, calcule la aceleracién que se obtiene en los dos siguientes casos:

) Un procesador A dotado de una segmentacién de 7 etapas, consumiendo cada ctapa el mismo tiempo.

Cada etapa ocasiona una sobrecarga de 6 nseg., no existiendo ningim tipo de detencién en la

segmentacién,

b) Un procesador B con una segmentacién de 7 etapas, consumiendo cada una de ellas 30 nseg., 30

nseg., 40 nseg., 50 nseg. y 50 nseg, respectivamente, y siendo la sobrecarga por cada etapa de 6 nseg. Un

33% de todas las instrucciones de la scgmentacién son detenidas durante un ciclo de reloj y un 8%

durante dos ciclos.

Problema 2 (3 puntos)

En un procesador veetorial con las siguientes earacteristicas

- _ Registros con una longitud vectorial maxima de 64 elementos.

~ Una unidad de suma vectorial con tiempo de arranque de 6 ciclos.

= Una unidad de multiplicacién con tiempo de arranque de 7 ciclos.

~ Una unidad de carga/almacenamiento con tiempo de arranque de 12 ciclos.

- La frecuencia de trabajo del procesador es 500 MHz,

- Thase de 10 ciclos y Thuele de 15 cielos.

icsnj i++)

x*A(i) + y*A(i);

Escriba el cédigo vectorial que realizaria las operaciones ubicadas en el interior del bucle y caleule 7, Toe,

Roo» yR,, en los siguientes casos:

a) Sin considerar encadenamiento de resultados.

b) Permitiendo encadenamientos.

©) Considerando encadenamientos y dos unidades de multiplicacién,

2 semana ~ Nacional yUnién Europea - Febrero - curso 2011/12 — Ingenieria de Computadores II - UNED ve

Problema 3 (3 puntos)

ispone de un sistema biprocesador (CPUs A y B) de memoria compartida que utiliza un protocolo snoopy

de coherencia de caché. Sabiendo que la CPU B tiene cargada en caché la variable X y que la CPU A realiza

una Iectura sobre la variable X (cead (x) ), seguida de una escritura sobre la misma variable (azite (x)). Se

pide que:

4) Describa la secuencia de acciones de coherencia y lus etiquetas de las cachés de cada procesador para

la variable X durante las instrucciones ejecutadas,

b) {Qué problemas pueden ocurrir en caso de necesitar que las operaciones realizadas por la CPU A se

realicen de manera atémica, es decir, que su resultado sea independiente de las posibles acciones

realizadas por la CPU B mientras la CPU A esta ejecutando sus acciones?

©) Describa la secuencia de acciones de coherencia y las etiquetas de las eachés de cada procesador para

la variable X en cada uno de los posibles problemas.

2 semana ~ Nacional yUnién Europea - Febrero - curso 2011/12 — Ingenieria de Computadores II - UNED 22

Вам также может понравиться

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Criptografia Seguridad ComputadoresДокумент307 страницCriptografia Seguridad Computadoresdanielfiguero5293Оценок пока нет

- Objective Proficiency2 Teachers Book Photocopiable Recording Scripts PDFДокумент13 страницObjective Proficiency2 Teachers Book Photocopiable Recording Scripts PDFEnrico FerrariОценок пока нет

- PED-1718 Ver 2Документ4 страницыPED-1718 Ver 2laoraculoОценок пока нет

- E710131300 17F1Документ2 страницыE710131300 17F1laoraculoОценок пока нет

- E719020250 16soДокумент2 страницыE719020250 16solaoraculoОценок пока нет

- Guia Teoria de La Informacion y Criptografia Basica UnedДокумент8 страницGuia Teoria de La Informacion y Criptografia Basica UnedlaoraculoОценок пока нет

- AritmeticaModular PDFДокумент39 страницAritmeticaModular PDFlaoraculo100% (1)

- E719020250 16SRДокумент2 страницыE719020250 16SRlaoraculoОценок пока нет

- E719020250 12so PDFДокумент2 страницыE719020250 12so PDFlaoraculoОценок пока нет

- Non-Linear 2D Transformations: Deconstructing PathsДокумент12 страницNon-Linear 2D Transformations: Deconstructing PathslaoraculoОценок пока нет

- E719020250 12SR PDFДокумент1 страницаE719020250 12SR PDFlaoraculoОценок пока нет

- E719020250 12F1 PDFДокумент2 страницыE719020250 12F1 PDFlaoraculoОценок пока нет

- InterludeДокумент2 страницыInterludelaoraculoОценок пока нет

- Drawing Polygons: Loops and Arrays: 5.1. The Repeat LoopДокумент8 страницDrawing Polygons: Loops and Arrays: 5.1. The Repeat LooplaoraculoОценок пока нет

- A 7Документ8 страницA 7laoraculoОценок пока нет

- TableДокумент4 страницыTablelaoraculoОценок пока нет

- Drawing Curves Automatically: Procedures As Arguments: Curveto Lineto Stroke Fill ClipДокумент9 страницDrawing Curves Automatically: Procedures As Arguments: Curveto Lineto Stroke Fill CliplaoraculoОценок пока нет

- CH 2Документ14 страницCH 2laoraculoОценок пока нет

- ZoomingДокумент3 страницыZoominglaoraculoОценок пока нет

- Getting Started in Postscript: in This Book We Shall Use A Program CalledДокумент17 страницGetting Started in Postscript: in This Book We Shall Use A Program CalledlaoraculoОценок пока нет

- CH 3Документ9 страницCH 3laoraculoОценок пока нет

- A 4Документ3 страницыA 4laoraculoОценок пока нет

- Evaluating Polynomials: Getting Along Without Variables: 1. The Most Straightforward Way To Do ItДокумент5 страницEvaluating Polynomials: Getting Along Without Variables: 1. The Most Straightforward Way To Do ItlaoraculoОценок пока нет

- Setting Up Your Postscript EnvironmentДокумент4 страницыSetting Up Your Postscript EnvironmentlaoraculoОценок пока нет

- Summary of Postscript Commands: 1. Mathematical FunctionsДокумент9 страницSummary of Postscript Commands: 1. Mathematical FunctionslaoraculoОценок пока нет

- A 3Документ2 страницыA 3laoraculoОценок пока нет