Академический Документы

Профессиональный Документы

Культура Документы

Quiz 1

Загружено:

Marquee Gerbuyos0 оценок0% нашли этот документ полезным (0 голосов)

57 просмотров10 страницquiz1

Оригинальное название

quiz 1

Авторское право

© © All Rights Reserved

Доступные форматы

DOCX, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документquiz1

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате DOCX, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

57 просмотров10 страницQuiz 1

Загружено:

Marquee Gerbuyosquiz1

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате DOCX, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 10

1) It is a thin sliced of semiconductor material, such as a crystalline

Wafer (Slice Or Substrate)

silicon, used in electronics for the fabrication of integrated circuits

2) He discovered the vacuum tubes in 1904 John Ambrose Fleming

3) Is a device that controls electric current between electrodes in an

Vacuum Tubes

evacuated container

Electronic Numeric

4) Worlds first electronic computer, and was first demonstrated at

Integrator And Calculator

the Moore School of Engineering in Pennsylvania in 1947

(ENIAC)

5) He discovered the p-n junction, in the year 1940, which is the

Russel Ohl

foundation in making the transistor

6) Date when Russel Ohl tested a small silicon slab that yielded a

February 23, 1940

surpring result

7) In the year 1947, they applied two closely-spaced gold contacts

held in space by a plastic wedge to the surface of a small stab of Bardeen and Brattain

high-purity germanium

8) The year Jack Kilby discovered the integrated circuit 1958

9) The date when Noyce filed his Semiconductor Device and Lead

July 1959

Structure patent

10) Year when silicon wafers were being manufactured in the U.S by

1960

companies such SunEdison

11) In 1965, they filed Patent US3423629A for the first high-capacity Eric O. Ernst, Donald J.

epitaxial apparatus Hurd, Gerard Seeley

12) Year when microprocessor integrates CPU function onto a single

1971

chip

Polycrystalline or

13) The crystal structure of a silicon

Polysilicon

14) Defined as gritty particles of worn or disintegrated rock with

grains varying in size from tenths of a millimeter to several Sand

millimeter

15) One of the most common elements on earth and is a gray, brittle,

Silicon

tetravalent chemical element

16) Is the raw material for silicon production Quartz (Silica)

17) A substance that is the end result when heating a mixture of silica Metallurgical-Grade Silicon

and carbon in an electric arc furnace to a temperature Production

18) Liquid compound of silicon Trichlorosilane

Electronic-Grade Silicon

19) Is the end result for a trichlorosilane mixed with other gaseous

(Semiconductor-Grade

chlorine compounds undergoes multiple distillation

Silicon)

20) Is the raw material for silicon single crystals which are grown by

Electronic-Grade Polysilicon

using different processes

21) The crystals that are grown from chunks of the intrinsic material,

Ingots

which have a polycrystalline structure and are undoped

22) The process of converting the polycrystalline chunks to a large

crystal of single-crystal structure, with the proper orientation and Crystal Growing

correct amount of N- or P-type

23) The crystallization velocity of metals by pulling mono- and and

polycrystals against gravity out of a melt which is held in a

crucible and was named after Jan Czochralski Czochralski Method

24) More than 75% of all single crystalline wafers are grown by this

method

Furnace

Crystal-Pulling

25) Three main components of a puller:

Mechanism

Ambient Control

26) It includes a fused-silica crucible, a graphite susceptor, a rotaion

Furnace

mechanism, a heating element, and a power supply

27) It includes a seed holder and a rotation mechanism Crystal-Pulling Mechanism

28) It includes a gas source, a flow control and an exhaust Ambient Control

29) It is selected to create either an N-type or P-type crystal Dopant

30) Surface of the liquid material Melt

31) Temperature and pulling speed are adjusted to neck the crystal

Necking

diameter down to several millimeters

32) Was developed at Bell Labs by Henry Theuerer in 1955 as a

modification of the method zone melting which was developed by

William Gardner Pfann Float-Zone Method

33) Is the go-to technique whenever a wafer requires high-purity

silicon with little impurities

34) The directional solidification by translating a melt from the hot

Bridgman Technique

zone to the cold zone of the furnace

Vertical Bridgman

35) It enables the growth of crystals in circular shape

Technique

Horizontal Bridgman

36) It grows D-shaped ingots

Technique

37) One of the earliest melt techniques used to grow large quantity of

crystals with high melting temperature

Verneull Method

38) It was first introduced by the French Auguste Verneull and

originally developed for producing synthetic gemstones

39) Was initially developed for growth of large alkali halide crystals by

Kyropoulos Method

the German scientist Spyro Kyropoulos

40) Structure arranged spatially in a regular and repetitive manner

giving a completely ordered structure and considered as the most Crystalline Material

stable form of solids

41) The simplest repeating unit in a crystal and is defined in terms of

Unit Cell

lattice points

42) The points in space about which the particles are free to vibrate in

Lattice Points

a crystal

43) Consisting of many crystalline parts that are randomly oriented

Poly Crystalline

with respect to each other

44) Crystal lattice of the entire sample is continuous and unbroken to

Mono Crystalline

the edges of the sample, with no grain boundaries

45) One or two flats ground into the edge of the wafer indicate

crystal orientation, and generally applies to wafers 125mm in Wafer Flats

diameter or smaller

46) The introduction of impurities into the intrinsic semiconductor

crystal to deliberately change its conductivity due to deficiency or Doping

excess of electrons

47) Are atoms of a different element than the atoms of the intrinsic

Impurity Atoms

semiconductor

Intrinsic Semiconductor

48) Two types of semiconductor material:

Extrinsic Semiconductor

49) Semiconductor in its pure form Intrinsic Semiconductor

50) Semiconductor that has been subjected to doping process Extrinsic Semiconductor

N-type

51) Two kinds of doped semiconductor:

P-type

52) Created by introducing impurity elements that has five valence of

N-type

electron such as antimony, arsenic and phosphorus

53) Diffused impurities with five valence of electrons Donor Atoms

54) Formed by doping a pure silicon crystal with impurity atoms

having three valence of electrons such as boron, gallium and P-type

indium

55) Diffused impurities with three valence of electrons Acceptor Atoms

56) Semiconductor produced via the Czochralski process and is also a

Gallium Arsenide

common wafer material

57) Imperfection in the regular geometrical arrangement of the

Crystal Defects

atoms in a crystalline solid

Point Defects

Line Defects

58) Defects in crystal:

Area Defects

Volume Defects

End Cropping

Diameter Grinding

Crystal Orientation,

Conductivity and

59) Wafer Preparation:

Resistivity Check

Grinding

Orientation

Indicators

60) Cropping off of the crystal ends with a saw End Cropping

61) Is a mechanical operation performed in a centerless grinder Diameter Grinding

62) Is determined by either X-ray diffraction or collimated light

Crystal Orientation

refraction

63) An important electrical check to ensure that the right dopant type

Conductivity Type (N or P)

was used

64) Is used to determine the amount of dopant put into the crystal

Resistivity Measurement

using a four-point probe

65) A flat is ground along the axis once the crystal is oriented on the

Major Flat

cutting block and will show up on each of the wafers

Inside Diameter

66) Wafer slicing: Diamond Saw

Wire Saw

67) Are used to ensure flat surfaces with little tapering and with a

Wire Saw

minimal amount if kerf loss

68) Its primary purpose is to remove the surface damage left over

Rough Polish

from the wafer-slicing process

69) The final polishing step is a combination of chemical etching and Chemical Mechanical

mechanical buffing Polishing (CMP)

70) The backs may receive a special process to induce crystal damage

and causes the growth of dislocations that radiate up into the Backside Damage

water

71) The trapping phenomenon and is a process by which unwanted

Gettering

impurities are removed by providing an alternative location

72) Is a mechanical process that leaves the wafer with a round edge Edge Grinding

73) Is employed to further create an edge that minimizes edge

Chemical Polishing

chipping and damage during fabrication

74) Is a process which converts silicon on the wafer into silicon

Oxidation

dioxide

Materials

Preparation

Crystal Growth or

Wafer Preparation

75) Stages of microchip manufacturing:

Wafer Fabrication

and Electrical Sort

Packaging or Final

Test

76) Is the manufacturing process used to create semiconductor

Wafer Fabrication

devices and circuits in and on a wafer surface

Layering

Patterning

77) Basic wafer fabrication process:

Doping

Heat Treatments

78) Is the operation used to add thin layers to the wafer surface Layering

79) Is the series of steps that results in the removal of selected

Patterning

portions of the added surface layers

80) Is the process that puts specific amounts of electrically active

dopants in the wafer surface through openings in the surface Doping

layers

81) Are the operations in which the wafer is simply heated and cooled

Heat Treatments

to achieve specific results

82) Is a chemical process used to produce high quality, high- Chemical Vapor Deposition

performance, solid materials (CVD)

83) Is a process used in microfabrication to transfer geometric

Photolithography

patterns to a film or substrate

84) Came from the Greek words lithos and graphia which directly

Lithography

translated would be writing on stones

85) Is transferring a pattern onto another surface

86) Is used in the manufacture of semiconductor components to

chemically remove layers from the surface of a wafer during Etching

manufacturing

87) Is the final stage in the semiconductor device fabrication process Packaging

Chip

Scribe Lines

TEG (Test Element

88) Wafer parts: Group)

Edge Die

Flat Zone

Major Flat/Notches

89) A tiny piece of silicon with electronic circuit patterns Chip

90) Thin, non-functional spaces between the functional pieces, where

Scribe Lines

a saw can safely cut the wafer without damaging the circuits

91) A prototype pattern that reveals the actual physical

characteristics of a chip so that it can be tested to see whether it Test Element Group (TEG)

works properly

92) Dies around the edge of a wafer considered production loss Edge Die

93) One edge of a wafer that is cut off flat to help identify the wafers

Flat Zone

orientation and type

94) Indicates the doping material and the orientation of the wafer Major Flat/Notches

95) The flat of longest length located in the circumference of the

Primary Flat

wafer

96) Indicates the crystal orientation and doping of the wafer Secondary Flat

97) No secondary flat P type <111>

98) 905 clockwise from primary flat P type <100>

99) 455 clockwise from primary flat N type <111>

100) 1805 clockwise from primary flat N type <100>

101) Are defined by the diameter of wafers that they are tooled to Semiconductor Fabrication

produce Plants (Fabs)

102) 2 wafer 1969

103) 3 wafer 1972

104) 4 wafer 1976

105) 6 wafer 1983

106) 8 wafer 1992

107) Is determined by the mechanical strength of the material used Wafer Thickness

IBM

Intel

108) The semiconductor manufacturers that teamed to manufacture

Samsung

the 450 mm wafer size production

TMSC

Global Foundries

109) Is used to estimate the count of dies in a single wafer Die Per Wafer (DPW)

110) International Technology Roadmap for Semiconductors ITRS

1) Process used to create the integrated circuits that are present in Semiconductor Devices

everyday electrical and electronic devices Fabrication

2) Was an American semiconductor company based in San Jose,

Fairchild Semiconductor

California and was founded in 1947, it became a pioneer in the

International Inc.

manufacturing of transistors and of integrated circuits

3) Small Scale Integration (SSI) 1964

4) Medium Scale Integration (MSI) 1968

5) Large Scale Integration (LSI) 1971

6) Very Large Scale Integration (VLSI) 1980

7) Ultra Large Scale Integration (ULSI) 1984

TECHNOLOGICAL MILESTON IN SEMICONDUCTOR INDUSTRY

NAME YEAR Transistors Logic gates

SSI 1964 1-10 1-12

MSI 1968 10-500 13-99

LSI 1971 500-20k 100-9,999

VLSI 1980 20k-1M 10k-99,999

ULSI 1984 >1M >100k

8) Is a designation in microprocessor designs where integrated

Giga Scale Integration (GSI)

circuits contain more than 1 billion transistor gates

9) Refers to a specific semiconductor manufacturing process and its

Technology Node

design rules

10) IBM produced a 6 nm transistor 2002

11) NEC produced a 5 nm transistor 2003

12) KAIST and National Nano Fab Center codeveloped a 3 nm

2006

transistor called FinFET

13) An Australian team fabricated a single transistor out of 7 atom

2010

that measured 4 nm in length

14) Scientists in Chungbuk National University in South Korea created

2012

2 nm transistor

15) IMEC and Cadence fabricated 5nm test chips 2015

Incoming Wafer

Deposition

Lithography

16) Semiconductor fabrication process: Etch

Strip

Clean

Deposition

Deposition

Removal

17) Four general categories of various processing steps in

Patterning

semiconductor device fabrication:

Modification of

Electrical Properties

18) Any process that grows, coats, or otherwise transfers a material

Deposition

onto the wafer

19) Is any process that removes material from the wafer Removal

20) Is the shaping or altering of deposited materials and is generally

Patterning

referred to as lithography

21) A chemical that coats the wafer in conventional lithography Photoresist

22) Focuses, aligns, and moves a mask, exposing select portions of

Stepper

the wafer below to short wavelength light

23) Wash away exposed region Developer Solution

Modification of Electrical

24) Has historically entailed doping transistor sources and drains

Properties

25) Serves to activate the implanted dopants Annealing

26) It is the process of fabricating miniature structures of micrometer Semiconductor Fabrication

scales and smaller (Microfabrication)

Semiconductor

24)27) Earliest microfabrication processes were used for integrated Manufacturing

circuit fabrication, also known as (Semiconductor Device

Fabrication)

28) Is a miniature machine that has both mechanical and electronic Microelectromechanical

components Systems

25)29) MEMs is commonly known as ____ in Japan Micromachines

26)30) In European countries, MEMs are more commonly referred to

Microsystems Technology

as

Deposition

Processes

31) Basic processes of MEMs: Patterning

Etching

Die Preparation

Bulk

Micromachining

Surface

32) MEMs manufacturing technologies:

Micromachining

High Aspect Ratio

Silicon Machining

33) Is the oldest paradigm of silicon based MEMs; Whole thickness of

a silicon wafer is used for building the micro-mechanical Bulk Micromachining

structures.

27)34) The most common etch in silicon Anisotropic Wet Etch

35) Builds microstructures by deposition and etching of different

Surface Micromachining

structural layers on top of the substrate

36) Is simply the multitude of layers of different materials have to be

Deposition

deposited during the IC fabrication process

Physical Vapor

Deposition (PVD)

37) Two most important deposition methods:

Chemical Vapor

Deposition (CVD)

38) Layer of material ranging from fractions of a nanometer to several

Thin Films

micrometers in layers

Evaporative

39) Classification of thin film deposition technologies:

Technologies

Glow-discharge

Technologies

Gas-phase Chemical

Processes

Liquid-phase

Chemical Formation

40) The source material is evaporated in a vacuum Evaporative Technologies

41) The electrode and gas-phase phenomena in various kinds of glow

Glow-discharge

discharges represents a rich source of processes used to deposit

Technologies

and etch thin films

42) Methods of film formation by purely chemical processes in the

Gas-phase Chemical

gas or vapor phases include chemical vapor deposition and

Processes

thermal oxidation

43) The growth of inorganic thin films from liquid phases by chemical

Liquid-phase Chemical

reactions is accomplished primarily by electrochemical processes

Formation

and by chemical deposition processes

Physical Vapor

44) Depositions that happen because of a physical reaction: Deposition

Casting

Chemical Vapor

Deposition

45) Depositions that happen because of a chemical reaction: Electrodeposition

Epitaxy

Thermal Oxidation

46) Process when oxygen combines with an element or substance,

Oxidation

changing the appearance of the element

47) Procedure used to deposit uniform thin films to flat substrates Spin Coating

48) A machine used for spin coating Spin Coater (Spinner)

49) Surface covering in which a metal is deposited on a conductive

Plating

surface

Physical Vapor Deposition

50) Deposition of a in the vapor phase onto a solid vacuum

(PVD)

Sputter Deposition

Evaporative

Deposition

Electron Beam

Deposition

Cathodic Arc

51) Physical vapor deposition techniques:

Deposition

Pulsed Laser

Deposition

Electrohydrodynam

ic Deposition

Plasma Spray PVD

52) Is the process whereby atoms are ejected from a target or source

Sputtering

material that is to be deposited on a substrate

53) Came from the Latin word Sputare meaning to emit saliva with

To Sputter

noise

54) He developed the first sputter gun in 1970 Peter J. Clarke

A local plasma

55) The source of ions might either be: Separate ion beam

source

56) If a high negative potential difference is applied between the

Diode Sputtering

target and the substrate in a rarefied argon environment

57) Uses magnets behind the negative cathode to trap electrons over

the negatively charged target material so they are not free to Magnetron Sputtering

bombard the substrate, allowing for faster deposition rates

58) Ions are extracted from a separate ion source to which the argon

Ion Beam Deposition

is fed directly

59) Is a common method of thin-film deposition Evaporative Deposition

60) Protruding features block the evaporated material from some

areas because the evaporated material attacks the substrate Shadowing (Step Coverage)

mostly from a single direction

61) Is a form of physical vapor deposition in which a target anode is

Electron Beam Physical

bombarded with an electron beam given off by a charged

Vapor Deposition (EBPVD)

tungsten filament under high vacuum

62) Is a physical vapor deposition technique in which an electric arc is

Cathodic Arc Deposition

used to vaporize material from cathode target

63) Begins with the striking of a high current, low voltage arc on the

surface of a cathode that gives rise to a small, highly energetic Arc Evaporation Process

emitting area known as a cathode spot

64) Is a physical vapor deposition technique where a high-power

pulsed laser beam is focused inside a vacuum chamber to strike a Pulsed Laser Deposition

target of the material that is to be deposited

Electrohydrodynamic

65) New process of thin film deposition

Deposition

66) Is a low pressure plasma spray technology recently developed by

Plasma Spray PVD

Sulzer Metco AG (Switzerland)

67) Is a chemical process used to produce high quality, high-

Chemical Vapor Deposition

performance, solid materials

Gas Delivery

System

Reactor Chamber

Substrate Loading

Mechanism

Energy Source

68) A CVD apparatus will consist of several basic components:

Vacuum System

Exhaust System

Exhaust Treatment

System

Process Control

Equipment

69) For the supply of precursors to the reactor chamber Gas Delivery System

70) Chamber within which deposition takes place Reactor Chamber

Substrate Loading

71) A system for introducing and removing substrates

Mechanism

72) Provide the energy/heat that is required to get the precursors to

Energy Source

react/decompose

73) A system for removal of all other gaseous species other that those

Vacuum System

required for the reaction/deposition

74) A system for removal of volatile by-products form the reaction

Exhaust System

chamber

75) In some instances, exhaust gases may not be suitable for release

into the atmosphere and may require treatment or conversion to Exhaust Treatment System

safe/harmless compounds

76) Gauges, control etc., to monitor process parameters such as

Process Control Equipment

pressure, temperature and time

Resistive Heating

Radiant Heating

77) Several suitable sources of heat for CVD processes: Radio Frequency

Heating

Lasers

78) Is a compound that participates in a chemical reaction that

Precursors

produces another compound

Вам также может понравиться

- The Use of Electrochemical Scanning Tunnelling Microscopy (EC-STM) in Corrosion Analysis: Reference Material and Procedural GuidelinesОт EverandThe Use of Electrochemical Scanning Tunnelling Microscopy (EC-STM) in Corrosion Analysis: Reference Material and Procedural GuidelinesОценок пока нет

- All Lect MergedДокумент685 страницAll Lect MergedRanjit YewaleОценок пока нет

- Review Article Tracing The Recorded History of ThiДокумент61 страницаReview Article Tracing The Recorded History of ThiPreparaduriasFisicaMatematicaОценок пока нет

- Logging History Rich With Innovation: Subsurface Data IntegrationДокумент4 страницыLogging History Rich With Innovation: Subsurface Data IntegrationAsahel NuñezОценок пока нет

- Nanotechnology: Carbon Nanotube (CNT)Документ42 страницыNanotechnology: Carbon Nanotube (CNT)محمد رمضان رجبОценок пока нет

- Transistor CharacteristicsДокумент41 страницаTransistor Characteristicsمحمد فاضل الكعبيОценок пока нет

- Lecture1-Introduction To Electronics (20!3!11)Документ7 страницLecture1-Introduction To Electronics (20!3!11)kspark595Оценок пока нет

- J 1151-2916 2000 tb01182 XДокумент21 страницаJ 1151-2916 2000 tb01182 Xrahil7860Оценок пока нет

- Pengenalan Teknologi Rangkaian Terintegrasi: Eka Maulana, ST, MT, Meng. Adharul Muttaqin, S.T., M.TДокумент35 страницPengenalan Teknologi Rangkaian Terintegrasi: Eka Maulana, ST, MT, Meng. Adharul Muttaqin, S.T., M.TMuhammad FauzanОценок пока нет

- Timeline Integrated CircuitДокумент24 страницыTimeline Integrated CircuitJayson Alva100% (1)

- 1 - Discovering The NanoscaleДокумент60 страниц1 - Discovering The NanoscalevelavansuОценок пока нет

- Nanotechnology: Yung Liou P601 Yung@phys - Sinica.edu - TW Institute of Physics Academia SinicaДокумент58 страницNanotechnology: Yung Liou P601 Yung@phys - Sinica.edu - TW Institute of Physics Academia SinicaPragyaОценок пока нет

- NanomaterialДокумент9 страницNanomaterialTahira BatoolОценок пока нет

- Chapter 4fabricationofICДокумент20 страницChapter 4fabricationofICManikandan RadhakrishnanОценок пока нет

- History of Ceramic MaterialsДокумент7 страницHistory of Ceramic MaterialsRaza AliОценок пока нет

- Unit 5 NanotechnolgyДокумент12 страницUnit 5 NanotechnolgySyeda SafiyaОценок пока нет

- IC FabricationДокумент78 страницIC FabricationSayandip KarОценок пока нет

- 9 PDFДокумент33 страницы9 PDFTejinder SinghОценок пока нет

- Semiconductor Fabrication Lecture NotesДокумент11 страницSemiconductor Fabrication Lecture NotesJoanna Fabricante100% (1)

- Tohoku University: Riichiro SaitoДокумент81 страницаTohoku University: Riichiro SaitoJeon JungkookОценок пока нет

- CH 01Документ72 страницыCH 01Shashi ShekharОценок пока нет

- Assignment: Department of Physics Bahauddin Zakariya University, MultanДокумент14 страницAssignment: Department of Physics Bahauddin Zakariya University, MultansaqibusmanОценок пока нет

- Mod1VLSI TECHNOLOGY1Документ65 страницMod1VLSI TECHNOLOGY1Jomon VargheseОценок пока нет

- (Chem 192) History of NanotechnologyДокумент1 страница(Chem 192) History of NanotechnologyCarl Jerome CentenoОценок пока нет

- Synthesis, Characterization and Applications of Carbon Nanotubes A ReviewДокумент6 страницSynthesis, Characterization and Applications of Carbon Nanotubes A ReviewEditor IJTSRDОценок пока нет

- Chapter 5 Fabrication of Microelectronic DevicesДокумент35 страницChapter 5 Fabrication of Microelectronic Devicesmuhamadsaidi60% (5)

- TransistorДокумент26 страницTransistorSaif HassanОценок пока нет

- What Is Nanotechnology?Документ37 страницWhat Is Nanotechnology?Daniel ARОценок пока нет

- Milestones in ElectronicsДокумент12 страницMilestones in ElectronicsGreg GarciaОценок пока нет

- EvolutionДокумент49 страницEvolutionMohammad RameezОценок пока нет

- The Journey of Silicon From The Big Bang To Adoption in Nanotechnology To Tri-Gate TechnologyДокумент13 страницThe Journey of Silicon From The Big Bang To Adoption in Nanotechnology To Tri-Gate TechnologyAbdulrahman Suleman AhmedОценок пока нет

- L10-Casting Solidification 13 PDFДокумент42 страницыL10-Casting Solidification 13 PDFNarasimha Murthy InampudiОценок пока нет

- History of NanotechnologyДокумент5 страницHistory of NanotechnologyAkama KulasekaraОценок пока нет

- Ch1 IntroductionДокумент96 страницCh1 Introductionwangjay329Оценок пока нет

- History of NanotechnologyДокумент12 страницHistory of NanotechnologyShubhangi RamtekeОценок пока нет

- CM - MEMS - TWO MARKS Five UNITSДокумент7 страницCM - MEMS - TWO MARKS Five UNITSSandhiyaОценок пока нет

- Cnts Synthesis: Department of Chemical Engineering, H.Bt.UДокумент20 страницCnts Synthesis: Department of Chemical Engineering, H.Bt.UPankaj AgrahariОценок пока нет

- Fituyre Full of LightДокумент5 страницFituyre Full of LightStellamaris MutukuОценок пока нет

- Applications of Nanotechnology: A Review: Ankush Singh, Madhura Suki, Ruchira Sharma, Pradnya IngleДокумент17 страницApplications of Nanotechnology: A Review: Ankush Singh, Madhura Suki, Ruchira Sharma, Pradnya IngleKRISHNA SINGHОценок пока нет

- Paper Hoda NiberДокумент5 страницPaper Hoda NiberAzmeer AsryОценок пока нет

- Tilli 2020Документ15 страницTilli 2020Athiyan RОценок пока нет

- Carbon Nanotube: A Review On Introduction, Fabrication Techniques and Optical ApplicationsДокумент7 страницCarbon Nanotube: A Review On Introduction, Fabrication Techniques and Optical ApplicationsTajudin1Оценок пока нет

- Divais MikroelektronikaДокумент6 страницDivais MikroelektronikaFaiza Abu RizalОценок пока нет

- 14 LiangДокумент70 страниц14 LiangJohnathon TaylorОценок пока нет

- E-Review GEAS Module 26Документ2 страницыE-Review GEAS Module 26Leeanne CabalticaОценок пока нет

- Evolution of Transistors Humble Beginnings To The Ubiquitous PresentДокумент9 страницEvolution of Transistors Humble Beginnings To The Ubiquitous PresentAsif MemonОценок пока нет

- History of MEMS - PresentationДокумент27 страницHistory of MEMS - PresentationbetoplapaОценок пока нет

- The Construction of The Great PyramidsДокумент17 страницThe Construction of The Great PyramidsFauzan RasipОценок пока нет

- Nanomateriaux Cours1 2024Документ40 страницNanomateriaux Cours1 2024idriss godaОценок пока нет

- Nanochemistry Imran UG ShortДокумент77 страницNanochemistry Imran UG Shortsharminmin92Оценок пока нет

- IC FabricationДокумент76 страницIC FabricationRoshdy AbdelRassoulОценок пока нет

- Cement IndustryДокумент6 страницCement IndustryRaj GoswamiОценок пока нет

- Integrated Circuit - WikipediaДокумент6 страницIntegrated Circuit - WikipediaFuckОценок пока нет

- Course Content: Introduction To NanoworldДокумент37 страницCourse Content: Introduction To NanoworldAbhijeetОценок пока нет

- Nano MaterialsДокумент121 страницаNano Materialsbb21csb0b07Оценок пока нет

- Sri Pushpam Nano-New, GCM, PPTДокумент48 страницSri Pushpam Nano-New, GCM, PPTMadhan MohanОценок пока нет

- 1.1 Existing Graphene DevicesДокумент39 страниц1.1 Existing Graphene DevicesAhmed UddinОценок пока нет

- History: Assorted Discrete Transistors. Packages in Order From Top To Bottom: TO-3, TO-126, TO-92, SOT-23Документ39 страницHistory: Assorted Discrete Transistors. Packages in Order From Top To Bottom: TO-3, TO-126, TO-92, SOT-23Sv AnandОценок пока нет

- MEC 2205 Lecture 1Документ29 страницMEC 2205 Lecture 1vincentОценок пока нет

- Topic#1 Introduction To Semiconductors IndustryДокумент28 страницTopic#1 Introduction To Semiconductors IndustryRio PerezОценок пока нет

- MANUAL MEDICIÓN RODADO Custom Track Service HandbookДокумент776 страницMANUAL MEDICIÓN RODADO Custom Track Service HandbookAlejandro CortesОценок пока нет

- Datasheet SKHI 22A PDFДокумент12 страницDatasheet SKHI 22A PDFGlauber GoncalvesОценок пока нет

- Air Permeability Test ResultДокумент4 страницыAir Permeability Test Resultritesh0raj-2Оценок пока нет

- Ion Exchangein Hydrometallurgical Processing An Overviewand Selected ApplicationsДокумент22 страницыIon Exchangein Hydrometallurgical Processing An Overviewand Selected ApplicationsShikoyeniОценок пока нет

- 01 - Solinst Water Level 101Документ3 страницы01 - Solinst Water Level 101Dt Paras InvestamaОценок пока нет

- AISC ASTM A325 OR A490 BoltsДокумент7 страницAISC ASTM A325 OR A490 BoltsJonatan López Carriel100% (1)

- Comitrol Processor Model 1700: Controlled Particle Size ReductionДокумент2 страницыComitrol Processor Model 1700: Controlled Particle Size ReductionNguyễn Lê Anh KhoaОценок пока нет

- Y. S. Touloukian, J. Koolhaas Gerritsen, W. H. Shafer - Coatings, Systems, and Composites-Springer US (1973)Документ262 страницыY. S. Touloukian, J. Koolhaas Gerritsen, W. H. Shafer - Coatings, Systems, and Composites-Springer US (1973)slovvlistОценок пока нет

- Potential Measurement To Determine The Chloride Threshold Concentration That Initiates Corrosion of Reinforcing Steel Bar in Slag ConcretesДокумент17 страницPotential Measurement To Determine The Chloride Threshold Concentration That Initiates Corrosion of Reinforcing Steel Bar in Slag ConcretesTarek ChikerОценок пока нет

- Course Specs Mar Power CHEDДокумент13 страницCourse Specs Mar Power CHEDClark LlameraОценок пока нет

- Uses of The Elements and Compounds in Our Daily LifeДокумент4 страницыUses of The Elements and Compounds in Our Daily LifeTaibah Nurwahidah Mohamad89% (9)

- Ssnde14 Final LДокумент72 страницыSsnde14 Final LmiamarchОценок пока нет

- GOST R 52029-2003 Water. Unit of HardnessДокумент4 страницыGOST R 52029-2003 Water. Unit of HardnessOMER EKERОценок пока нет

- Few Aspects in Deep Drawing Process: D Swapna, Ch. Srinivasa Rao, S RadhikaДокумент5 страницFew Aspects in Deep Drawing Process: D Swapna, Ch. Srinivasa Rao, S RadhikaBoby Madesen100% (1)

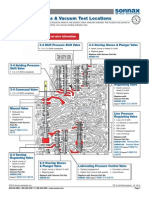

- 722 6 VacTestLocationsДокумент4 страницы722 6 VacTestLocationsUrszula WalczewskaОценок пока нет

- Seger Formula Glaze Calculator - Buscar Con GoogleДокумент1 страницаSeger Formula Glaze Calculator - Buscar Con Googlemartafrias7Оценок пока нет

- Goulds 3316 BulletinДокумент12 страницGoulds 3316 BulletinKEOPSS03Оценок пока нет

- Linbad Duct SupportsДокумент46 страницLinbad Duct SupportsdreamagiczОценок пока нет

- Aerated LagoonДокумент8 страницAerated LagoonAmmu JoeОценок пока нет

- MEISER Grating PDFДокумент122 страницыMEISER Grating PDFabdulloh_99Оценок пока нет

- Two Way Slab Design With VBAДокумент6 страницTwo Way Slab Design With VBAprabin gautamОценок пока нет

- ATA 24 - ElectricalДокумент68 страницATA 24 - ElectricalJose JimenezОценок пока нет

- Dream Residences - Water Supply & Fire Protection BOMДокумент1 страницаDream Residences - Water Supply & Fire Protection BOMPatrick LlenaresОценок пока нет

- PlumДокумент15 страницPlumChristian ConsignaОценок пока нет

- Seco CubeДокумент64 страницыSeco Cubem_mustafa77Оценок пока нет

- Astm D323 - 1999Документ10 страницAstm D323 - 1999Teymur RegenmaisterОценок пока нет

- Waves Group - Marketing Catalouge - 400MEДокумент26 страницWaves Group - Marketing Catalouge - 400MEfrostysidОценок пока нет

- ALPS Application Note - Leak Testing Injection Blow Molded BottlesДокумент5 страницALPS Application Note - Leak Testing Injection Blow Molded BottlesgovindОценок пока нет

- Terminal Blocks: J - AccessoriesДокумент24 страницыTerminal Blocks: J - Accessoriespaula09Оценок пока нет

- Arch. DictionaryДокумент68 страницArch. DictionaryVinay GuptaОценок пока нет