Академический Документы

Профессиональный Документы

Культура Документы

Week6 Memory Part2

Загружено:

Afs AsgИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Week6 Memory Part2

Загружено:

Afs AsgАвторское право:

Доступные форматы

Chapter 5

Large and Fast:

Exploiting Memory

Hierarchy

Main Memory Supporting Caches

Use DRAMs for main memory

Fixed width (e.g., 1 word)

Connected by fixed-width clocked bus

Bus clock is typically slower than CPU clock

Example cache block read

1 bus cycle for address transfer

15 bus cycles per DRAM access

1 bus cycle per data transfer

For 4-word block, 1-word-wide DRAM

Miss penalty = 1 + 415 + 1 = 62 bus cycles

Bandwidth = 16 bytes / 62 cycles = 0.25 B/cycle

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 2

Increasing Memory Bandwidth

4-word wide memory

Miss penalty = 1 + 15 + 1 = 17 bus cycles

Bandwidth = 16 bytes / 17 cycles = 0.94 B/cycle

4-bank interleaved memory

Miss penalty = 1 + 15 + 41 = 20 bus cycles

Bandwidth = 16 bytes / 20 cycles = 0.8 B/cycle

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 3

Advanced DRAM Organization

Bits in a DRAM are organized as a

rectangular array

DRAM accesses an entire row

Burst mode: supply successive words from a

row with reduced latency

Double data rate (DDR) DRAM

Transfer on rising and falling clock edges

Quad data rate (QDR) DRAM

Separate DDR inputs and outputs

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 4

DRAM Generations

Year Capacity $/GB 300

1980 64Kbit $1500000

250

1983 256Kbit $500000

1985 1Mbit $200000 200

1989 4Mbit $50000 Trac

150

1992 16Mbit $15000 Tcac

1996 64Mbit $10000 100

1998 128Mbit $4000

50

2000 256Mbit $1000

2004 512Mbit $250 0

2007 1Gbit $50 '80 '83 '85 '89 '92 '96 '98 '00 '04 '07

2017 16Gbit $5

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 5

5.3 Measuring and Improving Cache Performance

Measuring Cache Performance

Components of CPU time

Program execution cycles

Includes cache hit time

Memory stall cycles

Mainly from cache misses

With simplifying assumptions:

Memory stall cycles

Memory accesses

Miss rate Miss penalty

Program

Instructions Misses

Miss penalty

Program Instruction

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 6

Cache Performance Example

Given

I-cache miss rate = 2%

D-cache miss rate = 4%

Miss penalty = 100 cycles

Base CPI (ideal cache) = 2

Load & stores are 36% of instructions

Miss cycles per instruction

I-cache: 0.02 100 = 2

D-cache: 0.36 0.04 100 = 1.44

Actual CPI = 2 + 2 + 1.44 = 5.44

Ideal CPU is 5.44/2 =2.72 times faster

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 7

Average Access Time

Hit time is also important for performance

Average memory access time (AMAT)

AMAT = Hit time + Miss rate Miss penalty

Example

CPU with 1ns clock, hit time = 1 cycle, miss

penalty = 20 cycles, I-cache miss rate = 5%

AMAT = 1 + 0.05 20 = 2ns

2 cycles per instruction

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 8

Performance Summary

When CPU performance increased

Miss penalty becomes more significant

Decreasing base CPI

Greater proportion of time spent on memory

stalls

Increasing clock rate

Memory stalls account for more CPU cycles

Cant neglect cache behavior when

evaluating system performance

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 9

Associative Caches

Fully associative

Allow a given block to go in any cache entry

Requires all entries to be searched at once

Comparator per entry (expensive)

n-way set associative

Each set contains n entries

Block number determines which set

(Block number) modulo (#Sets in cache)

Search all entries in a given set at once

n comparators (less expensive)

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 10

Associative Cache Example

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 11

Spectrum of Associativity

For a cache with 8 entries

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 12

Associativity Example

Compare 4-block caches

Direct mapped, 2-way set associative,

fully associative

Block access sequence: 0, 8, 0, 6, 8

Direct mapped

Block Cache Hit/miss Cache content after access

address index 0 1 2 3

0 0 miss Mem[0]

8 0 miss Mem[8]

0 0 miss Mem[0]

6 2 miss Mem[0] Mem[6]

8 0 miss Mem[8] Mem[6]

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 13

Associativity Example

2-way set associative

Block Cache Hit/miss Cache content after access

address index Set 0 Set 1

0 0 miss Mem[0]

8 0 miss Mem[0] Mem[8]

0 0 hit Mem[0] Mem[8]

6 0 miss Mem[0] Mem[6]

8 0 miss Mem[8] Mem[6]

Fully associative

Block Hit/miss Cache content after access

address

0 miss Mem[0]

8 miss Mem[0] Mem[8]

0 hit Mem[0] Mem[8]

6 miss Mem[0] Mem[8] Mem[6]

8 hit Mem[0] Mem[8] Mem[6]

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 14

How Much Associativity

Increased associativity decreases miss

rate

But with diminishing returns

Simulation of a system with 64KB

D-cache, 16-word blocks, SPEC2000

1-way: 10.3%

2-way: 8.6%

4-way: 8.3%

8-way: 8.1%

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 15

Set Associative Cache Organization

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 16

Replacement Policy

Direct mapped: no choice

Set associative

Prefer non-valid entry, if there is one

Otherwise, choose among entries in the set

Least-recently used (LRU)

Choose the one unused for the longest time

Simple for 2-way, manageable for 4-way, too hard

beyond that

Random

Gives approximately the same performance

as LRU for high associativity

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 17

Multilevel Caches

Primary cache attached to CPU

Small, but fast

Level-2 cache services misses from

primary cache

Larger, slower, but still faster than main

memory

Main memory services L-2 cache misses

Some high-end systems include L-3 cache

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 18

Multilevel Cache Example

Given

CPU base CPI = 1, clock rate = 4GHz

Miss rate/instruction = 2%

Main memory access time = 100ns

With just primary cache

Miss penalty = 100ns/0.25ns = 400 cycles

Effective CPI = 1 + 0.02 400 = 9

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 19

Example (cont.)

Now add L-2 cache

Access time = 5ns

Global miss rate to main memory = 0.5%

Primary miss with L-2 hit

Penalty = 5ns/0.25ns = 20 cycles

Primary miss with L-2 miss

Extra penalty = 400 cycles

CPI = 1 + 0.02 20 + 0.005 400 = 3.4

Performance ratio = 9/3.4 = 2.6

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 20

Multilevel Cache Considerations

Primary cache

Focus on minimal hit time

L-2 cache

Focus on low miss rate to avoid main memory

access

Hit time has less overall impact

Results

L-1 cache usually smaller than a single cache

L-1 block size smaller than L-2 block size

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 21

Interactions with Advanced CPUs

Out-of-order CPUs can execute

instructions during cache miss

Pending store stays in load/store unit

Dependent instructions wait in reservation

stations

Independent instructions continue

Effect of miss depends on program data

flow

Much harder to analyse

Use system simulation

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 22

Interactions with Software

Misses depend on

memory access

patterns

Algorithm behavior

Compiler

optimization for

memory access

Chapter 5 Large and Fast: Exploiting Memory Hierarchy 23

Вам также может понравиться

- L - 3-AssociativeMapping - Virtual MemoryДокумент52 страницыL - 3-AssociativeMapping - Virtual MemoryLekshmiОценок пока нет

- Chapter 05 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionДокумент105 страницChapter 05 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionPriyanka Meena75% (4)

- Lecture-17 CH-05 2Документ22 страницыLecture-17 CH-05 2Osama RousanОценок пока нет

- Large and Fast: Exploiting Memory Hierarchy: Computer Organization and DesignДокумент107 страницLarge and Fast: Exploiting Memory Hierarchy: Computer Organization and DesignMin JustinОценок пока нет

- Memorias Cap5Документ115 страницMemorias Cap5GabrielОценок пока нет

- Cache DesignДокумент59 страницCache DesignChunkai HuangОценок пока нет

- Chapter 2 Adv 2007 PPTV 4Документ54 страницыChapter 2 Adv 2007 PPTV 4zelalem2022Оценок пока нет

- Lecture 12: Memory Hierarchy - Cache Optimizations: CSCE 513 Computer ArchitectureДокумент69 страницLecture 12: Memory Hierarchy - Cache Optimizations: CSCE 513 Computer ArchitectureFahim ShaikОценок пока нет

- 4 2 2Документ22 страницы4 2 2joОценок пока нет

- Unit 5 1 Cache Performance V 2Документ29 страницUnit 5 1 Cache Performance V 2LekshmiОценок пока нет

- Csa 05Документ105 страницCsa 05이다원Оценок пока нет

- Chapter 5 Large and Fast Exploiting Memory HierarchyДокумент96 страницChapter 5 Large and Fast Exploiting Memory Hierarchyq qqОценок пока нет

- ACA Unit-5Документ54 страницыACA Unit-5mannanabdulsattarОценок пока нет

- Advanced Computer Architecture-06CS81-Memory Hierarchy DesignДокумент18 страницAdvanced Computer Architecture-06CS81-Memory Hierarchy DesignYutyu YuiyuiОценок пока нет

- Cache1 2Документ30 страницCache1 2Venkat SrinivasanОценок пока нет

- Memory Hierarchies (Part 2) Review: The Memory HierarchyДокумент7 страницMemory Hierarchies (Part 2) Review: The Memory HierarchyhuyquyОценок пока нет

- CS140 Computer Organization: Chapter 6: MemoryДокумент81 страницаCS140 Computer Organization: Chapter 6: MemoryG Srilatha G SrilathaОценок пока нет

- Improving Cache PerformanceДокумент24 страницыImproving Cache Performanceramakanth_komatiОценок пока нет

- Memory Hierarchy DesignДокумент115 страницMemory Hierarchy Designshivu96Оценок пока нет

- Minmin 8Документ25 страницMinmin 8Mennah Tullah SamehОценок пока нет

- 05) Cache Memory IntroductionДокумент20 страниц05) Cache Memory IntroductionkoottyОценок пока нет

- Chapter 5: Large and Fast Exploiting Memory Hierarchy NotesДокумент16 страницChapter 5: Large and Fast Exploiting Memory Hierarchy NotesRyan KlemischОценок пока нет

- Lec 07Документ15 страницLec 07Rama DeviОценок пока нет

- Cache Memory Virtual MemoryДокумент40 страницCache Memory Virtual MemoryNeha RaoОценок пока нет

- Lecture 16Документ22 страницыLecture 16Alfian Try PutrantoОценок пока нет

- Lecture 6 Cache Optimization Contd.Документ21 страницаLecture 6 Cache Optimization Contd.Khadija Ali BaigОценок пока нет

- Lecture # 15Документ27 страницLecture # 15Noman Ajaz KørãíОценок пока нет

- Large and Fast: Exploiting Memory Hierarchy: The Hardware/Software Interface 5Документ49 страницLarge and Fast: Exploiting Memory Hierarchy: The Hardware/Software Interface 5Sara AlkheilОценок пока нет

- AC14L08 Memory HierarchyДокумент20 страницAC14L08 Memory HierarchyAlexОценок пока нет

- PartsДокумент3 страницыPartsAngela GalloОценок пока нет

- William Stallings Computer Organization and Architecture 9 EditionДокумент46 страницWilliam Stallings Computer Organization and Architecture 9 EditionGriya LidyaОценок пока нет

- Computer Architecture and Organization: Lecture16: Cache PerformanceДокумент17 страницComputer Architecture and Organization: Lecture16: Cache PerformanceMatthew R. PonОценок пока нет

- Computer ArchitectureДокумент5 страницComputer ArchitecturerudemaverickОценок пока нет

- Basic Optimization Techniques in Cache Memory 2.2.4Документ4 страницыBasic Optimization Techniques in Cache Memory 2.2.4harshdeep singhОценок пока нет

- Memory Hierarchy Design-AcaДокумент15 страницMemory Hierarchy Design-AcaGuruCharan SinghОценок пока нет

- Cache Performance Average Memory Access TimeДокумент23 страницыCache Performance Average Memory Access TimePulagam Lakshmi Sampath Reddy 21BME1298Оценок пока нет

- Memory Hierarchy - Introduction: Cost Performance of Memory ReferenceДокумент52 страницыMemory Hierarchy - Introduction: Cost Performance of Memory Referenceravi_jolly223987Оценок пока нет

- 13-Chapter5 Cache MEM P3Документ24 страницы13-Chapter5 Cache MEM P3Rayan HdadaОценок пока нет

- CPU CacheДокумент19 страницCPU Cache22194Оценок пока нет

- CH04Документ46 страницCH04sidОценок пока нет

- 10 1 1 92 377 PDFДокумент22 страницы10 1 1 92 377 PDFAzizul BaharОценок пока нет

- CHAPTER 2 Memory Hierarchy Design & APPENDIX B. Review of Memory HeriarchyДокумент73 страницыCHAPTER 2 Memory Hierarchy Design & APPENDIX B. Review of Memory HeriarchyRachmadio Nayub LazuardiОценок пока нет

- 5.2 Eleven Advanced Optimizations of Cache PerformanceДокумент13 страниц5.2 Eleven Advanced Optimizations of Cache PerformanceCieluu PandaОценок пока нет

- Computer Architecture: Memory Hierarchy DesignДокумент60 страницComputer Architecture: Memory Hierarchy Designapi-26594847Оценок пока нет

- Lecture 5: Memory Hierarchy and Cache Traditional Four Questions For Memory Hierarchy DesignersДокумент10 страницLecture 5: Memory Hierarchy and Cache Traditional Four Questions For Memory Hierarchy Designersdeepu7deeptiОценок пока нет

- Chapter 3 CacheДокумент38 страницChapter 3 CacheSetina AliОценок пока нет

- Embedded Systems Unit 8 NotesДокумент17 страницEmbedded Systems Unit 8 NotesPradeep Kumar Goud NadikudaОценок пока нет

- Caches and MemoryДокумент65 страницCaches and MemoryRupjit ChakrabortyОценок пока нет

- Slides04 05Документ25 страницSlides04 05need4eatОценок пока нет

- Computer Architecture Cache DesignДокумент28 страницComputer Architecture Cache Designprahallad_reddy100% (3)

- Memory Design: SOC and Board-Based SystemsДокумент48 страницMemory Design: SOC and Board-Based SystemsSathiyaSeelaОценок пока нет

- Chapter 03Документ58 страницChapter 03Tram NguyenОценок пока нет

- Lec 6Документ18 страницLec 6Rama DeviОценок пока нет

- HW4Документ3 страницыHW40123456789abcdefgОценок пока нет

- Internal Assignment 2 On Memory Organization F.M-100Документ1 страницаInternal Assignment 2 On Memory Organization F.M-100Sukanta KunduОценок пока нет

- Module One - Part I - Memory IntroДокумент20 страницModule One - Part I - Memory Intronirosha vijayОценок пока нет

- Chapter 6Документ37 страницChapter 6shubhamvslaviОценок пока нет

- Study Set 12 Memory Components and DRAMДокумент8 страницStudy Set 12 Memory Components and DRAMjnubkuybОценок пока нет

- CO Unit 3Документ86 страницCO Unit 3KarthikОценок пока нет

- Large and Fast: Exploiting Memory HierarchyДокумент24 страницыLarge and Fast: Exploiting Memory HierarchyAfs AsgОценок пока нет

- Week8 SampleMidtermДокумент2 страницыWeek8 SampleMidtermAfs AsgОценок пока нет

- Week4 InstructionsДокумент36 страницWeek4 InstructionsAfs AsgОценок пока нет

- Chapter 1 Part 2: Computer Abstractions and TechnologyДокумент27 страницChapter 1 Part 2: Computer Abstractions and TechnologyAfs AsgОценок пока нет

- 1 Differential Eqn - Lecture Notes 7Документ7 страниц1 Differential Eqn - Lecture Notes 7Afs AsgОценок пока нет

- 1 Differential Eqn - Lecture Notes 6: 1.1 Substitution Methods, Homogeneous Equations, Bernoulli Equa-TionsДокумент8 страниц1 Differential Eqn - Lecture Notes 6: 1.1 Substitution Methods, Homogeneous Equations, Bernoulli Equa-TionsAfs AsgОценок пока нет

- 1 Differential Eqn. Lecture Notes 1: 1.1 Introduction and Elementary ConceptsДокумент4 страницы1 Differential Eqn. Lecture Notes 1: 1.1 Introduction and Elementary ConceptsAfs AsgОценок пока нет

- Opentext Capture Recognition Engine Release NotesДокумент15 страницOpentext Capture Recognition Engine Release NotesHimanshi GuptaОценок пока нет

- Domains (Meinberg) Install GuideДокумент21 страницаDomains (Meinberg) Install GuideManu DafonteОценок пока нет

- Group 4: Prachi Agarwal, Kriti Sharan, Sumit Naugraiya, Sumit Puri, Vishnu Sharma & Govind DagaДокумент53 страницыGroup 4: Prachi Agarwal, Kriti Sharan, Sumit Naugraiya, Sumit Puri, Vishnu Sharma & Govind DagakritisharanОценок пока нет

- Pose Estimation of Large Scale Objects With 3DДокумент20 страницPose Estimation of Large Scale Objects With 3DAljosa OsepОценок пока нет

- Course No.: CE-331A, Geoinformatics (3-0-2-0)Документ2 страницыCourse No.: CE-331A, Geoinformatics (3-0-2-0)Pranjal SinghОценок пока нет

- Is The Biochip The Mark of The BeastДокумент32 страницыIs The Biochip The Mark of The BeastAntu JohnОценок пока нет

- Dav DZ340 PDFДокумент92 страницыDav DZ340 PDFCurtoAVidaОценок пока нет

- Compiler Lab VivaДокумент6 страницCompiler Lab VivaGaurav SharmaОценок пока нет

- IM4A5-32 LatticeДокумент62 страницыIM4A5-32 LatticeAnkitОценок пока нет

- Dm1 Introduction ML Data MiningДокумент39 страницDm1 Introduction ML Data MiningSubir RanjanОценок пока нет

- Camera Trap ManualДокумент94 страницыCamera Trap ManualAndreas VetraОценок пока нет

- Female Cordset: ADOAH040VAS0002E04Документ2 страницыFemale Cordset: ADOAH040VAS0002E04Sujata KulkarniОценок пока нет

- Proposal Project PrintingДокумент13 страницProposal Project PrintinglodewОценок пока нет

- Cartilla de Actividades de Inglés: Escuela N°127 DR Mariano MorenoДокумент6 страницCartilla de Actividades de Inglés: Escuela N°127 DR Mariano MorenoJosé Sisalli SaadОценок пока нет

- Documentation Matrix DS QMS 00 R2Документ19 страницDocumentation Matrix DS QMS 00 R2DhinakaranОценок пока нет

- Siemens Hicom 300 Set T8 ManualДокумент28 страницSiemens Hicom 300 Set T8 ManualFrank Sky WalkerОценок пока нет

- 2 - Site Crisis Management Plan TemplateДокумент42 страницы2 - Site Crisis Management Plan Templatesentryx1100% (7)

- MC Line: Multifunction Three Phase Overvoltage / Undervoltage RelayДокумент3 страницыMC Line: Multifunction Three Phase Overvoltage / Undervoltage RelayCerduardo Chanchisco Roga RojasОценок пока нет

- Manual Survey Pro For RangerДокумент337 страницManual Survey Pro For RangerIni ChitozОценок пока нет

- Rajesh Vasa - PHD ThesisДокумент252 страницыRajesh Vasa - PHD Thesisrajeshvasa100% (1)

- StqaДокумент169 страницStqaHimanshu SinghaniОценок пока нет

- Seminar Report On Virtual Laser KeyboardДокумент18 страницSeminar Report On Virtual Laser KeyboardAnimesh71% (7)

- Spatial AnalysisДокумент91 страницаSpatial Analysischiradzulu83% (6)

- Installation of A PCS7 Project 1Документ115 страницInstallation of A PCS7 Project 1Mohammad HaiderОценок пока нет

- Best Lesson PlanДокумент4 страницыBest Lesson Planapi-398545121Оценок пока нет

- Mba Time Table Updated On 1st Nov 2021Документ4 страницыMba Time Table Updated On 1st Nov 2021KNRavi KiranОценок пока нет

- WDM Important Questions 1Документ3 страницыWDM Important Questions 1PinkОценок пока нет

- HP Moonshot Provisiong Manager User GuideДокумент44 страницыHP Moonshot Provisiong Manager User GuideBalasubramanian ReguramanОценок пока нет

- SEC08-20 Rehabilitation TechnologyДокумент2 страницыSEC08-20 Rehabilitation TechnologyJuliana Orjuela Garcia100% (1)

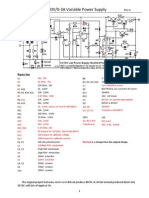

- Modified 0-30V - 0-3A Variable Power Supply - Rev.2Документ2 страницыModified 0-30V - 0-3A Variable Power Supply - Rev.2Manuel Cereijo NeiraОценок пока нет