Академический Документы

Профессиональный Документы

Культура Документы

DSD Lession Plan

Загружено:

er.deepakgangwar53930 оценок0% нашли этот документ полезным (0 голосов)

323 просмотров2 страницыdsd lesson plan

Оригинальное название

Dsd Lession Plan

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документdsd lesson plan

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

323 просмотров2 страницыDSD Lession Plan

Загружено:

er.deepakgangwar5393dsd lesson plan

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 2

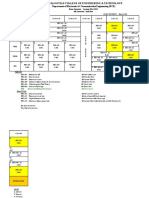

Academic plan for 5th Semester

Lesson Plan Digital System Design ETEC-309

S. No. Topic Lectures (44)

UNIT 1

1 Introduction to VHDL, design units, data objects, 2

2 signal drivers, inertial and transport delays, delta delay, 2

3 VHDL data types, concurrent and sequential statements. 2

4 Subprograms Functions, Procedures, attributes, generio, generate, 2

package,

5 IEEE standard logic library, file I/O, 2

6 Test bench, component declaration, instantiation, configuration. 2

UNIT 2

7 Combinational logic circuit design and VHDL implementation of 2

following circuits first adder, Subtractor,

8 decoder, encoder, 2

9 multiplexer, 1

10 Arithmetic Logic Unit, 1

11 barrel shifter, 1

12 4X4 key board encoder, 1

13 multiplier, 1

14 divider, 1

15 Hamming code encoder and correction circuits. 2

UNIT 3

16 Synchronous sequential circuits design finite state machines, 2

Mealy and Moore,

17 state assignments, 2

18 design and VHDL implementation of FSMs, 3

19 Linear feedback shift register (Pseudorandom and CRC). 3

UNIT 4

20 Asynchronous sequential circuit design primitive flow table, 2

concept of race, critical race and hazards,

21 design issues like metastability, synchronizers, clock skew and 2

timing considerations

22 Introduction to place & route process, 2

23 Introduction to ROM, PLA, PAL, Architecture of CPLD 2

(Xilinx/Altera).

24 Architecture of CPLD (Xilinx/Altera). 2

Text Books:

[T1] Douglas Perry ,VHDL 4th Edition, TMH

[T2] Stephen Brown, Zvonko Vranesic, Fundamentals of Digital Logic with VHDL design,

TMH.

Reference Books:

[R1] Charles. H.Roth ,Digital System Design using VHDL, PWS (1998)

[R2] John F. Wakerley ,Digital Design Principles And Practices ,Pearson Education

[R3] Navabi Z , VHDL-Analysis & Modelling of Digital Systems,McGraw Hill.

[R4] William I. Fletcher, An Engineering Approach To Digital Design, Prentice Hall

[R5] Bhasker, A VHDL Primmer, Prentice Hall 1995.

Вам также может понравиться

- Digital Integrated Circuits Syllabus'Документ2 страницыDigital Integrated Circuits Syllabus'shiv123charanОценок пока нет

- Switch 6Документ3 страницыSwitch 6karthiksvr26Оценок пока нет

- Ita1002 Digital-Computer-Fundamentals Eth 1.0 0 Ita1002Документ2 страницыIta1002 Digital-Computer-Fundamentals Eth 1.0 0 Ita1002ShivamОценок пока нет

- DICAДокумент2 страницыDICAak5775Оценок пока нет

- DCD HandoutДокумент38 страницDCD HandoutPrathap VuyyuruОценок пока нет

- Digital SystemsДокумент675 страницDigital SystemsvikramjhaОценок пока нет

- Digital Logic DesignДокумент8 страницDigital Logic DesignShubham ChoksiОценок пока нет

- Digital Circuits and SystemsДокумент3 страницыDigital Circuits and SystemsAayush JainОценок пока нет

- Cse1003 Digital-logic-And-Design Eth 1.1 47 Cse1003Документ8 страницCse1003 Digital-logic-And-Design Eth 1.1 47 Cse1003Shiva Charan0% (1)

- VTU Logic DesginДокумент2 страницыVTU Logic Desginmanju_mОценок пока нет

- Number System and RepresentationДокумент4 страницыNumber System and RepresentationVani telluriОценок пока нет

- Mapping of Course Outcomes With Student Outcomes CO - NO. Course Outcome's Mapped SO BTLДокумент7 страницMapping of Course Outcomes With Student Outcomes CO - NO. Course Outcome's Mapped SO BTLMohan KumarОценок пока нет

- B Tech ECE 5th Sem Lecture PLAN PDFДокумент5 страницB Tech ECE 5th Sem Lecture PLAN PDFishaОценок пока нет

- JДокумент1 страницаJ;(Оценок пока нет

- Lecture PlanДокумент1 страницаLecture Planlaviniaandronicus9Оценок пока нет

- Digital Electronics: Course Description and ObjectivesДокумент3 страницыDigital Electronics: Course Description and ObjectivesMaxОценок пока нет

- Demulti Plexer and MultiolexerДокумент7 страницDemulti Plexer and Multiolexerkaran007_mОценок пока нет

- Syllabus DLDA DSLДокумент4 страницыSyllabus DLDA DSLShirish RansingОценок пока нет

- B. P. Mandal College of Engineering Digital Electronics SyllabusДокумент1 страницаB. P. Mandal College of Engineering Digital Electronics SyllabusManoKumarОценок пока нет

- Logic DesignДокумент3 страницыLogic DesignHarsh BharadwajОценок пока нет

- STLD Important TopicsДокумент1 страницаSTLD Important TopicsAdari G V Chiranjeevi ACOE100% (2)

- Ref. 1. (N. G. Palan) VHDL Programming: Half and Full Adder, Full Subractor, Four Bit BinaryДокумент2 страницыRef. 1. (N. G. Palan) VHDL Programming: Half and Full Adder, Full Subractor, Four Bit Binarysonawaneulhas292Оценок пока нет

- Embedded System Lesson PlanДокумент4 страницыEmbedded System Lesson PlandeccancollegeОценок пока нет

- Test I Test II Test III Test IVДокумент4 страницыTest I Test II Test III Test IVAnisha SooryagayathramОценок пока нет

- Syllabus COДокумент7 страницSyllabus COAshwini MateОценок пока нет

- Digital System Design Lecture PlanДокумент4 страницыDigital System Design Lecture PlanIshita AggarwalОценок пока нет

- Sr. No. Topic NameДокумент1 страницаSr. No. Topic Namejibor83531Оценок пока нет

- 2008 PT-syllabusДокумент1 страница2008 PT-syllabusmuraliece muralieceОценок пока нет

- Beee206l Digital-Electronics TH 1.0 70 Beee206lДокумент2 страницыBeee206l Digital-Electronics TH 1.0 70 Beee206lComical comicОценок пока нет

- Detailed Syllabus1Документ17 страницDetailed Syllabus1DheereshОценок пока нет

- SyllabusДокумент2 страницыSyllabusnishantmanderna20Оценок пока нет

- 6Xn1 Digital Integrated CircuitsДокумент2 страницы6Xn1 Digital Integrated CircuitsapbhatkarОценок пока нет

- EE 271 Digital Circuits and Systems: Course Specification (Syllabus)Документ41 страницаEE 271 Digital Circuits and Systems: Course Specification (Syllabus)R.R.S. SavichevaОценок пока нет

- NU (DIGITTAL ELECTRONICS AND INSTRUMENTS) LatestДокумент2 страницыNU (DIGITTAL ELECTRONICS AND INSTRUMENTS) Latestkhushalee.chavadaОценок пока нет

- Logic Design Course OverviewДокумент1 страницаLogic Design Course OverviewVishal JoshiОценок пока нет

- Syllabus PDFДокумент1 страницаSyllabus PDFJitha VargheseОценок пока нет

- BEEE206L - DIGITAL-ELECTRONICS - TH - 1.0 - 67 - Digital ElectronicsДокумент3 страницыBEEE206L - DIGITAL-ELECTRONICS - TH - 1.0 - 67 - Digital ElectronicsNithish kumar RajendranОценок пока нет

- EC4002 - Digital Logic DesignДокумент5 страницEC4002 - Digital Logic DesignTarangОценок пока нет

- Digital Electronics Combinational and Sequential Circuit DesignДокумент2 страницыDigital Electronics Combinational and Sequential Circuit DesignjeevaОценок пока нет

- Structural Digital System Design - Lession PlanДокумент1 страницаStructural Digital System Design - Lession Planviswanathsreenath200Оценок пока нет

- EE206 DigitalSystemDesignДокумент2 страницыEE206 DigitalSystemDesignRajalearn2 Ramlearn2Оценок пока нет

- Microprocessor DSP Course OverviewДокумент3 страницыMicroprocessor DSP Course OverviewAbhishek Rao AmbedkarОценок пока нет

- Course Plan Dsp1Документ3 страницыCourse Plan Dsp1lakshg11Оценок пока нет

- Digital Circuits and SystemsДокумент2 страницыDigital Circuits and SystemsSuvdeep NayakОценок пока нет

- Digital Ic ApplicationsДокумент1 страницаDigital Ic ApplicationsChandrashekar67% (3)

- Text BooksДокумент2 страницыText BooksmtariqanwarОценок пока нет

- S.No Topics Lec: Advanced Computer Network ETCS-401Документ4 страницыS.No Topics Lec: Advanced Computer Network ETCS-401Anshul MittalОценок пока нет

- DIC SyllabusДокумент1 страницаDIC SyllabusSneha NargundkarОценок пока нет

- Digital Design SyllabusДокумент3 страницыDigital Design SyllabusRahul KumarОценок пока нет

- Ec6302 Digital Electronics PDFДокумент206 страницEc6302 Digital Electronics PDFAngelinОценок пока нет

- CSE 1003 - DigitalLogicDesignДокумент9 страницCSE 1003 - DigitalLogicDesignTeja nОценок пока нет

- BE2101 - Basic Electronics: (1 Semester - CS, IT) Credits: 3 Contact Hours: 3Документ3 страницыBE2101 - Basic Electronics: (1 Semester - CS, IT) Credits: 3 Contact Hours: 3Minimol RajОценок пока нет

- Digital Electronics SylabusДокумент1 страницаDigital Electronics SylabusTushar Kanti BeraОценок пока нет

- ECE101:Digital System Design: Syllabus Overview & Introduction To Digital ConceptsДокумент24 страницыECE101:Digital System Design: Syllabus Overview & Introduction To Digital ConceptsEzhil Ramanathan100% (1)

- DPCO_RegulationsДокумент6 страницDPCO_RegulationsPoovizhi BalanОценок пока нет

- Single and Multi-Chip Microcontroller Interfacing: For the Motorola 6812От EverandSingle and Multi-Chip Microcontroller Interfacing: For the Motorola 6812Оценок пока нет

- Dedicated Digital Processors: Methods in Hardware/Software Co-DesignОт EverandDedicated Digital Processors: Methods in Hardware/Software Co-DesignОценок пока нет

- Deepak Gangwar CV1Документ4 страницыDeepak Gangwar CV1er.deepakgangwar5393Оценок пока нет

- Digital CommДокумент1 страницаDigital Commer.deepakgangwar5393Оценок пока нет

- Digital CommДокумент1 страницаDigital Commer.deepakgangwar5393Оценок пока нет

- Monitoring Time TableДокумент33 страницыMonitoring Time Tableer.deepakgangwar5393Оценок пока нет

- UPSC Duty Chart 2016 BlankДокумент12 страницUPSC Duty Chart 2016 Blanker.deepakgangwar5393Оценок пока нет

- DHN To HWHДокумент2 страницыDHN To HWHer.deepakgangwar5393Оценок пока нет

- Time Table 16'jan'17 Even Sem 2016-17 1.3 SKДокумент24 страницыTime Table 16'jan'17 Even Sem 2016-17 1.3 SKer.deepakgangwar5393Оценок пока нет

- Templates FinalДокумент2 страницыTemplates Finaler.deepakgangwar5393Оценок пока нет

- Galgotias College ECE TimetableДокумент43 страницыGalgotias College ECE Timetableer.deepakgangwar5393Оценок пока нет

- Time Table Wef 28 Jul2015Документ56 страницTime Table Wef 28 Jul2015er.deepakgangwar5393Оценок пока нет

- Time Table FINAL 29th AugДокумент28 страницTime Table FINAL 29th Auger.deepakgangwar5393Оценок пока нет

- Monitoring Time Table 5 AUG 16Документ4 страницыMonitoring Time Table 5 AUG 16er.deepakgangwar5393Оценок пока нет

- Answer Any FIVE QuestionsДокумент4 страницыAnswer Any FIVE Questionser.deepakgangwar5393Оценок пока нет

- Modified Individual 3 April 2017Документ15 страницModified Individual 3 April 2017er.deepakgangwar5393Оценок пока нет

- Non Reporting ListДокумент40 страницNon Reporting Lister.deepakgangwar5393Оценок пока нет

- Final Year Project Presentation (PCB Lab On 31-03-2015 Timing 2:30 To 5 P.M.)Документ2 страницыFinal Year Project Presentation (PCB Lab On 31-03-2015 Timing 2:30 To 5 P.M.)er.deepakgangwar5393Оценок пока нет

- Form 12BB Tax Deduction Claim DetailsДокумент3 страницыForm 12BB Tax Deduction Claim Detailser.deepakgangwar5393Оценок пока нет

- Modified Individual 3 April 2017Документ15 страницModified Individual 3 April 2017er.deepakgangwar5393Оценок пока нет

- Final Year Project Presentation (PCB Lab On 31-03-2015 Timing 2:30 To 5 P.M.)Документ2 страницыFinal Year Project Presentation (PCB Lab On 31-03-2015 Timing 2:30 To 5 P.M.)er.deepakgangwar5393Оценок пока нет

- Organizing Committee DetailsДокумент2 страницыOrganizing Committee Detailser.deepakgangwar5393Оценок пока нет

- Antenna DesignДокумент1 страницаAntenna Designer.deepakgangwar5393Оценок пока нет

- Modified Individual 3 April 2017Документ15 страницModified Individual 3 April 2017er.deepakgangwar5393Оценок пока нет

- Ajanta Pharma LTDДокумент3 страницыAjanta Pharma LTDer.deepakgangwar5393Оценок пока нет

- Project Evaluation FormatДокумент2 страницыProject Evaluation Formater.deepakgangwar5393Оценок пока нет

- Time Table Wef 29 Jan 15 (4) LatestДокумент43 страницыTime Table Wef 29 Jan 15 (4) Latester.deepakgangwar5393Оценок пока нет

- Microstrip Patch Antenna Tutorial: Simulation and Experimental ResultsДокумент11 страницMicrostrip Patch Antenna Tutorial: Simulation and Experimental Resultscoolpixs4Оценок пока нет

- TT All Faculty 28 Jan 15Документ258 страницTT All Faculty 28 Jan 15er.deepakgangwar5393Оценок пока нет

- B.tech Ist Year SyllabusДокумент100 страницB.tech Ist Year Syllabuser.deepakgangwar5393Оценок пока нет

- Electronics & Comm. EnggДокумент14 страницElectronics & Comm. Engger.deepakgangwar5393Оценок пока нет

- Versao 4.2: Databasetype Postgresql 8.3 Date 02/03/2018Документ31 страницаVersao 4.2: Databasetype Postgresql 8.3 Date 02/03/2018rodrigoОценок пока нет

- TOC for document on programming concepts and technologiesДокумент38 страницTOC for document on programming concepts and technologiesAnand KumarОценок пока нет

- C Operators Questions and AnswersДокумент21 страницаC Operators Questions and AnswersWycliffe MwebiОценок пока нет

- Simply Rhino V-Ray For Rhino TrainingДокумент7 страницSimply Rhino V-Ray For Rhino Trainingkaisersoze_01Оценок пока нет

- Fcnsa - Fortigate Administration - NSE4 IДокумент38 страницFcnsa - Fortigate Administration - NSE4 IBlas DiazОценок пока нет

- CS 2252 - Microprocessors and Microcontrollers PDFДокумент2 страницыCS 2252 - Microprocessors and Microcontrollers PDFvelkarthi92Оценок пока нет

- Office365Migration DetailedProjectPlanДокумент4 страницыOffice365Migration DetailedProjectPlanJSОценок пока нет

- IBM BPM Best Practices - Process Modeling 5 Golden Rules - BHДокумент31 страницаIBM BPM Best Practices - Process Modeling 5 Golden Rules - BHGustavo ApodacaОценок пока нет

- 5.2.1.7 Lab - Viewing The Switch MAC Address TableДокумент5 страниц5.2.1.7 Lab - Viewing The Switch MAC Address Tablecesar andres ruiz carpioОценок пока нет

- Amit Kumar: 9470 Valley Ranch Pkwy E, Apt 2056, Irving, Texas 75063 US Home: +1-469-547-1558 US Cell:+1-972-489-7307Документ5 страницAmit Kumar: 9470 Valley Ranch Pkwy E, Apt 2056, Irving, Texas 75063 US Home: +1-469-547-1558 US Cell:+1-972-489-7307Amit KashyapОценок пока нет

- ARIS PPM System ArchitectureДокумент84 страницыARIS PPM System ArchitectureErdoğan Gökalp100% (1)

- A.: Understanding PC Hardware by Jemma, IncДокумент2 страницыA.: Understanding PC Hardware by Jemma, IncStephany Bryan Diez ItaoОценок пока нет

- RUP Informacion de ArtefactosДокумент39 страницRUP Informacion de ArtefactosJorge Luis Idiaquez HigaОценок пока нет

- Notes On Web ProgrammingДокумент5 страницNotes On Web ProgrammingianОценок пока нет

- SPSS QC Scripting HelpДокумент6 страницSPSS QC Scripting HelpMaverick 'Moriarty' JonesОценок пока нет

- AIOU Solved Assignments 1 & 2 Code 8620 Spring 2019 - AIOU Tutors PDFДокумент11 страницAIOU Solved Assignments 1 & 2 Code 8620 Spring 2019 - AIOU Tutors PDFRabab MahmoodОценок пока нет

- Research On AWS GlueДокумент5 страницResearch On AWS GlueJack Kenneth Bondoc-CutiongcoОценок пока нет

- AG2425 Spatial DatabasesДокумент36 страницAG2425 Spatial DatabasessriniОценок пока нет

- GSM-Based Electronic Notice Display SystemДокумент29 страницGSM-Based Electronic Notice Display SystemHarsh BhatiaОценок пока нет

- Technical Architecture System Design TemplateДокумент18 страницTechnical Architecture System Design TemplateSmitasamrat0% (1)

- Digital System Design Using Verilog December 2011Документ1 страницаDigital System Design Using Verilog December 2011Vinayaka HmОценок пока нет

- 4Документ17 страниц4endrisОценок пока нет

- Fundamentals of computer systems storage devicesДокумент6 страницFundamentals of computer systems storage devicesKhamisi BylalОценок пока нет

- Citrix Virtual Apps and Desktops 7 Advanced AdministrationДокумент3 страницыCitrix Virtual Apps and Desktops 7 Advanced Administrationd0wonloadОценок пока нет

- Relational Database PosterДокумент1 страницаRelational Database Posterapi-243325383Оценок пока нет

- Configuracion Firewall 2-5-2013Документ8 страницConfiguracion Firewall 2-5-2013Miguel Angel Medina BerdejaОценок пока нет

- ARIS Client Installation GuideДокумент22 страницыARIS Client Installation GuideJorgeОценок пока нет

- OS Concepts & ExercisesДокумент5 страницOS Concepts & ExercisesTediElmasОценок пока нет

- Image CompressionДокумент33 страницыImage CompressionMAILMEUSОценок пока нет