Академический Документы

Профессиональный Документы

Культура Документы

PIC 16F877 - CALM Instructions

Загружено:

des_troyer_840 оценок0% нашли этот документ полезным (0 голосов)

12 просмотров1 страницаsddf

Оригинальное название

16F877Calm

Авторское право

© © All Rights Reserved

Доступные форматы

DOC, PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документsddf

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате DOC, PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

12 просмотров1 страницаPIC 16F877 - CALM Instructions

Загружено:

des_troyer_84sddf

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате DOC, PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 1

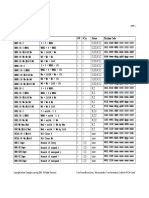

PIC 16F877 - CALM instructions

Code 14 bits Microchip CALM Flags Operation

110000 kkkkkkkk movlw val Move #Val,W [none]

000000 1fffffff movwf reg Move W,Reg [none]

001000 0fffffff movf reg,0 Move Reg,W [Z]

001000 1fffffff movf reg,1 Test Reg [Z]

000000 01100010 option Move W,Option [none]

000000 01100101 tris porta Move W,TrisA 1 [none]

000000 01100110 tris portb Move W,TrisB 1 [none]

000000 01100111 tris portc Move W,TrisC 1 [none]

111110 kkkkkkkk addlw val Add #Val,W [C,D,Z] #Val+W -> W

000111 0fffffff addwf reg,0 Add Reg,W [C,D,Z] Reg+W -> W

000111 1fffffff addwf reg,1 Add W,Reg [C,D,Z]

111100 kkkkkkkk sublw val Sub W,#Val,W [C2,D,Z] #Val+(-W) -> W

000010 0fffffff subwf reg,0 Sub W,Reg,W [C2,D,Z] Reg+(-W) -> W

000010 1fffffff subwf reg,1 Sub W,Reg [C2,D,Z] Reg+(-W) -> Reg

111001 kkkkkkkk andlw val And #Val,W [Z]

000101 0fffffff andwf reg,0 And Reg,W [Z]

000101 1fffffff andwf reg,1 And W,Reg [Z]

111000 kkkkkkkk iorlw val Or #Val,W [Z]

000100 0fffffff iorwf reg,0 Or Reg,W [Z]

000100 1fffffff iorwf reg,1 Or W,Reg [Z]

111010 kkkkkkkk xorlw val Xor #Val,W [Z]

000110 0fffffff xorwf reg,0 Xor Reg,W [Z]

000110 1fffffff xorwf reg,1 Xor W,Reg [Z]

001110 0fffffff swapf reg,0 Swap Reg,W [none] Reg swapped Reg

001110 1fffffff swapf reg,1 Swap Reg [none] Reg Reg sw. Reg W

000001 1fffffff clrf reg Clr Reg [Z=1]

000001 00000000 clrw Clr W [none]

000000 01100100 clrwdt ClrWDT [none]

000000 01100011 sleep Sleep [none]

001001 1fffffff comf reg,1 Not Reg [Z] Reg .not.Reg

001001 0fffffff comf reg,0 Not Reg,W [Z] Reg Reg .not.Reg W

001010 1fffffff incf reg,1 Inc Reg [Z] Reg+1 Reg

001010 0fffffff incf reg,0 Inc Reg,W [Z] Reg Reg Reg+1 W

000011 1fffffff decf reg,1 Dec Reg [Z] Reg-1 Reg

000011 0fffffff decf reg,0 Dec Reg,W [Z] Reg Reg Reg-1 W

001101 1fffffff rlf reg,1 RLC Reg [C] Reg .rlc.Reg

001101 0fffffff rlf reg,0 RLC Reg,W [C] Reg Reg .rlc.Reg W

001100 1fffffff rrf reg,1 RRC Reg [C] Reg .rrc.Reg

001100 0fffffff rrf reg,0 RRC Reg,W [C] Reg Reg .rrc.Reg W

0100bb bfffffff bcf reg,b Clr Reg:#b [none]

0101bb bfffffff bsf reg,b Set Reg:#b [none]

001111 1fffffff incfsz reg,1 IncSkip,EQ Reg [none] Reg+1 Reg

001111 0fffffff incfsz reg,0 IncSkip,EQ Reg,W [none] Reg Reg Reg+1 W

001011 1fffffff decfsz reg,1 DecSkip,EQ Reg [none] Reg-1 Reg

001011 0fffffff decfsz reg,0 DecSkip,EQ Reg,W [none] Reg Reg Reg-1 W

0110bb bfffffff btfsc reg,b TestSkip,BC Reg:#b [none]

0111bb bfffffff btfss reg,d TestSkip,BS Reg:#b [none]

101kkk kkkkkkkk goto addr Jump Addr [none]

100kkk kkkkkkkk call addr Call Addr [none]

110100 kkkkkkkk retlw val RetMove #Val,W [none]

000000 00001000 return Ret [none]

000000 00001001 retfie RetI [int]

000000 00000000 nop Nop [none]

bcf status,0 CLRC Clr F:#0

bsf status,0 SETC Set F:#0

btfss status,0 Skip,CS TestSkip,BS F:#0

btfsc status,0 Skip,CC TestSkip,BC F:#0

btfss status,2 Skip,EQ TestSkip,BS F:#2

Skip,ZS

btfsc status,2 Skip,NE btfsc status,2

Skip,ZC

Note 1: Move W,TrisD, Move W,TrisE does not exist. Select in

Bank1

Note 2: Processor add the 2-s complement; Carry value is

inverted compared to most other P

All instructions execute in 4 clock cycles (1 S at 4 MHz) except the Skip, Jump, Call and Ret that takes the double

Compare for equality: Xor W,Reg or Xor Reg,W Compare for Inequality: Sub instruction, but be careful

Except I/O, 16F87x, and other 14-bit instruction PICs have the same instruction set. jdn060828

Вам также может понравиться

- Appendix: Summary of The PIC18 Instruction SetДокумент6 страницAppendix: Summary of The PIC18 Instruction SetLoftie DeyzelОценок пока нет

- Field Description: WD Destination Register Select: 0000 W0 1111 W15Документ8 страницField Description: WD Destination Register Select: 0000 W0 1111 W15Juan Pablo PeñaОценок пока нет

- Instrucciones Del Pic16f84Документ15 страницInstrucciones Del Pic16f84Gaston Rodrigo PotenzaОценок пока нет

- Modelo ExamenДокумент7 страницModelo ExamenVIOLINISTA DE COMARAPAОценок пока нет

- Instruction SetДокумент4 страницыInstruction SetDinesh KumarОценок пока нет

- PIC16F84A: TABLE 7-2: Pic16Cxxx Instruction SetДокумент1 страницаPIC16F84A: TABLE 7-2: Pic16Cxxx Instruction SetKev GamesОценок пока нет

- Instructions SetДокумент1 страницаInstructions SetAbdulrahman JaberОценок пока нет

- Instrucciones PIC16F84AДокумент1 страницаInstrucciones PIC16F84AFabián Antonio Casas HuertaОценок пока нет

- Microcontroller Based Scada: Monitoring Station IndustryДокумент12 страницMicrocontroller Based Scada: Monitoring Station IndustrySelva GanapathyОценок пока нет

- 2.3 Arithmetic Instructions1Документ14 страниц2.3 Arithmetic Instructions1Nour Ziad Ibrahim AlkurdiОценок пока нет

- PIC18f Instruction SetДокумент3 страницыPIC18f Instruction SetSaivan HamamaОценок пока нет

- Measuring Speed and Position With A Quadrature EncoderДокумент3 страницыMeasuring Speed and Position With A Quadrature Encoderbetodias30Оценок пока нет

- Control UnitДокумент19 страницControl UnitHarshaОценок пока нет

- Lec Nnaik Sequential CircuitsДокумент27 страницLec Nnaik Sequential Circuits11kumarvishal4Оценок пока нет

- RISC-V Reference CardДокумент2 страницыRISC-V Reference CardTeresinha TeixeiraОценок пока нет

- TABLE 5-1: Special Function Register Map For Pic18F2Xk20/4Xk20 DevicesДокумент47 страницTABLE 5-1: Special Function Register Map For Pic18F2Xk20/4Xk20 DevicesDiego Vazquez GonzalezОценок пока нет

- Pep9 ReferenceДокумент6 страницPep9 Reference19524 AlekhyaОценок пока нет

- Microchip PIC16F8x Instruction SetДокумент3 страницыMicrochip PIC16F8x Instruction Setduo2coreОценок пока нет

- PIC24 Instruction Set SummaryДокумент8 страницPIC24 Instruction Set SummaryjhoanОценок пока нет

- P ROYECTO6, RAPIDДокумент2 страницыP ROYECTO6, RAPIDDiego Alonso Sanchez CipiranОценок пока нет

- MPMC Using Emulator 8086Документ8 страницMPMC Using Emulator 8086Smruti Smita PriyadarshiniОценок пока нет

- Laser G-Code Processing ExampleДокумент5 страницLaser G-Code Processing ExampleYakov ZinovievОценок пока нет

- Experiment 3: Decision Making and Looping Operation Using 8086Документ5 страницExperiment 3: Decision Making and Looping Operation Using 8086praveenembd1Оценок пока нет

- Examen MesaДокумент14 страницExamen MesaFernando QuirogaОценок пока нет

- ARM Instruction Set - Data Processing - IIДокумент13 страницARM Instruction Set - Data Processing - IIAniket SubudhiОценок пока нет

- Interfacing 86Документ3 страницыInterfacing 86Malgireddy RavireddyОценок пока нет

- TB Elevator0Документ2 страницыTB Elevator0Jimy Yan LinОценок пока нет

- A.C.Lab5 CerlatPavel FAF-192Документ9 страницA.C.Lab5 CerlatPavel FAF-192Pavlic CerlatОценок пока нет

- Chapter 3: Arm Instruction Set: (Architecture Version: Armv4T)Документ32 страницыChapter 3: Arm Instruction Set: (Architecture Version: Armv4T)sunilbhimuОценок пока нет

- PLC 877Документ13 страницPLC 877Irma Leticia Paniagua VasquezОценок пока нет

- Ex FansДокумент7 страницEx FansMohamad SalimОценок пока нет

- Either Source or Destination Is One Of: CPU RegisterДокумент81 страницаEither Source or Destination Is One Of: CPU Registersaigdv1978Оценок пока нет

- 16 Bit Alu in VHDLДокумент7 страниц16 Bit Alu in VHDLpuppyrОценок пока нет

- DigitalLogic - FlipFlop CircuitДокумент30 страницDigitalLogic - FlipFlop CircuitNasa McAikenОценок пока нет

- Microcontrollers: Dr. Jafar JalladДокумент83 страницыMicrocontrollers: Dr. Jafar JalladGreen HeartОценок пока нет

- Tetra Detector PDFДокумент12 страницTetra Detector PDFabacadabra3100% (1)

- LDICA Unit 5 PDFДокумент80 страницLDICA Unit 5 PDFbhanumanuОценок пока нет

- ME3241E Cheat SheetДокумент2 страницыME3241E Cheat SheetLaw Zhan HongОценок пока нет

- CH03 Solution PDFДокумент16 страницCH03 Solution PDF孫協廷Оценок пока нет

- Arm and Thumb Instruction SetДокумент36 страницArm and Thumb Instruction SetTanay DubeyОценок пока нет

- Experiment No.: 3: PC With Atmel StudioДокумент11 страницExperiment No.: 3: PC With Atmel StudioDhrumil ManiyarОценок пока нет

- Bai3 ASMДокумент10 страницBai3 ASMVu Van KhanhОценок пока нет

- Pep-8 ISA PDFДокумент1 страницаPep-8 ISA PDFGeo CasianОценок пока нет

- Ch5 - 1 Latches and Flip FlopsДокумент50 страницCh5 - 1 Latches and Flip FlopsMariam ElnourОценок пока нет

- St7 Microcontroller TrainingДокумент19 страницSt7 Microcontroller TrainingsafasabaОценок пока нет

- 3 Arithmetic and Logic v22Документ20 страниц3 Arithmetic and Logic v22vokhacnam2k1Оценок пока нет

- Phome: Ppick: Pers PersДокумент2 страницыPhome: Ppick: Pers Pers孛儿只斤阿斯根夫Оценок пока нет

- TarefasДокумент17 страницTarefasEvandro Fernandes LedemaОценок пока нет

- Vlsi Iiest SBДокумент45 страницVlsi Iiest SBUshaRaniDashОценок пока нет

- Fcode 54 en El SytucДокумент2 страницыFcode 54 en El SytucAga MenonОценок пока нет

- Sequential Logic Latches & Flip-Flops: Memory Elements Pulse-Triggered LatchДокумент33 страницыSequential Logic Latches & Flip-Flops: Memory Elements Pulse-Triggered LatchRAHUL KUMAR RОценок пока нет

- 04 2StartingToProgram IntroductiontoAssemДокумент24 страницы04 2StartingToProgram IntroductiontoAssemabdullah1998128Оценок пока нет

- 7 PIC18 InstructionSet Assembly Machine PDFДокумент15 страниц7 PIC18 InstructionSet Assembly Machine PDFbaseer khanОценок пока нет

- 3 Pic16f877 InstructДокумент8 страниц3 Pic16f877 InstructAdel DouDouОценок пока нет

- Flipflop TablesДокумент6 страницFlipflop TablesNandini JayakumarОценок пока нет

- Mupee 5Документ20 страницMupee 5api-3724082Оценок пока нет

- Note 4 Transmission Lines (Bounce Diagram)Документ31 страницаNote 4 Transmission Lines (Bounce Diagram)Charan Macharla'sОценок пока нет

- 凱內WZДокумент8 страниц凱內WZrrrrОценок пока нет

- Ups - ST002919Документ68 страницUps - ST002919des_troyer_84Оценок пока нет

- Ucm6500 Buyersguide SpanishДокумент110 страницUcm6500 Buyersguide Spanishdes_troyer_84Оценок пока нет

- Ucm6xxx Sip Trunk GuideДокумент24 страницыUcm6xxx Sip Trunk Guidedes_troyer_84Оценок пока нет

- New Product Dvg-1120S: D-Link Voip GatewayДокумент1 страницаNew Product Dvg-1120S: D-Link Voip Gatewaydes_troyer_84Оценок пока нет

- GXV3240 - GXV3240 Quick User GuideДокумент13 страницGXV3240 - GXV3240 Quick User Guidedes_troyer_84Оценок пока нет

- IT Policy: Information Technology ManualsДокумент18 страницIT Policy: Information Technology Manualsdes_troyer_84100% (1)

- GXV3240 - GXV3240 Quick User GuideДокумент6 страницGXV3240 - GXV3240 Quick User Guidedes_troyer_84Оценок пока нет

- Guia Ims Kamailio LoadmultiplierДокумент14 страницGuia Ims Kamailio Loadmultiplierdes_troyer_84Оценок пока нет

- Yeastar TA Series Analog VoIP Gateway Datasheet enДокумент2 страницыYeastar TA Series Analog VoIP Gateway Datasheet endes_troyer_84Оценок пока нет

- Vulnerability CatalogДокумент102 страницыVulnerability Catalogdes_troyer_84Оценок пока нет

- 04 AbstractДокумент1 страница04 Abstractdes_troyer_84Оценок пока нет

- Memory Management Unit 5Документ58 страницMemory Management Unit 5Nishant NalawadeОценок пока нет

- mp5w - Manual - English AUTONICS MP5W PDFДокумент4 страницыmp5w - Manual - English AUTONICS MP5W PDFAngel Eduardo PeñaОценок пока нет

- FLAC2 DДокумент180 страницFLAC2 DMohamed A. El-BadawiОценок пока нет

- HMMERДокумент5 страницHMMERemma698Оценок пока нет

- Project On AgricultureДокумент20 страницProject On AgricultureRaghupal reddy GangulaОценок пока нет

- DatasheetDurem114 tcm40-2080Документ1 страницаDatasheetDurem114 tcm40-2080Gildardo FigueroaОценок пока нет

- Trinity College Dublin ThesisДокумент6 страницTrinity College Dublin Thesisafcmrdbef100% (2)

- Zella Pro Tech Specs - March 2021Документ16 страницZella Pro Tech Specs - March 2021Yusuf ShunanОценок пока нет

- Graylog Extractors RsyslogДокумент3 страницыGraylog Extractors RsyslogAndrey TОценок пока нет

- Mad 1-2-3 PMДокумент33 страницыMad 1-2-3 PMK.B.SОценок пока нет

- Tomorrow'S Technology For Today'S Security: Product HighlightsДокумент2 страницыTomorrow'S Technology For Today'S Security: Product HighlightsBanu AtamОценок пока нет

- White Paper - DataOps Is NOT DevOps For DataДокумент15 страницWhite Paper - DataOps Is NOT DevOps For DataRezaОценок пока нет

- Job Description PharmacistДокумент4 страницыJob Description PharmacistAbdiОценок пока нет

- ANSI/TIA/EIA-568-B.3: Optical Fiber Cabling and Components: 1st Level BackboneДокумент2 страницыANSI/TIA/EIA-568-B.3: Optical Fiber Cabling and Components: 1st Level Backboneosgarsoto100% (1)

- BSNL VMC AN1020-21 (Detailed Visual Guide)Документ14 страницBSNL VMC AN1020-21 (Detailed Visual Guide)Nagaraju Gunturu100% (1)

- All DrawingДокумент505 страницAll DrawingMuyizere FabriceОценок пока нет

- 06-E-SAT Including Data Management and Use of ResultsДокумент53 страницы06-E-SAT Including Data Management and Use of ResultsRgen Al VillОценок пока нет

- Let's Learn About SpreadsheetsДокумент48 страницLet's Learn About SpreadsheetsHiltanasОценок пока нет

- TRADOC Pamphlet 525-92-1Документ38 страницTRADOC Pamphlet 525-92-1Ricardo Alfredo Martinez CambaОценок пока нет

- Variable DC Power Supply Project ReportДокумент10 страницVariable DC Power Supply Project ReportEngr. Zeeshan mohsin73% (22)

- Xillybus Product BriefДокумент2 страницыXillybus Product Briefraiatea2Оценок пока нет

- Sage One Accounting Getting Started Guide 1Документ82 страницыSage One Accounting Getting Started Guide 1romeoОценок пока нет

- Cinimamachine TuteДокумент7 страницCinimamachine TutegregoryОценок пока нет

- Mabl Worksheet Starting and Scaling Functional Automated TestingДокумент23 страницыMabl Worksheet Starting and Scaling Functional Automated TestingktbalajiОценок пока нет

- Integral Cycle Speed Control of Single Phase Induction Motor Using At89c51 Microcontroller PDFДокумент47 страницIntegral Cycle Speed Control of Single Phase Induction Motor Using At89c51 Microcontroller PDFrijilpoothadiОценок пока нет

- Material de Referencia - IT4IT™ Foundation Study GuideДокумент176 страницMaterial de Referencia - IT4IT™ Foundation Study Guidedagomez2013Оценок пока нет

- cs2201 Unit1 Notes PDFДокумент16 страницcs2201 Unit1 Notes PDFBal BolakaОценок пока нет

- L5 L6 L7 L8 L9 - Project ManagementДокумент94 страницыL5 L6 L7 L8 L9 - Project Managementapi-19922408Оценок пока нет

- WH1602W Tmi JTДокумент29 страницWH1602W Tmi JTscribe72Оценок пока нет

- 2019 - 2 - Advertisement No 3-2019 (Various Posts)Документ9 страниц2019 - 2 - Advertisement No 3-2019 (Various Posts)Shubham GautamОценок пока нет