Академический Документы

Профессиональный Документы

Культура Документы

Informe 2 Digitales FINAL

Загружено:

Juan Miguel DiazИсходное описание:

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Informe 2 Digitales FINAL

Загружено:

Juan Miguel DiazАвторское право:

Доступные форматы

> Laboratorio N2: Diseo de Circuitos Logicos Combinacionales, Grupo: 01 Subgrupo: 02 Puesto 3 1

Informe N2

Diseo de Circuitos Logicos Combinacionales

Subgrupo: 02 Puesto: 3

Juan Miguel Daz Dussn

20152142266

Andrs Felipe Hinestroza Garca

20152140727

obtener un circuito combinacional con el menor numero de

ResumenEn esta prctica, se realiza el diseo de un circuito integrados posibles mediante los diferentes mtodos de

lgico combinacional que suma dos nmeros de dos bits cada uno simplificacin de funciones booleanas, reconociendo las

y su salida se obtenga en binario natural complementado, distintas ventajas de lograr estos diseos como ahorrar espacio

comprobando una de las aplicaciones bsicas de los circuitos

de trabajo y reducir los costos de implementacin a la hora de

usando compuertas, implementando un diseo y verificando su

funcionamiento realizar el diseo ya simplificado.

Palabras clavesDiseo, Circuito lgico combinacional, III. MARCO TERICO

binario naturla complementado. Los circuitos lgicos combinacionales, estan formados por

funciones lgicas elementales como son (AND, OR, NOT,

I. OBJETIVOS

NAND, NOR, XOR) y como su nombre lo sugiere es un

Objetivo General: circuito cuya salida depende nicamente de una combinacin

Disear un circuito lgico combinacional usando del estado de sus entradas, como se podr observar, en estos

nicamente compuertas, las cuales constituyen la base circuitos no se almacena o se guarda ningna combinacin de

del diseo lgico. Esto permite adquirir el suficiente entrada para su uso posterior con otras combinaciones, es decir,

nivel prctico para desenvolverse eficazmente en no tienen memoria, todas las compuertas estn conectadas a las

cuestiones fundamentales como el anlisis de circuitos entradas del sistema y esta .

digitales, la simplificacin de funciones lgicas y

diseo

Estos circuitos representan una funcin booleana obtenida de

un problema inicial, el cual describir una tabla de verdad, en

Objetivos Especificos:

cuyas salidas que depender y variar directamente de los

Comprobar el funcionamiento del circuito lgico

estados de la entrada

combinacional aplicando todas las combinaciones

necesarias.

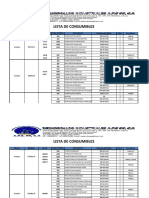

IV.MATERIALES UTILIZADOS.

Implementar un Circuito Lgico Combinacional,

segn la gua de laboratorio utilizando el menor 3 Resistencias 330.

numero de integrados. Jumpers.

Cables para conexin.

Comprobar la implementacin de circuitos cuya

3 Diodos LED color rojo.

funcin booleana es obtenida mediante el uso del

2 C.I. (74LS00).

mtodo de mapa de karnaugh para la simplificacin

1 C.I. (74LS08).

del problema previo descrito en la gua de 1 C.I. (74LS32).

laboratorio. 1 C.I. (74LS04).

1 C.I. (74LS86).

II. JUSTIFICACIN V. DESARROLLO PRCTICO.

Los circuitos lgicos combinacionales, son la base del diseo Para esta pratica se realiza el montaje de un circuito lgico

en electrnica digital, a fin de que el estudiante adquiera el combinacional, cuyo objetivo era mostrar en su salida la suma

conocimiento prctico y mejore su nivel en el diseo de este de dos nmeros binarios de 2 bits cada uno ingresados en la

tipo de circuitos, se plantea esta prctica con fin de aplicar los entrada, basados en la salida para nuestro caso binario natural

conocimientos adquiridos en las horas tericas, buscando complementado.

> Laboratorio N2: Diseo de Circuitos Logicos Combinacionales, Grupo: 01 Subgrupo: 02 Puesto 3 2

() ()

Previamente se realiz el diseo mediante simplificacin por =

mapas Karnaugh y procedimos a simplificar ms la expresin

mediante los diferentes teoremas del algebra booleana con los Utilizando los valores medidos.

cuales logramos un menor nmero de circuitos integrados a Siendo los resultados:

usar, siendo el resultado de 6 Circuitos Integrados.

I(Bit3) =7.9mA

El diagrama del circuito fue el siguiente: I(Bit2) =8.09mA

I(Bit1) =8.08mA

Como se puede observer, para esta configuracin de

visualizador, la corriente en las salidas esta dentro o muy

cercana al perfil de corriente que da el fabricante, por lo cual

no se est forzando a la compuerta, esto nos da a reconocer

una ventaja del diseo con salidas complementadas, pues para

conectar a cargas que demandan ms corriente, es una buena

alternativa.

VI.CONCLUSIONES.

La reduccin de una expresin booleana por el

mapa de karnaugh no siempre va a ser la ms

simplificada que asegura est mtodo, no siempre

utiliza el menor nmero de compuertas posibles.

La destreza en el algebra booleana nos permite

analizar una expresion booleana y modificarla

aprovechando diferentes teoremas y operaciones

Para los visualizadores se utiliz diodos LED rojos con una de otras compuertas, reduciendo el numero de

tensin promedio de 2.0V y corriente 8mA, la resistencia compuertas y por ende integrados necesarios para

calculada de 330 . su implementacin adecuada.

Durante la prctica se comprueba la tabla de verdad del Las ventajas de usar el menor numero de

circuito implementado, verificando el correcto funcionamiento integrados son bastante reconocibles, entre ellas

para todas las combinaciones de entrada, y observando los encontramos, mayor respeto a los perfiles de

niveles de tensin en la salida adems del correcto encendido tensin y corriente dados por el fabricante que para

de los LEDs que encienden cuando la salida es un bajo (segn nuestro caso trabajamos con la subfamilia 74LS de

lo estipulado en la gua de laboratorio). la familia TTL, menor gasto econmico, menor

Una vez comprobado el funciomiento del circuito, se consumo de potencia debido a que se alimentaran

procedi a mirar los niveles de tensin en los LEDs cuando menos circuitos integrados y una ventaja muy a

estaban encendidos y apagados en las distintas salidas con todas nivel de prctica, mayor facilidad en la

las combinanciones, y por ultimo se miden los valores de las implementacin del circuito,

resistencias para el posterior anlisis y bsqueda de margen de Una de las ventajas de disear con salidas

error. complementadas, claramente se da en que para

Los resultados se las prcticas se condensan en el documento usar visualizadores LEDS estas salidas mostraran

posterior a la prctica entregado a la monitora. el resultado de la salida respeto a la entrada sin

exigir una corriente muy grande que sobrepase los

perfiles de tensin del fabricante y por ende no

IV. DESARROLLO ANALITICO.

forzaremos a las compuertas.

Por qu cuando el LED est apagado, el Voltaje del LED no

es igual a Vcc?

Debido a la configuracin usada para el visualizador, como

estamos diseando con salidas complementadas, el LED no se VII.REFERENCIAS

enciende cuando la salida de la compuerta 74LS est en alto

[1] TOCCI, Ronald J. Sistemas digitales, principios y

(VOH=2.7V), resulta que si se observa esta tensin es aplicaciones/por Ronald J. Tocci.Dcima Edicin 1985.

comparable con VCC, por lo cual la tensin que caera en el [2] WAKERLY, John F. Diseo digital: principios y prcticas.

LED y la corriente que fluir en la malla del visualizador ser Pearson educacin, 2001

muy poco, en otras palabras, el LED si est polarizad o en

directa, pero la potencia necesaria para encender el LED NO

es suficiente.

Para la obtencin de corrientes en Bajo, se realiza la malla de

salida:

Вам также может понравиться

- Informe Digital I - Practica 1Документ6 страницInforme Digital I - Practica 1Raúl A.Оценок пока нет

- Aplicación de Circuitos Digitales para Manejo de Código BCDДокумент3 страницыAplicación de Circuitos Digitales para Manejo de Código BCDLuisAlbertoОценок пока нет

- Informe 2Документ2 страницыInforme 2HECTOR JULIAN SANTACRUZ GUTIERREZОценок пока нет

- Laboratorio Compuertas Digitales (1044)Документ3 страницыLaboratorio Compuertas Digitales (1044)Vanessa NavarroОценок пока нет

- Ramirez Brandon Lagos Andrew SD Inf P6 GR7-2Документ5 страницRamirez Brandon Lagos Andrew SD Inf P6 GR7-2brandon ramirezОценок пока нет

- Preinforme Laboratorio Electronica DigitalДокумент4 страницыPreinforme Laboratorio Electronica DigitalErick Pozo ClarosОценок пока нет

- Circuito de Un SemaforoДокумент4 страницыCircuito de Un SemaforoCARLOS FELIPE ROQUEMEОценок пока нет

- Informe #4Документ2 страницыInforme #4Duo Doble AОценок пока нет

- InformeДокумент10 страницInformeLuis DiazОценок пока нет

- Guia de Autoaprendizaje Digital I Tema1Документ13 страницGuia de Autoaprendizaje Digital I Tema1Steveen CerdaОценок пока нет

- Simulacion de Descripciones en VHDLДокумент6 страницSimulacion de Descripciones en VHDLNico BernalОценок пока нет

- Informe Taller 1Документ3 страницыInforme Taller 1Camila Diaz BОценок пока нет

- Trabajo FinalДокумент57 страницTrabajo FinalFranks Guevara0% (1)

- Informe 2 DigitalДокумент2 страницыInforme 2 DigitalCarlos CastroОценок пока нет

- Informe 4Документ5 страницInforme 4Nosoy David CastrariasОценок пока нет

- Guia de Laboratorio 5Документ2 страницыGuia de Laboratorio 5VICTOR HUGO CHOQUE CRUZОценок пока нет

- Actividad 2. Circuitos CombinacionalesДокумент4 страницыActividad 2. Circuitos CombinacionalesJuan MartinezОценок пока нет

- Actividad 2. Circuitos CombinacionalesДокумент4 страницыActividad 2. Circuitos CombinacionalesJuan MartinezОценок пока нет

- Laboratorio 5 AA.Документ4 страницыLaboratorio 5 AA.MARIA FERNANDA URREA RODRIGUEZОценок пока нет

- Lógica CombinacionalДокумент15 страницLógica CombinacionalAlexanderJ.RojasHerreraОценок пока нет

- Practica3 - Liliana Andrea LopezДокумент3 страницыPractica3 - Liliana Andrea LopezJuan carlos Garacia mazueraОценок пока нет

- LABORATORIO #4 JGДокумент3 страницыLABORATORIO #4 JGJosefath GonzalezОценок пока нет

- 2023dijital Lab#2Документ6 страниц2023dijital Lab#2Stalin GuzmánОценок пока нет

- Laboratorio 6 - Electronica DДокумент3 страницыLaboratorio 6 - Electronica Drringo27Оценок пока нет

- Informe 1Документ6 страницInforme 1Ricardo FloresОценок пока нет

- DigitalДокумент7 страницDigitalStalin GuzmánОценок пока нет

- Informe - 4 Tecer CoryyeДокумент5 страницInforme - 4 Tecer CoryyeNico BernalОценок пока нет

- Reporte de Practica - Electronica DigitalДокумент8 страницReporte de Practica - Electronica DigitalAlexis OrozcoОценок пока нет

- Practicas Eléctrica DigitalДокумент21 страницаPracticas Eléctrica DigitalCarlos Alberto Pech PerezОценок пока нет

- Cuarto Informe MicrosДокумент4 страницыCuarto Informe Microsest.laurava.castel3Оценок пока нет

- Formato DigitalesДокумент2 страницыFormato DigitalesramirezcustodearturoОценок пока нет

- Practicas Unidad 2Документ18 страницPracticas Unidad 2Alejandro Antonio Higuera NayaresОценок пока нет

- Laboratorio de Adicionadores BinariosДокумент5 страницLaboratorio de Adicionadores Binariospc hoyОценок пока нет

- U04 - Guía Del Estudiante FSD 1Документ8 страницU04 - Guía Del Estudiante FSD 1Washington CeliОценок пока нет

- Informe 5Документ2 страницыInforme 5patuchinmhОценок пока нет

- Reporte de Practica 01Документ3 страницыReporte de Practica 01JEAN ANTHONY MARTINEZ SERRANOОценок пока нет

- Informe de Laboratorio Electronica DigitalДокумент7 страницInforme de Laboratorio Electronica Digitalsebastian bustamanteОценок пока нет

- Secuencia Didactica SD 2018Документ12 страницSecuencia Didactica SD 2018amlaiaОценок пока нет

- Circuitos CombinacionalesДокумент41 страницаCircuitos CombinacionalesHoracio Pérez100% (1)

- Laboratorio 2Документ2 страницыLaboratorio 2Andres TasconОценок пока нет

- Diseño Multietapa ElectronicaДокумент9 страницDiseño Multietapa ElectronicaYulii Carreño MartinezОценок пока нет

- Practica PWMДокумент3 страницыPractica PWMGustavo AndradeОценок пока нет

- Ieee Simulador ElectroneumaticaДокумент2 страницыIeee Simulador ElectroneumaticaEdmond AndresОценок пока нет

- Informe - Multiplicador 2 x2Документ4 страницыInforme - Multiplicador 2 x2Chistian SanchezОценок пока нет

- Informe Previo 3 Marcelo Azpilcueta RubinaДокумент4 страницыInforme Previo 3 Marcelo Azpilcueta RubinaMarcelo Azpilcueta RubinaОценок пока нет

- De GR5 Alejandro Chicaiza Práctica#11 InformeДокумент2 страницыDe GR5 Alejandro Chicaiza Práctica#11 InformeAlejandro Sebastian Chicaiza TipanОценок пока нет

- Modulos CombinacionalesДокумент6 страницModulos CombinacionalesRolando Choque CahuanaОценок пока нет

- Informe Practica 4Документ4 страницыInforme Practica 4jhojan santiago sanchez morenoОценок пока нет

- Info Lab3 DigitaleslДокумент7 страницInfo Lab3 Digitalesljulian hincapieОценок пока нет

- Actividad 2 Carga Paralela EDGAR VEGA ARAGONДокумент7 страницActividad 2 Carga Paralela EDGAR VEGA ARAGONVega EdgarОценок пока нет

- Espe Electronica ELEE 14006 CIRCUITOS-DIGITALESДокумент2 страницыEspe Electronica ELEE 14006 CIRCUITOS-DIGITALESLindsay RangelОценок пока нет

- Practica 5Документ11 страницPractica 5kuborusОценок пока нет

- Laboratorio Virtual Nº2 - Mallas y Montaje de Circuito en ProtoboardДокумент14 страницLaboratorio Virtual Nº2 - Mallas y Montaje de Circuito en ProtoboardDANIEL DAVID LOSADA TELLOОценок пока нет

- Paper - IEEE Practica 3Документ6 страницPaper - IEEE Practica 3Aleja OrtegaОценок пока нет

- Informe 2 SDEДокумент7 страницInforme 2 SDELeonardo BenavidesОценок пока нет

- Informe 555Документ5 страницInforme 555JOSE MANUEL BENAVIDES GUTIERREZОценок пока нет

- Practicas DigitalesДокумент23 страницыPracticas DigitalesdavidОценок пока нет

- Actividades de Aprendizaje Electrónica DigitalДокумент16 страницActividades de Aprendizaje Electrónica DigitalCarlos RodriguezОценок пока нет

- Control neuronal y difuso para sistemas fotovoltaicosОт EverandControl neuronal y difuso para sistemas fotovoltaicosОценок пока нет

- Desarrollo de Las Escuelas Sociologicas..Документ4 страницыDesarrollo de Las Escuelas Sociologicas..nelcarlis67% (3)

- Contenido Curso Trabajo en Altura PDFДокумент2 страницыContenido Curso Trabajo en Altura PDFZambrano ArteagaОценок пока нет

- Caso de EstudioДокумент10 страницCaso de EstudioAdriana SalazarОценок пока нет

- Averiguar Cual Es El Puesto Que Se Le Dará Al Sujeto en La Compañía Mediante Su DesempeñoДокумент25 страницAveriguar Cual Es El Puesto Que Se Le Dará Al Sujeto en La Compañía Mediante Su DesempeñoGerfisReneeОценок пока нет

- ExposixionДокумент2 страницыExposixionXiomi GomezОценок пока нет

- Evaluacion Del Impacto de Un Plan de Cuidados en eДокумент11 страницEvaluacion Del Impacto de Un Plan de Cuidados en eErika CidОценок пока нет

- "Encuesta Sobre El Proceso EnfermeroДокумент11 страниц"Encuesta Sobre El Proceso EnfermeroMiryam PHОценок пока нет

- Nia 300Документ37 страницNia 300Andres Felipe RodriguezОценок пока нет

- Alegatos Tribunal Juan PabloДокумент9 страницAlegatos Tribunal Juan PabloCandice Marian VelezОценок пока нет

- s500 LincolnДокумент47 страницs500 Lincolnjorge varОценок пока нет

- Actividad de Aprendizaje 11 Evidencia 4 Seccion Virtual Indicadores de GestionДокумент5 страницActividad de Aprendizaje 11 Evidencia 4 Seccion Virtual Indicadores de GestionLUCELYS LEIVA GARCIAОценок пока нет

- Sinamic Step 7Документ111 страницSinamic Step 7Victor Manuel Aragon Torrado1Оценок пока нет

- Externalidades y Bienes PúblicosДокумент18 страницExternalidades y Bienes PúblicosdavidОценок пока нет

- Lista de Consumibles Equipos Pesados Por Modelos Terex Cat Komatsu Bomag VeermerДокумент25 страницLista de Consumibles Equipos Pesados Por Modelos Terex Cat Komatsu Bomag VeermerChristian Vásquez BasilioОценок пока нет

- Analisis MulticriterioДокумент22 страницыAnalisis MulticriterioLeón de AguaОценок пока нет

- ADMIN 04 Procesador TextosДокумент28 страницADMIN 04 Procesador TextosAntoito22Оценок пока нет

- Listado de Herramientas-Equipos-Consumibles San Carlos U7Документ16 страницListado de Herramientas-Equipos-Consumibles San Carlos U7AAОценок пока нет

- Fis TesisДокумент26 страницFis Tesisgear123_123Оценок пока нет

- Banco de PreguntasДокумент8 страницBanco de PreguntasNano LopezОценок пока нет

- Características Principales Geográficas de Arabia SauditaДокумент1 страницаCaracterísticas Principales Geográficas de Arabia SauditaLeticia Martinez100% (1)

- Last2 U1 A1 JeemДокумент7 страницLast2 U1 A1 JeemAnonymous son4o6bPОценок пока нет

- Temas - Finanzas GlobalesДокумент270 страницTemas - Finanzas GlobalesClaus KukutschkaОценок пока нет

- 3 Politica AnticorrupciónДокумент5 страниц3 Politica AnticorrupciónOmar Ricardo Rocha CdlmОценок пока нет

- Asignacion Final Semana 4 SergioДокумент7 страницAsignacion Final Semana 4 SergioSERGIO RICARDO MENDOZA ALFAROОценок пока нет

- Qué Crees Que Es El Aprendizaje Basado en ProyectosДокумент2 страницыQué Crees Que Es El Aprendizaje Basado en ProyectosKarem Jhael Lopez OrtizОценок пока нет

- Clase 7Документ8 страницClase 7paula CartagenaОценок пока нет

- Subtema 1.1 NORMAS (ANSI)Документ2 страницыSubtema 1.1 NORMAS (ANSI)Carlos RasgadoОценок пока нет

- Manual de Especificaciones TécnicasДокумент136 страницManual de Especificaciones Técnicasdcortes07Оценок пока нет

- Equipos para El Manejo de MaterialesДокумент9 страницEquipos para El Manejo de Materialesluisnoh100% (1)

- Mazda cx9Документ2 страницыMazda cx9muegano4Оценок пока нет