Академический Документы

Профессиональный Документы

Культура Документы

Lab07 Flip Flops

Загружено:

Alejandro Martin Leon CernaАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Lab07 Flip Flops

Загружено:

Alejandro Martin Leon CernaАвторское право:

Доступные форматы

ELECTRNICA DIGITAL I

PRCTICA DE LABORATORIO N 7

LATCHES Y FLIP - FLOPS

Ing. Alejandro Martin Len Cerna

ELECTRNICA DIGITAL I 1

PRCTICA DE LABORATORIO N 7

I. TITULO: LATCHES Y FLIP - FLOPS

II. OBJETIVOS:

Utilizar puertas lgicas para construir latches bsicos.

Conocer las diferencias entre un latch y un flip-flop.

Explicar en qu se diferencian los flip-flops S-R, J-K y D.

Comprender el significado de: Disparado por flanco, establecer y reestablecer flip-

flops, as como tambin retardo de propagacin y tiempo de establecimiento (setup

time).

Conocer las diversas aplicaciones que se pueden implementar con flip-flops.

Utilizar la herramienta ISIS Proteus para la simulacin de circuitos digitales

utilizando flip-flops.

III. MATERIALES Y EQUIPOS / INSTRUMENTOS:

MATERIALES: EQUIPOS / INSTRUMENTOS

C.I. (Circuitos Integrados): Fuente de alimentacin (+5Vcc)

(2) 74LS74Flip - Flop tipo D con Set y Clear. Fuente de 5V/3.3V para Protoboard (mas

(2) 74LS112 Flip - Flop tipo K con Set y Clear. cable USB)

Todas las dems compuertas lgicas usadas

anteriormente. (Datasheet de cada C.I.)

(2) Capacitores electrolticos: 1uF, 10uF, 100uF, Multmetro / Generador de Seales

4.7uF, 4.7nF Osciloscopio Tektronix

(2) Capacitores cermicos: 4.7nF

(10) Resistencias: 220 / 330 de 1/4W o 1/2W

(2) Resistencias: 1k, 10k, 47.5 k, 47, 128

(1) Potencimetro: 10k

(1) Protoboard

(2) Puntas para fuente de alimentacin

(2) Puntas para osciloscopio

(10) Diodos led (de color rojo u otros)

(10) Pulsadores de dos terminales

Cables jumper (M-M), cablecillos (UTP)

INGENIERA ELECTRNICA UPAO 2017 - 20

ELECTRNICA DIGITAL I 2

IV. PROCEDIMIENTO:

4.1. Implementar el circuito de la figura n1 en la potoboard, conocido como latch de

compuertas NAND o simplemente latch. Los flip-flops ms bsicos que existen

son de 2 compuertas NAND y NOR. Para este caso, las dos compuertas NAND estn

retroalimentadas en forma transversal. Las salidas de las compuertas identificadas

como

respectivamente, son las salidas del latch. Bajo condiciones normales

una salida ser el inverso de la otra. Existe dos entradas para el latch: la entrada SET

es la que estable Q en el estado 1, y la entrada RESET es la que restablece Q al

estado 0. Por lo general las entradas SET y RESET permanecen en el estado ALTO,

y una de ellas cambiara a BAJO mediante un pulso, cada vez que se quiera cambiar

el estado de las salidas del latch.

Figura n1: Latch de compuertas NAND.

Una vez implementado el circuito, visualizar las salidas

para cada

combinacin de entradas SET y RESET del latch, resuma y sintetice la operacin

descrita colocando sus resultados de manera conveniente en una tabla de funciones.

De la misma manera realizar la simulacin del circuito en ISIS Proteus y contrastar

sus resultados con la simulacin.

4.2. Implementar el circuito de la figura n2 en la potoboard, conocido como latch de

compuertas NOR. El latch de compuertas NOR opera exactamente de la misma

forma que el latch NAND, solo que las entradas SET y RESET son activas en ALTO,

en vez de activas en BAJO, y el estado detenido normal es SET = RESET = 0. La

salida Q cambiara a nivel ALTO mediante un pulso ALTO en la entrada SET, y

cambiara a BAJO mediante un pulso ALTO en la entrada RESET.

Realice el anlisis de la operacin del latch NOR exactamente de la misma forma

que lo hizo para el latch NAND, visualice y coloque sus resultados en su respectiva

tabla de funciones.

INGENIERA ELECTRNICA UPAO 2017 - 20

ELECTRNICA DIGITAL I 3

Figura n2: Latch de compuertas NOR.

De la misma manera realizar la simulacin del circuito en ISIS Proteus y contrastar

sus resultados con la simulacin.

4.3. Los flip-flop mas usas en los circuitos digitales son los del tipo J-K y D, por su

versatilidad y su gran variedad de funciones en su utilizacin. Estos flip-flop

presentan entradas de control denominadas J, K y D, a estas entradas se las conoce

tambin como entradas sncronas ya que su efecto sobre las salidas del flip-flop

estn sincronizadas con una entrada de reloj denominada CLOCK (CLK). Las

entradas de control sncronas deben usarse en conjunto con una seal de reloj para

disparar el FF (Flip-Flop).

La mayora de los FFs sincronizadas por reloj tienen tambin una o ms entradas

asncronas que operan de manera independiente a las entradas sncronas y a la

entrada de reloj. Estas entradas asncronas pueden usarse para establecer el FF al

estado 1 (SET) o borrar (RESET) el FF al estado 0 en cualquier momento, sin

importar las condiciones de las otras entradas. Dicho de otra manera, las entradas

asncronas, son entradas predominantes, las cuales pueden usarse para ignorar todas

las dems entradas y colocar el FF en uno u otro estado.

Implementar el circuito de la figura n3 en la potoboard. Este circuito muestra un

flip-flop J-K con dos entradas asncronas designadas como

, que

son entradas activas en nivel BAJO, como lo indican las burbujas en el smbolo del

FF. Realice las pruebas, examine los diversos casos y verifique el funcionamiento

del FF para cada una de las iteraciones, tanto en las entradas sncronas (J, K) y en las

entradas asncronas ( ) en los flancos activos del CLOCK.

INGENIERA ELECTRNICA UPAO 2017 - 20

ELECTRNICA DIGITAL I 4

Figura n3: Flip-Flop sincronizado por reloj en J-K con entradas asncronas.

Coloque los resultados de la salida Q para cada iteracin segn la siguiente tabla de

funciones.

De la misma manera realizar la simulacin del circuito en ISIS Proteus y contrastar

sus resultados con la simulacin utilizando el osciloscopio para observar los cambios

de las salidas de FF al variar las entras sncronas y asncronas del FF para cada flanco

de bajada del reloj.

4.4. Ahora modifique el circuito de la figura n3, usando como nueva entrada K la

negacin de la entrada J. Cmo se comportar ahora las salidas del FF haciendo

esta modificacin?

Figura n4: Flip-Flop sincronizado por reloj en J-K con entradas asncronas (modificado).

INGENIERA ELECTRNICA UPAO 2017 - 20

ELECTRNICA DIGITAL I 5

4.5. Implementar el circuito de la figura n5 en la potoboard, conocido como Flip-Flop

sincronizado por reloj del tipo D. A diferencia del flip-flop J-K y S-R este solo

presenta una entrada de control sncrona denominada D la cual significa datos.

La operacin de este flip-flop es muy simple: Q cambiara al mismo estado que est

presente en la entrada D, cuando ocurra un flanco de subida en el CLOCK. En otras

palabras, el nivel presente en D se almacenar en el flip-flop, en el instante en el que

ocurra una transicin de pendiente positiva del Reloj.

Figura n5: Flip-Flop sincronizado por reloj en D con entradas asncronas.

Coloque los resultados de la salida Q para cada iteracin segn la siguiente tabla de

funciones.

De la misma manera realizar la simulacin del circuito en ISIS Proteus y contrastar

sus resultados con la simulacin utilizando el osciloscopio para observar los cambios

de las salidas de FF al variar la entra sncrona D y asncronas del FF para cada flanco

de subida del reloj. Responda a la siguiente pregunta: Tendrn el mismo

comportamiento el circuito de Figura n4 con el circuito de la Figura n5? Justifique

su respuesta.

INGENIERA ELECTRNICA UPAO 2017 - 20

ELECTRNICA DIGITAL I 6

4.6. Implementar el circuito de la figura n6 en la potoboard, conocido como Registro

de desplazamiento para la transferencia de datos en serie.

Figura n6: Registro de desplazamiento de 4 bits en serie con Flip-Flops del tipo D

Una vez implementado el circuito, examine su comportamiento y explique la

transferencia de datos en serie, mediante el registro de desplazamiento de 4 bits.

Construya una tabla, la cual muestre como cambian los estados de cada FF (Salidas:

Q0, Q1, Q2, Q3) a medida que se aplican los pulsos de desplazamiento mediante el

CLOCK.

4.7. Simular el circuito de la figura n7 en el software ISIS Proteus, conocido como

Registro de desplazamiento para la transferencia de datos en paralelo.

Figura n7: Registro de desplazamiento de 3 bits en paralelo con Flip-Flops del tipo D

Una vez implementado el circuito, examine su comportamiento y explique la

transferencia de datos en paralelo, mediante el registro de desplazamiento de 3 bits.

Construya una tabla, la cual muestre como cambian los estados de cada FF (Salidas:

Q0, Q1, Q2) a medida que se aplican los pulsos de desplazamiento mediante el

CLOCK.

INGENIERA ELECTRNICA UPAO 2017 - 20

ELECTRNICA DIGITAL I 7

4.8. Implementar el circuito de la figura n8 en la potoboard, conocido como Contador

binario de 3 bits.

Figura n8: Flip-Flop J-K conectados como un contador binario de tres bits. (MOD-8).

En la figura n8, cada flip-flop tiene sus entras J y K en el nivel 1, por lo que cambiara

de estado (conmutara) cada vez que la seal en su entrada CLK cambie de ALTO a

BAJO. Tener en cuenta que los pulsos de reloj solo se aplican a la entrada CLK del

FF Q0. La salida Q0 est conectada a la entrada CLK del FF Q1. Y la salida Q1 est

conectada a la entrada CLK del FF Q2. Las formas de onda de la figura n 9,

muestran como los FFs cambian de estado a medida que se aplican los pulsos.

Figura n9: Formas de onda a la salida de cada FF

Como se muestra en la figura n 9, cada FF divide la frecuencia de su entrada por 2.

De esta forma, si agregramos un cuarto FF a la cadena, este tendra una frecuencia

igual a 1/16 de la frecuencia de reloj, y as en lo sucesivo.

Si utilizamos el nmero de FF apropiados, este circuito podra dividir una frecuencia

por cualquier potencia de 2. De manera especfica, si se utilizan N flip-flops se

producir una frecuencia de salida del ultimo FF, la cual equivale a 1/2 N de la

frecuencia de entrada. A esta aplicacin de los flip-flops se le conoce como divisin

de frecuencia.

INGENIERA ELECTRNICA UPAO 2017 - 20

ELECTRNICA DIGITAL I 8

Adems de funcionar como divisor de frecuencias, el circuito de la figura n 9,

tambin opera como contador binario. Para demostrarlo podemos examinar la

secuencia de estados de los FFs despus de que ocurra cada pulso de reloj. La figura

n10, presenta los resultados en una tabla de estados.

Figura n10: La tabla de estados del flip-flop muestra la secuencia de conteo binario.

Se puede observar que, para los primeros 7 pulsos de entrada, el circuito funciona

como un contador binario, en el cual los estados de los FFs representa a un nmero

binario equivalente al nmero de pulsos que se han introducido. Este contador tiene

una capacidad de hasta 1112 = 710 antes de regresar a 000. Otra manera de mostrar

cmo cambian los estados de los FFs con cada pulso de reloj que se aplica es

mediante el uso de un diagrama de transicin de estados, como se muestra en la

figura nmero n 11.

Figura n11: Diagrama de transicin de estados: Muestra cmo cambian los estados de

los FF contadores con cada pulso de reloj que se aplique.

Cada circulo representa uno de los posibles estados, segn lo indica el numero

binario dentro del crculo. Las flechas que conectan un circulo con otro muestran la

forma en que cambia un estado a otro, a medida que se aplica un pulso de reloj, de

esta forma podemos saber cul estado va antes y cual va despus. Los diagramas de

INGENIERA ELECTRNICA UPAO 2017 - 20

ELECTRNICA DIGITAL I 9

transicin de estados ayudan a describir, analizar y disear contadores y otros

circuitos secuenciales.

El contador de la figura n 8, tiene 2 3 = 8 estados distintos (del 000 al 111). A este

contador se le denomina contador MOD-8, en donde el nmero MOD indica la

cantidad de estados en la secuencia de conteo. Si se agrega un cuarto FF, la secuencia

de estados contara en binario desde 0000 hasta 1111, un total de 16 estados. A esto

se le llamara contador MOD-16. En general, si se conectan N flip-flops en el arreglo

de la figura n 8, el contador tendr 2N estados distintos, por lo cual ser un contador

MOD-2N. Sera capaz de contar hasta 2N -1 antes de regresar a 0. Por ltimo, el

nmero MOD de un contador tambin indica la divisin de frecuencia que se

obtiene del ultimo FF.

4.9. Implemente el circuito de la figura n 12, el cual consiste en un contador ascendente

del 0 al 7. De la misma manera realizar la simulacin del circuito en ISIS Proteus y

contrastar sus resultados con la simulacin.

Figura n12: Contador ascendente del 0 al 7 con flip-flop J-K.

INGENIERA ELECTRNICA UPAO 2017 - 20

4.10. Implemente el circuito de la figura n 13, el cual consiste en un contador ascendente descendente (del 0 al 7). De la misma manera realizar la

simulacin del circuito en ISIS Proteus y contrastar sus resultados con la simulacin.

Figura n13: Contador ascendente - descendente del 0 al 7 con flip-flop J-K.

ELECTRNICA DIGITAL I 11

V. CUESTIONARIO:

5.1. Cmo implementara un flip-flop tipo T usando un flip-flop del tipo J-K? Sustente

su respuesta.

5.2. Una seal de reloj de 20kHz se aplica a un flip-flop J-K, en donde J=K=1. Cul es

la frecuencia de la forma de onda de salida del FF?

5.3. Disear un contador asncrono que cuente cclicamente de 0 a 9 (del 9 pasa al 0).

Para la construccin del circuito se dispone de biestables J-K sncronos que se

activan con el flanco de bajada de la seal de reloj. Estos dispositivos disponen de

una entrada de borrado, CLR (clear), anloga a la de los biestables del contador 7493,

cuyo nivel activo es el 0.

5.4. Construir un contador asncrono con FF J-K que cuente cclicamente del 0 al 6.

5.5. Construir, mediante biestables D tipo latch, un registro de entrada paralelo, salida

paralelo para almacenar una palabra binaria de 8 bits.

5.6. Disear un registro de desplazamiento hacia la derecha de 8 bits en el que la entrada

de informacin se realice en serie y la salida en paralelo. Se emplearn biestables D

sncronos activados por flanco de bajada, siendo, sin embargo, el registro gobernado

por los flancos de subida de la seal de reloj. El circuito dispondr as mismo de una

activa a nivel bajo.

entrada de borrado

------------------------------------------------------------------------------------------------------------

FIN DEL LABORATORIO N 7

NO OLVIDE CERRAR TODAS LAS VENTANAS, APAGAR EL SISTEMA E

INSTRUMENTOS UTILIZADOS

--------------------------------------------------------------------------------------------------------------

El docente

Ing. Alejandro Martin Len Cerna

INGENIERA ELECTRNICA UPAO 2017 - 20

Вам также может понравиться

- Guia de Flip-Flops PracticaДокумент7 страницGuia de Flip-Flops PracticapctronikgarciaОценок пока нет

- Informe Flip FlopsДокумент11 страницInforme Flip FlopsLeonardo López Avila100% (1)

- Flip FlopДокумент4 страницыFlip FlopErick Esteban NarvaezОценок пока нет

- Informe Final 3 Sistemas DigitalesДокумент24 страницыInforme Final 3 Sistemas Digitalestania tarazonaОценок пока нет

- Diseño de Un Contador Sincronico Con Flip PDFДокумент8 страницDiseño de Un Contador Sincronico Con Flip PDFFrancisco Flores LunaОценок пока нет

- T Lab #03. Laboratorio Diseño Digital - 030218Документ34 страницыT Lab #03. Laboratorio Diseño Digital - 030218luis carrasquelОценок пока нет

- Divisor de Frecuencia y Contador de RizoДокумент2 страницыDivisor de Frecuencia y Contador de RizoEddy Fernando Queca CadizОценок пока нет

- Fli-Flops, Registros y ContadoresДокумент15 страницFli-Flops, Registros y ContadoresOmar XocaОценок пока нет

- Informe Latch y Flip FlopДокумент11 страницInforme Latch y Flip FlopAlex Vin0% (1)

- Práctica 8 FlipFlop JKДокумент6 страницPráctica 8 FlipFlop JKEdgar PinalesОценок пока нет

- PracticaДокумент12 страницPracticaIsa RochaОценок пока нет

- Contadores MonolíticosДокумент15 страницContadores MonolíticosJean Carlo ArrietaОценок пока нет

- Flip Flops UNLaMДокумент37 страницFlip Flops UNLaMAnonymous dsefX2Jhm8Оценок пока нет

- Implementacion Del Minesweeper Con Un Tablero de LedsДокумент16 страницImplementacion Del Minesweeper Con Un Tablero de LedsRenzo Moscoso BasalduaОценок пока нет

- Electronica Diagramas Circuitos - Cargador para Baterías NiMH de FloteДокумент2 страницыElectronica Diagramas Circuitos - Cargador para Baterías NiMH de FloteCarlos RamosОценок пока нет

- Ensayo de Sistemas DigitalesДокумент7 страницEnsayo de Sistemas DigitalesIgnacio Moreno0% (1)

- Mapas de KarnaughДокумент25 страницMapas de Karnaughjlva_lkpbОценок пока нет

- Contador de MooreДокумент6 страницContador de MooreErnesto VásquezОценок пока нет

- El Flip FlopДокумент17 страницEl Flip FlopLuigi Jair Torres MirandaОценок пока нет

- Cómo Funciona Un Chip 7490Документ1 страницаCómo Funciona Un Chip 7490Leo AriasОценок пока нет

- Practica Mapas de KarnaughДокумент9 страницPractica Mapas de KarnaughAline Gabriela Garcia HernandezОценок пока нет

- Contador 0-39 FlipFlop DДокумент7 страницContador 0-39 FlipFlop DAtocha Kú GüemezОценок пока нет

- Guia Flip Flop VHDLДокумент16 страницGuia Flip Flop VHDLViridiana Fernandez CarreonОценок пока нет

- Bies TableДокумент37 страницBies TableLuz Karina Lopez SaavedraОценок пока нет

- Diseño Flip FlopДокумент8 страницDiseño Flip FlopLuis GonzálezОценок пока нет

- Un Circuito Secuencial Puede Entenderse Simplemente Como Un Circuito Combinacional en El Cuallas Salidas Dependen Tanto de Las Entradas Como de Las Salidas en Instantes AnterioresДокумент5 страницUn Circuito Secuencial Puede Entenderse Simplemente Como Un Circuito Combinacional en El Cuallas Salidas Dependen Tanto de Las Entradas Como de Las Salidas en Instantes AnterioresNeiry FrancoОценок пока нет

- Los Flip FlopДокумент18 страницLos Flip FloproxanaОценок пока нет

- Contadores y MemoriasДокумент26 страницContadores y MemoriasHector ValdiviaОценок пока нет

- Registros - Previo 3Документ22 страницыRegistros - Previo 3César Guerrero CorneОценок пока нет

- Siste Digit Previo 3Документ6 страницSiste Digit Previo 3DiegoОценок пока нет

- Practicas Circuitos DIgitales-Luis UrdanetaДокумент102 страницыPracticas Circuitos DIgitales-Luis UrdanetaLuis D. Urdaneta G.100% (3)

- Laboratorio 5 Mapas de KarnaughДокумент6 страницLaboratorio 5 Mapas de KarnaughYesenia Jaime RoaОценок пока нет

- Fase1 E5Документ8 страницFase1 E5Luis EdynОценок пока нет

- Termostato ElectrónicoДокумент3 страницыTermostato ElectrónicoDownloadfree VeryfreeОценок пока нет

- Capitulo Vi Flip FlopДокумент76 страницCapitulo Vi Flip FlopVladimir ZamoraОценок пока нет

- Contadores y RegistrosДокумент19 страницContadores y RegistrosElymar91Оценок пока нет

- Contador de CajasДокумент3 страницыContador de CajasMundoRo ComiPaОценок пока нет

- FLIP FlopsДокумент9 страницFLIP FlopsDelfino OlivaresОценок пока нет

- Guía4 SDI-1 2018Документ6 страницGuía4 SDI-1 2018Jesus SJОценок пока нет

- Digitales 1 Previo 5Документ11 страницDigitales 1 Previo 5jorgeОценок пока нет

- Práctica 5 - Flip-Flops, Contadores Síncronos - 1Документ2 страницыPráctica 5 - Flip-Flops, Contadores Síncronos - 1Juan Camilo GonzalesОценок пока нет

- Contador CanicasДокумент8 страницContador Canicasaioros2112Оценок пока нет

- Cap 9 New MarginДокумент56 страницCap 9 New MarginRoberto TorresОценок пока нет

- Circuitos Digitales SecuencialesДокумент7 страницCircuitos Digitales SecuencialesJose Martinez EstradaОценок пока нет

- Diseño de Circuitos Secuenciales Empleando Flip-FlopДокумент7 страницDiseño de Circuitos Secuenciales Empleando Flip-FlopDaniel PesantezОценок пока нет

- Simplificacion de FuncionesДокумент46 страницSimplificacion de FuncionesGabriel JDОценок пока нет

- Sistemas Digitales Problemas 1Документ25 страницSistemas Digitales Problemas 1Ce ChavezОценок пока нет

- Práctica Microondas Electrónica DigitalДокумент18 страницPráctica Microondas Electrónica DigitalEduardo Canto0% (1)

- Maquinas MooreДокумент35 страницMaquinas MooreDaniel GuerraОценок пока нет

- Recopilacion Aportes Proyecto Final..Документ28 страницRecopilacion Aportes Proyecto Final..JoseSalamancaPlazasОценок пока нет

- Previo 1 Sist. DigitalesДокумент13 страницPrevio 1 Sist. DigitalesValeria Andrea Nina ArrescurenagaОценок пока нет

- Cronometro Flip Flop JKДокумент8 страницCronometro Flip Flop JKDiego V-aОценок пока нет

- Contador Con Flip-FlopДокумент19 страницContador Con Flip-FlopMiguel Angel CasiqueОценок пока нет

- Circuito Comparador de 2 BitsДокумент13 страницCircuito Comparador de 2 BitsAlberto Iztatik100% (2)

- Flip-Flop J-KДокумент15 страницFlip-Flop J-KWalter CMОценок пока нет

- DECODIFICADORДокумент5 страницDECODIFICADORAlejandro GonzalezОценок пока нет

- PRACTICA 2 Sistemas Digitales IIДокумент5 страницPRACTICA 2 Sistemas Digitales IIArmando Alvarado YucraОценок пока нет

- Practica 05 Edg 1Документ25 страницPractica 05 Edg 1Patricio OrdoñezОценок пока нет

- Informe Final 1 UtrillaДокумент10 страницInforme Final 1 UtrillaCaptain Underoos0% (1)

- PRACTICA 7 Flip Flpos DigitalДокумент4 страницыPRACTICA 7 Flip Flpos DigitalGustavo CoraisacaОценок пока нет

- Diseño Filtros MatlabДокумент19 страницDiseño Filtros MatlabAlejandro Martin Leon CernaОценок пока нет

- Filtro Rechaza BandasДокумент15 страницFiltro Rechaza BandasAlejandro Martin Leon CernaОценок пока нет

- Guia de Laboratorio 8 - SolucionДокумент6 страницGuia de Laboratorio 8 - SolucionAlejandro Martin Leon CernaОценок пока нет

- Proyectos - Sistemas Digitales IДокумент3 страницыProyectos - Sistemas Digitales IAlejandro Martin Leon CernaОценок пока нет

- Practica Guiada 06Документ1 страницаPractica Guiada 06Alejandro Martin Leon CernaОценок пока нет

- Labeledig106 IntegracionДокумент3 страницыLabeledig106 IntegracionAlejandro Martin Leon CernaОценок пока нет

- FirewallДокумент4 страницыFirewallAlex AVОценок пока нет

- Lazo Garcia Nuttsy Servidores AaaДокумент74 страницыLazo Garcia Nuttsy Servidores AaaFelipe RocheОценок пока нет

- CCTV Camaras Domo Todas Las Marcas y Modelos WWW - Logantech.com - MX Mérida, YucДокумент41 страницаCCTV Camaras Domo Todas Las Marcas y Modelos WWW - Logantech.com - MX Mérida, YucLogantechОценок пока нет

- HDC-SD900 HDC-SD909 HDC-TM900 HDC-HS900 QG EsДокумент28 страницHDC-SD900 HDC-SD909 HDC-TM900 HDC-HS900 QG EsDon Alfonso RamiroОценок пока нет

- Los Virus en GNU LinuxДокумент4 страницыLos Virus en GNU Linuxrobertomarques106130Оценок пока нет

- Grado 6º - Guia 3 - El Disco DuroДокумент2 страницыGrado 6º - Guia 3 - El Disco DuroIngrid Lizeth Burbano GuerreroОценок пока нет

- Como Desbloquear Un Archivo PDFДокумент2 страницыComo Desbloquear Un Archivo PDFRebeccaОценок пока нет

- 6.1.1.7 Lab - Using Wireshark To Examine Ethernet FramesДокумент8 страниц6.1.1.7 Lab - Using Wireshark To Examine Ethernet FramesEricka Ordoñez0% (1)

- Ing. Sandy Percy López Zúñiga. Garcia Chuquimamani David EderДокумент15 страницIng. Sandy Percy López Zúñiga. Garcia Chuquimamani David EderDAVID EDER GARCIA CHUQUIMAMANIОценок пока нет

- DNS Spoofing PDFДокумент13 страницDNS Spoofing PDFAndrésMauricioMarceloОценок пока нет

- P6 REDES (Comandos Ping y Tracert)Документ7 страницP6 REDES (Comandos Ping y Tracert)Damian Marín MarínОценок пока нет

- Ejercicio BGP Basico PDFДокумент11 страницEjercicio BGP Basico PDFfedericous85Оценок пока нет

- Cdi - Clase 00Документ32 страницыCdi - Clase 00juan martin pazОценок пока нет

- Evaluacion Entrada Excel AvanadoIIlsxДокумент119 страницEvaluacion Entrada Excel AvanadoIIlsxCarlos SmithОценок пока нет

- Partes Una Computadora para Niños de Primaria Internas y ExternasДокумент15 страницPartes Una Computadora para Niños de Primaria Internas y Externasselennis100% (1)

- CWE-863 Incorrect AuthorizationДокумент7 страницCWE-863 Incorrect AuthorizationRuben DelgadoОценок пока нет

- Instituto Salvadoreño de Superacion Integral Isaac NewtonДокумент2 страницыInstituto Salvadoreño de Superacion Integral Isaac NewtonissaОценок пока нет

- 7310-7320 VentasДокумент4 страницы7310-7320 Ventasruyolmos_zeroОценок пока нет

- Modelo DercasДокумент4 страницыModelo DercasMickelОценок пока нет

- ForenseДокумент29 страницForensenormluzОценок пока нет

- Manual de Configuracion VivotekДокумент20 страницManual de Configuracion Vivotekcesarvilleda1Оценок пока нет

- Marco TeoricoДокумент2 страницыMarco TeoricoDudu Ramos75% (4)

- Preguntas Del Examen Complexivo 2016Документ392 страницыPreguntas Del Examen Complexivo 2016Alianza Bolivariana Alfarista DuranОценок пока нет

- Backup Diferenciales y ParcialesДокумент5 страницBackup Diferenciales y ParcialesDianita PachecoОценок пока нет

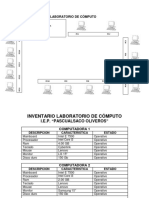

- Inventario Laboratorio de Computo PsoДокумент5 страницInventario Laboratorio de Computo PsoJorge ChavezОценок пока нет

- ACTIVIDAD N°4 - Arquitectura de La ComputadoraДокумент3 страницыACTIVIDAD N°4 - Arquitectura de La ComputadoraAnthony Nuñez CastroОценок пока нет

- Manual Administrador AlfrescoДокумент30 страницManual Administrador AlfrescoMario Navarro Madrid100% (1)

- ProcesamientoDigitalSeñalesUtilizandoMatlab (Pedro Huamaní Navarrete)Документ42 страницыProcesamientoDigitalSeñalesUtilizandoMatlab (Pedro Huamaní Navarrete)Alan Lopez100% (1)

- Actividad Redes InformativasДокумент4 страницыActividad Redes InformativasFelipe CaicedoОценок пока нет

- Inalambrico: Sistema Altavoces Cine CasaДокумент32 страницыInalambrico: Sistema Altavoces Cine CasaeddingfredОценок пока нет