Академический Документы

Профессиональный Документы

Культура Документы

Datasheet

Загружено:

Panagos Panagiotis0 оценок0% нашли этот документ полезным (0 голосов)

18 просмотров14 страницdata

Оригинальное название

datasheet (1)

Авторское право

© © All Rights Reserved

Доступные форматы

PDF или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документdata

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

18 просмотров14 страницDatasheet

Загружено:

Panagos Panagiotisdata

Авторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF или читайте онлайн в Scribd

Вы находитесь на странице: 1из 14

ANALOG

DEVICES

High Speed, Fast Settling

Precision Operational Amplifier

op-42

FEATURES

Fast

+ Slew Rate... S0Viue Min

* Settling-Time (0.01%) « us Max

*+ Gain-Bandwidth Product 1OMH2 Typ

Precise

+ Common-Mode Rejection - 8848 Min

+ Open-Loop G: =. S0OV/mV Min

+ Offset Voltage . + 750,V Max.

* Bias Current... 200pA Max

Excellent Radiation Hardness

‘Available in Die Form

ORDERING INFORMATION

1,228, PACKAGE OPERATING

Vega ‘CERDP PLASTIC SO LCC __ TEMPERATURE

“in O99 BPN BPN BPN ZOCONTACT RANGE

70 OpiAr ORCA —- — —OPe@ARGRED ML

07 Oper Opaez = > - No

15 OPAEL OPE : ND

so opsecr opaacs xiND

+ Fordovioesprcessedin oa complanceo Mil STO-689, 09/889atter pat

umber, Consut factor for 83 datasheet

11 Burnsnisavatabeen commercial ang ncuatia temperate ange pars in

etn, lati ci, and TO-canpackag

GENERAL DESCRIPTION

‘The OP-42 isa fast precision JFET-input operational amplifier.

Similar in speed to the OP-17, the OP-42 offers a symmetric

SIMPLIFIED SCHEMATIC

{58V/qs slew cate and is internally compensated for unity-gain

operation. OP-42 speedis achieved with a supply currentofless

than 6mA. Unity-gain stabilty, a wide full-power bandwidth of

800kHz, anda fast setting-time of 800nst0 0.01% make the OP-

42 anideal output ampitir for fast digital-to-analog converters,

Equal attention was given toboth speed and precision in the OP-

42 design. Is tight 750nV maximum input offset voltage com-

bined with wel-controlied drift of less than t0yV/°C eliminates

the need for external nulling in many circuits. The OP.42's

Continued

PIN CONNECTIONS

0.09

(Suffix)

20-CONTACTLCC

(RC-Sutfix)

B-PINCERDIP

Sutin)

EPOXYMINLOIP

(P-Suttix)

BPINSO

(G-Sutfix)

el

F

oP-42

GENERAL DESCRIPTION Continued

common-mode rejection of 8848 minimum over a +11V input

voltage range is exceptional for a high-speed amplifier. High

CMA combined with a minimum S0OVimV gain into 10kG load

{ensure excellantlinearityinboth noninverting andinverting gain

configurations, Tho low input bias and offset currents provided

by the JFET input stage suit the OP-42 for use in high-speed

sample and hold circuits, peak detectors, and log amplifiers.

Excellent radiation hardness characteristics make the OP-42

ideal for miltary and aerospace applications.

The OP-42 conforms to the standard 741 pinout with nulling to

\V-, The OP-£2 upgrades the performance of circuits using the

ADS44, ADB11, AD711, and LF400 by direct replacement. In

Circuits without nulling, the OP-42 offers an upgrade for designs.

Using the OP-16, OP-17, LT1022, LT1058, and HA2510.

ABSOLUTE MAXIMUM RATINGS (Note 1)

‘Supply Voltage. 220

Input Voltage (Note 2} 320

Differential Input Voltage (Note 2) 40v

Output Short-Circuit Duration Indfined

Storage Temperature Range.

Operating Temperature Range

65°C to +175°C

(OPa2A (4,2) 55°C to +125°C

(Pa, FW, Z) 28°C to 485°C

oPa2G 40°C to 485°C

Junction Temperature “6s°C to 4175°C,

Lead Temperature Range (Soldering, 60 sec) 4300°C

PACKAGE TYPE ANTES) Oe —_«UNTTS

70.090), 70 ow

a Hermie

BPin Pasko)

20Conact LOC RETO)

P6015)

11 Absole maxirum rings spp te bth DICE and packaged pa, tess

2, Foreussly volages les than 220 the absole maximum nt vga le

‘sual ne sup vate.

8 qt apacio fr worl cave mourtngcordons, Lo. © ectee for

‘bieeinsoctet or 70, CERDIP, PDIP ard LCC packageh 0, seed

torgevee sidered opted cru oar for 60 package

38

ELECTRICAL CHARACTERISTICS at V, = =15V, 7, = +25°C, unless otherwise noted

ona oraar

Panaweren symeot_covomoxs sin ve eww OP max ons

man voraae Yes es om a

Topas ure y Veg TBE tam SSC~*aO SC

Inpu OReiCuren gg Noy Wee CS SCSC=~ Sa

Iona wotge henge WR NOT) we RE ES

Sammons cu oe mB

Power Supehy PSAR 3s 40 - 2 8 - 2 0 wi

. a

Large Signst A, 200 (260 - 200 260 Vim

“tog can vo 260 wo aw -

“omsavome SBE BS TT

sone ais Ns

Sevcies apa oa = wT = mma

‘curren: ut ‘sc _teorauna 20 be ‘2 te

si Curent ty Nee se 8 es Bm

Siew Rate ae a oS 0

Fab Dw, (tea) 730 ooo ee

Gainsancnn Gow tyson - 0 = - 0 tie

Seting ine 4 _ (myaepaane i

Oveioaa Recovery 70 - m= - 70 ne

Phase Margin % oman _ 7 = _ ~~ domes

TF Ogee . oe - @

Gan Warn oer - °

Tupatieicad——q UnyGonSmie sq gap ~*~‘ a agSs*S*«, v0) 0 - we

Senserdwan ow a - 0 we

Sat Te i we - oo 10 a

Sverans ory 70 ~

‘ine ton :

Panag % aa Gun = * = eons

OP-42

ELECTRICAL CHARACTERISTICS atV, 25°C, unless otherwise noted. Continued

co

PARAMETER conorions un ye ax uns

Gane Ao 100 Open tone > ~ -

Cees ga —

Drive Capability ‘ote 4) oo _ ef

"imeduee an - 06 ~ be

Sparen - = - 2

bi Reece D

Vata nce ae ie 7 Won

vonage nace . % ave

®

eae ‘ = boo - oN

Trin Range _ * - "

tater 5 vm

So Voage Rage =e v

noes: 3. Seti is aoe Aang den es cet town

1 "Seuaiosy CUR tt Faures Somogicne tf pede purines bt mo oe

2 Guararleed by sows et and rma MY, » SRMEHt Ope 4 Guaranteed bt nat ete.

ELECTRICAL CHARACTERISTICS atV,, = +15V, -25°C <7, «85°C for E/F grades, and 40°C < , « +85°C for G grade,

unless otherwise noted.

OPa2E Paar OP-a26

PARAMETER sywaot_conomons, mun Tye MAX MIN TYP MAX mam TP MAX UNITS

(Ofer Vos = ea 48 = 8828 = 20 6

‘Ofer vations |

Temperate TOo5 - 4 0 - a - - 8 = wre

InputBis Curent iy ate) = 05 te = 0820 — 08 20

Trea Oteot Curent Ig Netw) 00802 — 906 e0 = 808 oA

IngutVotape ange WR (ote) a BB gy BE an Rs v

econ coun em 8 o

Power Supiy san Yanst0v - a - 0 - 6 ww

Rejection Rat SAR ao ° - -

Cara Sion! Toe Refi tes) ——~800 50D 00 00 Vinw

‘otege Gan oat vyeetov 100160100 00180

‘Output Votage ne mo 23 ap 23a 8S Y

‘Sung o ihe fie

Cura sn a) 360 ” 0 oma

swept Curent eS - os = st 6s ~ sheen

Siew Rate ee o 7 oo - ova

Canscine La8d ‘Uniy-Gan Sane co ow ao wom

‘eve Capabity ow) 2 7

NorEs: 2 Guarantee by HR st

117) = 85°C for IF Grados: T,= 125° Aga. 3. Gusrantoed but notte.

OP-42

ELECTRICAL CHARACTERISTICS at V,

18V, ~85°C « T, « 125°C for A grade, unless ctherwise noted.

‘OPER

Panaweren siuvot conomons wy ewan

Olt Voge oa = as 20 av

feat Volage

Tenperare Tos - ‘ 10 wre

Coaticert

input Bin Cent = é 20 o~

input Ob! Curent oy = rH ¥0 om

‘not Votage Range va (wote2) ee - v

Commons’ SCS nate

wR vo a - e

feccton °

"peta Pon aay - ~ ow

0 oe) Cry vim

‘tage Gin No 2a) Vat 0

‘Ouputvotage| na wo 128 - y

Swing 0 Na

Tror-Great Oct Sed 2 ~ ma

Carat Unt be tern * ss

Sip Curent ee yetows - 51 60 ma

Seurate a © @ en)

Capac tas to 280 7 oF

Dive Capay & -

Nores:

112 05°C lor EF Grades: T,«125°C(or Agate

2. Gusanteed by CMR tect.

2. Guaranteed butnot tests

Op-42

DICE CHARACTERISTICS

4 OFFSET VOLTAGE NULL.

2. INVERTING INPUT.

3, NONINVERTING INPUT

‘4 NEGATIVE SUPPLY

5, OFFSET VOLTAGE NULL

8. AMPLIFIER OUTPUT

T.POSITIVE SUPPLY

DIE SIZE 0.098 0.070 inch, 6860 6q mils

(2.40 1.78 mm, 443 ¢q. mm)

WAFER TEST LIMITS at Vs~ *15V, 7)= 25°C, unless otherwise noted.

ser otage 8 16 mvmax

ep Sine Curt ‘o 250 BAMA

Input Oat Curent tos PAM

ecw Reto sa ova ss

“Deapieings Sen nh Tis a

‘rent Lin bse teoround _ _ 10 van

supp Curent lee seis 6s mamax

Sow a * wasn

toes oe Uniy Gain see wo onsen

NOTES:

1 Guarantee by CMR test

Eecrcal tests are performed

factory fo rag

BURN-IN CIRCUIT

1: Due 0 vantone in aeerbly mathoge and nara yes lose, yi an

nt epeeitcations bused on cect uacaon tiveugh spe el assem ad testing

ceaping isnot

OP-42

TYPICAL PERFORMANCE CHARACTERISTICS.

OPEN-LOOP GAIN, PHASE CoMMON-MoDE POWER-SUPPLY REJECTION

FREQUENCY EJECTION vs FREQUENCY ve FREQUENCY

; on : * T

=R- TTT weak

erase jn we —|_} 3

gare Mi Ee + i

5 we Ba, | | :

2 | i

SLEW RATE ve

SLEW RATE ve DIFFERENTIAL SLEW RATE ve

TEMPERATURE INPUT VOLTAGE CAPACITIVE LOAD

ean 4 ;

3 : | :

: ott T i

5 wl PO eee

“ . | i

cot Zo Lif ame

SETTLING-TIME IsToRTION CLOSED-LOOP GaIN

ve STEP SIZE ve FREQUENCY ve FREQUENCY

sa hs | ras i

BS '

2 i

: | 5

\ = se

\ eon LL ty "i

op-42

TYPICAL PERFORMANCE CHARACTERISTICS.

CLOSED-LOOP SMALL-SIGNAL

(OUTPUT IMPEDANCE MaxiMUM OUTPUT SWING OVERSHOOT vs

vsFREQUENCY vs FREQUENCY LOAD CAPACITANCE

” Tm om | =

of } Sa GME ALY oe

a i | Zl |

I i. ri Wp ES ee

OUTPUT SWING vs SUPPLY CURRENT SUPPLY CURRENT vs

LOAD RESISTANCE ve TEMPERATURE SUPPLY VOLTAGE

“Owe Tl "Ty tae “ T

: [ Hime ~ T cet eyh

ie iin Pep aN

be in =

3 l b Tt fetecl |

= ry t a

TYPICAL DISTRIBUTION OF TYPICAL DISTRIBUTION OFFSET VOLTAGE

INPUT OFFSET VOLTAGE OF TCVog WARM-UP DRIFT

i oe ~ wy] “Coe

o Fase 1 .{"

& :” i T

g 1 Bool | 3

. —— Cor LoS

OP-42

TYPICAL PERFORMANCE CHARACTERISTICS

BIAS CURRENT vs

JUNCTION TEMPERATURE

&

&

OFFSET CURRENT vs

BIAS CURRENT vs

COMMON-MODE VOLTAGE

‘OPEN-LOOP GAIN vs

BIAS CURRENT

WARM-UP DRIFT

‘SHORT CIRCUIT

OUTPUT CURRENT vs

JUNCTION TEMPERATURE

JUNCTION TEMPERATURE JUNCTION TEMPERATURE

a =

fn

:

3°] 4

bn

VOLTAGE NOISE DENSITY

ve FREQUENCY

a

Pus |

Eo (it

pa lh t

el

" ai mi

op-42

APPLICATIONS INFORMATION

The OP-42 combines speed with a high level of input preci-

sion usually found only with slower devices. Well-behaved

‘AC performance in the form of clean transient response,

symmetrical slew-rates and a high degree of forgiveness to

supply decoupling are the hallmarks of this amplifier. AC

{gain and phase response are quite independent of tempera

ture or supply voltage. Figure 1 shows the OP-42's emall-

signal response. Even with 75pF loads, theres minimal ring-

ing in the output waveform. Large-signal response is shown

in Figure 2. This figure clearly shows the OP-42's exception-

ally close matching between positive and negative slew-

rates. Slew-rate symmetry decreases the DC offset a system

encounters when processing high-frequency signals, and

thus reduces the DG current necessary for load driving

FIGURE 1: Small-Signai Transient Response,

FIGURE 2: Large-Signal Transient Response,

Zz

‘As with most JFET-input amplifiers, the output of the OP-42

may undergo phase inversion if either input exceeds the

specified input voltage range. Phase inversion will not dam-

age the amplifier, nor will t cause an internal latch-up.

Supply decoupling should be used to overcome inductance

{and resistance associated with supply lines to the amplifier.

-10-

For most applications a 0.1,F to 0.01yF capacitor should be

placed between each supply pin and ground.

‘The OP-42 displays excellent resistance to radiation. Radia~

tion hardness data is available by contacting the factory.

OFFSET VOLTAGE ADJUSTMENT

Offset voltage is adjusted with a 10k!2 to 100kN potentiome-

ter as shown in Figure 3. The potentiometer should be con-

ected between pins 1 and 5 with its wiper connected to the

= supply. Nulling Vosin this manner changes TCVosby no

more than §:V/°C per milivolt of Vos change. Alternately,

Vos may be nulled by attaching the potentiometer wiper

through a 1MA resistor to the positive supaly rail

FIGURE 3: Input Offset Voltage Nulling

San ae remes wr

‘SETTLING-TIME

Guaranteed fast-settling is assured by sample-testing during

production. The OP-42 is configured asa unity-gaintollower

In the test circuit of Figure 4. This test method has advan-

tages over false-sum-node techniques in that the actual out-

utof theampiifieris measured, instead of an error-voltageat

the sum node. Common-mode settling affects are exercises

in this circuit, in addition to the slew-rate and bandwidth

effects measured by the false-sum-node method. A reason-

ably flat-top pulse is required as a stimulus,

‘The output waveform of the OP-42 being tested is clamped

by Schottky diodes and bulfered by the JFET source-

follower. The signal is amplified by a factor ot ten by the fast

amplifier IC1, then Schottky-clamped before being output,

The OP-41 provides overall offset nulling. Analysis of the

waveform using a digitizing oscilloscope determines the op

amp's seltling-time,

OP-42

FIGURE 4: Settling-Time Test Fixture

FIGURE 5: OP-42 Sottling-Characteristios

DAC OUTPUT AMPLIFIER

‘The OP-42is an excellent choice for a DAC output amplifier,

sino its high speed and fast settling-time allow quick transi

tions between codes, even for full-scale changes in output

lovel. The DAC output capacitance appears at the opera-

tional amplifier inputs, and must be compensated to ensure

oe

‘optimal settling speed. Compensation is achieved with ca

pacitor C in Figure 6. C must be adjusted to account for the:

DAC's output capacitance, the op amp's input capacitance,

land any stray capacitance at the inputs. With a bipovar DAC,

‘an additional shunt resistor may be used to optimize

response, This technique is described in PMI's application

rote AN-24,

FIGURE

DAC Output Amplifier Circuit

Highest speed is achieved using bipolar DACs such as PM's

DAC-08, DAC-10 of DAC-S12. The output capacitances of

these converters are up to an order of magnitude lower than

their CMOS counterparts, resulting In substantially faster

settling-times. The high output impedance of bipolar DACs.

allows the output amplifier to operate ia a true current-to-

voltage mode, with a noise gain of unity, hereby retaining the

amplifier’ full banéwiath, Offset voltage has minimal effect

Cn linearity with bipolar converters,

(CMOS digital-to-analog converters have higher output ca-

pacitances and lower output resistances than bipolar DACs.

OP-42

This results in slower settling-times, higher sensitivity to

offset voltages and a reduction in the output amplifiers

bandwidth, These trade-offs must be balanced against the

‘CMOS DAC's advantages in terms of interfacing capability,

power dissipation, accuracy levals and cost. Using the inter

‘nal feedback resistor which is present on most CMOS con-

verters, the gain applied to offset voltage varies between 4/3

‘and 2, depending upon output code, Contributions to linear

ity error willbe as much as 2/3Vos. Ina 10-volt 2-bit system,

this may add up to an additional 1/5LSB DNL with the

(OP-42E, Amplifierbandwidthisreduces by the same gaia factor

applied to offset voltage, however the OP-42's 10MHz gain-

‘bandwidth product results in no reduction of the CMOS con-

verter's multiplying bandwidth

Individual DAC data-sheets should be consulted for more

complete descriptions of the converters and their circuit

applications.

FIGURE 7: DAC Output Amplifier Response (PM-7545 DAC)

0.1uF capacitor, Compensation for the OP-42's input capac

itanco is provided by Cc. The circuit may be operated at any

‘gain, in the usual op emp configurations.

FIGURE 8: High-Current Output Buffer

DRIVING A HIGH-SPEED ADC

‘The OP-42's open-loop output resistance is approximately,

5011. When feedback is applied around the amplifier, output

resistance decreases in proportion to open-loop gain divided

by closed-loop gain (Ayoi/Ayci). Output impedance in-

creases as open-loop gain roll-off with frequency. High-

speed analog-to-digital converters require low source impe-

dances at high frequency. Output impedance at 1MHz is,

typically 50 for an OP-42 operating at unity-gain. Hf lower

utput impedances are required, an output butter may be

placed at the output of the OP-42.

HIGH-CURRENT OUTPUT BUFFER

‘The circult in Figure 8 shows a high-current output stage for,

the OP-42. Output current is limited by R1 and R2. For good

{racking between the output transistors Q1, Q2 and thelr

biasing diodes D1 and D2, thermal contact must be main=

tained between the transistor and its associated diode. If

good thermal contact is not maintained, Fi and R2 must be

Increased to 5-60 in order to prevent thermal runaway. Using,

500 resistors, the circuit easily drives a 750 load (Figure 8).

Output resistance is decreased and heavier loads may be

driven by decreasing R1 ana R2.

Base current and biasing for Q1 and Q2.are provided by two

current sources, the MAT-02 and the JFET. The 2k potenti

lometer in the JFET current source should be trimmed for

optimum transient performance. The case of the MAT-02,

should be connectedta V-, and decoupled to grouna with a

ae

DRIVING CAPACITIVE LOADS

Best performance will always be achieved by minimizing

Input and load capacitances around any high-speed ampli

fier. However, the OP-42 is guaranteed capable of driving a

1O0pF capacitive load over its full operating temperature

range while operating at any gain including unity. Typically

‘an OP-42 will drive more than 250pF at any temperature

‘Supply decoupling does affect capacitive load driving ability.

Extra care should be given to ensure good decoupling when

driving capacitive loads, and a larger decoupling capacitor

between 1uF and 10uF should be placed in paralel with the

usual decoupling capacitor on each supply.

OP-42

Large capacitive loads may be driven utilizing the circult

shown in Figure 10, Rt and C1 introduce a small amount ot

teodforward compensation around the amplifier to counter

act the phase lag induced by the output Impedance and load

capacitance. At DC and low frequencies, R1 Is contained

within the feedoack loop. Athigher frequencies, feedforward

‘compensation becomes increasingly dominant, and R1's,

effect on output impedance will become more noticeable.

When driving very large capacitances, slew-rate will be

limited by the short-circuit current limit. Although the un-

loaded slew-rate is insensitive to variations in temperature,

the output current limit has a negative temperature coetti-

cient, and is asymmetrical with regards to sourcing and sink-

1ng current. Therefore, slew-rate into excessive capacities

will decrease with increasing temperature, and will lose

symmetry.

COMPUTER SIMULATIONS

Many electronic design and analysis programs include mod-

fle for op amps which calculate AC performance from the

location of poles and zeros. As an ald to designers utilizing

such a program, major polas and zeros of the OP-4? are listed

below. Their location will vary slightly between production

lots. Typically, they will be within =15% of the frequency

listed. Use of this data will enabie the designer to evaluate

gross circuit performance quickly, but should not supplant

rigorous characterization of « breadboarded circuit

POLES ZEROS

20H IMHz

800KH2

3M

FIGURE 11: OP-41 Servo Amplifier Provides Offset Correction

FIGURE 10: Compensation for Large Capacitive Loads

AUTOZEROING OFFSET VOLTAGE

Figure 11 describes a circuit for automatic offset voltage and

driftcorrection. The OP-41 is used in aservo loop to force the

‘OP-42 outpul equal to the OP-41's offset voltage. Thus, tne

OP-42's effective input offset is held below 10uV (ImV/Ayc

100) despite any temperature variations. Thiscircuit will be

most advantageous in high-gain applications.

Feedback is accomplished using the OP-42's null pins, leav-

Ing both inputs free for other purposes. In the application

OP-42

shown, the OP-42 has seven multiplexed inputs, while the

eighth input provides a ground reference. Nulling isaccomp-

lished by addressing the grounded channel. This address

should be held for atleast 200s. After this time, the address

may be changed to another channel. The MUX-08 ENABLE

pin must be high during the entire nulling cycle. During this

time, JFET switch J1 turns on, completing feedback around

the OP-41 servo amplifier. A charge is developed across Cy,

to compensate for the OP-42's offset voltage. When another

channels addressed, J1 turns off, and the correction charge

is maintained across Cby the OP-4t, Droopis exceptionally

low — only 1.3uV/s at 25°C. A correction range of more than

4mV allows nulling of minor system offsets as well as the

OP-42's offset voltage.

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- Data SheetДокумент4 страницыData SheetPanagos PanagiotisОценок пока нет

- DatasheetДокумент2 страницыDatasheetPanagos PanagiotisОценок пока нет

- Data Sheet: Wireless ComponentsДокумент6 страницData Sheet: Wireless ComponentsPanagos PanagiotisОценок пока нет

- DatasheetДокумент2 страницыDatasheetPanagos PanagiotisОценок пока нет

- Radial Leads/Skycap /SR Series: General InformationДокумент14 страницRadial Leads/Skycap /SR Series: General Informationshine870494Оценок пока нет

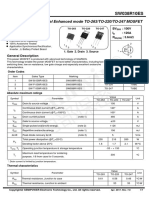

- N-Channel Enhanced Mode TO-263/TO-220/TO-247 MOSFET: SW038R10ESДокумент7 страницN-Channel Enhanced Mode TO-263/TO-220/TO-247 MOSFET: SW038R10ESPanagos PanagiotisОценок пока нет

- DatasheetДокумент10 страницDatasheetPanagos Panagiotis100% (1)

- St173Cpbf Series: Inverter Grade Thyristors Hockey Puk VersionДокумент9 страницSt173Cpbf Series: Inverter Grade Thyristors Hockey Puk VersionPanagos PanagiotisОценок пока нет