Академический Документы

Профессиональный Документы

Культура Документы

Fifo

Загружено:

pawanzОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Fifo

Загружено:

pawanzАвторское право:

Доступные форматы

FSM design using Verilog: AsicGuide.com http://electrosofts.com/verilog/fo.

html

HOME Electronics Directory Articles/ Tutorials eBooks

About Us FORUM Links Contact Us

Implementing a FIFO using Verilog

A FIFO or Queue is an array of memory commonly used

in hardware to transfer transfer data between two circuits

with different clocks. There are many other use of FIFO

also. FIFO uses a dual port memory and there will be two

pointers to point read and write addresses. Here is a

generalized block diagram of FIFO.

Generally fifos are implemented using rotating pointers. We can call write and read pointers of a FIFO as

head and tail of data area. Initially read and write pointers of the FIFO will point to the same location. In a

fifo with n locations, after writing data to 'n'th location, write pointer points to 0th location.

Here is an example to explain how FIFO uses the memory. This is a fifo of length 8, WP and RP are the

locations where write pointer and read pointer points. Shaded area in the diagram is filled with data.

One data pushed to fifo:

1 of 7 2017/11/05, 11:04

Вам также может понравиться

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (120)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- System Verilog Cheat SheetДокумент2 страницыSystem Verilog Cheat SheetRaymundo Saraiva100% (1)

- Metastability and Synchronizers - Posted PDFДокумент14 страницMetastability and Synchronizers - Posted PDFpawanzОценок пока нет

- Simple RTL PipelineДокумент7 страницSimple RTL PipelinepawanzОценок пока нет

- Clock and SynchronizationДокумент99 страницClock and SynchronizationpawanzОценок пока нет

- Atal Pension Yojana (Apy) Form To Upgrade/Downgrade Pension AmountДокумент1 страницаAtal Pension Yojana (Apy) Form To Upgrade/Downgrade Pension AmountpawanzОценок пока нет

- 14 Cach Dong Bo Du Lieu - Synchronous TechniquesДокумент8 страниц14 Cach Dong Bo Du Lieu - Synchronous TechniquesNguyễn Thế TuyênОценок пока нет

- Shiva Kavacham TeluguДокумент6 страницShiva Kavacham Teluguvinsha71Оценок пока нет

- Atmel 8456 8 and 32 Bit AVR Microcontrollers AVR127 Understanding ADC Parameters Application NoteДокумент20 страницAtmel 8456 8 and 32 Bit AVR Microcontrollers AVR127 Understanding ADC Parameters Application NoteSapna NarayananОценок пока нет

- Advanced Synthesis CookbookДокумент127 страницAdvanced Synthesis CookbookZow NiakОценок пока нет

- CPF User PDFДокумент203 страницыCPF User PDFpawanzОценок пока нет

- Tutorial Simulation Modelsim 0Документ14 страницTutorial Simulation Modelsim 0pawanzОценок пока нет

- LUT - (Look Up Table) : Field Programmable Gate ArraysДокумент3 страницыLUT - (Look Up Table) : Field Programmable Gate ArrayspawanzОценок пока нет

- Designing With PIN Diodes (AP5508-98)Документ17 страницDesigning With PIN Diodes (AP5508-98)fahkingmoronОценок пока нет

- Sync AsyncДокумент31 страницаSync AsyncAnand ThibbaiahОценок пока нет

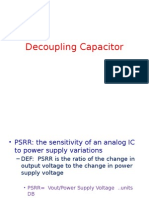

- Decouping CapacitorДокумент4 страницыDecouping CapacitorpawanzОценок пока нет

- BhartriharisubhashitaluДокумент80 страницBhartriharisubhashitalupawanzОценок пока нет

- 18Документ10 страниц18pawanzОценок пока нет

- Modeling of Finite State Machines: Debdeep MukhopadhyayДокумент36 страницModeling of Finite State Machines: Debdeep MukhopadhyaypawanzОценок пока нет

- Anjaneya Dandakam Telugu LargeДокумент3 страницыAnjaneya Dandakam Telugu LargepawanzОценок пока нет

- Next Gen 28 NM OverviewДокумент10 страницNext Gen 28 NM OverviewpawanzОценок пока нет

- DECS-IInd Sem SyllabusДокумент17 страницDECS-IInd Sem SyllabusDinesh KumarОценок пока нет

- Navagraha Stotram TeluguДокумент2 страницыNavagraha Stotram TelugumohankrishnavОценок пока нет

- Shiva KavachamДокумент10 страницShiva KavachampawanzОценок пока нет

- It ReturnsДокумент1 страницаIt ReturnspawanzОценок пока нет

- 4150 Electronics 4Документ3 страницы4150 Electronics 4pawanzОценок пока нет

- Names of Foodstuffs in Indian LanguagesДокумент19 страницNames of Foodstuffs in Indian LanguagesSubramanyam GundaОценок пока нет

- Electronics Symbols Cheat SheetДокумент14 страницElectronics Symbols Cheat Sheetpawanz100% (1)

- Systemverilog Made Easy: A Perl Interface To A Full Ieee 1800 Compliant ParserДокумент5 страницSystemverilog Made Easy: A Perl Interface To A Full Ieee 1800 Compliant ParsersattarsekharОценок пока нет

- Ubuntu12 04-DefaultApplicationKeyboardShortcutsДокумент20 страницUbuntu12 04-DefaultApplicationKeyboardShortcutspawanzОценок пока нет