Академический Документы

Профессиональный Документы

Культура Документы

Lab02 PDF

Загружено:

aditya kumarОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Lab02 PDF

Загружено:

aditya kumarАвторское право:

Доступные форматы

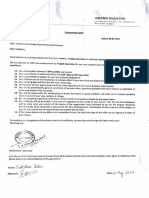

Lab Workbook Adding IP to a Hardware Design Lab

Adding IP to a Hardware Design Lab

Introduction

This lab guides you through the process of adding additional IP to an existing processor system by using

Xilinx Platform Studio (XPS). You will add GPIO peripheral from the IP Catalog tab to interface to the

push buttons and DIP switches on the Spartan-3E Starter Kit. At the end of the lab, you will generate the

bitstream and test the peripherals in hardware.

Objectives

After completing this lab, you will be able to:

Add additional IP to a hardware design

Update ucf file to support external ports of the added IP

Setup some of the compiler settings

Design Description

The purpose of this lab exercise is to extend the hardware design (Figure 1) created in Lab 1.

Figure 1. Extend the System from the previous lab

Procedure

This lab is separated into steps that consist of general overview statements that provide information on

www.xilinx.com/university SP3E 2-1

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

the detailed instructions that follow. Follow these detailed instructions to progress through the lab.

This lab comprises 7 primary steps: You will open the project, add and connect GPIO peripherals in the

system, configure the GPIO peripherals, make external GPIO connections, analyze the MHS file, add the

software application and compile and, finally, verify the design in hardware.

Note: If you are unable to complete the lab at this time, you can download the original lab files for this

module from the Xilinx University Program site at http://www.xilinx.com/university

General Flow for this Lab

Step 1: Step 2: Step 3: Step 4: Make Step 5:

Open the Add and Connect Configure External Analyze the

Project GPIO the GPIO GPIO MHS file

Peripherals to Peripherals Peripheral

the System Connections

Step 6: Add Step 7:

Software Verify the

Application Design in

and Compile Hardware

SP3E 2-2 www.xilinx.com/university

xup@xilinx.com

Lab Workbook Adding IP to a Hardware Design Lab

Open the Project Step 1

1-1. Create a lab2 folder and copy the contents of the lab1 folder into the lab2

folder. Launch Xilinx Platform Studio (XPS) and open the project file.

1-1-1. Create a lab2 folder in the c:\ xup\ embedded\ labs directory and copy the contents from lab1 to

lab2.

1-1-2. Open XPS by selecting Start All Programs Xilinx ISE Design Suite 13.2 EDK

Xilinx Platform Studio.

1-1-3. Select Open a recent project, Click OK and browse to C:\ xup\ embedded\ labs\ lab2.

1-1-4. Click system.xmp to open the project.

Add and Connect GPIO Peripherals to the System Step 2

2-1. Add two instances of an XPS GPIO Peripheral from the IP catalog to the

processor system via the System Assembly View.

XPS provides two methods for adding peripherals to an existing project.

You will use the first method, the System Assembly View panel, to add

most of the additional IP and connect them. The second method is to

manually edit MHS file.

2-1-1. Select the IP Catalog tab in the left window and click on plus sign next to General Purpose IO

entry to view the available cores under it (Figure 2).

Figure 2. IP Catalog

www.xilinx.com/university SP3E 2-3

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

2-1-2. Double-click on the XPS General Purpose IO core twice to add two instances to the System

Assembly View, each time clicking OK to accept the default configuration (you can make changes

to configuration settings, but we will do it later).

2-1-3. Change the instance names of the peripherals to dip and push, by clicking once in the name

column, typing the new name for the peripheral followed by pressing Enter key.

At this point, the System Assembly View should look like the following (Figure 3):

Figure 3. System Assembly View After Adding Peripherals

2-1-4. Click once in Bus Connection column for the push and dip instances to connect them as slave

devices to the PLB.

At this point, the Bus Connections tab should look like the following (Figure 4):

SP3E 2-4 www.xilinx.com/university

xup@xilinx.com

Lab Workbook Adding IP to a Hardware Design Lab

Figure 4. Bus Interfaces Tab showing Bus Connections to the Added Peripherals

2-1-5. Select the Addresses filter.

Note that there are few instances which are not assigned addresses.

You can manually assign the base address and size of your peripherals or have XPS generate

the addresses for you.

2-1-6. Click Generate Addresses (located on the right most end of the tabs) to automatically generate

the base and high addresses for the peripherals in the system. The base address and high

addresses will change as shown in Figure 5.

www.xilinx.com/university SP3E 2-5

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

Figure 5. Peripherals Memory Map

Configure the GPIO Peripherals Step 3

3-1. There are four push buttons and four DIP switches on the Spartan-3E

starter kit. You will first configure the push and dip instances according to

their sizes and direction, and then make external pin connections.

3-1-1. Select the Ports filter in the toolbar of the System Assembly View.

3-1-2. Double-click on the push instance to access the configuration window.

Notice that the peripheral can be configured for two channels, but, since we want to use only one

channel without interrupt, leave the GPIO Supports Interrupts and Enable Channel 2

unchecked.

The settings for the Common parameters should be set according to Figure 6 below.

Figure 6. Configurable Common Parameters of GPIO Instance for Push Buttons

3-1-3. Next click Channel 1, click on the GPIO Data Channel Width down arrow and set it to 4, you will

use 4 push buttons on the Spartan-3E starter kit. Set Channel 1 is input Only to True (Figure

7):

SP3E 2-6 www.xilinx.com/university

xup@xilinx.com

Lab Workbook Adding IP to a Hardware Design Lab

Figure 7. Setting Configurable Parameters for Push Buttons

3-1-4. Similarly, set the same parameters for the dip instance, as performed for the push buttons.

Make External GPIO Peripheral Connections Step 4

4-1. You will connect the push and dip instances to the push buttons and DIP

switches on the Spartan-3E starter kit. In order to do this, you must

establish the GPIO data ports as external FPGA pins and then assign them

to the proper locations on the FPGA via the UCF file. The location

constraints are provided for you in this section. Normally, one would

consult the Spartan-3E starter kit user manual to find this information.

4-1-1. In the Net field of theGPIO_IO_I port of the push instance, make the GPIO_IO_I port as external

by selecting Make External. You should see a new external net connection (Figure 8).

Figure 8. GPIO_in Port Connection Added to push Instance

www.xilinx.com/university SP3E 2-7

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

4-1-2. Similarly, make the GPIO_IO_I port of dip as external in the net field of the GPIO_IO_I port of the

dip instance.

The GPIO_IO_I ports of both dip and push are now connected externally on the FPGA (Figure

9).

Figure 9. Push and DIP Instances External Ports

4-1-3. Click on the system.ucf file under the Project tab and add the following code to assign pins to

push buttons (The constraints are provided in lab2.ucf file in c:\ xup\ embedded\ source

directory. Copy it from there and paste it in your ucf file).

Figure 10. UCF file (pin assignments).

4-1-4. Save the system.ucf and close it.

SP3E 2-8 www.xilinx.com/university

xup@xilinx.com

Lab Workbook Adding IP to a Hardware Design Lab

Analyze the MHS file Step 5

5-1. Open the system.mhs file, study its contents, and answer the following

questions.

5-1-1. Double-click the system.mhs file to open it if it is not already open.

Study the external ports sections and answer the following questions:

Question 1

Complete the following:

Number of external ports: ___________________

Number of external ports that are output: ___________________

Number of external ports that are input: ___________________

Number of external ports that are bidirectional: ___________________

5-1-2. Review the entire MHS file.

Question 2

List the instances to which the clk_s is connected:

___ __________________________________________

______________________________________________

List the instances connected to the mb_plb bus:

______________________________________________

______________________________________________

5-1-3. Review the memory map in the Addresses tab of the System Assembly View.

Question 3

Draw the address map of the system, providing instance names:

www.xilinx.com/university SP3E 2-9

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

Add Software Application and Compile Step 6

6-1. Start SDK from XPS, generate software platform project with default

settings and default software project name.

6-1-1. Start SDK by clicking Project Export Hardware Design to SDK and click on Export &

Launch SDK button with default settings.

Since we have not generated hardware bitstream and the default option is selected, a hardware

bitstream will be generated and then SDK will be open.

6-1-2. Browse to C:\xup\embedded\labs\lab2\SDK\SDK_Export and click OK.

6-1-3. In SDK, select File New Xilinx Board Support Package.

6-1-4. Click Finish with default settings (with standalone operating system).

This will open the Software Platform Settings form showing the OS and libraries selections

Figure 1. Board Support Package Settings

6-1-5. Click OK to accept the default settings, as we want to create a standalone_bsp_0 software

platform project without requiring any additional libraries support.

6-1-6. The library generator will run in the background and will create xparameters.h file in the

C:\ xup\embedded\labs\lab2\SDK\SDK_Export\standalone_bsp_0\microblaze_0\include\

directory.

SP3E 2-10 www.xilinx.com/university

xup@xilinx.com

Lab Workbook Adding IP to a Hardware Design Lab

6-2. Create an application project and import the provided lab2.c file.

6-2-1. Select File New Xilinx C Project.

6-2-2. Select Empty Application in the Select Project Template window, and enter TestApp as the

Project name and click Next.

Figure 2. Create a blank C Project

6-2-3. Select Target an existing Board Support Package option, then select standalone_bsp_0 and

click Finish.

6-2-4. The TestApp project will be created in the Project Explorer window of SDK.

www.xilinx.com/university SP3E 2-11

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

Figure 3. Use Existing Board Support Package

6-2-5. Select TestApp in the project view, right-click, and select Import.

6-2-6. Expand General category and double-click on File System.

6-2-7. Browse to c:\xup\embedded\source.

6-2-8. Select lab2.c and click Finish.

A snippet of the source code is shown in Figure 4.

SP3E 2-12 www.xilinx.com/university

xup@xilinx.com

Lab Workbook Adding IP to a Hardware Design Lab

Figure 4. Snippet of source code.

6-3. Set build setting to no optimization and generate linker script which targets

the application to the ilmb and dlmb memories as well as have 400 bytes of

heap and stack each.

6-3-1. Select TestApp project, right-click, and select C/C++ Build Settings.

6-3-2. Select Optimization option of the MicroBlaze gcc compiler in the Tool Settings tab and make

sure that the Optimization Level is set to None (-O0) as we have a software loop acting as a

delay loop and we do not want it to be optimized away.

www.xilinx.com/university SP3E 2-13

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

Figure 5. Setting the Compiler Settings

6-3-3. Select TestApp, right-click and select Generate Linker Script.

6-3-4. Target everything to ilmb and dlmb memories, set heap and stack to 400 bytes each, click

Generate and click Yes.

SP3E 2-14 www.xilinx.com/university

xup@xilinx.com

Lab Workbook Adding IP to a Hardware Design Lab

Figure 6. Setting Linker Script

Verify the Design in Hardware Step 7

7-1. Download the bitstream to the Spartan-3E starter kit.

7-1-1. Connect and power up the Spartan-3E starter kit.

7-1-2. Start a Hyper Terminal session

Baud rate: 115200

Data bits: 8

Parity: none

Stop bits: 1

Flow control: none

7-1-3. Select Xilinx Tools Program FPGA in SDK.

7-1-4. Click on drop-down button and select Testapp.elf file.

www.xilinx.com/university SP3E 2-15

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

Figure 17. Selecting Application

7-1-5. Click Program.

The elf file and the system.bit file will be combined into download.bit file which will then be

downloaded to program the FPGA.

Note: Once the bitstream is downloaded, you should see the DONE LED ON and a message

displayed in Hyper Terminal as shown in Figure 18.

Figure 18. Screen Shot after the Bitstream Downloading

7-1-6. After pressing the buttons and toggling the switches, and you should see the corresponding

values being displayed on the Hyper Terminal (Figure 19).

Figure 19. Push button and DIP switch status displayed on Hyper Terminal

SP3E 2-16 www.xilinx.com/university

xup@xilinx.com

Lab Workbook Adding IP to a Hardware Design Lab

7-1-7. Disconnect and close the Hyper Terminal window, and also close SDK and XPS.

Conclusion

GPIO peripherals were added from the IP catalog and connected to a MicroBlaze system that was

created in the first lab. The peripherals were configured and external FPGA connections were established.

Pin location constraints were made in the UCF file to connect the peripherals to push buttons and DIP

switches on the Spartan-3E starter kit.

In future labs in this course, you will learn how to add user cores, add software to the system, debug the

software, and verify the functionality of the completed design by using a Spartan-3E starter kit.

Answer

1. Complete the following:

Number of external ports: 20

Number of external ports that are output: 12

Number of external ports that are input: 5

Number of external ports that are bidirectional: 3

2. List the instances to which the clk_s is connected:

clock_generator_0

List the instances connected to the mb_plb bus:

microblaze_0, DDR_SDRAM, mdm_0, LEDs_8Bit, push, dip and RS232_DCE

3. Draw the address map of the system, providing instance names. You can sort the peripheral

addresses by base address from the Addresses tab of the Add/Edit Cores (dialog) box.

0x00000000 - 0x00001fff dlmb, llmb

unused

0x81400000 - 0x8140ffff push

0x81420000 - 0x8142ffff dip

0x81440000 - 0x8144ffff LEDs_8Bit

0x84000000 - 0x8400ffff RS232_DCE

0x84400000 - 0x8440ffff mdm_0

0x8c000000 - 0x8fffffff DDR_SDRAM

www.xilinx.com/university SP3E 2-17

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

Completed MHS File

# ##############################################################################

# Created by Base System Builder Wizard for Xilinx EDK 13.2 Build EDK_O.61xd

# Tue Jul 12 06:55:41 2011

# Target Board: Xilinx Spartan-3E Starter Board Rev D

# Family: spartan3e

# Device: XC3S500e

# Package: FG320

# Speed Grade: -4

# Processor number: 1

# Processor 1: microblaze_0

# System clock frequency: 50.0

# Debug Interface: On-Chip HW Debug Module

# ##############################################################################

PARAMETER VERSION = 2.1.0

PORT fpga_0_RS232_DCE_RX_pin = fpga_0_RS232_DCE_RX_pin, DIR = I

PORT fpga_0_RS232_DCE_TX_pin = fpga_0_RS232_DCE_TX_pin, DIR = O

PORT fpga_0_LEDs_8Bit_GPIO_IO_O_pin = fpga_0_LEDs_8Bit_GPIO_IO_O_pin, DIR = O, VEC =

[0:7]

PORT fpga_0_DDR_SDRAM_DDR_Clk_pin = fpga_0_DDR_SDRAM_DDR_Clk_pin, DIR = O

PORT fpga_0_DDR_SDRAM_DDR_Clk_n_pin = fpga_0_DDR_SDRAM_DDR_Clk_n_pin, DIR = O

PORT fpga_0_DDR_SDRAM_DDR_CE_pin = fpga_0_DDR_SDRAM_DDR_CE_pin, DIR = O

PORT fpga_0_DDR_SDRAM_DDR_CS_n_pin = fpga_0_DDR_SDRAM_DDR_CS_n_pin, DIR = O

PORT fpga_0_DDR_SDRAM_DDR_RAS_n_pin = fpga_0_DDR_SDRAM_DDR_RAS_n_pin, DIR = O

PORT fpga_0_DDR_SDRAM_DDR_CAS_n_pin = fpga_0_DDR_SDRAM_DDR_CAS_n_pin, DIR = O

PORT fpga_0_DDR_SDRAM_DDR_WE_n_pin = fpga_0_DDR_SDRAM_DDR_WE_n_pin, DIR = O

PORT fpga_0_DDR_SDRAM_DDR_BankAddr_pin = fpga_0_DDR_SDRAM_DDR_BankAddr_pin, DIR =

O, VEC = [1:0]

PORT fpga_0_DDR_SDRAM_DDR_Addr_pin = fpga_0_DDR_SDRAM_DDR_Addr_pin, DIR = O, VEC =

[12:0]

PORT fpga_0_DDR_SDRAM_DDR_DQ_pin = fpga_0_DDR_SDRAM_DDR_DQ_pin, DIR = IO, VEC =

[15:0]

PORT fpga_0_DDR_SDRAM_DDR_DM_pin = fpga_0_DDR_SDRAM_DDR_DM_pin, DIR = O, VEC =

[1:0]

PORT fpga_0_DDR_SDRAM_DDR_DQS_pin = fpga_0_DDR_SDRAM_DDR_DQS_pin, DIR = IO, VEC

= [1:0]

PORT fpga_0_DDR_SDRAM_ddr_dqs_div_io_pin = fpga_0_DDR_SDRAM_ddr_dqs_div_io_pin, DIR =

IO

PORT fpga_0_clk_1_sys_clk_pin = CLK_S, DIR = I, SIGIS = CLK, CLK_FREQ = 50000000

PORT fpga_0_rst_1_sys_rst_pin = sys_rst_s, DIR = I, SIGIS = RST, RST_POLARITY = 1

PORT dip_GPIO_IO_I_pin = dip_GPIO_IO_I, DIR = I, VEC = [0:3]

PORT push_GPIO_IO_I_pin = push_GPIO_IO_I, DIR = I, VEC = [0:3]

BEGIN microblaze

PARAMETER INSTANCE = microblaze_0

PARAMETER C_AREA_OPTIMIZED = 1

PARAMETER C_USE_BARREL = 1

PARAMETER C_DEBUG_ENABLED = 1

PARAMETER HW_VER = 8.20.a

BUS_INTERFACE DLMB = dlmb

BUS_INTERFACE ILMB = ilmb

BUS_INTERFACE DPLB = mb_plb

BUS_INTERFACE IPLB = mb_plb

SP3E 2-18 www.xilinx.com/university

xup@xilinx.com

Lab Workbook Adding IP to a Hardware Design Lab

BUS_INTERFACE DEBUG = microblaze_0_mdm_bus

PORT MB_RESET = mb_reset

END

BEGIN plb_v46

PARAMETER INSTANCE = mb_plb

PARAMETER HW_VER = 1.05.a

PORT PLB_Clk = clk_50_0000MHz

PORT SYS_Rst = sys_bus_reset

END

BEGIN lmb_v10

PARAMETER INSTANCE = ilmb

PARAMETER HW_VER = 2.00.b

PORT LMB_Clk = clk_50_0000MHz

PORT SYS_Rst = sys_bus_reset

END

BEGIN lmb_v10

PARAMETER INSTANCE = dlmb

PARAMETER HW_VER = 2.00.b

PORT LMB_Clk = clk_50_0000MHz

PORT SYS_Rst = sys_bus_reset

END

BEGIN lmb_bram_if_cntlr

PARAMETER INSTANCE = dlmb_cntlr

PARAMETER HW_VER = 3.00.b

PARAMETER C_BASEADDR = 0x00000000

PARAMETER C_HIGHADDR = 0x00001fff

BUS_INTERFACE SLMB = dlmb

BUS_INTERFACE BRAM_PORT = dlmb_port

END

BEGIN lmb_bram_if_cntlr

PARAMETER INSTANCE = ilmb_cntlr

PARAMETER HW_VER = 3.00.b

PARAMETER C_BASEADDR = 0x00000000

PARAMETER C_HIGHADDR = 0x00001fff

BUS_INTERFACE SLMB = ilmb

BUS_INTERFACE BRAM_PORT = ilmb_port

END

BEGIN bram_block

PARAMETER INSTANCE = lmb_bram

PARAMETER HW_VER = 1.00.a

BUS_INTERFACE PORTA = ilmb_port

BUS_INTERFACE PORTB = dlmb_port

END

BEGIN xps_uartlite

PARAMETER INSTANCE = RS232_DCE

PARAMETER C_BAUDRATE = 115200

PARAMETER C_DATA_BITS = 8

PARAMETER C_USE_PARITY = 0

PARAMETER C_ODD_PARITY = 0

PARAMETER HW_VER = 1.02.a

PARAMETER C_BASEADDR = 0x84000000

www.xilinx.com/university SP3E 2-19

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

PARAMETER C_HIGHADDR = 0x8400ffff

BUS_INTERFACE SPLB = mb_plb

PORT RX = fpga_0_RS232_DCE_RX_pin

PORT TX = fpga_0_RS232_DCE_TX_pin

END

BEGIN xps_gpio

PARAMETER INSTANCE = LEDs_8Bit

PARAMETER C_ALL_INPUTS = 0

PARAMETER C_GPIO_WIDTH = 8

PARAMETER C_INTERRUPT_PRESENT = 0

PARAMETER C_IS_DUAL = 0

PARAMETER HW_VER = 2.00.a

PARAMETER C_BASEADDR = 0x81440000

PARAMETER C_HIGHADDR = 0x8144ffff

BUS_INTERFACE SPLB = mb_plb

PORT GPIO_IO_O = fpga_0_LEDs_8Bit_GPIO_IO_O_pin

END

BEGIN mpmc

PARAMETER INSTANCE = DDR_SDRAM

PARAMETER C_NUM_PORTS = 1

PARAMETER C_SPECIAL_BOARD = S3E_STKIT

PARAMETER C_MEM_TYPE = DDR

PARAMETER C_MEM_PARTNO = MT46V32M16-6

PARAMETER C_MEM_DATA_WIDTH = 16

PARAMETER C_PIM0_BASETYPE = 2

PARAMETER HW_VER = 6.04.a

PARAMETER C_MPMC_BASEADDR = 0x8c000000

PARAMETER C_MPMC_HIGHADDR = 0x8fffffff

BUS_INTERFACE SPLB0 = mb_plb

PORT MPMC_Clk0 = clk_100_0000MHzDCM0

PORT MPMC_Clk90 = clk_100_0000MHz90DCM0

PORT MPMC_Rst = sys_periph_reset

PORT DDR_Clk = fpga_0_DDR_SDRAM_DDR_Clk_pin

PORT DDR_Clk_n = fpga_0_DDR_SDRAM_DDR_Clk_n_pin

PORT DDR_CE = fpga_0_DDR_SDRAM_DDR_CE_pin

PORT DDR_CS_n = fpga_0_DDR_SDRAM_DDR_CS_n_pin

PORT DDR_RAS_n = fpga_0_DDR_SDRAM_DDR_RAS_n_pin

PORT DDR_CAS_n = fpga_0_DDR_SDRAM_DDR_CAS_n_pin

PORT DDR_WE_n = fpga_0_DDR_SDRAM_DDR_WE_n_pin

PORT DDR_BankAddr = fpga_0_DDR_SDRAM_DDR_BankAddr_pin

PORT DDR_Addr = fpga_0_DDR_SDRAM_DDR_Addr_pin

PORT DDR_DQ = fpga_0_DDR_SDRAM_DDR_DQ_pin

PORT DDR_DM = fpga_0_DDR_SDRAM_DDR_DM_pin

PORT DDR_DQS = fpga_0_DDR_SDRAM_DDR_DQS_pin

PORT DDR_DQS_Div_O = fpga_0_DDR_SDRAM_ddr_dqs_div_io_pin

PORT DDR_DQS_Div_I = fpga_0_DDR_SDRAM_ddr_dqs_div_io_pin

END

BEGIN clock_generator

PARAMETER INSTANCE = clock_generator_0

PARAMETER C_CLKIN_FREQ = 50000000

PARAMETER C_CLKOUT0_FREQ = 100000000

PARAMETER C_CLKOUT0_PHASE = 90

PARAMETER C_CLKOUT0_GROUP = DCM0

PARAMETER C_CLKOUT0_BUF = TRUE

PARAMETER C_CLKOUT1_FREQ = 100000000

SP3E 2-20 www.xilinx.com/university

xup@xilinx.com

Lab Workbook Adding IP to a Hardware Design Lab

PARAMETER C_CLKOUT1_PHASE = 0

PARAMETER C_CLKOUT1_GROUP = DCM0

PARAMETER C_CLKOUT1_BUF = TRUE

PARAMETER C_CLKOUT2_FREQ = 50000000

PARAMETER C_CLKOUT2_PHASE = 0

PARAMETER C_CLKOUT2_GROUP = NONE

PARAMETER C_CLKOUT2_BUF = TRUE

PARAMETER C_EXT_RESET_HIGH = 1

PARAMETER HW_VER = 4.02.a

PORT CLKIN = CLK_S

PORT CLKOUT0 = clk_100_0000MHz90DCM0

PORT CLKOUT1 = clk_100_0000MHzDCM0

PORT CLKOUT2 = clk_50_0000MHz

PORT RST = sys_rst_s

PORT LOCKED = Dcm_all_locked

END

BEGIN mdm

PARAMETER INSTANCE = mdm_0

PARAMETER C_MB_DBG_PORTS = 1

PARAMETER C_USE_UART = 1

PARAMETER HW_VER = 2.00.b

PARAMETER C_BASEADDR = 0x84400000

PARAMETER C_HIGHADDR = 0x8440ffff

BUS_INTERFACE SPLB = mb_plb

BUS_INTERFACE MBDEBUG_0 = microblaze_0_mdm_bus

PORT Debug_SYS_Rst = Debug_SYS_Rst

END

BEGIN proc_sys_reset

PARAMETER INSTANCE = proc_sys_reset_0

PARAMETER C_EXT_RESET_HIGH = 1

PARAMETER HW_VER = 3.00.a

PORT Slowest_sync_clk = clk_50_0000MHz

PORT Ext_Reset_In = sys_rst_s

PORT MB_Debug_Sys_Rst = Debug_SYS_Rst

PORT Dcm_locked = Dcm_all_locked

PORT MB_Reset = mb_reset

PORT Bus_Struct_Reset = sys_bus_reset

PORT Peripheral_Reset = sys_periph_reset

END

BEGIN xps_gpio

PARAMETER INSTANCE = dip

PARAMETER HW_VER = 2.00.a

PARAMETER C_BASEADDR = 0x81420000

PARAMETER C_HIGHADDR = 0x8142ffff

PARAMETER C_GPIO_WIDTH = 4

PARAMETER C_ALL_INPUTS = 1

BUS_INTERFACE SPLB = mb_plb

PORT GPIO_IO_I = dip_GPIO_IO_I

END

BEGIN xps_gpio

PARAMETER INSTANCE = push

PARAMETER HW_VER = 2.00.a

PARAMETER C_BASEADDR = 0x81400000

PARAMETER C_HIGHADDR = 0x8140ffff

www.xilinx.com/university SP3E 2-21

xup@xilinx.com

Adding IP to a Hardware Design Lab Lab Workbook

PARAMETER C_GPIO_WIDTH = 4

PARAMETER C_ALL_INPUTS = 1

BUS_INTERFACE SPLB = mb_plb

PORT GPIO_IO_I = push_GPIO_IO_I

END

SP3E 2-22 www.xilinx.com/university

xup@xilinx.com

Вам также может понравиться

- Lab 2Документ21 страницаLab 2Văn Việt VõОценок пока нет

- Lab 2: Adding Ip To A Hardware Design Lab: Targeting Microblaze™ On The Spartan™-3E KitДокумент21 страницаLab 2: Adding Ip To A Hardware Design Lab: Targeting Microblaze™ On The Spartan™-3E KitAnil Kumar KadiyalaОценок пока нет

- Writing Basic Software Applications Lab: Figure 1. Design Updated From Previous LabДокумент21 страницаWriting Basic Software Applications Lab: Figure 1. Design Updated From Previous Labaditya kumarОценок пока нет

- FPGA Lab Journal: Verilog Experiments on Comparators and AddersДокумент98 страницFPGA Lab Journal: Verilog Experiments on Comparators and AddersAFTAB ALIОценок пока нет

- Lab05 PDFДокумент20 страницLab05 PDFaditya kumarОценок пока нет

- Lab 3Документ16 страницLab 3Văn Việt VõОценок пока нет

- Lab 3Документ14 страницLab 3Kyoung-min SongОценок пока нет

- MicroBlaze EDK TutorialДокумент69 страницMicroBlaze EDK Tutorialsreedhar_vkОценок пока нет

- Lab 04Документ21 страницаLab 04karthikp207Оценок пока нет

- 02 Creating HW LabДокумент5 страниц02 Creating HW LabgpuonlineОценок пока нет

- Lab - 06 - Timing Simulation & Design Implementation (Combinational Logic)Документ11 страницLab - 06 - Timing Simulation & Design Implementation (Combinational Logic)Muhammad SaudОценок пока нет

- Program Controlled I/OДокумент7 страницProgram Controlled I/ODavid RenzoОценок пока нет

- Embedded System Design Using IP Integrator: Figure 1. Processor Design of This LabДокумент24 страницыEmbedded System Design Using IP Integrator: Figure 1. Processor Design of This LabChandan MalleshОценок пока нет

- Lab 03Документ23 страницыLab 03karthikp207Оценок пока нет

- Smart Home Control System LabView PrototypeДокумент5 страницSmart Home Control System LabView PrototypeElaine LaLaОценок пока нет

- Workbook - EcoStruxure Building Operation 2.0 V1.4Документ144 страницыWorkbook - EcoStruxure Building Operation 2.0 V1.4huynh ngoc hoi Huynh100% (1)

- Lab 05Документ25 страницLab 05karthikp207Оценок пока нет

- Tutorial 1 Introduction To VHDL, and ISE 10.1 On The Digilent Spartan-3E Starter Kit BoardДокумент17 страницTutorial 1 Introduction To VHDL, and ISE 10.1 On The Digilent Spartan-3E Starter Kit BoardpwjfjfjklfdsОценок пока нет

- VHDL FPGA Tutorial for BeginnersДокумент12 страницVHDL FPGA Tutorial for BeginnersArdser AvicoОценок пока нет

- Test Sistem EtherNetIP AOI RSLogix5000 Integration Manual v1.3Документ66 страницTest Sistem EtherNetIP AOI RSLogix5000 Integration Manual v1.3rguzmanabundisОценок пока нет

- Microblaze Vivado TutorialДокумент24 страницыMicroblaze Vivado Tutorialashish jhaОценок пока нет

- EE326 Lab 2Документ25 страницEE326 Lab 2krishneelОценок пока нет

- Xup Building Basic Elements LabДокумент18 страницXup Building Basic Elements LabGibin GeorgeОценок пока нет

- Lab4 Intro & Lab4Документ20 страницLab4 Intro & Lab4Johanson CamasuraОценок пока нет

- ITSC203_Lab3bДокумент10 страницITSC203_Lab3bktftj5ydfvОценок пока нет

- Code Snippets Updated For Blender 254Документ140 страницCode Snippets Updated For Blender 254marcosocfОценок пока нет

- Lab 2-1 Develop Software Nios PIOДокумент11 страницLab 2-1 Develop Software Nios PIONguyên Trịnh Vũ ĐăngОценок пока нет

- Lab 2 Introduction To VHDL and Nexys2Документ18 страницLab 2 Introduction To VHDL and Nexys2Timmy OcantoОценок пока нет

- Lab RequirementsДокумент27 страницLab Requirementsthuan phamОценок пока нет

- SPCC AssignmentДокумент6 страницSPCC AssignmentKennethОценок пока нет

- Creating AXI-LITE 'Custom IP' in Vivado LabДокумент33 страницыCreating AXI-LITE 'Custom IP' in Vivado Labwwahib2Оценок пока нет

- Instruction of Preparation For The Course On - Remote Sensing Technology and Data ProcessingДокумент9 страницInstruction of Preparation For The Course On - Remote Sensing Technology and Data ProcessingFrinaldi SyafrilОценок пока нет

- Introduction To The Altera SOPC BuilderДокумент29 страницIntroduction To The Altera SOPC BuilderAmir PorterОценок пока нет

- Assignment 4Документ15 страницAssignment 4Sergio SanabriaОценок пока нет

- Lab 06Документ33 страницыLab 06karthikp207Оценок пока нет

- FPGA Course4 CapstoneProjectGuideModule3Документ63 страницыFPGA Course4 CapstoneProjectGuideModule3Oluwatimileyin Michael OlagunjuОценок пока нет

- PSoC Lab 0Документ9 страницPSoC Lab 0خالدمحمدОценок пока нет

- SDN ExerciseДокумент12 страницSDN ExerciseSandeep ReddyОценок пока нет

- Creating A Processor System LabДокумент28 страницCreating A Processor System LabAnvit NegiОценок пока нет

- Cip Safety Pf527 Hott 2015 v1 - 2 Mar 18 2015Документ16 страницCip Safety Pf527 Hott 2015 v1 - 2 Mar 18 2015ipasa100% (1)

- Xps Tutorial 21Документ12 страницXps Tutorial 21Quoc AnhОценок пока нет

- Hardware Simulator TutorialДокумент49 страницHardware Simulator TutorialManuel Emilio Gonzalez SantanaОценок пока нет

- Starting a Project in SBOДокумент144 страницыStarting a Project in SBORoni Araujo NaniniОценок пока нет

- Enocean Sensor Kit: Bringing Home Automation To The Raspberry PiДокумент17 страницEnocean Sensor Kit: Bringing Home Automation To The Raspberry PiYousri BoughamouraОценок пока нет

- Kinect Installation GuideДокумент7 страницKinect Installation GuideOscar GarciaОценок пока нет

- En ENetwork IPTM v4040Документ38 страницEn ENetwork IPTM v4040abdelhf1Оценок пока нет

- Programming Industrial Embedded Systems, 2017./2018.: Laboratory Exercise 1Документ69 страницProgramming Industrial Embedded Systems, 2017./2018.: Laboratory Exercise 1_download_only_Оценок пока нет

- CCNA Exploration 4.0.4.0 Instructor Packet Tracer Lab ManualДокумент38 страницCCNA Exploration 4.0.4.0 Instructor Packet Tracer Lab ManualshaytoonballaОценок пока нет

- 2IN35 - VLSI Programming - Lab Work: Information & PreparationДокумент5 страниц2IN35 - VLSI Programming - Lab Work: Information & Preparationbkrishna_888846Оценок пока нет

- Python Programming PDF Myanmar PDF Files DownloadДокумент6 страницPython Programming PDF Myanmar PDF Files DownloadNighty hezzОценок пока нет

- Vlsi Manual 2013-2014Документ36 страницVlsi Manual 2013-2014hr_suresh_kОценок пока нет

- Embedded Linux Handson Tutorial ZedBoardДокумент46 страницEmbedded Linux Handson Tutorial ZedBoardecd4282003Оценок пока нет

- Embedded Systems Design with Platform FPGAs: Principles and PracticesОт EverandEmbedded Systems Design with Platform FPGAs: Principles and PracticesРейтинг: 5 из 5 звезд5/5 (1)

- Introduction to Python Programming: Learn Coding with Hands-On Projects for BeginnersОт EverandIntroduction to Python Programming: Learn Coding with Hands-On Projects for BeginnersОценок пока нет

- Integrated Circuit Design CAD Tool Information - Cadence - CAD PDFДокумент339 страницIntegrated Circuit Design CAD Tool Information - Cadence - CAD PDFrakheep123Оценок пока нет

- Linear Tech - LTSPICE Getting Started GuideДокумент53 страницыLinear Tech - LTSPICE Getting Started GuideSyed Muneeb BukhariОценок пока нет

- Quartus Tutorial 1Документ27 страницQuartus Tutorial 1aditya kumarОценок пока нет

- Ranking H-Index Publisher Conference Details Country DeadlineДокумент15 страницRanking H-Index Publisher Conference Details Country Deadlineaditya kumarОценок пока нет

- Lab03 PDFДокумент21 страницаLab03 PDFaditya kumarОценок пока нет

- AppendixC QuartusДокумент24 страницыAppendixC QuartusNguyen Duc TaiОценок пока нет

- Quartus Licensing InstructionДокумент1 страницаQuartus Licensing Instructionaditya kumarОценок пока нет

- Lab 01Документ21 страницаLab 01aditya kumarОценок пока нет

- Teshome AbabuДокумент96 страницTeshome AbabuaqpcarlitosОценок пока нет

- Lab06 PDFДокумент17 страницLab06 PDFaditya kumarОценок пока нет

- Hickok 09 MicroBlazeInterruptsEDKДокумент6 страницHickok 09 MicroBlazeInterruptsEDKRishi BGОценок пока нет

- Amba 99Документ488 страницAmba 99aditya kumarОценок пока нет

- Xps Spi PDFДокумент38 страницXps Spi PDFaditya kumarОценок пока нет

- Amba 99Документ488 страницAmba 99aditya kumarОценок пока нет

- Using and Creating Interrupt-Based Systems: DefinitionsДокумент37 страницUsing and Creating Interrupt-Based Systems: Definitionsaditya kumarОценок пока нет

- Hickok 09 MicroBlazeInterruptsEDKДокумент6 страницHickok 09 MicroBlazeInterruptsEDKRishi BGОценок пока нет

- Presentation of The LordДокумент1 страницаPresentation of The LordSarah JonesОценок пока нет

- A - Bahasa Inggris-DikonversiДокумент96 страницA - Bahasa Inggris-DikonversiArie PurnamaОценок пока нет

- Request Letter To EDC Used PE PipesДокумент1 страницаRequest Letter To EDC Used PE PipesBLGU Lake DanaoОценок пока нет

- ViscosimetroДокумент7 страницViscosimetroAndres FernándezОценок пока нет

- Instruction/Special Maintenance Instruction (IN/SMI)Документ2 страницыInstruction/Special Maintenance Instruction (IN/SMI)ANURAJM44Оценок пока нет

- Iqvia PDFДокумент1 страницаIqvia PDFSaksham DabasОценок пока нет

- Maths Lit 2014 ExamplarДокумент17 страницMaths Lit 2014 ExamplarAnymore Ndlovu0% (1)

- 3 0 Visual Weld InspectorДокумент74 страницы3 0 Visual Weld InspectorVincent Sofia RaphaelОценок пока нет

- Gigahertz company background and store locationsДокумент1 страницаGigahertz company background and store locationsjay BearОценок пока нет

- Manual de Instalare Centrala de Incendiu Adresabila 1-4 Bucle Teletek IRIS PRO 250bucla 96 Zone 10000 EvenimenteДокумент94 страницыManual de Instalare Centrala de Incendiu Adresabila 1-4 Bucle Teletek IRIS PRO 250bucla 96 Zone 10000 EvenimenteAlexandra DumitruОценок пока нет

- Ultrasonic Inspection Standards for Wrought MetalsДокумент44 страницыUltrasonic Inspection Standards for Wrought Metalsdomsoneng100% (1)

- Incident Report Form: RPSG-IMS-F-24 Accident and Investigation Form 5AДокумент2 страницыIncident Report Form: RPSG-IMS-F-24 Accident and Investigation Form 5ARocky BisОценок пока нет

- VSP-12Way - Is Rev.03Документ55 страницVSP-12Way - Is Rev.03Marcelo AlmeidaОценок пока нет

- WM3000U - WM3000 I: Measuring Bridges For Voltage Transformers and Current TransformersДокумент4 страницыWM3000U - WM3000 I: Measuring Bridges For Voltage Transformers and Current TransformersEdgar JimenezОценок пока нет

- Human Resource Management: Chapter One-An Overview of Advanced HRMДокумент45 страницHuman Resource Management: Chapter One-An Overview of Advanced HRMbaba lakeОценок пока нет

- Sample Feedback IELTS Academic Task 1 Band 6 Double GraphДокумент3 страницыSample Feedback IELTS Academic Task 1 Band 6 Double GraphalinaemmeaОценок пока нет

- Maintenance: ASU-600 SeriesДокумент54 страницыMaintenance: ASU-600 SeriesMichael Maluenda Castillo100% (2)

- AP Statistics - 2014-2015 Semester 1 Test 3Документ4 страницыAP Statistics - 2014-2015 Semester 1 Test 3Camden BickelОценок пока нет

- DOLE AEP Rule 2017Документ2 страницыDOLE AEP Rule 2017unhoopterenceОценок пока нет

- Forms of Business Organization: Sole Proprietorship, Partnership, Corporation, CooperativesДокумент17 страницForms of Business Organization: Sole Proprietorship, Partnership, Corporation, CooperativesSanti BuliachОценок пока нет

- LeasingДокумент2 страницыLeasingfollow_da_great100% (2)

- Article 4Документ31 страницаArticle 4Abdul OGОценок пока нет

- BC Specialty Foods DirectoryДокумент249 страницBC Specialty Foods Directoryjcl_da_costa6894Оценок пока нет

- English 8-Q3-M3Документ18 страницEnglish 8-Q3-M3Eldon Julao0% (1)

- 63db2cf62042802 Budget Eco SurveyДокумент125 страниц63db2cf62042802 Budget Eco SurveyNehaОценок пока нет

- Hollow lateral extrusion process for tubular billetsДокумент7 страницHollow lateral extrusion process for tubular billetsjoaopedrosousaОценок пока нет

- Proprietar Utilizator Nr. Crt. Numar Inmatriculare Functie Utilizator Categorie AutovehiculДокумент3 страницыProprietar Utilizator Nr. Crt. Numar Inmatriculare Functie Utilizator Categorie Autovehicultranspol2023Оценок пока нет

- Building A Computer AssignmentДокумент3 страницыBuilding A Computer AssignmentRajaughn GunterОценок пока нет

- Savable Data Page - Its Configuration, Usage & ExecutionДокумент20 страницSavable Data Page - Its Configuration, Usage & ExecutionsurmanpaОценок пока нет

- Book Two - 2da. EdiciónДокумент216 страницBook Two - 2da. EdiciónJhoselainys PachecoОценок пока нет