Академический Документы

Профессиональный Документы

Культура Документы

A4955 Datasheet

Загружено:

Shah ZaibОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

A4955 Datasheet

Загружено:

Shah ZaibАвторское право:

Доступные форматы

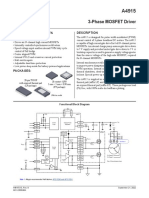

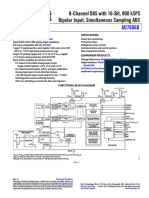

A4955

Full-Bridge PWM Gate Driver

FEATURES AND BENEFITS DESCRIPTION

• Standard IN1/IN2 control logic Designed for pulse-width-modulated (PWM) control of DC

• Overcurrent indication motors, the A4955 is capable of 50 V operation and provides

• Adjustable off-time and blank-time gate drive for an all N-channel external MOSFET bridge.

• Adjustable current limit

Input terminals are provided for use in controlling the speed and

• Adjustable gate drive

direction of a DC motor with externally applied PWM control

• Synchronous rectification

signals. Internal synchronous rectification control circuitry is

• Internal UVLO

provided to lower power dissipation during PWM operation.

• Crossover-current protection

• MOSFET VDS protection Internal circuit protection includes VDS protection, thermal

• Voltage output proportional to load current shutdown with hysteresis, undervoltage monitoring of VBB,

• A4955K is AEC-Q100 Grade 1 qualified and crossover-current protection.

• Commercial temperature grade (A4955G: –40°C to 105°C)

The A4955 is supplied in a low-profile 4 × 4 mm, 20-contact

• Automotive temperature grade (A4955K: –40°C to 125°C)

QFN package (suffix “ES”) and a 20-lead eTSSOP (suffix

“LP”), both with exposed thermal pad.

PACKAGES:

20-Pin QFN (suffix “ES”) 20-Pin eTSSOP (suffix “LP”)

with Exposed Thermal Pad with Exposed Thermal Pad

Not to scale

0.1 µF

CP1

CP2

TSD UVLO

VIN

CHARGE PUMP VCP

ISET 0.1 µF

VBB

VREG

RC VCP

STANDBY GHA GHA

SLEEPn GHB

SB

IN1 Control GATE

Logic DRIVE

IN2

SA SA

OCLn

OCL

GLA GLA

System Filter

GLB

Controller optional

AIOUT HOLD ×10

RSENSE

Inrush current limit =

+ SENSE

VREF/10 * RSENSE

–

VREF ÷10

GND

Functional Block Diagram

A4955-DS, Rev. 2 November 30, 2017

MCO-0000347

A4955 Full-Bridge PWM Gate Driver

SPECIFICATIONS

SELECTION GUIDE

Part Number Ambient Temperature Range Packing Notes

A4955GESTR-T –40°C to 105°C 1500 pieces per 7-inch reel

A4955GLPTR-T –40°C to 105°C 4000 pieces per 13-inch reel

A4955KLPTR-T –40°C to 125°C 4000 pieces per 13-inch reel AEC-Q100 Qualified

ABSOLUTE MAXIMUM RATINGS

Characteristic Symbol Notes Rating Unit

Load Supply Voltage VBB 50 V

Motor Outputs VSx VSx – VSENSE; VBB – VSx –2 to 52 V

–0.5 to 0.5 V

SENSE VSENSE

tW < 500 ns –4 to 4 V

OCLn VOCLn –0.3 to 5.5 V

VREF VREF –0.3 to 5.5 V

ISET VISET –0.3 to 5.5 V

AIOUT VAIOUT –0.3 to 5.5 V

Logic Input Voltage Range VIN SLEEPn, IN1, IN2 –0.3 to 5.5 V

Junction Temperature TJ 150 °C

Storage Temperature Range TS –55 to 150 °C

Range G –40 to 105 °C

Operating Temperature Range TA

Range K –40 to 125 °C

THERMAL CHARACTERISTICS (may require derating at maximum conditions; see application information)

Characteristic Symbol Test Conditions* Value Unit

ES Package 4-Layer PCB, 1 in.2 copper 37 °C/W

RθJA

LP Package 4-Layer PCB, 1 in.2 copper 28 °C/W

*Power dissipation and thermal limits must be observed.

Allegro MicroSystems, LLC 2

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A4955 Full-Bridge PWM Gate Driver

VREF

OCLn

IN1

IN2

RC

GND 1 20 CP1

20

19

18

17

16

AIOUT 2 19 VBB

ISET 1 15 AIOUT OCLn 3 18 CP2

SLEEPn 2 14 GND VREF 4 17 VCP

SENSE 3 PAD 13 CP1 IN2 5 16 SA

PAD

GLB 4 12 VBB 6 15

IN1 GHA

GLA 5 11 CP2

RC 7 14 SB

10

8 13

6

9

7

ISET GHB

GHB

SB

GHA

SA

VCP

SLEEPn 9 12 GLA

SENSE 10 11 GLB

Package ES, 20-Pin QFN Pinouts Package LP, 20-Pin eTSSOP Pinouts

Terminal List Table

Number

Name Function

ES Package LP Package

ISET 1 8 Terminal to set gate drive current

SLEEPn 2 9 Sleep input, active low

SENSE 3 10 Sense resistor connection, low-side gate return

GLB 4 11 Gate driver

GLA 5 12 Gate driver

GHB 6 13 Gate driver

SB 7 14 High-side bridge reference

GHA 8 15 Gate driver

SA 9 16 High-side bridge reference

VCP 10 17 Charge pump reservoir cap connection

CP2 11 18 Charge pump terminal

VBB 12 19 Supply voltage

CP1 13 20 Charge pump terminal

GND 14 1 Ground

AIOUT 15 2 Analog output proportional to VSENSE

OCLn 16 3 OCP and OVP output flag, open drain

VREF 17 4 Analog OCP reference input

IN2 18 5 Digital IN2 input

IN1 19 6 Digital IN1 input

RC 20 7 Terminal to set blank- and off-time

PAD – –

Allegro MicroSystems, LLC 3

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A4955 Full-Bridge PWM Gate Driver

ELECTRICAL CHARACTERISTICS: Valid for Temperature Range G version at TJ = 25°C and

for Temperature Range K version at TJ = –40°C to 150°C, VBB = 5.5 to 50 V, unless otherwise specified

Characteristics Symbol Test Conditions Min. Typ. Max. Unit

IBB – 6 10 mA

VBB Supply Current

IBB SLEEPn = low, Standby Mode – – 5 µA

GATE DRIVE

Relative to VBB, IGATE = 200 µA, VBB = 8 to 50 V 6.5 6.8 7.5 V

High-Side Gate Drive Output VGH

Relative to VBB, IGATE = 200 µA, VBB = 5.5 V – 5.2 – V

IGATE = 200 µA, VBB = 8 to 50 V 6.5 6.8 7.5 V

Low-Side Gate Drive Output VGL

IGATE = 200 µA, VBB = 5.5 V – 5.4 – V

Gate Drive Pull-Up Current IGPU RISET = 30 kΩ; VGH = VGL = 4 V 21 30 39 mA

Gate Drive Pull-Down Current IGPD RISET = 30 kΩ; VGH = VGL = 4 V 47 68 89 mA

Dead-Time tDT – 1000 – ns

Passive Pull-Down Resistance RGPD 30 50 70 kΩ

LOGIC INPUT AND OUTPUT

Logic Output Voltage VOCLn I = 2 mA, overcurrent detected – 0.2 0.3 V

Logic Output Leakage IOCLn V = 5 V, normal operation – – 5 µA

PWM Current Limit Flag Timer tOCLn 300 500 600 µs

VIH 2.0 – – V

Logic Input Voltage VIL – – 0.8 V

VIL(SLEEPn) SLEEPn input – – 0.4 V

Logic Input Hysteresis VHYS – 320 – mV

Logic Input Pull-Down Resistor RPD 30 50 70 kΩ

VREF Input Current IVREF VREF = 2.5 V –5 <1 5 µA

VREF Input Range VREF 0 – 2.5 V

Current Gain AV VREF / VSENSE, VREF = 2.5 V 9.5 – 10.5 V/V

Input Offset, SENSE VOSSENSE –10 – 10 mV

Fixed Off-Time tOFF RRC = 30 kΩ, CRC = 1 nF – 30 – µs

Percent Fast Decay PFD Internal PWM chop – 13 – %

Blank-Time tBLK RRC = 30 kΩ, CRC = 1 nF 2.1 3 3.9 µs

Power-Up Delay tpu Time until outputs are enabled – 50 300 µs

AIOUT Gain AIOUT AIOUT/VSENSE, VSENSE = 50 to 200 mV 9 10 11 V/V

Input Offset, AIOUT VOSAIOUT –15 – 15 mV

Sample-and-Hold Accuracy VSH(ACC) – 15 – mV

Sample-and-Hold Droop Rate VDROOP – – 1 mV/µs

AIOUT Output Impedance ROUT(AIOUT) 0.75 1.00 1.45 kΩ

PROTECTION CIRCUITS

UVLO Enable Threshold VBB(UVLO) VBB rising 5.10 5.25 5.40 V

UVLO Hysteresis VBB(UVLO,HYS) 200 300 350 mV

VDS Threshold VDSTH – 2 – V

Thermal Shutdown Temperature TJTSD Temperature increasing 150 165 185 °C

Thermal Shutdown Hysteresis ΔTJ Recovery = TJTSD – ΔTJ – 30 – °C

[1] Specified limits are tested at a single temperature and assured over operating temperature range by design and characterization.

[2] Target trip level = VDSTH = VDRAIN – VSx (High Side On) or VDSTH = VSx – VSENSE (Low Side On).

Allegro MicroSystems, LLC 4

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A4955 Full-Bridge PWM Gate Driver

Control Logic

10 × VSENSE >

IN1 IN2 SLEEPn OUTA OUTB Function

VREF

x x 0 x Z Z Sleep (Standby) Mode

0 0 1 x Z Z Coast

0 1 1 false L H Reverse

1 0 1 false H L Forward

1 1 1 x L L Slow Decay SR (Brake)

0 1 1 true H/L L Internal Chop Reverse, Mixed Decay *

1 0 1 true L H/L Internal Chop Forward, Mixed Decay *

* In fast decay, outputs change to high-Z state when load current approaches zero, to prevent reversal of current.

IOCL = VREF / RSENSE / 10

I_OUT

tOCLn

OCLn

OCLn Output Flag

OCLn output function is described in the Functional Description section.

A A B B C

300 µs

AIOUT

0V

VSENSE = VREF /10

V SENSE

0V

IN 1

(IN2 = High)

AIOUT Output

A. Internal OCL chop. AIOUT holds while SENSE voltage varies during the mixed-decay off-time.

B. INx chop. AIOUT holds while SENSE voltage drops to 0 V during slow decay.

C. Slow-decay timeout. AIOUT is forced to 0 V 300 µs after ENABLE goes low.

Allegro MicroSystems, LLC 5

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A4955 Full-Bridge PWM Gate Driver

FUNCTIONAL DESCRIPTION

Device Operation The formula for determining the gate drive is:

The A4955 is designed to operate DC motors. The output drivers 900

IGATE_HS (mA) = 1.9 +

are capable of 50 V with gate-driver capability for an all N-chan- RISET (kΩ)

nel external MOSFET H-bridge. Control logic includes syn-

1700

chronous rectification to reduce power dissipation. Current limit IGATE_LS (mA) = 3.5 +

is regulated by fixed off-time pulse-width-modulated (PWM) RISET (kΩ)

control circuitry. RC

Internal PWM Current Control The RC terminal is used to set both fixed off-time and blank-time

for the internal PWM current control. Refer to the following three

Peak current is regulated by monitoring the voltage on an exter- sections to select RC component values.

nal sense resistor.

IPEAK =

VREF Fixed Off-Time Setting

(10 × RSENSE) The internal PWM current-control circuitry uses a one-shot to

control the time the drivers remain off. The one-shot off-time

When the peak current is exceeded, the source driver turns off

(tOFF) is determined by the selection of an external resistor and

for a fixed period tOFF to chop the current. The outputs operate

capacitor connected from the RC timing terminal to ground. The

in mixed-decay mode during tOFF. Refer to the Fixed Off-Time

off-time, over a range of values of CRC = 470 to 1500 pF and

Setting section to set tOFF.

RRC = 12 to 100 kΩ, is approximated by:

The internal current-sense circuit is ignored for tBLANK after tOFF = RRC × CRC + dead time

PWM transitions. The comparator output is blanked to prevent

false overcurrent detection due to reverse recovery currents of the Blank-Time Setting

clamp diodes, or switching transients related to the capacitance of

the load, or both. Refer to the Blank-Time Setting section to set This circuit blanks the output of the current-sense comparator

tBLANK. when the outputs are switched by the internal current-control

circuitry or by an external PWM chop command. The comparator

Brake blanking time, tBLANK, is determined by the selection of an exter-

nal resistor and capacitor connected from the RC timing terminal

It is important to note that the internal PWM current-control to ground, and is approximated by:

circuit will not limit the current when braking, since the current (3.6/RRC (kΩ))

does not flow through the sense resistor. The maximum current tBLANK = 2.6 µs × CRC (nF) × e

can be approximated by VBEMF / RMOTOR. Care should be taken

to ensure that the maximum ratings of the external MOSFET are Slow Decay

not exceeded in worst-case braking situations of high speed and In slow-decay mode, the low-side switch stays on and the

high inertial loads. high-side switch turns off. Due to the synchronous rectification

feature, the complementary low-side switch turns on after a dead-

ISET time.

A resistor from ISET terminal to ground sets the magnitude of

the gate current. The sink and source current ratios are fixed at

Fast Decay SR

approximately 2-to-1 where the pull-down current is approxi- In fast-decay mode, the high-side and low-side switches turn off,

mately two times the pull-up current. RISET should be between and the complementary pair of switches is turned on, effectively

15 and 150 kΩ. reversing the voltage polarity across the motor winding.

Allegro MicroSystems, LLC 6

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A4955 Full-Bridge PWM Gate Driver

Mixed Decay Charge Pump

When the peak current is reached, as set by the sense resistor and The charge pump is used to generate a supply above VBB to

voltage on VREF, the PWM current limiter initiates an off-time. drive the high-side MOSFETs. The VCP voltage is internally

The off-time is determined by the resistor and capacitor on the monitored and, in the case of a fault condition, the outputs of the

RC terminal. In mixed-decay mode, the driver will initiate a fast device are disabled.

decay, after a dead-time, for 13% of the programmed off-time.

After the fast-decay time expires, the bridge will switch to slow MOSFET VDS Protection

decay for the remaining off-time. When the bridge is operating The drain-to-source voltage is monitored across the MOSFET

in fast decay, it will internally prevent current reversal by putting any time the MOSFET is on. If the voltage across the MOSFET

the bridge in a high-Z state if the current through the sense resis- exceeds VDSTH, the bridge is disabled and latched off.

tor falls close to zero.

In order to prevent false VDS faults, the VDS monitor is blanked

OCLn Output immediately after any MOSFET is turned on. The VDS monitor

waits for a blank-time defined by the components on the RC ter-

An open-drain logic output will be driven low to indicate system

minal before monitoring the VDS level. During the off-time when

operation. The OCLn terminal is driven low under two condi-

SR is active, VDS blanking is fixed at 1 μs.

tions:

1. When the system is limiting current to value set by VREF and VDS Fault

RSENSE. Once overcurrent events are no longer detected, the When a VDS fault occurs, and the bridge is disabled, and the

A4955 will release the indication after a time tOCLn. fault is latched, the OCLn terminal is immediately driven low.

2. When a VDS fault is detected, the OCLn terminal is driven The latch can only be reset by going into standby or by dropping

low. It is released when the fault is reset. VBB below the UVLO threshold.

The OCLn terminal, in combination with the AIOUT terminal, Standby Mode

can provide valuable information about how the system is behav-

ing: Low power standby mode is activated when SLEEPn is brought

low. Standby mode disables most of the internal circuitry, includ-

• Overcurrent events can indicate a motor stall condition, in ing the charge pump and internal regulator. When coming out of

which case the system controller can respond to the fault standby mode, the A4955 requires up to 300 μs before the outputs

condition by reducing PWM duty. When OCLn is low and the can respond to input commands.

voltage on AIOUT is greater than 0 V, the controller is actively

limiting current with the internal, fixed off-time PWM current TSD

limiter.

If the die temperature increases to approximately TTSD, the full

• In the case of a VDS fault, the OCLn terminal is also driven bridge outputs will be disabled until the internal temperature falls

low, but the AIOUT voltage will be 0 V, because the bridge below TTSD minus a hysteresis level of THYS.

has been disabled. This notifies the user that a VDS fault has

occurred and the driver has been disabled. Fault Shutdown

AIOUT In the event of a fault due to excessive junction temperature,

or low voltage on VCP or VBB, the outputs of the device are

An analog output can be used to monitor current through the disabled until the fault condition is removed. At power-up, the

external sense resistor (if used). The SENSE voltage is gained by UVLO circuit disables the drivers until the UVLO thresholds are

a factor of 10 and fed to the AIOUT terminal. A sample-and-hold exceeded.

circuit is used to capture the voltage across the sense resistor and

holds it during periods when the voltage is not representative of

the current in the motor. The AIOUT Output diagram illustrates

when the voltage is held. The held voltage will droop at a rate

equal to VDROOP. In the case of a VDS fault on the bridge, the

AIOUT terminal will be discharged to zero volts.

Allegro MicroSystems, LLC 7

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A4955 Full-Bridge PWM Gate Driver

TERMINAL CIRCUIT DIAGRAMS

IN1

SX VCP IN2

RISET

6.7 V AIOUT

VREF

SLEEPn

RC 10 V

OCLn

GND

GND

VCP

VBB GHX

8V 6.7 V

GLX SX

GND GND

SENSE

CP2

VCP CP1

8V

GND

VBB GND

GND

SENSE

VBB

56 V

GND 8V GND

GND

Allegro MicroSystems, LLC 8

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A4955 Full-Bridge PWM Gate Driver

PACKAGE OUTLINE DRAWINGS

For Reference Only – Not for Tooling Use

(Reference JEDEC MO-220WGGD)

Dimensions in millimeters

NOT TO SCALE

Exact case and lead configuration at supplier discretion within limits shown

0.30

4.00 ±0.15 0.50

20

20

0.95

1

2 A 1

2

4.00 ±0.15 2.45 4.10

2.45

21X D C

4.10

0.08 C 0.75 ±0.05

SEATING

PLANE C PCB Layout Reference View

+0.05

0.25

–0.07

0.50 BSC

+0.15

0.40

–0.10

A Terminal #1 mark area

B B Exposed thermal pad (reference only, terminal #1 identifier appearance at supplier

2.45 discretion)

2 C Reference land pattern layout (reference IPC7351 QFN50P400X400X80-21BM);

1 all pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to

meet application process requirements and PCB layout tolerances; when mounting

on a multilayer PCB, thermal vias at the exposed thermal pad land can improve

20 thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

2.45 D Coplanarity includes exposed thermal pad and terminals

ES Package, 20-Pin QFN with Exposed Thermal Pad

Allegro MicroSystems, LLC 9

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A4955 Full-Bridge PWM Gate Driver

For Reference Only – Not for Tooling Use

(Reference MO-153 ACT)

NOT TO SCALE

Dimensions in millimeters

Exact case and lead configuration at supplier discretion within limits shown

6.50 ±0.10

4.20

8º

0º

20

0.20

0.09

C

3.00 4.40 ±0.10 6.40 ±0.20

1.00 REF

0.60 ±0.15

1 2

0.25 BSC

20X C

1.20 MAX SEATING PLANE

0.10 C SEATING

PLANE GAUGE PLANE

0.30

0.65 BSC 0.15

0.19

0.00

0.45 0.65

NNNNNNN

20 YYWW

LLLLLLL

1.70

1

D Standard Branding Reference View

N = Device part number

= Supplier emblem

Y = Last two digits of year of manufacture

W = Week of manufacture

3.00 6.10 L = Lot number

A Terminal #1 mark area

B Reference land pattern layout (reference IPC7351 SOP65P640X110-21M);

all pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary

to meet application process requirements and PCB layout tolerances; when

mounting on a multilayer PCB, thermal vias at the exposed thermal pad land

can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

1 2

C Exposed thermal pad (bottom surface)

4.20

D Branding scale and appearance at supplier discretion

B PCB Layout Reference View

LP Package, 20-Pin eTSSOP with Exposed Thermal Pad

Allegro MicroSystems, LLC 10

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

A4955 Full-Bridge PWM Gate Driver

Revision History

Revision Revision Date Description of Revision

– February 12, 2015 Initial Release

Updated functional block diagram (page 1); added packing information (page 2); changed

1 July 14, 2015

references to LSS to SENSE

2 November 30, 2017 Updated ISET section (page 6)

Copyright ©2017, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to

permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that

the information being relied upon is current.

Allegro’s products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of

Allegro’s product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its

use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com

Allegro MicroSystems, LLC 11

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

Вам также может понравиться

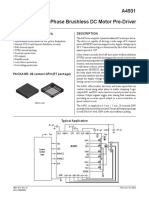

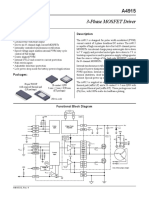

- A4915 DatasheetДокумент17 страницA4915 Datasheetkarol1301Оценок пока нет

- A4950 DatasheetДокумент9 страницA4950 DatasheetIndra KurniawanОценок пока нет

- A4942-DatasheetДокумент13 страницA4942-DatasheetLee HoonОценок пока нет

- Three-Phase Sensorless Pump Driver IC A89303: Features and Benefits DescriptionДокумент22 страницыThree-Phase Sensorless Pump Driver IC A89303: Features and Benefits Description박남수Оценок пока нет

- DM311Документ16 страницDM311Hernan Ortiz EnamoradoОценок пока нет

- DatasheetДокумент21 страницаDatasheetpiur w100% (1)

- A4954 Datasheet PDFДокумент9 страницA4954 Datasheet PDFJason WuОценок пока нет

- Max5090A/B/C 2A, 76V, High-Efficiency Maxpower Step-Down DC-DC ConvertersДокумент17 страницMax5090A/B/C 2A, 76V, High-Efficiency Maxpower Step-Down DC-DC ConvertersDuc VoquangОценок пока нет

- A3959 DatasheetДокумент12 страницA3959 DatasheetOctavio ParedesОценок пока нет

- A4931 DatasheetДокумент12 страницA4931 DatasheetDiego HernandezОценок пока нет

- A4941Документ9 страницA4941Lee HoonОценок пока нет

- Ka 3511Документ28 страницKa 3511analias100% (1)

- 3-Phase MOSFET Driver - A4915 - 11959609Документ17 страниц3-Phase MOSFET Driver - A4915 - 11959609Ramón MartinezОценок пока нет

- ICM7555 General Purpose CMOS Timer: Description Pin ConfigurationДокумент9 страницICM7555 General Purpose CMOS Timer: Description Pin ConfigurationkalimbaloОценок пока нет

- Automotive, Programmable Stepper Driver: Features and Benefits DescriptionДокумент45 страницAutomotive, Programmable Stepper Driver: Features and Benefits DescriptionCHADDOU100% (1)

- Green Mode PWM Controller Reduces Standby PowerДокумент5 страницGreen Mode PWM Controller Reduces Standby PowerCarlos Marinho SilvaОценок пока нет

- Transition-Mode PFC Controller: BCD TechnologyДокумент15 страницTransition-Mode PFC Controller: BCD TechnologyWilson vargas de la cruzОценок пока нет

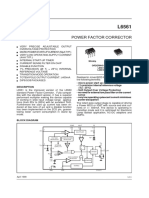

- Power Factor Corrector: Minidip SO8 Ordering Numbers: L6561 (Minidip) L6561D (SO8)Документ11 страницPower Factor Corrector: Minidip SO8 Ordering Numbers: L6561 (Minidip) L6561D (SO8)Karim CocasОценок пока нет

- Programmable DC/DC Controller For Advanced Microprocessors: Device Package Temp Range (T)Документ6 страницProgrammable DC/DC Controller For Advanced Microprocessors: Device Package Temp Range (T)ibrahim başderОценок пока нет

- L6561Документ11 страницL6561Gilson3DОценок пока нет

- Ad7606b 1623783Документ73 страницыAd7606b 1623783Jeferson AlvesОценок пока нет

- Data SheetДокумент19 страницData SheetRobertoBarbosaОценок пока нет

- FSCQ1565RP: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterДокумент24 страницыFSCQ1565RP: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterManuelAlejandroVicuñaRojasОценок пока нет

- R1290K Series: 3ch DC/DC For TFT LCDДокумент42 страницыR1290K Series: 3ch DC/DC For TFT LCDSergei OssifОценок пока нет

- (Codientu - Org) - BD 9397Документ30 страниц(Codientu - Org) - BD 9397VươngОценок пока нет

- White LED Driver For Large LCD Panels (DCDC Converter Type) : DatasheetДокумент29 страницWhite LED Driver For Large LCD Panels (DCDC Converter Type) : DatasheetIoanamih83Оценок пока нет

- KA3511Документ21 страницаKA3511AliОценок пока нет

- CR6224Документ10 страницCR6224sergioviriliОценок пока нет

- Tps 40222Документ28 страницTps 40222Banupriya BalasubramanianОценок пока нет

- Ad 5791Документ27 страницAd 5791Truong Dang VinhОценок пока нет

- TB9080FG Web Datasheet en 20111213Документ5 страницTB9080FG Web Datasheet en 20111213vllsОценок пока нет

- Bd9397efv eДокумент30 страницBd9397efv eGiovanni Carrillo VillegasОценок пока нет

- Oscilador Booster Led Sony BD9397EFVДокумент30 страницOscilador Booster Led Sony BD9397EFVAntonio Chavez100% (1)

- Ci CS2841B PDFДокумент6 страницCi CS2841B PDFEdson CostaОценок пока нет

- KA5M0965Q: Fairchild Power Switch (SPS)Документ14 страницKA5M0965Q: Fairchild Power Switch (SPS)Jose Angel TorrealbaОценок пока нет

- Infineon ICE1PCS01 DS v01 - 03 enДокумент18 страницInfineon ICE1PCS01 DS v01 - 03 enToader MarcuОценок пока нет

- SD6834 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetДокумент10 страницSD6834 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage Mosfetحسین مشعلОценок пока нет

- Features: TPIC74100-Q1 Buck/Boost Switch-Mode RegulatorДокумент30 страницFeatures: TPIC74100-Q1 Buck/Boost Switch-Mode RegulatorSyah NormanОценок пока нет

- Viper50/Sp Viper50A/Asp: Smps Primary I.CДокумент20 страницViper50/Sp Viper50A/Asp: Smps Primary I.CRalie RalevОценок пока нет

- FSCQ1565RT: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterДокумент25 страницFSCQ1565RT: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterPaulo Roberto s freireОценок пока нет

- L6565 DatasheetДокумент17 страницL6565 DatasheetJose BenavidesОценок пока нет

- Infineon ICE2PCS01 DataSheet v02 - 03 ENДокумент19 страницInfineon ICE2PCS01 DataSheet v02 - 03 ENАлексей АндрияшОценок пока нет

- SD6835 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetДокумент9 страницSD6835 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetАлександр КачеишвилиОценок пока нет

- KA3511BS: Intelligent Voltage Mode PWM ICДокумент20 страницKA3511BS: Intelligent Voltage Mode PWM ICPlamenPetrovОценок пока нет

- 8610 AxfДокумент6 страниц8610 Axfbruno magalhãesОценок пока нет

- STR-W6200D PWM Switching Regulator Application GuideДокумент17 страницSTR-W6200D PWM Switching Regulator Application Guidecjtrybiec0% (1)

- Uc2842b-45b Uc3842b-45b STДокумент15 страницUc2842b-45b Uc3842b-45b STAлександр ФедорчукОценок пока нет

- Si-8001ffe Ds enДокумент9 страницSi-8001ffe Ds enalexОценок пока нет

- Ice 2 As 01Документ24 страницыIce 2 As 01teleserviceОценок пока нет

- OB3372 On BrightДокумент13 страницOB3372 On BrightPedro Leandro SilvaОценок пока нет

- DSAZIHA100078408Документ20 страницDSAZIHA100078408Rjati devamОценок пока нет

- Fairchild Power Switch (FPS) : Features DescriptionДокумент12 страницFairchild Power Switch (FPS) : Features DescriptioncomphomeОценок пока нет

- Regulador Advanced SC 414Документ29 страницRegulador Advanced SC 414Paulo SilvaОценок пока нет

- Microcontrolador ViperДокумент23 страницыMicrocontrolador ViperAlvaro Javier Baños RiveraОценок пока нет

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2От EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Оценок пока нет

- MASNOON DUA / Muslim Prayer / Masnun Duwa / Dua MasnunДокумент84 страницыMASNOON DUA / Muslim Prayer / Masnun Duwa / Dua MasnunakhilismОценок пока нет

- Computer Memories and StorageДокумент6 страницComputer Memories and StorageShah ZaibОценок пока нет

- Computer Memories and StorageДокумент6 страницComputer Memories and StorageShah ZaibОценок пока нет

- The AVR Microcontroller and Embedded Systems (PDFDrive)Документ118 страницThe AVR Microcontroller and Embedded Systems (PDFDrive)Shah ZaibОценок пока нет

- Tutorial of Non-Isolated DC-DC Converters in Discontinuous Mode (Benny Yeung)Документ5 страницTutorial of Non-Isolated DC-DC Converters in Discontinuous Mode (Benny Yeung)Shah ZaibОценок пока нет

- Inverter Problems SolutionДокумент10 страницInverter Problems SolutionShah ZaibОценок пока нет

- Defining Intelligence: Shahzaib ShahДокумент2 страницыDefining Intelligence: Shahzaib ShahShah ZaibОценок пока нет

- Matching Mosfet Drivers To Mosfets: Equation 2Документ10 страницMatching Mosfet Drivers To Mosfets: Equation 2Rafael OgasawaraОценок пока нет

- EEC Design Project ReportДокумент6 страницEEC Design Project ReportShah ZaibОценок пока нет

- Continuity of ProphethoodДокумент11 страницContinuity of ProphethoodShah ZaibОценок пока нет

- Electrical PlansДокумент4 страницыElectrical Plansrbalmodal100% (1)

- Operational AmplifierДокумент112 страницOperational AmplifierEdson TorresОценок пока нет

- Samsung UN32EH4000 Chasis U71A B PDFДокумент108 страницSamsung UN32EH4000 Chasis U71A B PDFautrera50% (2)

- 6264Документ8 страниц6264api-3711187Оценок пока нет

- How To Measure Duty Cycle With A Digital MultimeterДокумент2 страницыHow To Measure Duty Cycle With A Digital MultimeterCiprian AndreescuОценок пока нет

- Atmel 42365 SAM C21 DatasheetДокумент1 194 страницыAtmel 42365 SAM C21 Datasheetalex diazОценок пока нет

- Knowles MLC Catalogue 2016Документ102 страницыKnowles MLC Catalogue 2016SalvadorОценок пока нет

- Service Manual: Indoor UnitДокумент28 страницService Manual: Indoor UnitEmanuel MarquesОценок пока нет

- Differentiator Circuit Design and AnalysisДокумент3 страницыDifferentiator Circuit Design and AnalysisKharol A. BautistaОценок пока нет

- Pspice TutorialДокумент25 страницPspice Tutorialamar7716dumОценок пока нет

- CL-32Z30DS Schematic DiagramsДокумент18 страницCL-32Z30DS Schematic DiagramsTammy KelleyОценок пока нет

- Ece-IV-linear Ics & Applications (10ec46) - Question PaperДокумент12 страницEce-IV-linear Ics & Applications (10ec46) - Question PaperPrakash ShiggaviОценок пока нет

- Keypad Interfacing With ARM7 SlickerДокумент15 страницKeypad Interfacing With ARM7 SlickerDenise NelsonОценок пока нет

- Semiconductor Module Users GuideДокумент318 страницSemiconductor Module Users GuideR YОценок пока нет

- Sursa de Tensiune - DatasheetДокумент2 страницыSursa de Tensiune - DatasheetAdrianaОценок пока нет

- LUM240PSW245PSW250PДокумент2 страницыLUM240PSW245PSW250PEko Yuli SulistionoОценок пока нет

- MSP 430 G 2955Документ71 страницаMSP 430 G 2955ezekielmuddОценок пока нет

- Special Forming ProcessДокумент11 страницSpecial Forming Processvelavansu0% (2)

- Pulse Amplitude Modulation & DemodulationДокумент8 страницPulse Amplitude Modulation & DemodulationRashed IslamОценок пока нет

- STK621-043A-E: Air Conditioner Three-Phase Compressor Motor Driver IMST Inverter Power Hybrid ICДокумент8 страницSTK621-043A-E: Air Conditioner Three-Phase Compressor Motor Driver IMST Inverter Power Hybrid ICjicoelhoОценок пока нет

- Thesis FinalДокумент29 страницThesis FinalDanika Jan100% (2)

- BGA's, LGA's, QFN/DFN's - Oh My, Can Traditional DFM SurviveДокумент54 страницыBGA's, LGA's, QFN/DFN's - Oh My, Can Traditional DFM SurvivemrbustaОценок пока нет

- Vlsi PT 1st Year SyllabusДокумент17 страницVlsi PT 1st Year SyllabusMANGAL KUMAR MOHAPATRAОценок пока нет

- Electrical Electronics Engineering: Sssutms SehoreДокумент16 страницElectrical Electronics Engineering: Sssutms SehoreolexОценок пока нет

- Physics MathematicsДокумент36 страницPhysics Mathematicsmudabbir muhammad33% (3)

- RW748U 700W 48V DC Wall Mount RectifierДокумент2 страницыRW748U 700W 48V DC Wall Mount RectifierGuillermo OvelarОценок пока нет

- Vle 722 UsermanualДокумент92 страницыVle 722 UsermanualheldermnaОценок пока нет

- Sony TVC LCD Ke 32ts2uДокумент99 страницSony TVC LCD Ke 32ts2uGiada SpaccarotellaОценок пока нет

- AFE eДокумент110 страницAFE eDươngОценок пока нет

- EEE431 Module 2Документ27 страницEEE431 Module 2Victor ImehОценок пока нет