Академический Документы

Профессиональный Документы

Культура Документы

Trilithic Data Sheet Bts 7740 G: 1 1.1 Features

Загружено:

KrocodileОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Trilithic Data Sheet Bts 7740 G: 1 1.1 Features

Загружено:

KrocodileАвторское право:

Доступные форматы

TrilithIC BTS 7740 G

Data Sheet

1 Overview

1.1 Features

• Quad D-MOS switch driver

• Free configurable as bridge or quad-switch

• Optimized for DC motor management applications

• Low RDS ON: 110 mτ high-side switch, 100 mτ low-

side switch (typical values @ 25 C) P-DSO-28-14

• Maximum peak current: typ. 8 A @ 25 C=

• Very low quiescent current: typ. 5 ←A @ 25 C=

• Small outline, enhanced power P-DSO-package

• Full short-circuit-protection

• Operates up to 40 V

• Status flag diagnosis

• Overtemperature shut down with hysteresis

• Internal clamp diodes

• Isolated sources for external current sensing

• Under-voltage detection with hysteresis

• PWM frequencies up to 1 kHz

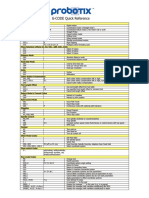

Type Ordering Code Package

BTS 7740 G Q67007-A9374 P-DSO-28-14

1.2 Description

The BTS 7740 G is part of the TrilithIC family containing three dies in one package:

One double high-side switch and two low-side switches. The drains of these three

vertical DMOS chips are mounted on separated leadframes. The sources are connected

to individual pins, so the BTS 7740 G can be used in H-bridge- as well as in any other

configuration. Both the double high-side and the two low-side switches of the

BTS 7740 G are manufactured in SMART SIPMOS® technology which combines low

RDS ON vertical DMOS power stages with CMOS control circuitry. The high-side switch is

fully protected and contains the control and diagnosis circuitry. Also the low-side

switches are fully protected, the equivalent standard product is the BSP 77.

In contrast to the BTS 7750 G, which consists of lower ohmic chips in the same

package, the BTS 7740 G offers a lower price for applications, which do not need the

high current capability of the BTS 7750 G or BTS 7750 GP.

Data Sheet 1 2001-02-01

BTS 7740 G

1.3 Pin Configuration

(top view)

DL1 1 28 DL1

IL1 2 27 SL1

DL1 3 26 SL1

LS-Leadframe

N.C. 4 25 DL1

DHVS 5 24 DHVS

GND 6 23 SH1

IH1 7 22 SH1

HS-Leadframe

ST 8 21 SH2

IH2 9 20 SH2

DHVS 10 19 DHVS

N.C. 11 18 DL2

LS-Leadframe

DL2 12 17 SL2

IL2 13 16 SL2

DL2 14 15 DL2

Figure 1

Data Sheet 2 2001-02-01

BTS 7740 G

1.4 Pin Definitions and Functions

Pin No. Symbol Function

1, 3, 25, 28 DL1 Drain of low-side switch1, leadframe 1 1)

2 IL1 Analog input of low-side switch1

4 N.C. not connected

5, 10, 19, 24 DHVS Drain of high-side switches and power supply voltage,

leadframe 2 1)

6 GND Ground

7 IH1 Digital input of high-side switch1

8 ST Status of high-side switches; open Drain output

9 IH2 Digital input of high-side switch2

11 N.C. not connected

12, 14, 15, 18 DL2 Drain of low-side switch2, leadframe 3 1)

13 IL2 Analog input of low-side switch2

16,17 SL2 Source of low-side switch2

20,21 SH2 Source of high-side switch2

22,23 SH1 Source of high-side switch1

26,27 SL1 Source of low-side switch1

1)

To reduce the thermal resistance these pins are direct connected via metal bridges to the leadframe.

Pins written in bold type need power wiring.

Data Sheet 3 2001-02-01

BTS 7740 G

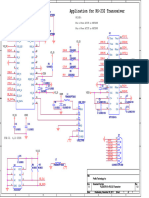

1.5 Functional Block Diagram

DHVS

5,10,19,24

8

ST

Diagnosis Biasing and Protection

7

IH1 Driver

IN OUT

0 0 L L

0 1 L H RO1 RO2 20,21

9 1 0 H L SH2

IH2 1 1 H H

12,14,15,18

DL2

6

GND

22, 23

SH1

1,3,25,28

Protection DL1

2

Gate

IL1

Driver

Protection

13

Gate

IL2

Driver

26, 27 16, 17

SL1 SL2

Figure 2

Block Diagram

Data Sheet 4 2001-02-01

BTS 7740 G

1.6 Circuit Description

Input Circuit

The control inputs IH1,2 consist of TTL/CMOS compatible Schmitt-Triggers with

hysteresis. Buffer amplifiers are driven by these stages and convert the logic signal into

the necessary form for driving the power output stages. The inputs are protected by ESD

clamp-diodes.

The inputs IL1 and IL2 are connected to the internal gate-driving units of the N-channel

vertical power-MOS-FETs.

Output Stages

The output stages consist of an low RDS ON Power-MOS H-bridge. In H-bridge

configuration, the D-MOS body diodes can be used for freewheeling when commutating

inductive loads. If the high-side switches are used as single switches, positive and

negative voltage spikes which occur when driving inductive loads are limited by

integrated power clamp diodes.

Short Circuit Protection

The outputs are protected against

– output short circuit to ground

– output short circuit to the supply voltage, and

– overload (load short circuit).

An internal OP-Amp controls the Drain-Source-Voltage by comparing the DS-Voltage-

Drop with an internal reference voltage. Above this trippoint the OP-Amp reduces the

output current depending on the junction temperature and the drop voltage.

In the case of overloaded high-side switches the status output is set to low.

The fully protected low-side switches have no status output.

Overtemperature Protection

The high-side and the low-side switches also incorporate an overtemperature protection

circuit with hysteresis which switches off the output transistors. In the case of the high-

side switches, the status output is set to low.

Undervoltage-Lockout (UVLO)

When VS reaches the switch-on voltage VUVON the IC becomes active with a hysteresis.

The High-Side output transistors are switched off if the supply voltage VS drops below

the switch off value VUVOFF.

Data Sheet 5 2001-02-01

BTS 7740 G

Status Flag

The status flag output is an open drain output with Zener-diode which requires a pull-up

resistor, c.f. the application circuit on page 14. Various errors as listed in the table

“Diagnosis” are detected by switching the open drain output ST to low. A open load

detection is not available. Freewheeling condition does not cause an error.

2 Truthtable and Diagnosis (valid only for the High-Side-Switches)

Flag IH1 IH2 SH1 SH2 ST Remarks

Inputs Outputs

0 0 L L 1 stand-by mode

Normal operation; 0 1 L H 1 switch2 active

identical with functional truth table 1 0 H L 1 switch1 active

1 1 H H 1 both switches

active

Overtemperature high-side switch1 0 X L X 1

1 X L X 0 detected

Overtemperature high-side switch2 X 0 X L 1

X 1 X L 0 detected

Overtemperature both high-side switches 0 0 L L 1

X 1 L L 0 detected

1 X L L 0 detected

Undervoltage X X L L 1 not detected

Inputs: Outputs: Status:

0 = Logic LOW Z = Output in tristate condition 1 = No error

1 = Logic HIGH L = Output in sink condition 0 = Error

X = don’t care H = Output in source condition

X = Voltage level undefined

Data Sheet 6 2001-02-01

BTS 7740 G

3 Electrical Characteristics

3.1 Absolute Maximum Ratings

– 40 C < Tj < 150 C

Parameter Symbol Limit Values Unit Remarks

min. max.

High-Side-Switches (Pins DHVS, IH1,2 and SH1,2)

Supply voltage VS – 0.3 42 V –

Supply voltage for full short VS(SCP) 28 V

circuit protection

HS-drain current* IS –7 ** A TA = 25°C; tP < 100 ms

HS-input current IIH –5 5 mA Pin IH1 and IH2

HS-input voltage VIH – 10 16 V Pin IH1 and IH2

Note: * single pulse ** internally limited

Status Output ST

Status pull up voltage VST – 0.3 5.4 V

Status Output current IST –5 5 mA Pin ST

Low-Side-Switches (Pins DL1,2, IL1,2 and SL1,2)

Drain-Source-Clamp voltage VDSL 42 – V VIL = 0 V; ID 1 mA

Supply voltage for short VDSL(SCP) 30 V VIL = 5 V

circuit protection 20 V VIL = 10 V

LS-drain current* IDL –7 ** A TA = 25°C; tP < 100 ms

LS-input voltage VIL – 0.3 10 V –

Note: * single pulse ** internally limited

Temperatures

Junction temperature Tj – 40 150 C –

Storage temperature Tstg – 55 150 C –

Data Sheet 7 2001-02-01

BTS 7740 G

3.1 Absolute Maximum Ratings (cont’d)

– 40 C < Tj < 150 C

Parameter Symbol Limit Values Unit Remarks

min. max.

Thermal Resistances (one HS-LS-Path active)

LS-junction case RthjC L – 20 K/W measured to pin 3 or 12

HS-junction case RthjC H – 20 K/W measured to pin 19

Junction ambient Rthja – 60 K/W device soldered to

Rthja = Tj(HS)/(P(HS)+P(LS)) reference PCB with

6 cm2 cooling area

ESD Protection (Human Body Model acc. MIL STD 883D, method 3015.7 and EOS/

ESD assn. standard S5.1 - 1993)

Input LS-Switch VESD – 2 kV

Input HS-Switch VESD – 1 kV

Status HS-Switch VESD – 2 kV

Output LS and HS-Switch VESD – 8 kV all other pins connected

to Ground

Note: Maximum ratings are absolute ratings; exceeding any one of these values may

cause irreversible damage to the integrated circuit.

3.2 Operating Range

– 40 C < Tj < 150 C

Parameter Symbol Limit Values Unit Remarks

min. max.

Supply voltage VS VUVOFF 42 V After VS rising

above VUVON

Input voltages VIH – 0.3 15 V –

Input voltages VIL – 0.3 10 V –

Output current IST 0 2 mA –

Junction temperature Tj – 40 150 C –

Note: In the operating range the functions given in the circuit description are fulfilled.

Data Sheet 8 2001-02-01

BTS 7740 G

3.3 Electrical Characteristics

ISH1 = ISH2 = ISL1 = ISL2 = 0 A; – 40 C < Tj < 150 C; 8 V < VS < 18 V

unless otherwise specified

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Current Consumption HS-switch

Quiescent current IS – 5 8 ←A IH1 = IH2 = 0 V

Tj = 25 C

– – 12 ←A IH1 = IH2 = 0 V

Supply current IS – 1 2 mA IH1 or IH2 = 5 V

VS = 12 V

– 2 4 mA IH1 and IH2 = 5 V

VS = 12 V

Leakage current of ISH LK – – 6 ←A VIH = VSH = 0 V

highside switch

Leakage current through ILKCL = – – 10 mA IFH = 3 A

logic GND in free wheeling IFH + ISH

condition

Current Consumption LS-switch

Input current IIL – 8 30 ←A VIL = 5 V;

normal operation

– 160 300 ←A VIL = 5 V;

failure mode

Leakage current of lowside IDL LK – 2 10 ←A VIL = 0 V

switch

Under Voltage Lockout (UVLO) HS-switch

Switch-ON voltage VUVON – – 4.5 V VS increasing

Switch-OFF voltage VUVOFF 1.8 – 3.2 V VS decreasing

Switch ON/OFF hysteresis VUVHY – 1 – V VUVON – VUVOFF

Data Sheet 9 2001-02-01

BTS 7740 G

3.3 Electrical Characteristics (cont’d)

ISH1 = ISH2 = ISL1 = ISL2 = 0 A; – 40 C < Tj < 150 C; 8 V < VS < 18 V

unless otherwise specified

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Output stages

Inverse diode of high-side VFH – 0.8 1.2 V IFH = 3 A

switch; Forward-voltage

Inverse diode of lowside VFL – 0.8 1.2 V IFL = 3 A

switch; Forward-voltage

Static drain-source RDS ON H – 110 140 mτ ISH = 1 A

on-resistance of highside Tj = 25 C

switch

Static drain-source RDS ON L – 100 120 mτ ISL = 1 A;

on-resistance of lowside VGL = 5 V

switch Tj = 25 C

Static path on-resistance RDS ON – – 500 mτ RDS ON H + RDS ON L

ISH = 1 A;

Short Circuit of highside switch to GND

Initial peak SC current ISCP H 8 9.5 11 A Tj = – 40 °C

7 8 9.5 A Tj = + 25 °C

5 6 7.5 A Tj = + 150 °C

Short Circuit of highside switch to VS

Output pull-down-resistor RO 12 22 50 kτ VDSL = 3 V

Short Circuit of lowside switch to VS

Initial peak SC current ISCP L 12 17 22 A Tj = – 40 C

10 15 20 A Tj = 25 C

7 10 15 A Tj = 150 C

Data Sheet 10 2001-02-01

BTS 7740 G

3.3 Electrical Characteristics (cont’d)

ISH1 = ISH2 = ISL1 = ISL2 = 0 A; – 40 C < Tj < 150 C; 8 V < VS < 18 V

unless otherwise specified

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Thermal Shutdown

Thermal shutdown junction Tj SD 155 180 190 C –

temperature

Thermal switch-on junction Tj SO 150 170 180 C –

temperature

Temperature hysteresis αT – 10 – C αT = TjSD – TjSO

Status Flag Output ST of highside switch

Low output voltage VST L – 0.2 0.6 V IST = 1.6 mA

Leakage current IST LK – – 10 ←A VST = 5 V

Zener-limit-voltage VST Z 5.4 – V IST = 1.6 mA

Switching times of highside switch

Turn-ON-time; tON – 85 180 ←s RLoad = 12 τ

to 90% VSH VS = 12 V

Turn-OFF-time; tOFF – 80 180 ←s RLoad = 12 τ

to 10% VSH VS = 12 V

Slew rate on 10 to 30% VSH dV/dtON – – 1.1 V/←s RLoad = 12 τ

VS = 12 V

Slew rate off 70 to 40% VSH -dV/ – – 1.5 V/←s RLoad = 12 τ

dtOFF VS = 12 V

Note: switching times are guaranteed by design

Data Sheet 11 2001-02-01

BTS 7740 G

3.3 Electrical Characteristics (cont’d)

ISH1 = ISH2 = ISL1 = ISL2 = 0 A; – 40 C < Tj < 150 C; 8 V < VS < 18 V

unless otherwise specified

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Switching times of lowside switch

Turn-ON-time 70 to 50% tON – 70 170 ←s RLoad = 12 τ

VSHVIL = 0 to 10 V VS = 12 V

Turn-OFF-time; tOFF – 40 150 ←s RLoad = 12 τ

to 10% VSL VS = 12 V

Slew rate on 70 to 50% VSH -dV/dtON – – 1.0 V/←s RLoad = 12 τ

VIL = 0 to 10 V VS = 12 V

Slew rate off 50 to 70% VSH dV/dtOFF – – 1.0 V/←s RLoad = 12 τ

VIL = 0 to 10 V VS = 12 V

Note: switching times are guaranteed by design

Control Inputs of highside switches GH 1, 2

H-input voltage VIH High – – 2.5 V –

L-input voltage VIH Low 1 – – V –

Input voltage hysterese VIH HY – 0.3 – V –

H-input current IIH High 15 30 60 ←A VIH = 5 V

L-input current IIH Low 5 – 20 ←A VIH = 0.4 V

Input series resistance RI 2.7 4 5.5 kτ –

Zener limit voltage VIH Z 5.4 – – V IIH = 1.6 mA

Control Inputs GL1, 2

Gate-threshold-voltage VIL th 0.9 1.7 2.2 V IDL = 2 mA

Note: The listed characteristics are ensured over the operating range of the integrated

circuit. Typical characteristics specify mean values expected over the production

spread. If not otherwise specified, typical characteristics apply at TA = 25 C and

the given supply voltage.

Data Sheet 12 2001-02-01

BTS 7740 G

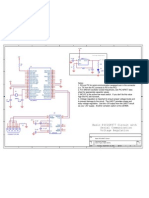

VS=12V

IS

CS CL

470nF 100µF

IFH1,2

DHVS

IST LK 5,10,19,24

IST VDSH2 VDSH1

ST 8

-VFH2 -VFH1

Diagnosis Biasing and Protection

VST

IIH1

IH1 7 Gate

VSTL

Driver

VSTZ

RO1 RO2 20,21 SH2 ISH2

IIH1

IH2 9 Gate

VIH1 DL2 IDL2

Driver 12,14,15,18

GND 6 IDL LK 2 VUVON

VIH2

IGND SH1 ISH1 VUVOFF

22,23

ILKCL IDL1

DL1

1,3,25,28

Protection

IDL LK 1

IIL1 IL1 2

Gate

Driver

Protection

VIL1 IIL2 IL2 13

Gate

Driver

VIL th 1

26,27

VIL2 16,17 VDSL1 VDSL2

VIL th 2 SL1 SL2 -VFL1 -VFL2

ISCP L 1 ISCP L 2

ISL1 ISL2

Figure 3

Test Circuit

HS-Source-Current Named during Short Named during Leakage-

Circuit Cond.

ISH1,2 ISCP H IDL LK

Data Sheet 13 2001-02-01

BTS 7740 G

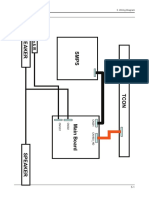

Watchdog

Reset TLE I

VS=12V

4278G

Q

D

RQ CQ CD D01 CS

τ

100 kτ 22µF 47nF Z39 10µF

WD R VCC DHVS

5,10,19,24

RS ST 8

τ

10 kτ

Diagnosis Biasing and Protection

IH1 7

Gate

Driver

RO1 RO2 20,21 SH2

IH2 9 Gate

DL2

Driver 12,14,15,18

GND 6

µP M

SH1

22,23

DL1

1,3,25,28

Protection

IL1 2

Gate

Driver

Protection

IL2 13

Gate

Driver

26,27

16,17

GND SL1 SL2

In case of VDSL<-0.6V or reverse battery the current into the µC might be limited by external resitors to protect the µC

Figure 4

Application Circuit

Data Sheet 14 2001-02-01

BTS 7740 G

4 Package Outlines

P-DSO-28-14

(Plastic Transistor Single Outline Package)

0.35 x 45˚

2.65 max

2.45 -0.2

7.6 -0.2 1)

0.2 -0.1

+0.09

x

8˚ ma

0.23

1.27 0.4 +0.8

0.35 +0.15 2) 0.1 10.3 ±0.3

0.2 28x

28 15

1 14

18.1 -0.4 1)

Index Marking

1) Does not include plastic or metal protrusions of 0.15 max rer side

2) Does not include dambar protrusion of 0.05 max per side GPS05123

GPS05123

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device Dimensions in mm

Data Sheet 15 2001-02-01

BTS 7740 G

Published by

Infineon Technologies AG i Gr.,

Bereichs Kommunikation

St.-Martin-Strasse 53,

D-81541 München

© Infineon Technologies AG 1999

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as warranted

characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding

circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address

list).

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the

failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life

support devices or systems are intended to be implanted in the human body, or to support and/or maintain and

sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other

persons may be endangered.

Data Sheet 16 2001-02-01

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

Вам также может понравиться

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesОт EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesРейтинг: 4.5 из 5 звезд4.5/5 (7)

- Trilithic Data Sheet Bts 781 GP: 1 1.1 FeaturesДокумент17 страницTrilithic Data Sheet Bts 781 GP: 1 1.1 FeaturesВиктор СабовОценок пока нет

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetДокумент32 страницы7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareОценок пока нет

- TPS5125Документ21 страницаTPS5125Shaun Dwyer Van HeerdenОценок пока нет

- Patillaje XBTZ968 - XBTZ915pdfДокумент1 страницаPatillaje XBTZ968 - XBTZ915pdfwashington100% (1)

- BUK9MHH-65PNN PhilipsSemiconductorsДокумент16 страницBUK9MHH-65PNN PhilipsSemiconductorsKotaobormota DanilovichОценок пока нет

- Panel Board SchematicsДокумент5 страницPanel Board SchematicskevinalleinОценок пока нет

- TLE7209 R InfineonДокумент16 страницTLE7209 R Infineonmobil benerОценок пока нет

- 7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetДокумент4 страницы7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetallisonОценок пока нет

- Alcatel Omnipcx Enterprise: Cblv36 CableДокумент6 страницAlcatel Omnipcx Enterprise: Cblv36 CableAriel BecerraОценок пока нет

- TOSHIBA 32AV500U Wiring - DiagramДокумент1 страницаTOSHIBA 32AV500U Wiring - Diagramdreamyson1983Оценок пока нет

- TM1638 enДокумент18 страницTM1638 enfotakis michaelОценок пока нет

- Toy Car Remote Controller With Five Functions: TX-2B/RX-2BДокумент11 страницToy Car Remote Controller With Five Functions: TX-2B/RX-2BJulio Gustavo LazzosОценок пока нет

- Tle 7263eДокумент62 страницыTle 7263eCarlos PenagosОценок пока нет

- Green-Mode PWM Controller: General Description FeaturesДокумент10 страницGreen-Mode PWM Controller: General Description FeaturesValdir DerlannОценок пока нет

- Data SheetДокумент16 страницData Sheetcarrei JohnОценок пока нет

- M63029FPДокумент22 страницыM63029FPhackwerkОценок пока нет

- PDTA124E Series: 1. Product ProfileДокумент18 страницPDTA124E Series: 1. Product ProfiletodorloncarskiОценок пока нет

- 74LS290Документ7 страниц74LS290jaja558Оценок пока нет

- MC2101 TM1628 PDFДокумент22 страницыMC2101 TM1628 PDFPol ErnОценок пока нет

- uPD16510A RenesasДокумент15 страницuPD16510A RenesasAnh Le NgocОценок пока нет

- Basic 16f877Документ1 страницаBasic 16f877api-27535945100% (1)

- Tait Programmer 1Документ1 страницаTait Programmer 1Juan Guillermo Palacio UribeОценок пока нет

- Wiring DiagramДокумент4 страницыWiring DiagramDjalma MoreiraОценок пока нет

- Half Bridge Driver Based On: C2 1uF/25V CN1 C5 10uF/25V D1 MBRS140T3G C3 220uF/63VДокумент2 страницыHalf Bridge Driver Based On: C2 1uF/25V CN1 C5 10uF/25V D1 MBRS140T3G C3 220uF/63VratnaОценок пока нет

- Toy Car Remote Controller With Nine Functions: TX-5B/RX-5BДокумент9 страницToy Car Remote Controller With Nine Functions: TX-5B/RX-5BYan SuОценок пока нет

- Stib1060dm2t LДокумент23 страницыStib1060dm2t LРуслан КаргиевОценок пока нет

- Si3012 FS ModemДокумент54 страницыSi3012 FS ModemAnonymous xDBXbk89PОценок пока нет

- Pdtc114ee, Pdtc114em, Pdtc114et, Pdtc114eu NXPДокумент17 страницPdtc114ee, Pdtc114em, Pdtc114et, Pdtc114eu NXPTrieeОценок пока нет

- DatasheetДокумент16 страницDatasheetAndres GuerreroОценок пока нет

- Fds6986S: Dual Notebook Power Supply N-Channel Powertrench SyncfetДокумент10 страницFds6986S: Dual Notebook Power Supply N-Channel Powertrench Syncfetdayne81sОценок пока нет

- Tle 4726 IacДокумент23 страницыTle 4726 Iacfreddys merchanОценок пока нет

- Wiring DiagramДокумент4 страницыWiring DiagramAntonio MacedoОценок пока нет

- Schematic - PIC-Broggio Certo2 - 2023-10-26Документ1 страницаSchematic - PIC-Broggio Certo2 - 2023-10-26ENERGOSОценок пока нет

- Tle5205 2Документ23 страницыTle5205 2Richard MachadoОценок пока нет

- Transistor BUK765R2-40B DatasheetДокумент14 страницTransistor BUK765R2-40B Datasheetmobil benerОценок пока нет

- System Basis Chip T L E 6 2 6 6 G: Integrated LS CAN, LDO and LS - HS SwitchesДокумент50 страницSystem Basis Chip T L E 6 2 6 6 G: Integrated LS CAN, LDO and LS - HS Switchescork_ieОценок пока нет

- TX-2B/RX-2B: Silan SemiconductorsДокумент10 страницTX-2B/RX-2B: Silan SemiconductorsVijay Dhar MauryaОценок пока нет

- SN 74 CBTLV 3257Документ6 страницSN 74 CBTLV 3257Кирилл ОлейникОценок пока нет

- TB6564AHQ (THB6064AH) : PWM Chopper-Type Bipolar Stepping Motor Driver ICДокумент39 страницTB6564AHQ (THB6064AH) : PWM Chopper-Type Bipolar Stepping Motor Driver ICTran Duc IOTОценок пока нет

- TB6564AHQ (THB6064AH) : PWM Chopper-Type Bipolar Stepping Motor Driver ICДокумент39 страницTB6564AHQ (THB6064AH) : PWM Chopper-Type Bipolar Stepping Motor Driver ICTran Duc IOTОценок пока нет

- General Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETДокумент10 страницGeneral Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETErnesto PuenteОценок пока нет

- 1 Tle5206 2 - 1Документ23 страницы1 Tle5206 2 - 1Fran CastanoОценок пока нет

- Green-Mode PWM Controller With Integrated Protections: General Description FeaturesДокумент18 страницGreen-Mode PWM Controller With Integrated Protections: General Description FeaturesRUSLANОценок пока нет

- Ne5521 Sa5521 2Документ11 страницNe5521 Sa5521 2José AdelinoОценок пока нет

- DatasheetДокумент12 страницDatasheetWAN MOZESОценок пока нет

- TI 58 59-HW-manualДокумент28 страницTI 58 59-HW-manualAlejandro MenéndezОценок пока нет

- PDTA114E Series: 1. Product ProfileДокумент17 страницPDTA114E Series: 1. Product ProfileGian MontillaОценок пока нет

- D D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoДокумент38 страницD D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoArturo PicolinОценок пока нет

- D D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoДокумент39 страницD D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With Fifoapi-3825669Оценок пока нет

- Smart Octal Low-Side Switch: LogicДокумент17 страницSmart Octal Low-Side Switch: Logicjuan echeverryОценок пока нет

- GTL2010 10-Bit Bidirectional Low-Voltage Translator: FeaturesДокумент19 страницGTL2010 10-Bit Bidirectional Low-Voltage Translator: FeaturesMigue SolinasОценок пока нет

- SCH Pl2303ta V1.0Документ1 страницаSCH Pl2303ta V1.0Reginaldo LeiteОценок пока нет

- Overview Data Sheets: F 3222: 8 Fold Input ModuleДокумент2 страницыOverview Data Sheets: F 3222: 8 Fold Input ModulemohamadziОценок пока нет

- Datasheet SN3218Документ12 страницDatasheet SN3218Daniel SilvaОценок пока нет

- BOMДокумент1 страницаBOMpriyankaОценок пока нет

- SG3524 PDFДокумент24 страницыSG3524 PDFErasmo Franco SОценок пока нет

- Sg3524 Texas Instrument WayДокумент24 страницыSg3524 Texas Instrument WayDaniel NwodoОценок пока нет

- MC9S12C64Документ2 страницыMC9S12C64KrocodileОценок пока нет

- Radiatoare LED SpecSheet - DL CHS 0700 BДокумент2 страницыRadiatoare LED SpecSheet - DL CHS 0700 BKrocodileОценок пока нет

- Dashcam Viewer Users ManualДокумент33 страницыDashcam Viewer Users ManualKrocodile0% (1)

- CSC - Catalog Miezuri de FeДокумент84 страницыCSC - Catalog Miezuri de FeKrocodileОценок пока нет

- Elman UkДокумент1 601 страницаElman UkKrocodileОценок пока нет

- Introducere in Code WarriorДокумент11 страницIntroducere in Code WarriorKrocodileОценок пока нет

- AN2548Документ24 страницыAN2548KrocodileОценок пока нет

- $QLPDWLRQV: &Uhdwh'Hvljq$VvhpeoДокумент7 страниц$QLPDWLRQV: &Uhdwh'Hvljq$VvhpeoKrocodileОценок пока нет

- Trusa de Metalizare Gauri PCBДокумент4 страницыTrusa de Metalizare Gauri PCBKrocodileОценок пока нет

- Mcu8051ide enДокумент110 страницMcu8051ide enKrocodileОценок пока нет

- G Codes PDFДокумент1 страницаG Codes PDFKrocodileОценок пока нет

- Mirror TutorialДокумент4 страницыMirror TutorialKrocodileОценок пока нет

- 330C & 330C L Excavators KDD00001-UP (MACHINE) POWERED by C-9 Engine (SEBP3365 - 49) - Sistemas y ComponentesДокумент6 страниц330C & 330C L Excavators KDD00001-UP (MACHINE) POWERED by C-9 Engine (SEBP3365 - 49) - Sistemas y ComponentesDaniel Rafael Torres Regardiz100% (1)

- Fault Analysis-Electronic Equipment Troubleshooting & Repair - PSMBДокумент3 страницыFault Analysis-Electronic Equipment Troubleshooting & Repair - PSMBpeterpinion98220% (1)

- PCM ManualДокумент32 страницыPCM ManualalbertojanetaОценок пока нет

- S 2 7F NF 01 PDFДокумент2 страницыS 2 7F NF 01 PDFSuong Ngo DinhОценок пока нет

- Magnetic Resonant Coupling Based Wireless PowerДокумент7 страницMagnetic Resonant Coupling Based Wireless PowerHartantoОценок пока нет

- Ir 2153Документ9 страницIr 2153SteveAbonyiОценок пока нет

- Physics Investigatory Project: Topic: To Construct AnДокумент24 страницыPhysics Investigatory Project: Topic: To Construct Anpradhumna dixitОценок пока нет

- F-FRAME TC01200002E TBG 5-24-17 Rev 3Документ66 страницF-FRAME TC01200002E TBG 5-24-17 Rev 3carlos4041Оценок пока нет

- Key TagДокумент1 страницаKey TagStephane Durel MbidaОценок пока нет

- Amplifier Yorkville Nx750pДокумент9 страницAmplifier Yorkville Nx750pcarlosavictoriaОценок пока нет

- AccessoriesДокумент2 страницыAccessoriesPankaj JadhavОценок пока нет

- Parameter Setting Keep Voice Traffic in 3G Network HuaweiДокумент2 страницыParameter Setting Keep Voice Traffic in 3G Network HuaweimosesОценок пока нет

- Chapter 4Документ22 страницыChapter 4hadushОценок пока нет

- Battery Eliminator CircuitДокумент5 страницBattery Eliminator CircuitGiriОценок пока нет

- UntitledДокумент5 страницUntitledAshok MaharanaОценок пока нет

- Circuit Schematic Electronics - Light Flasher (Blinking Lights)Документ5 страницCircuit Schematic Electronics - Light Flasher (Blinking Lights)ReneОценок пока нет

- A Dual-Band Highly Miniaturized Patch Antenna: Ahmad A. Salih, and Mohammad S. Sharawi, Senior Member, IEEEДокумент4 страницыA Dual-Band Highly Miniaturized Patch Antenna: Ahmad A. Salih, and Mohammad S. Sharawi, Senior Member, IEEEBavithraОценок пока нет

- Mic 4120Документ10 страницMic 4120tabassam7801Оценок пока нет

- Low-Noise AmplifierДокумент115 страницLow-Noise Amplifierkaviarasu1990Оценок пока нет

- CDX mp30Документ48 страницCDX mp30sonicman23Оценок пока нет

- Chapter 7Документ41 страницаChapter 7CarolineОценок пока нет

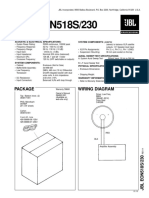

- JBL Eon518s-230Документ13 страницJBL Eon518s-230Joelcio Ribeiro GomesОценок пока нет

- TP Advanced IC Packaging Technology OverviewДокумент25 страницTP Advanced IC Packaging Technology Overviewalbertsdeguzman100% (1)

- 2-1. Elect - Single Line DiagramДокумент7 страниц2-1. Elect - Single Line DiagramHendrias Ari SujarwoОценок пока нет

- BAUR Cable Locator: Data SheetДокумент2 страницыBAUR Cable Locator: Data Sheetwinston11Оценок пока нет

- HK Aura Studio2 Spec Sheet (English)Документ2 страницыHK Aura Studio2 Spec Sheet (English)n333aroraОценок пока нет

- Truck Adblue Emulator For MAN INSTRUCTIONS PDFДокумент4 страницыTruck Adblue Emulator For MAN INSTRUCTIONS PDFobd2worksОценок пока нет

- 51 MP6200 DTraining ManualДокумент58 страниц51 MP6200 DTraining ManualDaniboy1994Оценок пока нет

- Resume PatelДокумент2 страницыResume Patelsubhash_tuhhОценок пока нет

- Chapter 11 Lecture PowerPointДокумент45 страницChapter 11 Lecture PowerPointMaritess CationОценок пока нет