Академический Документы

Профессиональный Документы

Культура Документы

Info 4 Contadores

Загружено:

baad13Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Info 4 Contadores

Загружено:

baad13Авторское право:

Доступные форматы

Universidad Nacional del Callao

Facultad de Ingeniería Eléctrica y Electrónica

INTRODUCCION:

En el presente laboratorio, se desarrolla el análisis funcional de los circuitos secuenciales

desarrollados con los biestables (Latch y Flip Flops); que permiten obtener secuencias de

estados binarios que al ser decodificados nos permiten obtener una sucesión de estados

ascendente, descendente y/o desordenado (escalador) pero periódico, estableciendo el

módulo del contador, permitiendo además establecer funciones de almacenamiento de pulsos

recibidos por el sistema digital (proceso de conteo) y relacionar con la temporización de

eventos del sistema digital de lógica cableada.

OBJETIVOS GENERALES:

Analizar e Implementar diversos circuitos secuenciales asíncronos y síncronos,

relacionados con la generación de estados ascendentes, descendentes y/o escaladores;

implementados con los Flips Flops.

La visualización del funcionamiento de cada una de los circuitos de contadores son

implementados utilizando dispositivos display y/o diodos leds en las salidas.

Implementar circuitos básicos con IC TTL y CMOS.

Adquirir destreza para el montaje y cableado de circuitos digitales en el prothoboard y/o

en circuito impreso.

Que el estudiante aprenda utilizar los principios básicos para el análisis de circuitos

digitales secuenciales mediante simuladores y que tenga la capacidad de realizar la

detección de fallos, corregirlos y comprobar su buen funcionamiento.

RESUMEN:

El experimento consta de circuitos secuenciales que desarrollan las funciones de contadores,

por lo que se debe atender especial atención de su análisis, funcionamiento, operación de los

circuitos y los resultados obtenidos (respuesta de funcionamiento del circuito, diagramas de

tiempo). Por lo que se recomienda efectuar las consultas previas en los apuntes de clases,

manuales técnicos adecuados en relación a los dispositivos a emplear y los circuitos digitales a

implementar. Por último se implementa el circuito con los circuitos integrados realizando

conjuntamente pruebas individuales de su funcionamiento y al terminar dicho proceso se

procede a hacer las verificaciones y desarrollo de las tablas de estados y construir los

diagramas de tiempo.

MARCO TEORICO:

La teoría desarrollada en clases.

Sistemas Digitales : 2013-B

Ing. Utrilla Salazar Darío

Universidad Nacional del Callao

Facultad de Ingeniería Eléctrica y Electrónica

LISTADO DE MATERIALES:

Circuitos Integrados IC 555, TTL: 74LS76, 74LS74, 74LS00, 74LS02, 74LS04.

Prothoboard y pulsador.

Cables de conexión.

Manuales técnicos.

Resistencias de diversos valores (100Kohm, 120 Kohm)

Diodos LED´s.

Condensadores de diversos valores: 0.1 uF, 4.7uF, 10uF.

IMPLEMENTACION:

1) Implementar el contador asíncrono “UP” modulo 16 mostrado en la Figura 1. Analice su

funcionamiento, desarrolle la Tabla de estados y construir el diagrama de tiempo;

(Sugerencia Usar IC 74LS76)

Figura 1 Contador asíncrono “UP” módulo 16

Funcionamiento con IC 74LS76: Este contador se encuentra constituido por flip-flop JK en

modo de conmutación al mantener presente en las entradas J y K un 1 lógico y conectados

entre sí de forma asíncrona, es decir, que la salida del flip-flop 1 está conectada de forma

directa a la entrada de reloj del siguiente flip-flop 2 . Los indicadores de salida dan una

señal binaria, donde el indicador Q1 es el LSB (Bit Menos Significativo), el indicador (Q4) es

el MSB (Bit Más Significativo).

El circulito en la entrada de reloj (CLK) de los flip-flops (IC 74LS76), nos indica que trabajan

o conmutan con lógica negativa, es decir, que se activan en la transición de ALTA a BAJA

(flanco posterior) del pulso de reloj y la salida del flip-flop 1 (Q1) va del nivel BAJO al ALTO

dando como resultado la cuenta binaria 0001. En el pulso 2, en la transición del nivel ALTO

a BAJO, flip-flop 1 se desactiva pasando su salida del nivel ALTO a BAJO, activando el flip-

flop 2, conmutando la salida del nivel BAJO a ALTO generando la cuenta 0010, en el pulso

3 del reloj se activa flip-flop 1 generando la salida 0011, porque flip-flop 2 se encuentra en

mantenimiento teniendo su salida (Q2) activada, en el siguiente pulso se incrementa la

cuenta a 0100, según se observa en el diagrama de tiempo de la figura 3.

Sistemas Digitales : 2013-B

Ing. Utrilla Salazar Darío

Universidad Nacional del Callao

Facultad de Ingeniería Eléctrica y Electrónica

Estados Q4 Q3 Q2 Q1

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 1 0 1 0

11 1 0 1 1

12 1 1 0 0

13 1 1 0 1

14 1 1 1 0

15 1 1 1 1

Figura 2 Tabla de estados

Figura 3 Diagrama de tiempo

2) Al circuito contador asíncrono “UP” modulo 16 de la Figura 1, modificar para que pueda

realizar la función de:

a) Contador “UP” modulo 13

b) Contador “UP” modulo 10

c) Contador “UP” modulo 7

Modificando el contador de módulo 16 con IC 74LS76 en proteus sería el siguiente

circuito:

Sistemas Digitales : 2013-B

Ing. Utrilla Salazar Darío

Universidad Nacional del Callao

Facultad de Ingeniería Eléctrica y Electrónica

Este circuito puede operar como un Contador “UP” modulo 7, Contador “UP” modulo 10 ó

Contador “UP” modulo 13 solo debemos de seleccionar en el DIP-SWITCH el modulo

deseado.

3) Al circuito contador asíncrono “UP” de la Figura 1, configurar para que realice la función

de divisor de frecuencia entre:

a) Divisor entre 15

b) Divisor entre 12

c) Divisor entre 10

El contaje de pulsos se encuentra asociado directamente a la división de la frecuencia de

los mismos: los biestables de un contador «completo» (módulo n potencia entera de 2)

proporcionan en sus salidas ondas digitales cuyas frecuencias son, respectivamente, la

mitad (1/2), la cuarta parte (1/4), la octava parte (1/8),… (1/2i)…, de la frecuencia de los

pulsos de entrada.

En el caso de un contador «parcial» (módulo n, siendo n un número cualquiera), tomando

como salida la de su biestable de valor más significativo, se obtiene la división por n de la

frecuencia de los pulsos que recibe, es decir, produce un pulso en su salida por cada n

pulsos en su entrada.

En el siguiente circuito se ha configurado la figura 1 para obtener divisores de frecuencias

de 10, 12 y 15 según se seleccione en el DIP-SWITCH.

Sistemas Digitales : 2013-B

Ing. Utrilla Salazar Darío

Universidad Nacional del Callao

Facultad de Ingeniería Eléctrica y Electrónica

4) Implementar el circuito contador síncrono, cuyo diagrama se muestra en la Figura 2,

analice su funcionamiento, desarrolle su tabla de estados y graficar el diagrama de

tiempos de Qn, Q2n, Q3n y Q4n. (Considere Qn: LSB Q4n: MSB) Para su implementación

utilice IC 74LS76.

Figura 2. Circuito contador síncrono.

Sistemas Digitales : 2013-B

Ing. Utrilla Salazar Darío

Universidad Nacional del Callao

Facultad de Ingeniería Eléctrica y Electrónica

De la figura podemos encontrar las relaciones entre las salidas Q presentes y las entradas J y K de

cada uno de los FF usados:

J1=𝑄2 𝑄4 + 𝑄4 ⊕ 𝑄3 ; K1=Q4 + 𝑄2 ⊕ 𝑄3

J2=𝑄1 (𝑄4 + 𝑄3) ; K2=𝑄1(Q4+Q3)

J3=Q1+ 𝑄2 ⊕ 𝑄4 ; K3=Q2+ 𝑄1 Q3

J4= 𝑄2 + 𝑄1 (𝑄3) ; K4=𝑄3 + 𝑄2

Tabla de estados:

Estados Q4 Q3 Q2 Q1

0 0 0 0 0

15 1 1 1 1

10 1 0 1 0

5 0 1 0 1

13 1 1 0 1

4 0 1 0 0

11 1 0 1 1

6 0 1 1 0

1 0 0 0 1

12 1 1 0 0

0 0 0 0 0

Tiene 10 estados y se trata de un contador escalador

5) Implementar un circuito contador síncrono UP/DOWN módulo 10, utilizando el diseño

del informe previo del presente laboratorio. Utilice Flip Flops JK.

Sistemas Digitales : 2013-B

Ing. Utrilla Salazar Darío

Universidad Nacional del Callao

Facultad de Ingeniería Eléctrica y Electrónica

6) Implementar el circuito de un contador síncrono, descrito por las funciones Lógicas de

los Flip Flops; analice su funcionamiento, desarrolle su tabla de estados y su diagrama de

tiempos. (Para su implementación. Sugerencia Utilice IC 74LS76). Considere Q4n : MSB

Qn : LSB.

J4 = (Qn)´ + Q2n

K4 = Qn +Q2n +Q3n

J3 = (Qn)´

K3 = (Q4n)´

J2 = Qn (Q3n)´ + (Qn)´Q3n Q4n

K2 = (Qn)´+ Q3n

J1 = (Q2n)´ Q4n

K1 = Q2n (Q3n)´+ (Q2n)´(Q4n)´

Implementación en proteus:

Tabla de estados:

Estados Q4 Q3 Q2 Q1

0 0 0 0 0

12 1 1 0 0

7 0 1 1 1

9 1 0 0 1

3 0 0 1 1

12 1 0 1 0

4 0 1 0 0

8 1 0 0 0

13 1 1 0 1

5 0 1 0 1

0 0 0 0 0

Tiene 10 estados y se trata de un contador escalador

Sistemas Digitales : 2013-B

Ing. Utrilla Salazar Darío

Universidad Nacional del Callao

Facultad de Ingeniería Eléctrica y Electrónica

OBSERVACIONES Y CONCLUSIONES:

1) Las tablas de verdad han sido utilizadas como herramientas para obtener conclusiones

respecto al funcionamiento u operación de los circuitos realizados.

2) Los sistemas digitales en la actualidad son muy empleados y para aplicaciones específicas

es necesario realizar el diseño de estos circuitos, el procedimiento de diseño de los

circuitos contadores son muy parecidos y empleando la misma lógica se puede extender a

contadores de cualquier cantidad de bits.

3) Debemos de tener mucho cuidado al momento de la implementación en el prothoboard.

BIBLIOGRAFIA:

1) Alan Marcovitz B. Diseño Digital. 2ª edición Editorial Mc Graw Hill.

2) Enrique Mandado. Sistemas Electrónicos Digitales. 7ª Edición. Biblioteca UDB.

3) Morris Mano. Diseño Digital. 1ª Edición. Editorial Prentice Hall. Biblioteca UDB.

4) John F. Wakerly. Diseño Digital, principios y prácticas. Editorial Prentice Hall.

5) Louis Nashelsky. Fundamentos de tecnología digital. 1ª Edición. Noriega

Editores, Limusa.

6) Ronald J. Tocci. Sistemas digitales, principios y aplicaciones. Biblioteca UDB.

Sistemas Digitales : 2013-B

Ing. Utrilla Salazar Darío

Вам также может понравиться

- Planeacion EXPONERДокумент9 страницPlaneacion EXPONERbaad13Оценок пока нет

- apuntesIC4 PDFДокумент174 страницыapuntesIC4 PDFbaad13Оценок пока нет

- Informe Previo 4 DigitalesДокумент19 страницInforme Previo 4 Digitalesbaad13Оценок пока нет

- EC-2322 Carta de Smith PDFДокумент8 страницEC-2322 Carta de Smith PDFbaad13Оценок пока нет

- Tema 9 Espacio de Estados PDFДокумент34 страницыTema 9 Espacio de Estados PDFbaad13Оценок пока нет

- PPTCap4 1 PDFДокумент160 страницPPTCap4 1 PDFbaad13Оценок пока нет

- PPTCap4 1 PDFДокумент160 страницPPTCap4 1 PDFbaad13Оценок пока нет

- MT227 FormasCanonicas PDFДокумент16 страницMT227 FormasCanonicas PDFbaad13Оценок пока нет

- Informe Final #01Документ13 страницInforme Final #01baad13Оценок пока нет

- Trabajo S 1Документ21 страницаTrabajo S 1baad13Оценок пока нет

- EspacioEstado3 PDFДокумент6 страницEspacioEstado3 PDFbaad13Оценок пока нет

- Sumador de 4 BitsДокумент11 страницSumador de 4 Bitsbaad13Оценок пока нет

- 05 PresentationcontadoresДокумент51 страница05 PresentationcontadoresjavierscribbbОценок пока нет

- Sistemas Distribuidos Orientados A ServiciosДокумент19 страницSistemas Distribuidos Orientados A Serviciosbaad13Оценок пока нет

- Int - Tele Final5Документ16 страницInt - Tele Final5baad13Оценок пока нет

- Final de Intro A Tele1Документ24 страницыFinal de Intro A Tele1Billy Markos Felix GutierrezОценок пока нет

- Int - Tele Final6Документ14 страницInt - Tele Final6baad13Оценок пока нет

- Gestion Academica - Grupo1Документ13 страницGestion Academica - Grupo1baad13Оценок пока нет

- 2 - Congreso de La Republica - Inf. Final Sobre ChoropampaДокумент25 страниц2 - Congreso de La Republica - Inf. Final Sobre ChoropampadiegoemetОценок пока нет

- Tema 2 EdCДокумент66 страницTema 2 EdCbaad13Оценок пока нет

- Informe Previo 01Документ19 страницInforme Previo 01baad13Оценок пока нет

- Digitales I - Previo 5Документ21 страницаDigitales I - Previo 5baad13Оценок пока нет

- Código Arduino Sensor de PulsosДокумент1 страницаCódigo Arduino Sensor de Pulsosbaad13Оценок пока нет

- BiestablesДокумент2 страницыBiestablesbaad13Оценок пока нет

- Ficha Técnica Crystal PlugДокумент2 страницыFicha Técnica Crystal PlugJose Abanto CruzОценок пока нет

- Solved Exercises From Pindyck's MicroeconomicsДокумент6 страницSolved Exercises From Pindyck's MicroeconomicsMateo King73% (11)

- Cómo Desinstalo Mi Producto de Seguridad ESET ManualmenteДокумент8 страницCómo Desinstalo Mi Producto de Seguridad ESET ManualmenteceucihОценок пока нет

- Bioetica Tarea 3Документ4 страницыBioetica Tarea 3José Luis Alonso EscamillaОценок пока нет

- Panel Solar CaseroДокумент11 страницPanel Solar CaseroVilma Sonia Chavez Condori80% (5)

- Formato SIB 02Документ4 страницыFormato SIB 02Jhonny AlbertoОценок пока нет

- Violencia 5Документ7 страницViolencia 5Wilber Condori ChoqueОценок пока нет

- 6 7 y 8 GuytonДокумент6 страниц6 7 y 8 Guytontonolo100% (1)

- 5to Año - Castellano.Manual de Instrucciones Unidad 2Документ6 страниц5to Año - Castellano.Manual de Instrucciones Unidad 2eliiana MuňozОценок пока нет

- Baterias Niquel-CadmioДокумент10 страницBaterias Niquel-CadmioMarcos Fernández PeñafielОценок пока нет

- AguaДокумент2 страницыAguaGabriela QuerevalúОценок пока нет

- Entrega Final Del Proyecto Investigativo.Документ24 страницыEntrega Final Del Proyecto Investigativo.Aporte Simple SASОценок пока нет

- Sigma16 Es BDДокумент2 страницыSigma16 Es BDautoelevadoresОценок пока нет

- S3-Tarea 3.1tasas de Conversión y Construcción de Ventas PDFДокумент8 страницS3-Tarea 3.1tasas de Conversión y Construcción de Ventas PDFIsabel PinedaОценок пока нет

- Enfoques Por CompetenciaДокумент6 страницEnfoques Por CompetenciaKarla Carolina Ore RodasОценок пока нет

- Matematicas Financieras 1 PDFДокумент271 страницаMatematicas Financieras 1 PDFSofi Alvarez100% (3)

- De Máquina TérmicaДокумент26 страницDe Máquina TérmicaJosé Stalin Palacios YungaОценок пока нет

- Barrio Villa JimenezДокумент16 страницBarrio Villa JimenezFernanda MoralesОценок пока нет

- La Mecánica de La Dominación InternaДокумент2 страницыLa Mecánica de La Dominación InternaEduardo Ramirez MarcosОценок пока нет

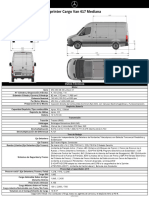

- Sprinter CargoVan 417 Mediana - 90764313-MXFДокумент1 страницаSprinter CargoVan 417 Mediana - 90764313-MXFManuel SalinasОценок пока нет

- Panasonic KX-TG1711 Wireless PhoneДокумент36 страницPanasonic KX-TG1711 Wireless PhoneIsmael TuzОценок пока нет

- 04-Unidad 03 - Ejercicio de Reforzamiento - Conocimiento y Sus TiposДокумент8 страниц04-Unidad 03 - Ejercicio de Reforzamiento - Conocimiento y Sus TiposJavier UcañanОценок пока нет

- Estudio de Los Valores Plásticos, Modelado y Tallado para La Creación de Obras EscultóricasДокумент12 страницEstudio de Los Valores Plásticos, Modelado y Tallado para La Creación de Obras EscultóricasDannes BustillosОценок пока нет

- Ejercicios06 MateBasica Posgrado 2021 2Документ2 страницыEjercicios06 MateBasica Posgrado 2021 2Davito Andrés RochaОценок пока нет

- Geometria AplicadaДокумент13 страницGeometria AplicadaFernando David Mendizabal MendozaОценок пока нет

- Análisis de Mercado para The Balance BowlДокумент3 страницыAnálisis de Mercado para The Balance BowlBrayan MuñozОценок пока нет

- Seguridad Ocupacional ChinalcoДокумент48 страницSeguridad Ocupacional ChinalcoAxel Vinces60% (5)

- TeatroДокумент10 страницTeatrovityaОценок пока нет

- Ponencias FotovoltaicaДокумент58 страницPonencias FotovoltaicaPablo VazquezОценок пока нет

- Laboratorio N4Документ2 страницыLaboratorio N4Jonathan Chafloque TasaycoОценок пока нет