Академический Документы

Профессиональный Документы

Культура Документы

Analysis of Low Power High Speed Carry Skip Adder

Загружено:

IJRASETPublicationsАвторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Analysis of Low Power High Speed Carry Skip Adder

Загружено:

IJRASETPublicationsАвторское право:

Доступные форматы

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue V, May 2018- Available at www.ijraset.com

Analysis of Low Power High Speed Carry Skip

Adder

Miss. Rakhi G. Tale1, Prof. Dr. R.M. Deshmukh2

1

Department of Electronics and Telecommunication DRGITR, Amravati, Maharashtra, India

2

(HOD) Department of Electronics and Telecommunication, DRGITR, Amravati, Maharashtra India

Abstract: Adders are a key building obstruct in number juggling and rationale units. Along these lines expanding their speed

firmly influence the speed of processor itself. In this paper a carry skip adder(CSKA) structure that has a higher speed yet

bring down vitality utilization contrasted and the customary one is proposed. The speed improvement is accomplished by

joining link and incrementation plans to customary CSKA (Conv-CSKA) structure. What's more, rather than using multiplexer

rationale, the proposed structure makes utilization of AND-OR-Invert (AOI) as well as AND-Invert (OAI) compound entryways

for the skip rationale. The structure might be acknowledged with both settled stage size(FSS) and variable stage measure (VSS)

styles, wherein the latter additionally makes strides the speed and vitality parameters of the viper. At last, a crossover variable

dormancy augmentation of the proposed structure, which brings down the power utilization without extensively affecting the

speed, is displayed. This augmentation uses a modified parallel structure for expanding the slack time, and subsequently,

empowering further voltage lessening.

Keywords: CSKA, Incrementation block, carry skip logic.

I. INTRODUCTION

There are numerous approaches to enhance the execution of advanced circuits. One of the most effortless path is to diminish the

supply voltage. This relies upon the way that the exchanging vitality has a quadratic reliance on supply voltage. Contingent upon

the supply voltage decrease, when the gadget is in the ON state, it works in super limit, close edge or sub edge districts. In these

three locales of activity, the close edge area gives a reasonable tradeoff between control utilization and postponement. In extra to

the handle of supply voltage. One can look over an assortment of viper families. There are various snake families like convey

select viper, swell convey viper, convey skip snake, parallel prefix viper and so on. Looking at the qualities of various snake

families. The convey skip snake is observed to be the one which is most reasonable for the development of a quick adder.The

consistently expanding interest for portable electronic gadgets requires the utilization of energy proficient VLSI circuits.

Calculations in these gadgets should be performed utilizing low-control, region proficient circuits working at more noteworthy

speed. Expansion is the most essential number-crunching task; and viper is the most major number-crunching part of the

processor. Adders are enter building obstruct in number juggling and rationale units (ALUs). There are numerous takes a shot at

the subject of advancing the speed and energy of these units, which have been accounted for in [1-5]. It is exceptionally attractive

to accomplish higher velocities at low-control/vitality utilizations, which is a test for the architects of broadly useful processors.

One of the viable methods to bring down the power utilization of advanced circuits is to diminish the supply voltage because of

quadratic reliance of the exchanging vitality on the voltage and expansion to the handle of the supply voltage, one may pick

between various snake structures/families for streamlining force and speed. There are numerous viper families with various

postponements, control utilizations, and territory uses. Illustrations incorporate swell convey snake (RCA), convey increase viper

(CIA), convey skip viper (CSKA), convey select snake (CSLA), and parallel prefix adders (PPAs). The portrayals of every one of

these viper models alongside their attributes might be found in [6]. The RCA has the most straightforward structure with the

littlest territory and power utilization yet with the most exceedingly awful basic way delay. In the CSLA, the speed, control

utilization, and region uses are significantly bigger than those of the RCA. The PPAs, which are likewise called convey look-ahead

adders, abuse guide parallel prefix structures to produce the convey as quick as could reasonably be expected. There are diverse

sorts of the parallel prefix calculations that prompt distinctive PPA structures with various exhibitions. For instance, the Kogge–

Stone snake (KSA) [2] is one of the speediest structures however brings about vast power utilization and region use. It ought to be

noticed that the structure complexities of PPAs are more than those of other snake plans. The CSKA, which is an effective viper as

©IJRASET: All Rights are Reserved 2174

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue V, May 2018- Available at www.ijraset.com

far as power utilization and zone use. It is intended to accelerate the option activity by including a proliferation of bear bit a bit of

whole snake [7]. The basic way deferral of the CSKA is significantly littler than the one in the RCA, though its territory and

power utilization are like those of the RCA. Convey skip snake has the upside of short postponement and high registering

productivity so causes wide consideration. What's more, because of the modest number of transistors, the CSKA profits by

generally short wiring lengths and a customary and basic design [7-9]. In this paper, we have actualized an integral multiplexer as

a skip rationale utilizing TANNER EDA instrument for rapid and low power utilization of a 4 bit convey skip snake. The

developing business sector of convenient (e.g., mobile phones, gaming comforts, and so on.), battery powered electronic

frameworks requests microelectronic circuits outline with ultralow control dispersal. As the joining, size, and many-sided quality

of the chips keep on increasing, the trouble in giving satisfactory cooling may either include huge cost or point of confinement the

usefulness of the figuring frameworks which make utilization of those incorporated circuits.

II. LITERATURE REVIEW

A static CMOS CSKA structure called CI-CSKA was proposed, which displays a higher speed and lower vitality utilization

contrasted and those of the traditional one. The speed improvement was accomplished by altering the structure through the

connection and incremenation methods. Likewise, AOI and OAI compound doors were abused for the convey skip rationales. [1]

The basic way postponement of the CSKA is significantly littler than the one in the RCA, though its territory and power utilization

are like those of the RCA. What's more, the power-defer item (PDP) of the CSKA is littler than those of the CSLA and PPA

structures [1].

The paper [2] entitled, the execution parameters of postponement, normal power, PDP and EDP are thought about at various

innovation hub. Most pessimistic scenario postponement can be lessened with various strategies which has been proposed for full

adders, it gives a streamlining methods that is Static CMOS innovation and Pass Transistor rationale utilized just for the instance

of consistent square size to enhance the speed execution.

CMOS rationale, every rationale organize is controlled by input flag which contain pull up system and draw down system. In the

Pass Transistor rationale (PTL), it lessens the quantity of transistor which are utilized to outline all the kind of rationale gates[2].

The correlation of normal energy of CMOS and PTL procedures of convey skip viper with supply voltage variety, it is watched that

CMOS methods devours more power than the PTL system.

The paper [3] entitled, A novel incrementer circuit then phases of the CSA by ascertaining do (C0) of the square in parallel

alongside third piece by utilizing a parallel chain of AND doors, though an arrangement example of convey proliferation is

utilized as a part of RCA structure, which decreases the deferral of augmenting in CSA when contrasted and the traditional RCA

is utilized. CSA decreased proliferation defer attributes.

The paper [4] entitled, The essential thought of this work is to utilizes straightforward and zone productive entryway level

alteration to lessen zone and energy of CSLA. In that the Binary to Excess-1 Converter (BEC) is utilized rather than RCA with

Cin=1 in the standard CSLA to accomplish bring down region and power utilization. The upsides of BEC rationale originates

from the lesser number of rationale doors than n-bit full viper structure. A n+1-bit BEC is required to supplant the n-bit RCA.

The paper [5] entitled, an effective Carry select snake by sharing the Common Boolean rationale (CBL) term is utilized. In this

paper, an effective technique utilized that replaces the BEC utilizing Common Boolean Logic. After a rationale disentanglement,

just a single OR entryway and one inverter door for convey and summation task has been required. Through the multiplexer, the

right yield as indicated by the rationale conditions of the convey in flag has been chosen.

The paper [6] entitled, the convey select (CS) activity is plan before the computation of conclusive aggregate, which is not quite

the same as the ordinary approach. Bit examples of two expecting convey words (relating to cin = 0 and 1) and settled cin bits are

utilized for rationale streamlining of CS and age units. An effective CSLA configuration is gotten utilizing streamlined rationale

units. Because of little convey yield delay, the proposed CSLA configuration is great contender for the square-root (SQRT) CSLA.

[6]

III. ADDER ARCHITECTURES

Multiple-bit addition can be as simple as connecting several full adders in series or it can be more complex. How the full adders

are connected or the technique that is used for adding multiple bits defines the adder architecture. Architecture is the most

©IJRASET: All Rights are Reserved 2175

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue V, May 2018- Available at www.ijraset.com

influential property on the computation time of an added. This property can limit the overall performance. In general the

computation time is proportional to the number of bits implemented in the adder. Many different adder architectures have been

proposed to reduce or eliminate this proportional dependence on the number of bits. Several adder architectures are reviewed in

the following sections.

Fig 1: conventional structure of CSKA

Different piece expansion can be as basic as interfacing a few full adders in arrangement or it can be more intricate. How the full

adders are associated or the procedure that is utilized for including numerous bits characterizes the snake design. Design is the

most persuasive property on the calculation time of an additional. This property can restrain the general execution. By and large

the calculation time is corresponding to the quantity of bits actualized in the snake. A wide range of snake designs have been

proposed to diminish or kill this corresponding reliance on the quantity of bits. A few snake structures are evaluated in the

accompanying segments.

The customary structure of the CSKA comprises of stages containing chain of full adders (FAs) (RCA piece) and 2:1 multiplexer

(convey skip rationale). The RCA squares are associated with each other through 2:1 multiplexers, which can be set into at least

one level structures. The CSKA design (i.e., the quantity of the FAs per organize) greatly affects the speed of this sort of viper [1].

A CSKA performs quick expansion since adders are part in pieces of N bits. It incredibly lessens the deferral of the viper through

its basic way, since the convey bit for each piece can be skirted (skip) over the squares. It comprises of straightforward RCA with

an AND-OR skip rationale as appeared in Figure 3. It creates complete from each piece contingent upon MSB full snake do, LSB

full viper convey in and entirety bit of each full viper. On the off chance that the AND-OR skip rationale yield is 1, the present

piece will be skirted and next square will begin calculation [1].

A. Proposed CSKA structure

The structure depends on joining the connection and the incrementation plans with the Conv-CSKA structure, and subsequently, is

signified by CI-CSKA. It furnishes us with the capacity to utilize easier convey skip rationales. The rationale replaces 2:1

multiplexers by AOI/OAI compound doors . The entryways, which comprise of less transistors, have bring down postponement,

territory, and littler power utilization contrasted and those of the 2:1 multiplexer. Note that, in this structure, as the bring spreads

through the skip rationales, it moves toward becoming supplemented. Along these lines, at the yield of the skip rationale of even

stages, the supplement of the convey is produced. The structure has an extensive lower proliferation delay with a somewhat littler

region contrasted and those of the ordinary one. Note that while the power utilizations of the AOI (or OAI) door are littler than

that of the multiplexer, the power utilization of the proposed CI-CSKA is somewhat more than that of the regular one. This is

because of the expansion in the quantity of the entryways, which forces a higher wiring capacitance (in the noncritical paths)The

purpose behind utilizing both AOI and OAI compound doors as the skip rationales is the upsetting elements of these doors in

standard cell libraries. Along these lines the requirement for an inverter door, which expands the power utilization and deferral, is

disposed of. On the off chance that an AOI is utilized as the skip rationale, the following skip rationale should utilize OAI door.

Furthermore, another point to specify is that the utilization of the proposed skipping structure in the Conv-CSKA structure builds

the postponement of the basic way impressively. This begins from the way that, in the Conv-CSKA, the skip rationale (AOI or

OAI compound doors) can't sidestep the zero convey contribution until the point when the zero convey input engenders from the

comparing RCA square. To take care of this issue, in the proposed structure, we have utilized a RCA hinder with a convey

©IJRASET: All Rights are Reserved 2176

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue V, May 2018- Available at www.ijraset.com

contribution of zero (utilizing the link approach). Along these lines, since the RCA piece of the stage does not have to sit tight for

the convey yield of the past stage, the yield conveys of the squares are ascertained in parallel.

Fig.2 Proposed CI-CSKA structure

Fig.3 Incrementation Block

The inward structure of the incrementation piece, which contains a chain of half-adders (HAs), is appeared in Fig. 3. Also, take

note of that, to diminish the deferral extensively, to compute the convey yield of the stage, the convey yield of the incrementation

square isn't utilized.

B. Hybrid Variable Latency CSKA Structure

The fundamental thought behind utilizing VSS CSKA structures was in view of nearly adjusting the deferrals of ways to such an

extent that the postponement of the basic way is limited contrasted and that of the FSS structure . This denies us from having the

Opportunity of utilizing the slack time for the supply voltage scaling. To give the variable dormancy highlight to the VSS CSKA

structure, we supplant a portion of the center stages in our proposed structure with a PPA adjusted in this paper. It ought to be

noticed that since the Conv-CSKA structure has a lower speed than that of the proposed one, in this area, we don't think about the

customary structure.

Fig.4 Hybrid variable latency CSKA

©IJRASET: All Rights are Reserved 2177

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue V, May 2018- Available at www.ijraset.com

Fig.5 Conventional CSKA

Fig.6 Conventional CSKA waveform

Fig.7 Proposed CSKA

Fig.8 Proposed CSKA waveform

Fig. 9 Hybrid CSKA

©IJRASET: All Rights are Reserved 2178

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue V, May 2018- Available at www.ijraset.com

Fig. 10 Hybrid CSKA waveform

III. RESULT ANALYSIS

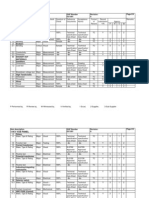

Table:1 Depicts power and current values at 5V.

Sr Parameters Conventiona Proposed Hybrid

no. l

1 Leakage 26u 245.11u 174.42

Current(A u

mpere)

2 Power 132u 1.225m 872.1u

(Watt)

Table:2 Depicts power and current values at 4.9V.

Sr Parameters Conventiona Proposed Hybrid

no. l

1 Leakage 25.24u 227.57u 162.2u

Current(A

mpere)

2 Power 123.7u 1.11m 794.8u

(Watt)

Table:3 Depicts power and current values at 4.8V.

Sr Parameter Convention Proposed Hybrid

no. s al

1 Leakage 24.04u 210.4u 150.2u

Current(A

mpere)

2 Power 115.40u 1.010m 721.2u

(Watt)

Table:4 Depicts power and current values at 4.7V.

Sr Parameters Conventiona Proposed Hybrid

no. l

1 Leakage 22.89u 193.6u 135.8u

Current(A

mpere)

2 Power 107.59u 510.3 651.3u

(Watt)

©IJRASET: All Rights are Reserved 2179

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue V, May 2018- Available at www.ijraset.com

IV. CONCLUSION

This paper gives study of various adder like conventional, proposed and Hybrid CI-CSKA. In conv- CSKA the 2.1 mux is used

which is replaced by AOI, OAI gates. Which requires few transistor than 2:1 mux The total number of transistor count required

is less which reduces area and power dissipation. This paper analyzed the speed enhancement, achieved by applying

concatenation and incrimination schemes to improve the efficiency of the conventional CSKA structure.The speed enhancement

was achieved by modifying the structure through the concatenation and incrimination techniques. In addition, AOI and OAI

compound gates were developed for the carry skip logics. This paper analysed the current and power at different supply voitage

levels. The result suggested that hybrid CSKA consumed low power and a better candidate for the high speed application.

REFERENCES

[1] Milad Bahadori, Mehdi Kamal, Ali Afzali-Kusha, Senior Member, IEEE, and Massoud Pedram, Fellow, IEEE, “High-Speed and Energy-Efficient Carry Skip

Adder Operating Under a Wide Range of Supply Voltage Levels IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS,

VOL. 24, NO. 2, FEBRUARY 2016

[2] Pournima Pankaj Patil' and Archana Arvind Hatkar “Comparative Analysis of 8 Bit Carry Skip Adder using CMOS and PTL Techniques with Conventional

MOSFET at 32 Nanometer Regime 1st IEEE International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES-2016)

[3] Samiappa Sakthikumaran1, S. Salivahanan, V. S. Kanchana Bhaaskaran2, V. Kavinilavu, B. Brindha and C. Vinoth “A Very Fast and Low Power Carry Select

Adder Circuit” 978-1-4244-8679-3/11/$26.00 ©2011 IEEE.

[4] B. Ramkumar and H.M. Kittur, “Low-power and area-efficient carry-select adder,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 2, pp. 371–

375, Feb. 2012

[5] S.Manju and V. Sornagopal, “An efficient SQRT architecture of carry select adder design by common Boolean logic,” in Proc. VLSI ICEVENT, 2013, pp. 1–5

[6] Basant Kumar Mohanty, Senior Member, IEEE, and Sujit Kumar Patel, “Area–Delay–Power Efficient Carry-Select Adder”, IEEE TRANSACTIONS ON

CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 61, NO. 6, JUNE 2014

[7] Y. He and C.-H. Chang, “A power-delay efficient hybrid carrylookahead/ carry-select based redundant binary to two’s complement converter,” IEEE Trans.

Circuits Syst. I, Reg. Papers, vol. 55, no. 1, pp. 336–346, Feb. 2008.

[8] C.-H. Chang, J. Gu, and M. Zhang, “A review of 0.18 μm full adder performances for tree structured arithmetic circuits,” IEEE Trans. Very Large Scale Integr.

(VLSI) Syst., vol. 13, no. 6, pp. 686–695, Jun. 2005

[9] D. Markovic, C. C. Wang, L. P. Alarcon, T.-T. Liu, and J. M. Rabaey, “Ultralow-power design in near-threshold region,” Proc. IEEE, vol. 98, no. 2, pp. 237–252,

Feb. 2010.

[10] S. Jain et al., “A 280 mV-to-1.2 V wide-operating-range IA-32processor in 32 nm CMOS,” in IEEE Int. Solid-State Circuits Conf.Dig. Tech. Papers (ISSCC), Feb.

2012, pp. 66–68.

[11] R. Zimmermann, “Binary adder architectures for cell-based VLSI andtheir synthesis,” Ph.D. dissertation, Dept. Inf. Technol. Elect. Eng., Swiss Federal Inst.

Technol. (ETH), Zürich, Switzerland, 1998.

[12] D. Harris, “A taxonomy of parallel prefix networks,” in Proc. IEEE Conf.Rec. 37th Asilomar Conf. Signals, Syst., Comput., vol. 2. Nov. 2003,pp. 2213–2217.

[13] V. G. Oklobdzija, B. R. Zeydel, H. Dao, S. Mathew, and R. Krishnamurthy, “Energy-delay estimation technique for highperformance microprocessor VLSI

adders,” in Proc. 16th IEEE Symp. Comput. Arithmetic, Jun. 2003, pp. 272–279.

[14] K. Chirca et al., “A static low-power, high-performance 32-bit carryskip adder,” in Proc. Euromicro Symp. Digit. Syst. Design (DSD),Aug./Sep. 2004, pp. 615–

619

[15] M. Alioto and G. Palumbo, “A simple strategy for optimized design of one-level carry-skip adders,” IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 50,

no. 1, pp. 141–148, Jan. 2003

[16] Jia et al., “Static CMOS implementation of logarithmic skip adder,”in Proc. IEEE Conf. Electron Devices Solid-State Circuits, Dec. 2003,pp. 509–512

[17] H. Suzuki, W. Jeong, and K. Roy, “Low power adder with adaptivesupply voltage,” in Proc. 21st Int. Conf. Comput

[18] Y.-S. Su, D.-C. Wang, S.-C. Chang, and M. Marek-Sadowska, “Performanceoptimization using variable-latency design style,” IEEE Trans.Very Large Scale

Integr. (VLSI) Syst., vol. 19, no. 10, pp. 1874–1883, Oct. 2011.

[19] K. Du, P. Varman, and K. Mohanram, “High performance reliable variable latency carry select addition,” in Proc. Design, Autom., Test Eur. Conf. Exhibit.

(DATE), Mar. 2012, pp. 1257–1262.

[20] J. M. Rabaey, A. Chandrakasa, and B. Nikolic, Digital Integrated Circuits: A Design Perspective, 2nd ed. Englewood Cliffs, NJ, USA: Prentice-Hall, 2003..

Design, Oct. 2003,pp. 103–106

©IJRASET: All Rights are Reserved 2180

Вам также может понравиться

- IoT-Based Smart Medicine DispenserДокумент8 страницIoT-Based Smart Medicine DispenserIJRASETPublications100% (1)

- Advanced Wireless Multipurpose Mine Detection RobotДокумент7 страницAdvanced Wireless Multipurpose Mine Detection RobotIJRASETPublicationsОценок пока нет

- Design and Analysis of Fixed-Segment Carrier at Carbon Thrust BearingДокумент10 страницDesign and Analysis of Fixed-Segment Carrier at Carbon Thrust BearingIJRASETPublicationsОценок пока нет

- Skill Verification System Using Blockchain SkillVioДокумент6 страницSkill Verification System Using Blockchain SkillVioIJRASETPublicationsОценок пока нет

- Controlled Hand Gestures Using Python and OpenCVДокумент7 страницControlled Hand Gestures Using Python and OpenCVIJRASETPublicationsОценок пока нет

- Air Conditioning Heat Load Analysis of A CabinДокумент9 страницAir Conditioning Heat Load Analysis of A CabinIJRASETPublicationsОценок пока нет

- 11 V May 2023Документ34 страницы11 V May 2023IJRASETPublicationsОценок пока нет

- BIM Data Analysis and Visualization WorkflowДокумент7 страницBIM Data Analysis and Visualization WorkflowIJRASETPublicationsОценок пока нет

- Design and Analysis of Components in Off-Road VehicleДокумент23 страницыDesign and Analysis of Components in Off-Road VehicleIJRASETPublicationsОценок пока нет

- Design and Analysis of Fixed Brake Caliper Using Additive ManufacturingДокумент9 страницDesign and Analysis of Fixed Brake Caliper Using Additive ManufacturingIJRASETPublicationsОценок пока нет

- Credit Card Fraud Detection Using Machine Learning and BlockchainДокумент9 страницCredit Card Fraud Detection Using Machine Learning and BlockchainIJRASETPublications100% (1)

- Real Time Human Body Posture Analysis Using Deep LearningДокумент7 страницReal Time Human Body Posture Analysis Using Deep LearningIJRASETPublications100% (1)

- TNP Portal Using Web Development and Machine LearningДокумент9 страницTNP Portal Using Web Development and Machine LearningIJRASETPublicationsОценок пока нет

- A Review On Speech Emotion Classification Using Linear Predictive Coding and Neural NetworksДокумент5 страницA Review On Speech Emotion Classification Using Linear Predictive Coding and Neural NetworksIJRASETPublicationsОценок пока нет

- Experimental Study of Partial Replacement of Cement by Pozzolanic MaterialsДокумент9 страницExperimental Study of Partial Replacement of Cement by Pozzolanic MaterialsIJRASETPublicationsОценок пока нет

- Real-Time Video Violence Detection Using CNNДокумент7 страницReal-Time Video Violence Detection Using CNNIJRASETPublicationsОценок пока нет

- A Blockchain and Edge-Computing-Based Secure Framework For Government Tender AllocationДокумент10 страницA Blockchain and Edge-Computing-Based Secure Framework For Government Tender AllocationIJRASETPublicationsОценок пока нет

- Comparative in Vivo Study On Quality Analysis On Bisacodyl of Different BrandsДокумент17 страницComparative in Vivo Study On Quality Analysis On Bisacodyl of Different BrandsIJRASETPublicationsОценок пока нет

- Skin Lesions Detection Using Deep Learning TechniquesДокумент5 страницSkin Lesions Detection Using Deep Learning TechniquesIJRASETPublicationsОценок пока нет

- Low Cost Scada System For Micro IndustryДокумент5 страницLow Cost Scada System For Micro IndustryIJRASETPublicationsОценок пока нет

- Design and Development of Cost-Effective 3D-PrinterДокумент7 страницDesign and Development of Cost-Effective 3D-PrinterIJRASETPublicationsОценок пока нет

- CryptoDrive A Decentralized Car Sharing SystemДокумент9 страницCryptoDrive A Decentralized Car Sharing SystemIJRASETPublications100% (1)

- Preparation of Herbal Hair DyeДокумент12 страницPreparation of Herbal Hair DyeIJRASETPublications100% (1)

- Literature Review For Study of Characteristics of Traffic FlowДокумент10 страницLiterature Review For Study of Characteristics of Traffic FlowIJRASETPublicationsОценок пока нет

- Vehicles Exhaust Smoke Detection and Location TrackingДокумент8 страницVehicles Exhaust Smoke Detection and Location TrackingIJRASETPublications100% (1)

- Achieving Maximum Power Point Tracking With Partial ShadingДокумент10 страницAchieving Maximum Power Point Tracking With Partial ShadingIJRASETPublicationsОценок пока нет

- An Automatic Driver's Drowsiness Alert SystemДокумент7 страницAn Automatic Driver's Drowsiness Alert SystemIJRASETPublications100% (1)

- Smart Video Surveillance Using YOLO Algorithm and OpenCVДокумент8 страницSmart Video Surveillance Using YOLO Algorithm and OpenCVIJRASETPublications100% (1)

- Structural Design of Underwater Drone Using Brushless DC MotorДокумент9 страницStructural Design of Underwater Drone Using Brushless DC MotorIJRASETPublicationsОценок пока нет

- Application For Road Accident RescueДокумент18 страницApplication For Road Accident RescueIJRASETPublications100% (1)

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- 4.10) Arch Shaped Self Supporting Trussless Roof SpecificationsДокумент11 страниц4.10) Arch Shaped Self Supporting Trussless Roof Specificationshebh123100% (1)

- 701.ssvseat 1.04Документ2 страницы701.ssvseat 1.04Cosmin MuscaluОценок пока нет

- High Integrity Aluminum (GENERAL)Документ140 страницHigh Integrity Aluminum (GENERAL)Kmilo Giraldo100% (3)

- Car DeerДокумент2 страницыCar DeerNEGameandParksОценок пока нет

- Using Dapper Asynchronously inДокумент1 страницаUsing Dapper Asynchronously inGiovani BrondaniОценок пока нет

- Concept of Circulation in A Free Vortex FlowДокумент55 страницConcept of Circulation in A Free Vortex FlowAnil KumarОценок пока нет

- Trade List 13 Mar 2019Документ74 страницыTrade List 13 Mar 2019Bharat JainОценок пока нет

- Report On Automatic Phase Changer: Submitted ByДокумент32 страницыReport On Automatic Phase Changer: Submitted ByAndrea JohnsonОценок пока нет

- 6-C-RIIMPO301E - Conduct Hydraulic Excavator Operations - Learner Guide - V 1.1 02122019 PDFДокумент31 страница6-C-RIIMPO301E - Conduct Hydraulic Excavator Operations - Learner Guide - V 1.1 02122019 PDFOwen PerrinОценок пока нет

- The Right Stuff PDFДокумент4 страницыThe Right Stuff PDFNeelank Tiwari100% (1)

- Folder Fiamm Neptune 2010 EngДокумент4 страницыFolder Fiamm Neptune 2010 EngchokribОценок пока нет

- 500-600 Forklifts & Buckmaster: Parts CatalogДокумент281 страница500-600 Forklifts & Buckmaster: Parts CatalogRoberto Mariano100% (2)

- Build-A-Bard ABB - RFQ-807683Reaprovechamiento Relaves - SR For Cotejado 010A - HVACДокумент18 страницBuild-A-Bard ABB - RFQ-807683Reaprovechamiento Relaves - SR For Cotejado 010A - HVACchristianОценок пока нет

- Pds 55930Документ2 страницыPds 55930ekosuryonoОценок пока нет

- How To Measure MTFДокумент64 страницыHow To Measure MTFamtcorporationОценок пока нет

- Acceleration GrpahДокумент14 страницAcceleration GrpahRAFAEL TORRESОценок пока нет

- Nuevo CvuДокумент1 страницаNuevo CvuJesús GonzálezОценок пока нет

- Quality Assurance Plan (1) ..Документ5 страницQuality Assurance Plan (1) ..ARUNKUMARANNANBHEDAОценок пока нет

- FR-8x Editor Eng01 WДокумент8 страницFR-8x Editor Eng01 WRadulian Daniel100% (1)

- Adjusting Well Pump Pressure SwitchesДокумент1 страницаAdjusting Well Pump Pressure SwitchesD_D_76Оценок пока нет

- Ultra Petronne Interior Supply Corp.: Manufacturer of Light Metal FramesДокумент1 страницаUltra Petronne Interior Supply Corp.: Manufacturer of Light Metal Framesjun vincint geleraОценок пока нет

- C12200Документ3 страницыC12200xgiorg100% (1)

- Mech 3-Module 1Документ41 страницаMech 3-Module 1melkisidick angloanОценок пока нет

- MILL Series GB-1007 01Документ20 страницMILL Series GB-1007 01Ady IonutОценок пока нет

- 27C ChainДокумент19 страниц27C ChainyanaziОценок пока нет

- Good Practices in Government Resource Planning, Developed Vs Developing CountriesДокумент11 страницGood Practices in Government Resource Planning, Developed Vs Developing CountriesFreeBalanceGRPОценок пока нет

- Autodesk Inventor - Sheet Metal Punch IfeaturesДокумент6 страницAutodesk Inventor - Sheet Metal Punch IfeaturesNdianabasi UdonkangОценок пока нет

- PORTFOLIO: OFFICE WORK (20/06/2022-20/12/2022) Harleen KlairДокумент34 страницыPORTFOLIO: OFFICE WORK (20/06/2022-20/12/2022) Harleen KlairHarleen KlairОценок пока нет

- Iec60092-350 (Ed2 0) enДокумент7 страницIec60092-350 (Ed2 0) enAzad RahmanОценок пока нет

- Honeywell P7640B1032 Differential Pressure Sensors PDFДокумент2 страницыHoneywell P7640B1032 Differential Pressure Sensors PDFMarcello PorrinoОценок пока нет