Академический Документы

Профессиональный Документы

Культура Документы

Passo

Загружено:

Marcos Vinícius0 оценок0% нашли этот документ полезным (0 голосов)

9 просмотров12 страницОригинальное название

passo

Авторское право

© © All Rights Reserved

Доступные форматы

PDF, TXT или читайте онлайн в Scribd

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

0 оценок0% нашли этот документ полезным (0 голосов)

9 просмотров12 страницPasso

Загружено:

Marcos ViníciusАвторское право:

© All Rights Reserved

Доступные форматы

Скачайте в формате PDF, TXT или читайте онлайн в Scribd

Вы находитесь на странице: 1из 12

UNIVERSIDADE DE BRASÍLIA – UnB

FACULDADE GAMA - FGA

VERSÃO 1.0

MANUAL: ISE 14.7

AUTOR: GUSTAVO CALTABIANO EICHLER

SUPERVISÃO: PROFA. LOURDES BRASIL

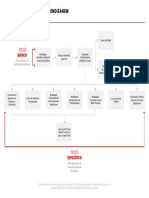

Passo a passo Portas OR, AND e XOR no ISE 14.7

1. Iniciar um novo projeto:

Vá na aba superior, clique no Item File e selecione New Project

2. Ao abrir a página de New Project Wizard, nomeie seu projeto e clique em Next. Em

seguida clique em Next novamente e depois em Finish.

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

3. Para iniciar um Codigo em VHDL, vá na aba superior e clique em Project e em seguida

New Source

4. Ao abrir o New Source Wizard, selecione o item VHDL Module e nomeie seu Projeto e

clique em Next.

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

5. Após o item 4, abrirá uma janela para especificar as entradas e saídas do projeto.

Nomeie as entradas e as saídas de acordo com o seu projeto e clique em Next e depois

Finish.

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

6. Agora na tela do computador temos o corpo do projeto montado. Para dar sequência

ao projeto, obtenha da tabela verdade das portas Or, And e Xor suas expressões

lógicas.

Fonte:http://www.bpiropo.com.br/graficos/FPC_AC20051003a.jpg

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

7. Obtendo as expressões lógicas da tabela acima, vamos ao código digitar a expressão

Lógica no espaço que segue logo após a palavra begin. Os códigos abaixo são

respectivamente And, Or e Xor.

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

8. Para simular o comportamento das portas lógicas criadas abriremos o item ISim, que

se localiza na parte esquerda da tela, lembre-se de estar no ambiente de simulação

para fazer esse procedimento. Ao abrir o item Isim duas opções ficarão disponíveis:

Check Syntax e Simulate Model. Clique duas vezes em simulate model para iniciar a

simulação.

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

9. Ao abrir a página de simulação, clique com o botão direito em uma das duas entradas

que foi especificada no seu projeto e selecione a opção Force clock. Force o clock para

as duas entradas especificadas no projeto trocando apenas o valor do período.

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

10. Selecione o item Run All ou o item ao lado direito para rodar de passo em passo na aba

superior para dar início a simulação.

11. Cheque os valores obtidos com os valores esperados para verificar o funcionamento

pleno do projeto. As imagens mostram respectivamente as simulações das portas And,

Or e Xor.

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

12. Para visualizar os níveis lógicos da simulação em forma de números, ao invés de

formas de onda, é possível um virtual bus clicando com o botão direito na entrada em

que você deseja e clicar em New Virtual Bus. Essa ferramenta transforma as formas de

onda em números que representam os níveis lógicos de cada entrada selecionada.

13. Fim do projeto.

Feito por: Gustavo Caltabiano Eichler

Data: 21/08/2016

Вам также может понравиться

- CAD - Projetos Elétricos PDFДокумент228 страницCAD - Projetos Elétricos PDFCelso BoniОценок пока нет

- Códigos de Transação em Contabilidade de Objetos de CustoДокумент4 страницыCódigos de Transação em Contabilidade de Objetos de CustoRui AlmeidaОценок пока нет

- Apol Analise de SistemasДокумент3 страницыApol Analise de SistemasWilliam Magalhaes100% (1)

- Treinamento - 2019 Rádio Full Outdoor Júlio Beltrão Mw-Rot-Nokia-2020Документ88 страницTreinamento - 2019 Rádio Full Outdoor Júlio Beltrão Mw-Rot-Nokia-2020Keilon AraujoОценок пока нет

- 158.054 Manual Controlador Digital Mam-680 (Formado Gibi) - 10-20Документ27 страниц158.054 Manual Controlador Digital Mam-680 (Formado Gibi) - 10-20Loja do Compressor100% (4)

- 02 Sdac 09 Arquitetura MicroprocessadoresДокумент21 страница02 Sdac 09 Arquitetura MicroprocessadoresAR*Оценок пока нет

- Área de Projecto - Grelha de Auto e Hetero - Avaliação - Sessão de Trabalho GrupoДокумент2 страницыÁrea de Projecto - Grelha de Auto e Hetero - Avaliação - Sessão de Trabalho Grupomajoper83% (18)

- Apostila Redes SociaisДокумент104 страницыApostila Redes Sociaisrrosa_996272Оценок пока нет

- 7 7000 0-00 11uspДокумент166 страниц7 7000 0-00 11uspEvandro Jva compressores100% (1)

- Exercicios Internet Parte1Документ5 страницExercicios Internet Parte1MarcellaFerreira100% (1)

- TS7200HD PDFДокумент2 страницыTS7200HD PDFHelio SoaresОценок пока нет

- Enq 2013Документ4 страницыEnq 2013Prof.EderОценок пока нет

- Manual Instalacao Do Assinador Digital Arisp W7 and VistaДокумент7 страницManual Instalacao Do Assinador Digital Arisp W7 and VistaalexОценок пока нет

- DS 11 Booleanas pt1 12032020Документ6 страницDS 11 Booleanas pt1 12032020Raphael Henrique SoaresОценок пока нет

- Como Adicionar Botão Voltar Ao TopoДокумент7 страницComo Adicionar Botão Voltar Ao Topojorge fevereiroОценок пока нет

- Tablet A7Документ4 страницыTablet A7Alessandro VieiraОценок пока нет

- Painel de Vagas Infovagas MaioДокумент14 страницPainel de Vagas Infovagas MaioDiego AОценок пока нет

- Acústica SubmarinaДокумент2 страницыAcústica SubmarinaClaudioTRodriguesОценок пока нет

- Talha Catraca GeralДокумент2 страницыTalha Catraca GeralantonyОценок пока нет

- Siafi 90032Документ4 139 страницSiafi 90032almacen2023hospitalОценок пока нет

- 540-Eletrotecnia, Cursos Com EquivalênciaaДокумент3 страницы540-Eletrotecnia, Cursos Com EquivalênciaaxupiterОценок пока нет

- Catálogo Compacto - RENNAДокумент8 страницCatálogo Compacto - RENNAGuilhermeОценок пока нет

- Esss Trilha Aprendizagem CFDДокумент1 страницаEsss Trilha Aprendizagem CFDTHIAGOОценок пока нет

- Formulario Preventiva - RodotremДокумент1 страницаFormulario Preventiva - RodotremRafael Recco BarbosaОценок пока нет

- Oficina 01 Tipos e Gêneros TextuaisДокумент27 страницOficina 01 Tipos e Gêneros Textuaisclebermirabela67% (3)

- Manual HirensДокумент36 страницManual HirensValdomiro Ferreira Cunha33% (3)

- Modelo Proposta Levantamento Planimetrico CadastralДокумент2 страницыModelo Proposta Levantamento Planimetrico CadastralPaulo HenriqueОценок пока нет

- Waves GTR Solo - Funciona Com o Win 7 64 Bit - KVR AudioДокумент4 страницыWaves GTR Solo - Funciona Com o Win 7 64 Bit - KVR AudioHélio MandecoОценок пока нет

- 3.1 4. Estrutura Do Script - Exercíco PDFДокумент5 страниц3.1 4. Estrutura Do Script - Exercíco PDFRivaldoCabralОценок пока нет

- Manual LotusДокумент659 страницManual LotusErika DavinoОценок пока нет