Академический Документы

Профессиональный Документы

Культура Документы

Portable Media Keeps Playing and Playing And... : Tuneintoe TV

Загружено:

hairol717549Исходное описание:

Оригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Portable Media Keeps Playing and Playing And... : Tuneintoe TV

Загружено:

hairol717549Авторское право:

Доступные форматы

electronic design

The Authority

on Emerging

Technologies for

Design Solutions

04.10.08

www.electronicdesign.com

Portable audio • Industrial wireless • Portable video • Visual robotic development • Embedded in ED

Portable

Media Keeps

Playing and

41

Playing

TECHNOLOGY REPORT

p| Invisible Links Revolutionize

Industrial Communications

ENGINEERING ESSENTIALS

47

and...

p| Success In Portable Video

Starts With A Balanced Design

DESIGN SOLUTION

p| 64 Mixed-Signal Processors Can Aid

Visual Robotic Development

Tune in to E NGINEERING TV. COM IC

C designers find innovative

ways

ay ttoo extend battery life in

portable

rtabl media players and

ltim

multimedia phones.

34

April 10, 2008 Vol. 56, No. 7

p|

$10.00 A Penton Publication

Periodicals Postage paid

USPS/100 Approved Poly

0410Cover_Spine.indd Cv1 3/27/08 2:35:44 PM

techview

MicroSemi’s PD64001 PSE controller sup- The availability of real PoE Plus chips poses

Only Bud offers the ports current levels up to 720 mA (36 W at at least two interesting questions. The first

full range of cabinets: the input to the CAT5 cable, 30 W at the PD, is how enthusiastic PD OEMs will be about

Low Cost to Fully assuming 50 V at the PSE) using 802.11at implementing a scheme that requires them to

Featured to two-event classification. Designs requiring up write additional application software to com-

Customizable.

to 60 W can use a four-pair architecture using municate status information to the PSE—for

two devices. The PD64001 was sampling in example, “My user will/will not require video-

February, and it will be in production by the screen operation for this call, so give me my

end of the quarter. full power allotment now.” The second is

The Akros AS1135 is a PD controller imple- how enthusiastic IT managers will be about

menting the two-event physical-layer classifi- supporting a phone system whose power

cation functionality of the 802.3at standard. capabilities were sized based on statistical

Two-event classification allows the PD to analyses of usage.

recognize whether it is connected to Type Answering the first question, Akros

1 (802.3af/13W) or Type 2 (802.3at/30W) CEO Simon Prutton says that the company is

power sourcing equipment. It also informs dealing with video-over-IP OEMs that

the PSE that it’s safe to increase power deliv- are now developing products that will use

ered to the PD from 13 to 30 W. the new chips. With respect to the second,

Furthermore, the AS1135 provides “AT he says that Ethernet switch makers are going

Detect” functionality on a logic output pin. forward with product development, although

This enables the system microcontroller they seem to be hedging their bets by

to self-configure the networked appliance building in a robust safety factor when they

based on the power delivery capability of the size their power supplies.

network. It’s possible to set the switching DON TUITE

frequency of the integrated dc-dc controller AKROS SILICON • www.akrossilicon.com

anywhere between 100 and 500 kHz. It is MICROSEMI • www.microsemi.com

currently sampling as well. ED ONLINE 18558

SERDES IP Releases Tackle Top Speeds

High-speed design and serial buses used for chip-to-chip communications seem to

go hand in hand nowadays. Whether you’re talking signal integrity, printed-circuit

board (PCB) routability, or a slew of other factors, it just makes sense. Therefore, the

ready availability of reliable serializaer/deserializer (SERDES) intellectual property

(IP) is imperative.

Avago SERDES Offerings From eSilicon

Data rate 90 nm1 65 nm2

Protocol standards

(Gbits/s) (G, G-OD) (G+, G+OD)

Gigabit Ethernet 1.25 * *

PCI Express Gen 1 and 2 2.5 and 5.0 * *

10GBase-CX4 3.125 (x4 lanes) * *

XAUI/10GBase-KX4 3.125 (x4 lanes) * *

6.25 (LR and SR;

CEI-6G * *

MR)

XFI (10-Gbit Ethernet) 10.3125 *

Fibre Channel 1.0626, 2.125,

* *

(8x, 4x, 2x, 1x) 4.25, 8.5

Fibre Channel

TEL: 440-946-3200 10.51875 *

(10GFC Serial)

FAX: 440-951-4015

5.0, 6.25, 7.5,

saleseast@budind.com Chip-to-Chip/Backplane *

10.3125

www.budind.com/3

1. Frequencies higher than 6.25G require G-OD process 2. Frequencies higher than 7.5G require G+OD process

READER SERVICE 86 04.10.08 ELECTRONIC DESIGN

p25,26,28,30,32,33.indd 28 3/27/08 1:56:11 PM

techview

TX RX

Data Lane 0 TX SERDES data 0 Data Lane 0 RX SERDES data 0 SLE’s Interlaken

Format MUX Format MUX

Control Lane 1 TX SERDES data 1 Control Lane 1 RX SERDES data 1 IP core scales

Statistics Lane 2 TX SERDES data 2 Statistics Lane 2 RX SERDES data 2 from one to 24

… … … …

lanes, with each

Lane N TX SERDES data N Lane N RX SERDES data N lane capable

Debug Debug Debug Debug of raw data

Flow-control clk Flow-control clk

Flow control Flow-control Flow-control sync Flow control Flow-control rates between

Flow-control sync

format Flow-control data format Flow-control data 3.125 and 6.375

Config Gbits/s.

Interrupt Config

Tundra Semiconductor’s Silicon Logic Engineering (SLE) data rate equals just over 150 Gbits/s, which is the fastest rate

division addresses this need with an Interlaken IP core capable possible according to SLE.

of 150 Gbits/s (see the figure). Originally developed by Cortina Other features include support for up to 64k channels, a con-

Systems, the Interlaken protocol is a royalty-free specification tinuous meta frame for programming frequency allowing for

that combines the SPI-4.2 and XAUI architectures, which have lane alignment, and 64B/67B data encoding and scrambling.

seen high adoption rates in networking systems. SLE’s Interlaken IP core should pop into just about any ASIC,

SLE’s core is fully scalable, making it a good fit for future net- and it works with off-the-shelf SERDESs from most vendors.

work equipment designs, such as switches, routers, and storage It’s available through SLE’s sales channel.

devices. Each one of its 24 lanes is capable of 3.125 to 6.375 If network storage is your game, then you realize that data

Gbits/s. When all 24 lanes are chugging at full speed, the raw bandwidth and processing expectations have skyrocketed over

the past few years, with power con-

sumption and form factor expected to

remain constant. Again, the trend is to

include a high-speed SERDES to help

meet these requirements.

Recently, eSilicon partnered with

Avago to license its embedded SERDES

cores targeted at the network storage,

communications, and high-perfor-

mance computing markets. The multi-

tude of SERDES offerings includes 90-

and 65-nm CMOS processes available

from TSMC.

This sixth-generation suite of offer-

ings has been road tested in many

OV-7604-C7

Low-Power products. Avago offers its cores at rates

Clock Oscillator

from 1.0625 to 10.51875 Gbits/s, and

the company claims they provide strong

signal integrity and jitter performance.

Other features include an adaptive feed-

back equalizer in the receiver, program-

Never before could you get high performance in such

a small package. A precision timing crystal and a CMOS

mable transmitter pre-emphasis, and a

oscillator in a ceramic SMD, just 3.2 x 1.5 x1.0mm. bit error rate of less than 10-17. A broad

• 5.5V to 1.2V operation for reliable Call: 847-818-XTAL (9825) selection of Avago SERDES cores over

operation – even on low battery email: sales @microcrystal.com a range of data rates and protocol stan-

• Max. current: 0.5μA @ 3.0V www.microcrystal.com dards is available from eSilicon (see the

• Short start-up time of 0.5sec max. table). DANIEL HARRIS

• RoHS Compliant; 100% lead-free SILICON LOGIC ENGINEERING

• Ideal for cell phones, smart phones, siliconlogic.com/asic_fpga_interlaken_

GPS, PDAs, and portable instruments core.asp

ESILICON

esilicon.com/offerings/avago.php

ED ONLINE 18559

READER SERVICE 116

04.10.08 ELECTRONIC DESIGN

30

p25,26,28,30,32,33.indd 30 3/27/08 1:56:20 PM

Вам также может понравиться

- Wiring Devices General - Catalogue - 2014-2016Документ41 страницаWiring Devices General - Catalogue - 2014-2016CH Asia100% (1)

- Boost Athletic Performance and Build Safer Drones with Printed ElectronicsДокумент2 страницыBoost Athletic Performance and Build Safer Drones with Printed ElectronicsZypno ZypnoОценок пока нет

- BSD Curriculum Pathway - ALL COURSESДокумент6 страницBSD Curriculum Pathway - ALL COURSESkeemoe hannОценок пока нет

- ProgrammaNABA2023 2definitivoДокумент14 страницProgrammaNABA2023 2definitivoHyphae ProjectОценок пока нет

- Leica iCON Build BRO 793504 1120 en LRДокумент4 страницыLeica iCON Build BRO 793504 1120 en LRyamilОценок пока нет

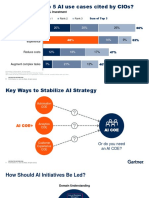

- Gartner - AI Use Cases, Implementation and AdoptionДокумент3 страницыGartner - AI Use Cases, Implementation and AdoptionMuriel PresnoОценок пока нет

- The Colour of Sound: Special ReportДокумент68 страницThe Colour of Sound: Special ReportRed PlagueОценок пока нет

- PCB Production Solutions: For IC, HDI, BGA, MSAP and FPC ProcessesДокумент9 страницPCB Production Solutions: For IC, HDI, BGA, MSAP and FPC ProcessesEkokrentОценок пока нет

- Elektrotec 2019 BrochureДокумент4 страницыElektrotec 2019 BrochureRuchirОценок пока нет

- BEA 2011 TechSurvequi en PDFДокумент2 страницыBEA 2011 TechSurvequi en PDFjacques_henry666Оценок пока нет

- Milestone's Perspective on Responsible Use of TechnologyДокумент22 страницыMilestone's Perspective on Responsible Use of TechnologyjojoОценок пока нет

- Grameen in Healthcare - A Dose of IT - 22 Nov 2010 - Asian Age - Page 11 - Kapil Khandelwal - EquNev CapitalДокумент1 страницаGrameen in Healthcare - A Dose of IT - 22 Nov 2010 - Asian Age - Page 11 - Kapil Khandelwal - EquNev CapitalKapil KhandelwalОценок пока нет

- CertificationsДокумент2 страницыCertificationsLy CẩmОценок пока нет

- Engineering Is Development by FIDICДокумент161 страницаEngineering Is Development by FIDICspi.architectsОценок пока нет

- Ece - iii-II Reg, May 2023 - BRVДокумент12 страницEce - iii-II Reg, May 2023 - BRVAkhilesh InternОценок пока нет

- Focus On Electronics: Game-Like Interfaces For Toyota Concept CarДокумент6 страницFocus On Electronics: Game-Like Interfaces For Toyota Concept Carjuki_7Оценок пока нет

- Blockchain Based Framework For Software Development Using DevOpsДокумент6 страницBlockchain Based Framework For Software Development Using DevOpsLuis Gustavo NetoОценок пока нет

- 399) NVQ Level 5 Correct AD-1Документ1 страница399) NVQ Level 5 Correct AD-1முஹம்மது றினோஸ்Оценок пока нет

- Screenshot 2023-02-27 at 11.44.52Документ1 страницаScreenshot 2023-02-27 at 11.44.52jsskkakaОценок пока нет

- Porsche Engineering MagazineДокумент40 страницPorsche Engineering MagazineDiego MenezesОценок пока нет

- Mansingh 2021Документ3 страницыMansingh 2021Chirag SaraswatОценок пока нет

- Welcome To Your Digital Edition Of: Tech Briefs and Photonics & Imaging TechnologyДокумент114 страницWelcome To Your Digital Edition Of: Tech Briefs and Photonics & Imaging TechnologyPetros TsenesОценок пока нет

- Guide The Modernization of Digital Technology FoundationssДокумент13 страницGuide The Modernization of Digital Technology Foundationssyuri.rodriguesОценок пока нет

- Sciencedirect: © 2016, Ifac (International Federation of Automatic Control) Hosting by Elsevier Ltd. All Rights ReservedДокумент4 страницыSciencedirect: © 2016, Ifac (International Federation of Automatic Control) Hosting by Elsevier Ltd. All Rights ReservedCarolina JaimesОценок пока нет

- Edelweiss Technology Fund - NFOДокумент4 страницыEdelweiss Technology Fund - NFOcholavarmanОценок пока нет

- Computational Design PortfolioДокумент11 страницComputational Design PortfolioMUditaLauОценок пока нет

- Sahil Kundal: UI/UX Designer and Software EngineerДокумент3 страницыSahil Kundal: UI/UX Designer and Software EngineerSahil KundalОценок пока нет

- Sahil Kundal UI/UX PortfolioДокумент3 страницыSahil Kundal UI/UX PortfolioSahil KundalОценок пока нет

- Mass Personalization With Industry 40 by SMEs A CoДокумент7 страницMass Personalization With Industry 40 by SMEs A CoAulia AzzahraОценок пока нет

- Why UX Is Not Only The Responsibility of The UX'er: by Janne Jul JensenДокумент73 страницыWhy UX Is Not Only The Responsibility of The UX'er: by Janne Jul JensenBeaurel FohomОценок пока нет

- Panasonic KV s4085cw Document Scanner Handy Manual 64Документ64 страницыPanasonic KV s4085cw Document Scanner Handy Manual 64driverhcareОценок пока нет

- Master of Technology in IT LeadershipДокумент7 страницMaster of Technology in IT LeadershipweiweiahОценок пока нет

- English Presentation of CoHistory2Документ3 страницыEnglish Presentation of CoHistory2ribEnglishОценок пока нет

- 4 2 - RAMI Martin Hankel PDFДокумент21 страница4 2 - RAMI Martin Hankel PDFKrishnan Subramanian100% (1)

- DE FUNCTIONAL CHART (Revised)Документ1 страницаDE FUNCTIONAL CHART (Revised)Jebong A. MarquezОценок пока нет

- Rituraj Test - Impact of Industry 4.0 On Indian Manufacturing SectorДокумент1 страницаRituraj Test - Impact of Industry 4.0 On Indian Manufacturing SectorRituraj SrivastavaОценок пока нет

- MITSUBAДокумент7 страницMITSUBAROBINSON FERNEYОценок пока нет

- Hypermedia IphoneДокумент1 страницаHypermedia Iphoneapi-81040815Оценок пока нет

- BPMN MBSE Workflow for Automated Production SystemsДокумент2 страницыBPMN MBSE Workflow for Automated Production SystemsAhmedОценок пока нет

- Enterprise Architecture For High Flexible and Agile Company inДокумент6 страницEnterprise Architecture For High Flexible and Agile Company inAthena KarakasidouОценок пока нет

- 1.1 Digital Acceleration ProgramДокумент12 страниц1.1 Digital Acceleration ProgramRizky PriyandaniОценок пока нет

- Silicon Valley PortfolioДокумент2 страницыSilicon Valley PortfolioAzif K MohammedОценок пока нет

- AESS 2022 - 05 - 22 - Alkitronic - Company Profile - Long - ENДокумент55 страницAESS 2022 - 05 - 22 - Alkitronic - Company Profile - Long - ENابوالحسن السلطانيОценок пока нет

- IoT Solutions Guide March14 DigitalДокумент39 страницIoT Solutions Guide March14 DigitalAnonymous VmQZwM5AОценок пока нет

- PO-CO Working MethodsДокумент6 страницPO-CO Working MethodsKundan Kumar RaoОценок пока нет

- IT&D Southwest: Technical Troubleshooting GuideДокумент6 страницIT&D Southwest: Technical Troubleshooting GuideeMedia ProducerОценок пока нет

- Annual Report 2018 2019Документ253 страницыAnnual Report 2018 2019Ankaj AroraОценок пока нет

- SbocДокумент6 страницSbocvictor_h_canteroОценок пока нет

- OEC Technology 1 SBДокумент137 страницOEC Technology 1 SBsaad mouhieddineОценок пока нет

- Digital Engineering - 2017-01Документ44 страницыDigital Engineering - 2017-01Бушинкин ВладиславОценок пока нет

- Iete Chencon 2022Документ1 страницаIete Chencon 2022Aafreen SanaОценок пока нет

- Let's Connect.: Weidmüller - Your Partner in Industrial ConnectivityДокумент2 страницыLet's Connect.: Weidmüller - Your Partner in Industrial ConnectivityEhsan RohaniОценок пока нет

- Naval State U Computer Engr Course SyllabusДокумент5 страницNaval State U Computer Engr Course SyllabusArnold de VegaОценок пока нет

- WWW Neit Edu Blog Index PHP 2015 09 Autocad Placing Your Dimensions and Text On The Right Angles For Isometric DrawingsДокумент4 страницыWWW Neit Edu Blog Index PHP 2015 09 Autocad Placing Your Dimensions and Text On The Right Angles For Isometric DrawingsJun AntonioОценок пока нет

- ICME 2019 Deadline ExtendedДокумент2 страницыICME 2019 Deadline Extendedanup880Оценок пока нет

- Additive Manufacturing For Orthopedic Applications Ca - 2023 - Procedia ComputeДокумент9 страницAdditive Manufacturing For Orthopedic Applications Ca - 2023 - Procedia Computevncheck.comОценок пока нет

- A&E VN: Leading Automation Solutions ProviderДокумент22 страницыA&E VN: Leading Automation Solutions Providerz3nnh0cОценок пока нет

- OMOTEC School & STEM LAB PresentationДокумент17 страницOMOTEC School & STEM LAB PresentationOn My Own TehnologyОценок пока нет

- Offshore Piping Design: Technical Design Procedures & Mechanical Piping MethodsОт EverandOffshore Piping Design: Technical Design Procedures & Mechanical Piping MethodsОценок пока нет

- A Bidirectional Automatic Room Light Controller Using Visitor CounterДокумент12 страницA Bidirectional Automatic Room Light Controller Using Visitor CounterNilabha DasОценок пока нет

- Micro Project Chapter1 5Документ9 страницMicro Project Chapter1 5api-276860885Оценок пока нет

- Step To Unlock b970Документ11 страницStep To Unlock b970sincotanОценок пока нет

- AVTech Manual English CPD576W AVC776 V1.0Документ26 страницAVTech Manual English CPD576W AVC776 V1.0han2solo8Оценок пока нет

- ITE 6220 LessonsДокумент6 страницITE 6220 LessonsRochie RoasaОценок пока нет

- OpenBoot 4.x Command Reference ManualДокумент204 страницыOpenBoot 4.x Command Reference Manualsabre620Оценок пока нет

- Asm 330 LHHДокумент84 страницыAsm 330 LHHp kОценок пока нет

- Ldnio Pricelist 2023Документ12 страницLdnio Pricelist 2023Mostafa MoatasimОценок пока нет

- Akai Z4/Z8 and MPC 400 Sysex SpecificationsДокумент58 страницAkai Z4/Z8 and MPC 400 Sysex SpecificationsSaverio PaiellaОценок пока нет

- KNX 100G - Setup Guide: E G H C D FДокумент4 страницыKNX 100G - Setup Guide: E G H C D FSkrapОценок пока нет

- Introduction To Microprocessors: Gursharan Singh TatlaДокумент24 страницыIntroduction To Microprocessors: Gursharan Singh TatlaSastry VaranasiОценок пока нет

- Programming Playstation 2Документ13 страницProgramming Playstation 24gen_7Оценок пока нет

- CPU Architecture: Control Unit (CU)Документ10 страницCPU Architecture: Control Unit (CU)i study100% (1)

- Z-3190 ProgrammingGuideДокумент71 страницаZ-3190 ProgrammingGuideDaniel Glen-WilliamsonОценок пока нет

- Basic: Fieldmate R1.02 For The SalespersonДокумент22 страницыBasic: Fieldmate R1.02 For The SalespersonNumanОценок пока нет

- Nexys 2 UcfДокумент7 страницNexys 2 UcfGabi FloreaОценок пока нет

- MacBook Pro (13-Inch, Mid 2009) - Technical SpecificationsДокумент4 страницыMacBook Pro (13-Inch, Mid 2009) - Technical SpecificationsIndianOnRunОценок пока нет

- Asset Inventory Management TemplateДокумент85 страницAsset Inventory Management TemplateM Monjur MobinОценок пока нет

- CHTДокумент45 страницCHTRajesh ChoudharyОценок пока нет

- Screenshot 2022-12-16 at 23.44.01Документ1 страницаScreenshot 2022-12-16 at 23.44.01Seagull BelugaОценок пока нет

- DR Diagram NETVIZДокумент78 страницDR Diagram NETVIZoriel100% (1)

- Siliconchip Softwave ListДокумент246 страницSiliconchip Softwave ListLong Nguyen KimОценок пока нет

- PCF8574 Pcf8574aДокумент33 страницыPCF8574 Pcf8574aEsdras José Francisco Palacios MéridaОценок пока нет

- PIC-EK User ManualДокумент91 страницаPIC-EK User Manualdjdkd,fОценок пока нет

- Modicon Modernisation Guide - Quantum To X80 Evolution Cable Management Installation Kit, Jul'19 - MFR91487Документ4 страницыModicon Modernisation Guide - Quantum To X80 Evolution Cable Management Installation Kit, Jul'19 - MFR91487Asim ButtОценок пока нет

- SWF Multi Head Embroidery Machine Control PartsДокумент78 страницSWF Multi Head Embroidery Machine Control PartsLuis Caba Ramirez100% (1)

- Viewsat 9000 Setup GuideДокумент4 страницыViewsat 9000 Setup Guidecici709394Оценок пока нет

- UM1912 User ManualДокумент16 страницUM1912 User ManualMax SlobodianОценок пока нет

- BIOS Setup: User's GuideДокумент56 страницBIOS Setup: User's Guideאיתי אדלרОценок пока нет

- Introduction To Computer ArchitectureДокумент23 страницыIntroduction To Computer ArchitectureLwanga Charles Chas100% (1)