Академический Документы

Профессиональный Документы

Культура Документы

Labo 2

Загружено:

Miguel MurilloОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

Labo 2

Загружено:

Miguel MurilloАвторское право:

Доступные форматы

SISTEMAS DIGITALES II

LABORATORIO N º 2

Objetivo: Esta práctica tiene como objetivo el verificar el funcionamiento de los FLIP

FLOPS JK y D asíncronos y obtener experimentalmente sus tablas de verdad

respectivas.

FLIP FLOP JK ASÍNCRONO

Descripción: El FLIP FLOP JK se caracteriza por eliminar la condición de

indeterminación de los FLIP FLOPS RS armados previamente con compuertas NAND Y

NOR.

El circuito y su tabla de verdad es la que se muestra a continuación:

J K Q n+1

L L Qn

L H H

H L L

H H Qn

Procedimiento:

1. Armar el FLIP FLOP JK con compuertas NOR y AND utilizando los circuitos

integrados 7402 y 7408.

2. El FLIP FLOP denominado RS tiene 2 entradas J y K y 2 salidas

complementarias Q y Q.

3. Alimentar el circuito integrado en sus terminales Vcc y GND con tensión Vcc =

5 Voltios.

4. Conectar las salidas Q y Q a LEDs de manera que podamos visualizar los

cambios de estado.

Vcc = 5 V

1 K Ohm 1 K Ohm

7402

7408

7402

7408

5. Llenar la tabla de verdad del FLIP FLOP respectivo.

ENTRADAS SALIDAS

J K Qn Q n+1

Qn+1

L L L

L L H

L H L

L H H

H L L

H L H

H H L

H H H

FLIP FLOP D ASÍNCRONO

Descripción: El FLIP FLOP D se caracteriza porque la salida Qn+1 adquiere el valor de

la entrada D. Como se ve en la figura el inversor impide que las entradas sean iguales.

Por tanto se comporta como un FLIP FLOP JK con las entradas complementadas.

El circuito y su tabla de verdad es la que se muestra a continuación:

Qn

D Qn

D Qn Q n+1

Qn+1

L L

L H

H L

H H

Materiales:

- 2 resistencias de 1 K Ohms

- 2 resistencias de 330 Ohms.

- 1 CI 7408 AND cuádruple.

- 1 CI 7402 NOR cuádruple.

- Fuente de poder.

- Protoboard

- Multímetro digital.

- 2 LEDs.

Вам также может понравиться

- Proyecto Pozo A Tierra CorregidoДокумент28 страницProyecto Pozo A Tierra CorregidoDlc MiguelОценок пока нет

- Flexión MecánicaДокумент25 страницFlexión MecánicaCesar Andres Peralta Vidal100% (1)

- Equilibrio Gas LiquidoДокумент5 страницEquilibrio Gas LiquidoRenzo Acevedo Cano100% (1)

- Clasificacion de Las MatricesДокумент3 страницыClasificacion de Las MatricesHebert AlvareezОценок пока нет

- Ejercicios Fluidos CanalesДокумент5 страницEjercicios Fluidos CanalesBrenda Yadira SeñasОценок пока нет

- Patron de Radiacion de Dos AntenasДокумент7 страницPatron de Radiacion de Dos AntenasMiguel MurilloОценок пока нет

- Capítulo 5 Chile DepredadorДокумент6 страницCapítulo 5 Chile DepredadorMiguel MurilloОценок пока нет

- 3Документ1 страница3Miguel MurilloОценок пока нет

- Convocatoria YMCAДокумент2 страницыConvocatoria YMCAMiguel MurilloОценок пока нет

- MatmilДокумент10 страницMatmilMiguel MurilloОценок пока нет

- Conflicto Entre Dos PaisesДокумент3 страницыConflicto Entre Dos PaisesMiguel MurilloОценок пока нет

- Trabajo MetodologiaДокумент4 страницыTrabajo MetodologiaMiguel MurilloОценок пока нет

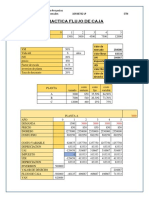

- Practica Flujo de CajaДокумент3 страницыPractica Flujo de CajaMiguel MurilloОценок пока нет

- PreguntasДокумент5 страницPreguntasMiguel Murillo100% (1)

- Banda Base-Fibra OpticaДокумент5 страницBanda Base-Fibra OpticaMiguel MurilloОценок пока нет

- Ejercicio Maderera Oriental Flujo de CajaДокумент2 страницыEjercicio Maderera Oriental Flujo de CajaMiguel MurilloОценок пока нет

- Equipo Transmisor FM-BroadcastДокумент2 страницыEquipo Transmisor FM-BroadcastMiguel MurilloОценок пока нет

- Proyecto PepДокумент25 страницProyecto PepMiguel MurilloОценок пока нет

- Practica Flujo de CajaДокумент3 страницыPractica Flujo de CajaMiguel MurilloОценок пока нет

- Andrés de Santa Cruz Nació El 5 de Diciembre de 1792 en La Ciudad de La PazДокумент9 страницAndrés de Santa Cruz Nació El 5 de Diciembre de 1792 en La Ciudad de La PazMiguel MurilloОценок пока нет

- Ejercicio Maderera Oriental Flujo de CajaДокумент2 страницыEjercicio Maderera Oriental Flujo de CajaMiguel MurilloОценок пока нет

- Trabajo MetodologiaДокумент4 страницыTrabajo MetodologiaMiguel MurilloОценок пока нет

- Trabajo MetodologiaДокумент4 страницыTrabajo MetodologiaMiguel MurilloОценок пока нет

- Trabajo MetodologiaДокумент4 страницыTrabajo MetodologiaMiguel MurilloОценок пока нет

- En CuestaДокумент1 страницаEn CuestaMiguel MurilloОценок пока нет

- Aspectos GeneralesДокумент2 страницыAspectos GeneralesMiguel MurilloОценок пока нет

- Ejercicio Maderera Oriental Flujo de CajaДокумент2 страницыEjercicio Maderera Oriental Flujo de CajaMiguel MurilloОценок пока нет

- Simetrías de Ondas PeriódicasДокумент3 страницыSimetrías de Ondas PeriódicasMiguel MurilloОценок пока нет

- Ejm 1Документ7 страницEjm 1Miguel MurilloОценок пока нет

- Andrés de Santa Cruz Nació El 5 de Diciembre de 1792 en La Ciudad de La PazДокумент9 страницAndrés de Santa Cruz Nació El 5 de Diciembre de 1792 en La Ciudad de La PazMiguel MurilloОценок пока нет

- WeimarДокумент6 страницWeimarMiguel MurilloОценок пока нет

- Aspectos GeneralesДокумент2 страницыAspectos GeneralesMiguel MurilloОценок пока нет

- Modulación de Fase - PMДокумент2 страницыModulación de Fase - PMMiguel MurilloОценок пока нет

- Equipo Transmisor FM Ultra 800Документ4 страницыEquipo Transmisor FM Ultra 800Miguel MurilloОценок пока нет

- Radiodifusion FM AMДокумент6 страницRadiodifusion FM AMMiguel MurilloОценок пока нет

- Ctfis - 1s-IiipДокумент9 страницCtfis - 1s-IiipmalcommmОценок пока нет

- Granulometría Mediante Rayo LaserДокумент6 страницGranulometría Mediante Rayo LaserGabriel Ricardo PachecoОценок пока нет

- Fundamentos TecnicosДокумент23 страницыFundamentos TecnicosMichael GonzalezОценок пока нет

- Cfe P33Документ3 страницыCfe P33Alberto GonzalezОценок пока нет

- Autoevaluacion CinematicaДокумент1 страницаAutoevaluacion CinematicaYisus 264Оценок пока нет

- S27 CytДокумент2 страницыS27 CytaОценок пока нет

- Clase 7 SolucionarioДокумент17 страницClase 7 Solucionariojavi jofre inostrozaОценок пока нет

- AMATISTAДокумент9 страницAMATISTAJose Carlos Amado RamirezОценок пока нет

- Distribución Muestral de ProporcionesДокумент4 страницыDistribución Muestral de ProporcionesJimena Perales AceroОценок пока нет

- Extracción de Un Pigmento Vegetal Por Cromatografía en PapelДокумент5 страницExtracción de Un Pigmento Vegetal Por Cromatografía en PapelNohely PinedaОценок пока нет

- Fisica XDДокумент3 страницыFisica XDHansel DueñasОценок пока нет

- Práctica 1Документ14 страницPráctica 1danielОценок пока нет

- Mediciones y ErroresДокумент8 страницMediciones y ErroresOscar Hbk Vargas TercerosОценок пока нет

- Respuestas Hidrodinámicas de La Instalación de Acuicultura LONGLINE Con Redes de Linterna en Olas (Cañari Quispe, D. - Henriquez Alfaro, E.)Документ22 страницыRespuestas Hidrodinámicas de La Instalación de Acuicultura LONGLINE Con Redes de Linterna en Olas (Cañari Quispe, D. - Henriquez Alfaro, E.)Diego CañariОценок пока нет

- FII Taller Final 2021Документ3 страницыFII Taller Final 2021JAROL ALVEIRO LOZANO VIVAS0% (2)

- Algebra MatricesДокумент16 страницAlgebra MatricesMónica MarcaОценок пока нет

- Estudio de La Interacción de La Radiación Visible Con La Piel Humana Por Medio de Imagenología Polarimétrica Empleando Fuentes de Iluminación LEDДокумент81 страницаEstudio de La Interacción de La Radiación Visible Con La Piel Humana Por Medio de Imagenología Polarimétrica Empleando Fuentes de Iluminación LEDAlan Miguel Rodríguez AcuñaОценок пока нет

- Reporte de Investigacion - Transformacion LinealДокумент7 страницReporte de Investigacion - Transformacion LinealDanna JaegerОценок пока нет

- Método de Euler. Ecuaciones Diferenciales - Solución NuméricaДокумент4 страницыMétodo de Euler. Ecuaciones Diferenciales - Solución NuméricaCris AcevedoОценок пока нет

- Solucion Actividad 1Документ6 страницSolucion Actividad 1Isai Caleb Huacasi PandiaОценок пока нет

- Aca Real Fundamentos de MatematicasДокумент9 страницAca Real Fundamentos de MatematicasJOHN FREDDY BEDOYA RAMIREZОценок пока нет

- Práctica RefractometríaДокумент9 страницPráctica RefractometríaAnder RiveraОценок пока нет

- Informe Ensayos Mecanicos Curso Anclajes FeeДокумент63 страницыInforme Ensayos Mecanicos Curso Anclajes Feekmariyus133311Оценок пока нет

- Ejercicios Resueltos 1Документ5 страницEjercicios Resueltos 1Leuri RincónОценок пока нет

- Informe Ensayo de TensionДокумент10 страницInforme Ensayo de TensionChirstian BautistaОценок пока нет