Академический Документы

Профессиональный Документы

Культура Документы

New DSP Operation Using Vedic Mathematics

Загружено:

demo testОригинальное название

Авторское право

Доступные форматы

Поделиться этим документом

Поделиться или встроить документ

Этот документ был вам полезен?

Это неприемлемый материал?

Пожаловаться на этот документАвторское право:

Доступные форматы

New DSP Operation Using Vedic Mathematics

Загружено:

demo testАвторское право:

Доступные форматы

DSP OPERATION USING VEDIC MATHEMATICS

A Mini Project report Submitted in partial fulfillment of the Academic requirements for

the award of the degree of

Bachelor of Technology

In

Electronics & Communication Engineering

Submitted by

SHUBHAM PATRA (15H51A04G3)

CH. MADHU SUDHAN (15H51A04D1)

D. SHAHSI KUMAR (15H51A04D3)

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

CMR COLLEGE OF ENGINEERING & TECHNOLOGY

(Autonomous)

(NAAC Accredited with ‘A’ Grade & NBA Accredited)

(Approved by AICTE, Permanently Affiliated to JNTU Hyderabad)

KANDLAKOYA, MEDCHAL ROAD, HYDERABAD-501401

2016-17

DSP OPERATION USING VEDIC MATHEMATICS

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

CMR COLLEGE OF ENGINEERING & TECHNOLOGY

(Autonomous)

(NAAC Accredited with ‘A’ Grade & NBA Accredited)

(Approved by AICTE, Permanently Affiliated to JNTU Hyderabad)

KANDLAKOYA, MEDCHAL ROAD, HYDERABAD-501401

CERTIFICATE

This is to certify that the mini project report entitled “DSP OPERATION USING VEDIC

MATHEMATICS” is a bonafide work done by Shubham Patra (15H51A04G3), Ch. Madhu

Sudhan (15H51A04D1), D. Shashi Kumar (15H51A04D3) of III B.Tech ECE, in partial

fulfillment of the requirements for the award of the degree of Bachelor of Technology in

Electronics & Communication Engineering, submitted to the Department of Electronics and

Communication Engineering, CMR College of Engineering & Technology, Hyderabad during the

Academic Year 2018-19.

(Ms. T.Swapna Rani) (Dr. B. Lokeshwara Rao)

Assistant Professor Professor & HOD

Project Coordinator Department of ECE

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

DECLARATION

We students of IV B.Tech Department of Electronics and Communication Engineering, CMR

COLLEGE OF ENGINEERING AND TECHNOLOGY, Kandlakoya, Hyderabad, hereby

Declare, that under the supervision of our guide Ms. T. SWAPNA RANI Asst. Prof. we have

Independently carried out the project titled “DSP OPERATION USING VEDIC

MATHEMATICS” and submitted the report in partial fulfillment of the requirement for the award

of Bachelor of Technology in Electronics and Communication Engineering by the Jawaharlal

Nehru Technological University, Hyderabad (JNTUH) during year 2018-2019.

SHUBHAM PATRA (15H51A04G3)

CH. MADHU SUDHAN (15H51A04D1)

D. SHASHI KUMAR (15H51A04D3)

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

ACKNOWLEDGEMENT

We are obliged and grateful to thank Dr. B.Lokeshwara Rao, Professor and HOD, Department of

ECE, CMRCET, for his cooperation in all respects during the course.

We would like to thank Dr. M. Sudhakar, Dean (Planning and Development) ECE, CMRCET, for

his encouragement throughout our course.

We would like to thank the Principal of CMRCET, Dr.V.A.Narayana, for his support in the course

of this project work.

Finally we thank all our faculty members and Lab Assistants for their valid support.

We own all our success to our beloved parents, whose vision, love and inspiration has made us

reach out for these glories.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

ABSTRACT

Digital Signal Processing (DSP) operations are very important part of engineering as well as

medical discipline. Designing of DSP operations have many approaches. For the designing of DSP

operations, multiplication is play important role to perform signal processing operations such as

Convolution and Correlation. The new approach of this implementation is mentally and easy to

calculate of DSP operations for small length of sequences. In this paper a fast method for DSP

operations based on ancient Vedic mathematics is contemplated. The implementation of high

speed DSP operations of two finite length sequences using Vedic Urdhava-Triyagbhayam

Multiplication Sutra (approach/method) is done. Urdhava-Triyagbhayam Sutra is very efficient

multiplication formula applicable for all types of multiplication. This algorithm is implemented in

MATLAB and all the operation is performed in single Graphical User Interface (GUI) window.

Vedic mathematics based DSP operations reduce the processing time as compare to inbuilt

function of MATLAB. It reduces the 40-60% time from inbuilt function and this algorithm

operates in concept of Vedic multiplier

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

TABLE OF CONTENTS

CHAPTERS DESCRIPTION

I Introduction

1.1 Introduction

1.2 Verilog HDL

1.3 VHDL

1.4 VLSI

II

LITERATURE REVIEW

2.1 Introduction

2.2 Definition

2.3 Functions

2.4 History

2.5 Types

III Fundamental VLSI design modules

3.1

3.2

3.3

IV Block diagram, Flowchart & Working

4.1 Working

4.2 Block Diagram

4.3 Flowchart

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

V RESULT

5.1 simulation

5.2 Synthesis

VI Conclusion

1 references

VII Appendix

7.1 Source code

7.2 Test bench

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

CHAPTER- I

INTRODUCTION

Objective:

To design DSP operations (linear convolution, circular convolution and correlation) with the help

of VEDIC URDHAVA – TRIYAGBHYAM which increases the efficiency of system and reduces

the processing time.

Outline of the Project:

For ease of understanding the project, this book is divided in to six chapters. Chapter-I

describes about introduction Xilinx ISE design suite and VHDL. Chapter-II discusses about the

basic blocks such as multiplexer and AND gate logic(do here). Chapter-III talks about talks about

Block Diagram, flowchart and working of the project. In the end we summarize our report with

result, conclusion and references followed by appendix.

1.1 Introduction

The development of microelectronics spans a time which is even lesser than the average life

expectancy of a human, and yet it has seen as many as four generations. Early 60’s saw the low

density fabrication processes classified under Small Scale Integration (SSI) in which transistor

count was limited to about 10. This rapidly gave way to Medium Scale Integration in the late

60’s when around 100 transistors could be placed on a single chip.

Transistor-Transistor logic (TTL) offering higher integration densities outlasted other IC

families like ECL and became the basis of the first integrated circuit revolution. It was the

production of this family that gave impetus to semiconductor giants like Texas Instruments,

Fairchild and National Semiconductors. Early seventies marked the growth of transistor count to

about 1000 per chip called the Large Scale Integration.

By mid-eighties, the transistor count on a single chip had already exceeded 1000 and hence came

the age of Very Large Scale Integration or VLSI. Though many improvements have been made

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

and the transistor count is still rising, further names of generations like ULSI are generally

avoided.

Thus this project focuses on developing and simulating a code that performs the function of candy

vending machine i.e. dispenses the desired candies as per the amount inserted by the consumer.

This project aims at identifying the main issues in designing a VLSI chip and helps us to learn the

techniques required to develop and simulate a Verilog code using dedicated Verilog compilers and

synthesizers that will help us in developing the required application.

To develop the project using Verilog HDL, we need to have a brief understanding about the tool

that we will be using to simulate and test the module.

To develop this module, the tool that we used software Xilinx ISE design suite but this software

has following advantages over rest .they are

1. It’s open source version and is available for free download.

2. It has a friendly user interface and can be easily used by beginners.

3. It follows all the ANSI and IEEE standards and is also industrial software.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Language support

1.2 Verilog

Verilog, standardized as IEEE 1364, is a hardware description language (HDL) used to model

electronic systems. It is most commonly used in the design and verification of digital circuits at

the register-transfer level of abstraction. It is also used in the verification of analog

circuits and mixed-signal circuits, as well as in the design of genetic circuits.

Hardware description languages such as Verilog differ from software programming

languages because they include ways of describing the propagation time and signal strengths

(sensitivity). There are two types of assignment operators; a blocking assignment (=), and a non-

blocking (<=) assignment. The non-blocking assignment allows designers to describe a state-

machine update without needing to declare and use temporary storage variables. Since these

concepts are part of Verilog language semantics, designers could quickly write descriptions of

large circuits in a relatively compact and concise form.

Verilog concept of 'wire' consists of both signal values (4-state: "1, 0, floating, undefined") and

signal strengths (strong, weak, etc.). This system allows abstract modelling of shared signal lines,

where multiple sources drive a common net. When a wire has multiple drivers, the wire's

(readable) value is resolved by a function of the source drivers and their strengths.

Subsets of statements in the Verilog language are synthesizable. Verilog modules that conform to

a synthesizable coding style, known as RTL (register-transfer level), can be physically realized

by synthesis software. Synthesis software algorithmically transforms the (abstract) Verilog

source into a net list, a logically equivalent description consisting only of elementary logic

primitives (AND, OR, NOT, flip-flops, etc.) that are available in a

specific FPGA or VLSI technology. Further manipulations to the net list ultimately lead to a

circuit fabrication blueprint (such as a photo mask set for an ASIC or a bit stream file for

an FPGA).

There are four levels of abstraction in Verilog:

1. Switch level: this is lowest level, implemented using switches or transistors. The designer

must know the switch level implementations.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

2. Gate level: this is implemented using logic gates. The designer here must know the exact gate

level diagram of the design.

3. Data flow level: this is implemented by specifying the data flow, I.e. registers used in the

design.

4. Behavioral level: this is highest level of abstraction. It is implemented with design algorithms.

Here the designer necessarily not needs to know the exact hardware implementation knowledge.

1.3 VHDL

VHDL (VHSIC Hardware Description Language) is a hardware description language used

in electronic design automation to describe digital and mixed-signal systems such as field-

programmable gate arrays and integrated. VHDL can also be used as a general purpose parallel

programming language.

VHDL is commonly used to write text models that describe a logic circuit. Such a model is

processed by a synthesis program, only if it is part of the logic design. A simulation program is

used to test the logic design using simulation models to represent the logic circuits that interface

to the design. This collection of simulation models is commonly called a test bench.

One can design hardware in a VHDL IDE (for FPGA implementation such as Xilinx ISE, Altera

Quartus, Synopsys Simplify or Mentor Graphics HDL Designer) to produce the RTL schematic

of the desired circuit. After that, the generated schematic can be verified using simulation

software which shows the waveforms of inputs and outputs of the circuit after generating the

appropriate test bench. To generate an appropriate test bench for a particular circuit or VHDL

code, the inputs have to be defined correctly.

A final point is that when a VHDL model is translated into the "gates and wires" that are mapped

onto a programmable logic device such as a CPLD or FPGA, then it is the actual hardware being

configured, rather than the VHDL code being "executed" as if on some form of a processor chip.

Advantage of opting Verilog over VLSI:

1. Like C programming language.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

2. Compared to VHDL, Verilog data types a very simple, easy to use and very much geared

towards modeling hardware structure as opposed to abstract hardware modeling.

3. Verilog may be preferred because of its simplicity.

4. Starting with zero knowledge of either language, Verilog is probably the easiest to grasp

and understand.

1.4 INTRODUCTION TO VLSI

1.4.1 Historical Perspective

The electronics industry has achieved a phenomenal growth over the last two decades,

mainly due to the rapid advances in integration technologies, large-scale systems design - in short,

due to the advent of VLSI. The number of applications of integrated circuits in high-performance

computing, telecommunications, and consumer electronics has been rising steadily, and at a very

fast pace. Typically, the required computational power (or, in other words, the intelligence) of

these applications is the driving force for the fast development of this field. Figure 1.1 gives an

overview of the prominent trends in information technologies over the next few decades. The

current leading-edge technologies (such as low bit-rate video and cellular communications)

already provide the end-users a certain amount of processing power and portability.-

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

This trend is expected to continue, with very important implications on VLSI and systems

design. One of the most important characteristics of information services is their increasing need

for very high processing power and bandwidth (in order to handle real-time video, for example).

The other important characteristic is that the information services tend to become more and more

personalized (as opposed to collective services such as broadcasting), which means that the devices

must be more intelligent to answer individual demands, and at the same time they must be portable

to allow more flexibility/mobility

As more and more complex functions are required in various data processing and

telecommunications devices, the need to integrate these functions in a small system/package is

also increasing. The level of integration as measured by the number of logic gates in a monolithic

chip has been steadily rising for almost three decades, mainly due to the rapid progress in

processing technology and interconnect technology. Table 1.1 shows the evolution of logic

complexity in integrated circuits over the last three decades, and marks the milestones of each era.

Here, the numbers for circuit complexity should be interpreted only as representative examples to

show the order-of-magnitude. A logic block can contain anywhere from 10 to 100 transistors,

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

depending on the function. State-of-the-art examples of ULSI chips, such as the DEC Alpha or the

INTEL Pentium contain 3 to 6 million transistors.

ERA DATE COMPLEXITY

(number of logic blocks per chip)

Single transistor 1959 less than 1

Unit logic (one gate) 1960 1

Multi-function 1962 2-4

Complex function 1964 5 - 20

Medium Scale Integration 1967 20 - 200 (MSI)

Large Scale Integration 1972 200 - 2000 (LSI)

Very Large Scale Integration 1978 2000 - 20000 (VLSI)

Ultra Large Scale Integration 1989 20000 - ? (ULSI)

Table:- Evolution of logic complexity in integrated circuits.

The most important message here is that the logic complexity per chip has been (and still

is) increasing exponentially. The monolithic integration of a large number of functions on a

single chip usually provides:

Less area/volume and therefore, compactness

Less power consumption

Less testing requirements at system level

Higher reliability, mainly due to improved on-chip interconnects

Higher speed, due to significantly reduced interconnection length

Significant cost savings

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Figure:- Evolution of integration density and minimum feature size, as seen in the early 1980s.

Therefore, the current trend of integration will also continue in the foreseeable future.

Advances in device manufacturing technology, and especially the steady reduction of minimum

feature size (minimum length of a transistor or an interconnect realizable on chip) support this

trend. Figure 1.2 shows the history and forecast of chip complexity - and minimum feature size -

over time, as seen in the early 1980s. At that time, a minimum feature size of 0.3 microns was

expected around the year 2000. The actual development of the technology, however, has far

exceeded these expectations. A minimum size of 0.25 microns was readily achievable by the year

1995. As a direct result of this, the integration density has also exceeded previous expectations -

the first 64 Mbit DRAM, and the INTEL Pentium microprocessor chip containing more than 3

million transistors were already available by 1994, pushing the envelope of integration density.

When comparing the integration density of integrated circuits, a clear distinction must be made

between the memory chips and logic chips. Figure 1.3 shows the level of integration over time for

memory and logic chips, starting in 1970. It can be observed that in terms of transistor count, logic

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

chips contain significantly fewer transistors in any given year mainly due to large consumption of

chip area for complex interconnects. Memory circuits are highly regular and thus more cells can

be integrated with much less area for interconnects.

Figure:- Level of integration over time, for memory chips and logic chips.

Generally speaking, logic chips such as microprocessor chips and digital signal processing

(DSP) chips contain not only large arrays of memory (SRAM) cells, but also many different

functional units. As a result, their design complexity is considered much higher than that of

memory chips, although advanced memory chips contain some sophisticated logic functions. The

design complexity of logic chips increases almost exponentially with the number of transistors to

be integrated. This is translated into the increase in the design cycle time, which is the time period

from the start of the chip development until the mask-tape delivery time. However, in order to

make the best use of the current technology, the chip development time has to be short enough to

allow the maturing of chip manufacturing and timely delivery to customers. As a result, the level

of actual logic integration tends to fall short of the integration level achievable with the current

processing technology. Sophisticated computer-aided design (CAD) tools and methodologies are

developed and applied in order to manage the rapidly increasing design complexity.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

1.4.2 VLSI Design Flow

The design process, at various levels, is usually evolutionary in nature. It starts with a given

set of requirements. Initial design is developed and tested against the requirements. When

requirements are not met, the design has to be improved. If such improvement is either not possible

or too costly, then the revision of requirements and its impact analysis must be considered. The Y-

chart (first introduced by D. Gajski) shown in Fig. 1.4 illustrates a design flow for most logic chips,

using design activities on three different axes (domains) which resemble the letter Y.

Figure:- Typical VLSI design flow in three domains (Y-chart representation).

The Y-chart consists of three major domains, namely:

behavioral domain,

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

structural domain,

Geometrical layout domain.

The design flow starts from the algorithm that describes the behaviour of the target chip. The

corresponding architecture of the processor is first defined. It is mapped onto the chip surface by

floor planning. The next design evolution in the behavioural domain defines finite state machines

(FSMs) which are structurally implemented with functional modules such as registers and

arithmetic logic units (ALUs).

These modules are then geometrically placed onto the chip surface using CAD tools for automatic

module placement followed by routing, with a goal of minimizing the interconnects area and signal

delays. The third evolution starts with a behavioural module description. Individual modules are

then implemented with leaf cells. At this stage the chip is described in terms of logic gates (leaf

cells), which can be placed and interconnected by using a cell placement & routing program. The

last evolution involves a detailed Boolean description of leaf cells followed by a transistor level

implementation of leaf cells and mask generation. In standard-cell based design, leaf cells are

already pre-designed and stored in a library for logic design use.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Figure:- A more simplified view of VLSI design flow.

Figure provides a more simplified view of the VLSI design flow, taking into account the

various representations, or abstractions of design - behavioral, logic, circuit and mask layout. Note

that the verification of design plays a very important role in every step during this process. The

failure to properly verify a design in its early phases typically causes significant and expensive re-

design at a later stage, which ultimately increases the time-to-market.

Although the design process has been described in linear fashion for simplicity, in reality

there are many iterations back and forth, especially between any two neighboring steps, and

occasionally even remotely separated pairs. Although top-down design flow provides an excellent

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

design process control, in reality, there is no truly unidirectional top-down design flow. Both top-

down and bottom-up approaches have to be combined. For instance, if a chip designer defines an

architecture without close estimation of the corresponding chip area, then it is very likely that the

resulting chip layout exceeds the area limit of the available technology. In such a case, in order to

fit the architecture into the allowable chip area, some functions may have to be removed and the

design process must be repeated. Such changes may require significant modification of the original

requirements. Thus, it is very important to feed forward low-level information to higher levels

(bottom up) as early as possible.

In the following, we will examine design methodologies and structured approaches which

have been developed over the years to deal with both complex hardware and software projects.

Regardless of the actual size of the project, the basic principles of structured design will improve

the prospects of success. Some of the classical techniques for reducing the complexity of IC design

are: Hierarchy, regularity, modularity and locality.

1.4.3 Design Hierarchy

The use of hierarchy, or � divide and conquer� technique involves dividing a module into sub-

modules and then repeating this operation on the sub-modules until the complexity of the smaller

parts becomes manageable. This approach is very similar to the software case where large

programs are split into smaller and smaller sections until simple subroutines, with well-defined

functions and interfaces, can be written. In Section 1.2, we have seen that the design of a VLSI

chip can be represented in three domains. Correspondingly, a hierarchy structure can be described

in each domain separately. However, it is important for the simplicity of design that the hierarchies

in different domains can be mapped into each other easily.

As an example of structural hierarchy, Fig. 1.6 shows the structural decomposition of a CMOS

four-bit adder into its components. The adder can be decomposed progressively into one- bit

adders, separate carry and sum circuits, and finally, into individual logic gates. At this lower level

of the hierarchy, the design of a simple circuit realizing a well-defined Boolean function is much

more easier to handle than at the higher levels of the hierarchy.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

In the physical domain, partitioning a complex system into its various functional blocks will

provide a valuable guidance for the actual realization of these blocks on chip. Obviously, the

approximate shape and size (area) of each sub-module should be estimated in order to provide a

useful floor plan. Figure 1.7 shows the hierarchical decomposition of a four-bit adder in physical

description (geometrical layout) domain, resulting in a simple floor plan. This physical view

describes the external geometry of the adder, the locations of input and output pins, and how pin

locations allow some signals (in this case the carry signals) to be transferred from one sub-block

to the other without external routing. At lower levels of the physical hierarchy, the internal mask

Figure:- Structural decomposition of a four-bit adder circuit, showing the hierarchy down to gate

level.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Figure-3.7: Regular design of a 2-1 MUX, a DFF and an adder, using inverters and tri-state

buffers.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

CHAPTER II

LITERATURE REVIEW

2.1 INTRODUCTION

This chapter will explain about the development of the vending machine. This chapter also

contains the information about the previous research on vending machine payment method. In the

end of this chapter, the payment method for the vending machine will be discussed.

2.2 DEFINITION

2.3 FUNCTIONS

Vending machine has two functions that are selling the product and selling the service to the

customers. Vending machine will sell the product that is installed into the body with different

prices. After paying a certain amount, a product if available at the machine, releases it. For the

vending machine that provides service as the main function, the service also may become available

after paying. Example for the service vending machine is Money ATM.

2.4 HISTORY

Vedic mathematics is an ancient fast calculation mathematics technique which is taken from

historical ancient book of wisdom. Vedic mathematics is an ancient Vedic mathematics which

provides the unique technique of mental calculation with the help of simple rules and principles.

Veda rediscovered by the holiness Jagad Guru Shree Bharti Krishna Tirtha Ji Maharaj (1884-1960)

in between 1911-1918. According to Swami-Ji all Vedic mathematics is based on 16Sutra

(Algorithm) and 16- up-sutra (Sub-algorithm) after broadly research in Atharva Veda . It computes

all the basic as well as complex mathematical operation easily and quickly also provides a power

full mantel technique. It is more consistent than modern mathematics and provides an expeditious

solution. The term Vedic mathematics is evolving from the word “Veda” which means warehouse

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

of all knowledge. It is based on sixteen sutras which transact different branches of mathematics

i.e. algebra, geometry, arithmetic. Former Shankrachrya Shree Bharti Krishna Tirtha of India was

developed in to the ancient Vedic text and established the new method of this system in his

pioneering work in Vedic mathematics (1965). Which was the starting point of the new work in

Vedic math’s era? A batter deal of research is also being transport how to develop more powerful

and easy application of the Vedic sutras geometry, calculus, trigonometric, computing application

(property). Modern mathematics is an integral part of the technical education most of the

engineering system design is based on the various mathematical approaches. The necessity for

expeditious processing speed used following Vedic mathematics algorithm.

1. Ekadhikena Purvena – By one more than the previous one.

2. Nikhilam Navatascaramap Dasatah – All from 9 and last from 10.

3. Urdhva-Tiryagbhyam – Vertically and crosswise.

4. Paravartya Yojayet – Transpose and adjust.

5. Shunyam Samyasamuccaye – When the sum is the same that sum is zero.

6. (Anurupye) Shunyamanyat – If one is in ratio, the other is zero.

7. Sankalana-Vyavakalanabhyam – By addition and by subtraction.

8. Puranapuranabyham – By the completion or no completion.

9. Calana-Kalanabyham – Differences and Similarities.

10. Yaavadunam – Whatever the extent of its deficiency.

11. Vyastisamanstih – Part and Whole.

12. Sesanyankena Caramena – The remainders by the last digit.

13. Sopantyadvayamantyam – The ultimate and twice the penultimate.

14. Ekanyunena Purvena – By one less than the previous one.

15. Gunitasamuccayah – The product of the sum is equal to the sum of the product.

16. Gunakasamuccayah – The factors of the sum is equal to the sum of the factors.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

2.5 URDHAVA – TIRYAGBHYAM

Urdhva-Tiryagbhyam sutras are the basic sutras which is applicable for all case of multiplication.

This itself is very short and compendious consisting of only one combine word and means

“vertically and crosswise” i.e. the first bit of multiplicand and the first bit of multiplier are

multiplied with vertically and crosswise method. Vertically and crosswise multiplication

procedure is also known as array multiplication technique. Fig-2.1 represents the 6×6 multiplier

using vertically and crosswise method.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Figure 2.1: .Urdhava-Triyagbhyam Method

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

2.5 DSP OPERATIONS

Digital Signal Processing (DSP) operations are very important part of engineering as well as

medical discipline. Designing of DSP operations have many approaches. For the designing of DSP

operations, multiplication is play important role to perform signal processing operations such as

Convolution and Correlation. The new approach of this implementation is mentally and easy to

calculate of DSP operations for small length of sequences. In this paper a fast method for DSP

operations based on ancient Vedic mathematics is contemplated.

The implementation of high speed DSP operations of two finite length sequences using Vedic

Urdhava-Triyagbhayam Multiplication Sutra (approach/method) is done. Urdhava-Triyagbhayam

Sutra is very efficient multiplication formula applicable for all types of multiplication.

DSP operation is the heart of the mobile communication and satellite communication system. The

convolution plays a preciously role in Digital Signal Processing and Image Processing. It is used

for designing of digital filter and correlation application. The linear convolution effectively designs

by using simple Vedic multiplier. Convolution is basic concept to designing the finite impulse

response filter, Discrete Fourier Transform (DFT) and Fast Fourier Transform (FFT). Linear

Convolution of two finite length sequence normally computed by using the application of Discrete

Fourier Transform.

Design of all DSP operations with the help of high speed Vedic multiplier which increase the

efficiency of system and reduces the processing time. In this method compute the 2N-1 point

convolution sequence from N point discrete time sequence and N-point circular convolution of

using 2N-1 point Convolution of discrete time sequence. To reduce the processing time of DSP

such as Right–angle circular convolution is operation proposed alternative method.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

The convolution of f and g is written f∗g, using an asterisk or star. It is defined as the integral

of the product of the two functions after one is reversed and shifted. As such, it is a particular kind

of integral transform:

Linear Convolution

Let us consider two input sequence

x(n)=[x(0), x(1), ............., x(L-1)] ............................................(u)

and

h(n)=[h(0),h(1), ...... , h(M+1)] ............................................(v)

The convolution of the length-L input X with the order-M filter h will output the sequence Y(n).

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

From Equation (3)

-(L -1) ≤ m- n ≤ 0

Adding both side n

n - (L -1) ≤ m ≤ n

m must satisfy simultaneously the inequalities

0≤m≤M

n -(L -1) ≤ m ≤ n

From above relation m must be greater than the maximum of the two left- hand sides and

less than the minimum of the two right- hand sides.

Max (0,n-L+1) ≤ m ≤ Min(n,M)

Then the Direct form of Convolution

n=0,1,2,………………..L+M-1 ………..(5)

Equation (5) represent the linear convolution of input sequence x and h for n = 0, 1... L+M-1.

Circular Convolution

Technically linear convolution gives an opportunity to calculate a L-point circular convolution of

the two input sequence. The circular convolution of the L+M-1 point linear convolution calculate

from given condition.

yc (n) = y0(n) + y0(L + n) ……………..(6)

n = 0, 1... L-2

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Correlation

Design of correlation is similarly as linear convolution only that we deal with a reflected version

of one signal. First input signal is simple but second input signal is reflected. After applying

convolution process (Equation (u) is same and reflected the value of equation of (v)). Let us

consider two input sequence are x(n) = [x(0), x(1),........, x(L-2), x(L-1)] and

h(n) = [h(M+1), h(M), .... , h(1), h(0)]. Convolution operation with both the input sequences,

calculate the correlation operation y (n).

PROPOSED ALGORITHM

For Linear Convolution

The design of linear convolution has been show in fig. (1). For two 6-point input sequence x(n)=

[x(0), x(1), x(2), x(3), x(4), x(5)] and h(n)= [ h(0), h(1), h(2), h(3), h(4), h(5)]. This algorithm is

design for any large value of N.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Show the technique of linear convolution using the Urdhava-Triyagbhyam sutras of Vedic

mathematics. The convolved outputs sequences are given by the equation show below.

y(0) = x(0)h(0) …(7)

y(1) = x(0)h(1)+x(1)h(0) …(8)

y(2) = x(0)h(2)+x(1)h(1)+x(2)h(0) …(9)

y(3) = x(0)h(3)+x(1)h(2)+x(2)h(1)+x(3)h(0) …(10)

y(4) = x(0)h(4)+x(1)h(3)+x(2)h(2)+x(3)h(1)+x(4)h(0) …(11)

y(5) = x(0)h(5)+x(1)h(4)+x(2)h(3)+x(3)h(2)+x(4)h(1)+x(5)h(0) …(12)

y(6) = x(1)h(5)+x(2)h(4)+x(3)h(3)+x(4)h(2)+x(5)h(1) …(13)

y(7) = x(2)h(5)+x(3)h(4)+x(4)h(3)+x(5)h(2) …(14)

y(8) = x(3)h(5)+x(4)h(4)+x(5)h(3) …(15)

y(9) = x(4)h(5)+x(5)h(4) …(16)

y(10) = x(5)h(5) …(17)

Equation (7-17) represents the output value of the convolution.

Circular Convolution

The Urdhava –Triyagbhyam is always performed for even number of sequence and gives

odd number of sequences. Circular Convolution perform the following steps are done

1. The middle term of the output of convolution is first marked according to figure-2.

The output term y(5) is circled.

2. Before the middle term output sequence y(0), y(1), y(2), y(3), y(4) consist array

which is left side of array and after the middle term output sequence y(6), y(7), y(8),

y(9), y(10) consist array which is right side of array.

3. Put up the circled middle term is fixed, and MSB bit of left side array and right side

of array will be added. Similarly all the bit position in the right side array will be

added with successively left side bit array position show in fig-2.

4. This step will go on until all the bit position in the left side and right side array of the

middle bit according to above step. After addition we get output of the circular

convolution. Final output calculates by following equation.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

v(0) = y(0) + y(6) …(18)

v(1) = y(1) + y(7) …(19)

v(2) = y(2) + y(8) …(20)

v(3) = y(3) + y(9) …(22)

v(4) = y(4) + y(10) …(23)

v(5) = y(5) …(24)

Fig : 2. Proposed Circular Convolution technique

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Correlation

The design of correlation is based on the linear convolution has been show in figure. For two 6-

point input sequence x(n) = [x(0), x(1), x(2), x(3), x(4), x(5)] and h(n) = [h(5), h(4), h(3), h(2),

h(1), h(0)]. This algorithm is design for any large value of N.

y(0) = x(0)h(5) ...(25)

y(1) = x(0)h(4)+x(1)h(5) ...(26)

y(2) = x(0)h(3)+x(1)h(4)+x(2)h(5) ...(27)

y(3) = x(0)h(2)+x(1)h(3)+x(2)h(4)+x(3)h(5) ...(28)

y(4) = x(0)h(1)+x(1)h(2)+x(2)h(3)+x(3)h(4)+x(4)h(5) ...(29)

y(5) = x(0)h(0)+x(1)h(1)+x(2)h(2)+x(3)h(3)+x(4)h(4)+x(5)h(5) ...(30)

y(6) = x(1)h(0)+x(2)h(1)+x(3)h(2)+x(4)h(3)+x(5)h(4) ...(31)

y(7) = x(2)h(0)+x(3)h(1)+x(4)h(2)+x(5)h(3) ...(32)

y(8) = x(3)h(0)+x(4)h(1)+x(5)h(2) ...(33)

y(9) = x(4)h(0)+x(5)h(1) ...(34)

y(10) = x(5)h(0) ...(35)

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Equation (25-35) represents the output of the cross-correlation. For Auto-Correlation both

the input sequence are similar use in above method.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

CHAPTER-III

FUNDAMENTAL VLSI DESIGN MODULES

3.1: 2-to-1 Multiplexer:

An adder is a digital logic circuit in electronics that implements addition of numbers. In many

computers and other types of processors, adders are used to calculate addresses, similar operations

and table indices in the ALU and also in other parts of the processors. These can be built for many

numerical representations like excess-3 or binary coded decimal. Adders are classified into two

types: half adder and full adder. The half adder circuit has two inputs: A and B, which add two

input digits and generate a carry and sum. The full adder circuit has three inputs: A and C, which

add the three input numbers and generate a carry and sum. This article gives brief information

about half adder and full adder in tabular forms and circuit diagrams.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Half Adder and Full Adder Circuit

An adder is a digital circuit that performs addition of numbers. The half adder adds two binary

digits called as augend and addend and produces two outputs as sum and carry; XOR is applied to

both inputs to produce sum and AND gate is applied to both inputs to produce carry. The full adder

adds 3 one bit numbers, where two can be referred to as operands and one can be referred to as bit

carried in. And produces 2-bit output, and these can be referred to as output carry and sum.

Half Adder

By using half adder, you can design simple addition with the help of logic gates. Let’s see an

addition of single bits.

0+0=0

0+1=1

1+0=1

1+1=10

These are the least possible single-bit combinations. But the result for 1+1 is 10, the sum result

must be re-written as a 2-bit output. Thus, the equations can be written as

0+0=00

0+1=01

1+0=01

1+1=10

The output ‘1’of ‘10’ is carry-out. ‘SUM’ is the normal output and ‘CARRY’ is the carry-out.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Half Adder Truth Table

Here’s what a truth table would look like for such a circuit:

Now it has been cleared that 1-bit adder can be easily implemented with the help of the XOR Gate

for the output ‘SUM’ and an AND Gate for the ‘Carry’. When we need to add, two 8-bit bytes

together, we can be done with the help of a full-adder logic. The half-adder is useful when you

want to add one binary digit quantities. A way to develop a two-binary digit adders would be to

make a truth table and reduce it. When you want to make a three binary digit adder, do it again.

When you decide to make a four digit adder, do it again. The circuits would be fast, but

development time is slow.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Full Adder

This adder is difficult to implement than a half-adder. The difference between a half-adder and a

full-adder is that the full-adder has three inputs and two outputs, whereas half adder has only two

inputs and two outputs. The first two inputs are A and B and the third input is an input carry as C-

IN. When a full-adder logic is designed, you string eight of them together to create a byte-wide

adder and cascade the carry bit from one adder to the next.

The output carry is designated as C-OUT and the normal output is designated as S.

Full Adder Truth Table

With the truth-table, the full adder logic can be implemented. You can see that the output S is an

XOR between the input A and the half-adder, SUM output with B and C-IN inputs. We take C-

OUT will only be true if any of the two inputs out of the three are HIGH.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

3.2 LOGICAL OPERATORS:-

Logical operators are typically used with Boolean (logical) values. When they are, they

return a Boolean value. However, the && and || operators actually return the value of one of the

specified operands, so if these operators are used with non-Boolean values, they may return a non-

Boolean value.

Logical AND operator &&:-

The && (logical AND) operator indicates whether both operands are true. If both

operands have nonzero values, the result has the value 1.Otherwise, the result has the value 0.The

type of the result is int.Both operands must have a arithmetic or pointer type.The usual arithmetic

conversions on each operand are performed.

Unlike the & (bitwise AND) operator, the && operator guarantees left-to-right evaluation of the

operands. If the left operand evaluates to 0(or false), the right operand is not evaluated.

The following examples show how the expressions that contain the logical AND operators are

evaluated:

Expressions Result

1 && 0 false or 0

1 && 4 true or 1

0 && 0 false or 0

The following examples uses the logical AND operator to avoid division by zero :( y! =0) && (x/y)

The expressions x/y is not evaluated when y! =0 evaluates to 0(or false).

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

CHAPTER IV

4.1: WORKING:

We consider a ‘vending machine’ that have two output products of 10Rs cost candy

and this only accepts a 2Rs coin and a 10Rs coin. Let n=2Rs and d=10Rs and pretending that if

we select ‘1-select line’ then the vending machine selects the 10Rs candy product and if we

select ‘0-select line’ then the vending machine selects the 20Rs candy product.

Consider for 10Rs cost product there will be a state diagram

containing 5 states .

For 10Rs product:

If n=2Rs, d=10Rs,

If the coin inserted is n=2Rs coin then S0 state of the five states is occupied by that coin.

i.e., present state S0=2Rs, n=1, d=0 and o/p=0

But we need 10Rs to get the product but we inserted only 2Rs and we still need four 2Rs coins

(8Rs).So the output is ZERO when we inserted 2Rs coin which occupied the state S0. Then the

next state will be S1-state.

And if we again insert a 2Rs coin it occupies the second state (S1).

i.e., present state S1=2Rs, n=1, d=0 and o/p=0

Even now also the output will be zero since we still need to insert 3 more 2Rs coins (6Rs) to get

product. So, it will goes to next state. The next state will be the third state (S2).

The third coin that we will insert will occupy the state three (S2).

i.e., present state S2=2Rs, n=1, d=0 and o/p=0

Still the output is ZERO, it means, we still need to insert 2 more 2Rs (4Rs) coins to get the

product. Then it goes to next state. The next state will be the fourth state (S3).

The fourth coin occupies the fourth state.

i.e., present state S3=2Rs, n=1, d=0, o/p=0

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

The output is still ZERO it means we still need to insert 1 more 2 Rs coin to get the product.

Then it goes to next state. The next state will be the fifth state (S4).

The fifth 2Rs coin occupies the fifth state.

i.e., present state S4=2Rs, n=1, d=0, o/p=1

Here, in this state by inserting the last fifth 2Rs coin, the vending machine comes to know that it

got 10Rs and gives the 10Rs cost product. Then it goes to the next state. The next state is the

initial state i.e., state 1 (S0).

If input=d=10Rs

At first state S0 we have given the input coin which is d=10Rs, then it occupies all the remaining

states and again it is, by default comes to initial state (S0).

i.e., present state S0=10Rs, n=0, d=1, o/p=1

Here, the output will be one, since we inserted the 10Rs coin the vending machine needs to give

the product. And the next state will be initial state (S0) as we have already seen in the above

sentence.

4.2 BLOCK DIAGRAM:-

n

Candy

Coin d Vending open

release

sensor machine mechanis

reset

FSM m

clk

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

4.3 FLOW CHART:-

Circular Convolution

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Linear Convolution

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Correlation

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Urdhava – Triyagbhyam

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Chapter-V

RESULT

5.1 SIMULATION RESULT:

OUTPUT: (i) Linear Convolution

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

OUTPUT: (ii) Circular Convolution

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

OUTPUT : (iii) Correlation

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

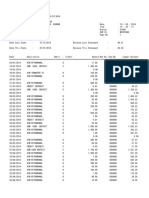

5.2 SYNTHESIS RESULT

Linear Convolution

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Circular Convolution

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

Correlation

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

CHAPTER VI

CONCLUSION

A fast computation of DSP operations of two finite length sequence implemented. DSP operations

are based on URDHAVA - TIRYAGBHYAM method of Vedic mathematics, which reduces the

processing time as compare to inbuilt function of MATLAB. Proposed algorithm provide average

processing time in micro second and conventional operation provide average time in milli second.

FUTURE SCOPE:

It is possible to carry out research work on uses of Vedic mathematical algorithms over traditional

methods in FIR and IIR filters that will provide effective results for de-noising of biomedical

signals.

It can be further used for FFT and IFFT calculation. To improve filtering techniques used in image

processing, stenography, network security and in many more signal processing.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

REFERENCES:

[1] L. R. Rabiner and B. Gold, “Theory and Application of Digital Signal Processing”. Englewood

Cliffs, NJ: Prentice-Hall, 1975.

[2] S. Nazeer Hussain , G . Sudhakiran , “Vedic mathematics application in DSP”. International

journal of advanced research in computer science and software engineering. Volume 6, Issue4,

April 2016.

[3] Anannya Maiti, Kousav Chakraborty , Razia Sultana, “Design and implementation of 4-bit

Multiplier”. International journal of engineering trends in science and technology.

[4] Kaustab M. Gaikwad ,Mahesh S. Chavan, “ Vedic mathematics for DSP operations ”.

International jornal of computer applications.

[5] “The Dynamic Vedic Multiplier Implemented in FPGA for DSP Application”, by Gurumoorthy

Vaithiyanathan.

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

CHAPTER-VII

APPENDIX:

7.1 Appendix : Source code

The whole project is developed in behavioral modeling.

Candy Vending Machine:

module circular_convolution(

input [5:0]x0,x1,x2,x3,x4,x5,x6,x7,x8,x9,

input [5:0]h0,h1,h2,h3,h4,h5,h6,h7,h8,h9,

output [10:0]y0,y1,y2,y3,y4,y5,y6,y7,y8,y9 );

wire [10:0]p0,p1,p2,p3,p4,p5,p6,p7,p8,p9,p10,p11,p12,p13,p14,p15,p16,p17,p18;

linear_convolution LC(x0,x1,x2,x3,x4,x5,x6,x7,x8,x9, h0,h1,h2,h3,h4,h5,h6,h7,h8,h9,

p0,p1,p2,p3,p4,p5,p6,p7,p8,p9,p10,p11,p12,p13,p14,p15,p16,p17,p18)

assign y0=p0+p10;

assign y1=p1+p11;

assign y2=p2+p12;

assign y3=p3+p13;

assign y4=p4+p14;

assign y5=p5+p15;

assign y6=p6+p16;

assign y7=p7+p17;

assign y8=p8+p18;

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

assign y9=p9;

endmodule

module linear_convolution(

input [5:0]x0,x1,x2,x3,x4,x5,x6,x7,x8,x9,

input [5:0]h0,h1,h2,h3,h4,h5,h6,h7,h8,h9,

output [10:0]y0,y1,y2,y3,y4,y5,y6,y7,y8,y9,y10,y11,y12,y13,y14,y15,y16,y17,y18 );

wire [10:0]p0,p1,p2,p3,p4,p5,p6,p7,p8,p9,p10,p11,p12,p13,p14,p15,p16,p17,p18,p19,

p20,p21,p22,p23,p24,p25,p26,p27,p28,p30,p31,p32,p33,p34,p35,p36,p37,p38,p39,

p40,p41,p42,p43,p44,p45,p46,p47,p48,p49,p50,p51,p52,p53,p54,p55,p56,p57,p58,p59,

p60,p61,p62,p63,p64,p65,p66,p67,p68,p69,p70,p71,p72,p73,p74,p75,p76,p77,p78,p79,

p80,p81,p82,p83,p84,p85,p86,p87,p88,p89,p90,p91,p92,p93,p94,p95,p96,p97,p98;

urdhva u1(x0,h0,y0);

urdhva u2(x0,h1,p0);

urdhva u3(x1,h0,p1);

assign y1=p0+p1;

urdhva u4(x0,h2,p2);

urdhva u5(x1,h1,p3);

urdhva u6(x2,h0,p4);

assign y2=p2+p3+p4;

urdhva u7(x0,h3,p5);

urdhva u8(x1,h2,p6);

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

urdhva u9(x2,h1,p7);

urdhva u10(x3,h0,p8);

assign y3=p5+p6+p7+p8;

urdhva u11(x0,h4,p9);

urdhva u12(x1,h3,p10);

urdhva u13(x2,h2,p11);

urdhva u14(x3,h1,p12);

urdhva u15(x4,h0,p13);

assign y4=p9+p10+p11+p12+p13;

urdhva u16(x0,h5,p14);

urdhva u17(x1,h4,p15);

urdhva u18(x2,h3,p16);

urdhva u19(x3,h2,p17);

urdhva u20(x4,h1,p18);

urdhva u21(x5,h0,p19);

assign y5=p14+p15+p16+p17+p18+p19;

urdhva u22(x0,h6,p20);

urdhva u23(x1,h5,p21);

urdhva u24(x2,h4,p22);

urdhva u25(x3,h3,p23);

urdhva u26(x4,h2,p24);

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

urdhva u27(x5,h1,p25);

urdhva u28(x6,h0,p26);

assign y6=p20+p21+p22+p23+p24+p25+p26;

urdhva u29(x0,h7,p27);

urdhva u30(x1,h6,p28);

urdhva u31(x2,h5,p30);

urdhva u32(x3,h4,p31);

urdhva u33(x4,h3,p32);

urdhva u34(x5,h2,p33);

urdhva u35(x6,h1,p34);

urdhva u36(x7,h0,p35);

assign y7=p27+p28+p30+p31+p32+p33+p34+p35;

urdhva u37(x0,h8,p36);

urdhva u38(x1,h7,p37);

urdhva u39(x2,h6,p38);

urdhva u40(x3,h5,p39);

urdhva u41(x4,h4,p40);

urdhva u42(x5,h3,p41);

urdhva u43(x6,h2,p42);

urdhva u44(x7,h1,p43);

urdhva u45(x8,h0,p44);

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

assign y8=p36+p37+p38+p39+p40+p41+p42+p43+p44;

urdhva u46(x0,h9,p45);

urdhva u47(x1,h8,p46);

urdhva u48(x2,h7,p47);

urdhva u49(x3,h6,p48);

urdhva u50(x4,h5,p49);

urdhva u51(x5,h4,p50);

urdhva u52(x6,h3,p51);

urdhva u53(x7,h2,p52);

urdhva u54(x8,h1,p53);

urdhva u55(x9,h0,p54);

assign y9=p45+p46+p47+p48+p49+p50+p51+p52+p53+p54;

urdhva u56(x1,h9,p55);

urdhva u57(x2,h8,p56);

urdhva u58(x3,h7,p57);

urdhva u59(x4,h6,p58);

urdhva u60(x5,h5,p59);

urdhva u61(x6,h4,p60);

urdhva u62(x7,h3,p61);

urdhva u63(x8,h2,p62);

urdhva u64(x9,h1,p63);

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

assign y10=p55+p56+p57+p58+p59+p60+p61+p62+p63;

urdhva u65(x2,h9,p64);

urdhva u66(x3,h8,p65);

urdhva u67(x4,h7,p66);

urdhva u68(x5,h6,p67);

urdhva u69(x6,h5,p68);

urdhva u70(x7,h4,p69);

urdhva u71(x8,h3,p70);

urdhva u72(x9,h2,p71);

assign y11=p64+p65+p66+p67+p68+p69+p70+p71;

urdhva u73(x3,h9,p72);

urdhva u74(x4,h8,p73);

urdhva u75(x5,h7,p74);

urdhva u76(x6,h6,p75);

urdhva u77(x7,h5,p76);

urdhva u78(x8,h4,p77);

urdhva u79(x9,h3,p78);

assign y12=p72+p73+p74+p75+p76+p77+p78;

urdhva u80(x4,h9,p79);

urdhva u81(x5,h8,p80);

urdhva u82(x6,h7,p81);

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

urdhva u83(x7,h6,p82);

urdhva u84(x8,h5,p83);

urdhva u85(x9,h4,p84);

assign y13=p79+p80+p81+p82+p83+p84;

urdhva u86(x5,h9,p85);

urdhva u87(x6,h8,p86);

urdhva u88(x7,h7,p87);

urdhva u89(x8,h6,p88);

urdhva u90(x9,h5,p89);

assign y14=p85+p86+p87+p88+p89;

urdhva u91(x6,h9,p90);

urdhva u92(x7,h8,p91);

urdhva u93(x8,h7,p92);

urdhva u94(x9,h6,p93);

assign y15=p90+p91+p92+p93;

urdhva u95(x7,h9,p94);

urdhva u96(x8,h8,p95);

urdhva u97(x9,h7,p96);

assign y16=p94+p95+p96;

urdhva u98(x8,h9,p97);

urdhva u99(x9,h8,p98);

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

assign y17=p97+p98;

urdhva u100(x9,h9,y18);

endmodule

module correlation(input [5:0]x0,x1,x2,x3,x4,x5,

input [5:0]h0,h1,h2,h3,h4,h5,

output [10:0]y0,y1,y2,y3,y4,y5,y6,y7,y8,y9,y10 );

wire[10:0]w1,w2,w3,w4,w5,w6,w7,w8,w9,w10,w11,w12,w13,w14,w15,w16,w17,w18,w19,w20

,w21,w22,w23,w24,w25,w26,w27,w28,w29,w30,w31,w32,w33,w34;

urdhva u0(x0,h5,y0);

urdhva u1(x0,h4,w1);

urdhva u2(x1,h5,w2);

assign y1=w1+w2;

urdhva u3(x0,h3,w3);

urdhva u4(x1,h4,w4);

urdhva u5(x2,h5,w5);

assign y2 = w3+w4+w5;

urdhva u6(x0,h2,w6);

urdhva u7(x1,h3,w7);

urdhva u8(x2,h4,w8);

urdhva u9(x3,h5,w9);

assign y3 = w6+w7+w8+w9;

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

urdhva u10(x0,h1,w10);

urdhva u11(x1,h2,w11);

urdhva u12(x2,h3,w12);

urdhva u13(x3,h4,w13);

urdhva u14(x4,h5,w14);

assign y4 = w10+w11+w12+w13+w14;

urdhva u15(x0,h0,w15);

urdhva u16(x1,h1,w16);

urdhva u17(x2,h2,w17);

urdhva u18(x3,h3,w18);

urdhva u19(x4,h4,w19);

urdhva u20(x5,h5,w20);

assign y5 = w15+w6+w17+w18+w19+w20;

urdhva u21(x1,h0,w21);

urdhva u22(x2,h1,w22);

urdhva u23(x3,h2,w23);

urdhva u24(x4,h3,w24);

urdhva u25(x5,h4,w25);

assign y6 = w21+w22+w23+w24+w25;

urdhva u26(x2,h0,w26);

urdhva u27(x3,h1,w27);

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

urdhva u28(x4,h2,w28);

urdhva u29(x5,h3,w29);

assign y7 = w26+w27+w28+w29;

urdhva u30(x3,h0,w30);

urdhva u31(x4,h1,w31);

urdhva u32(x5,h2,w32);

assign y8 = w30+w31+w32;

urdhva u33(x4,h0,w33);

urdhva u34(x5,h1,w34);

assign y9 = w33+w34;

urdhva u35(x5,h0,y10);

endmodule

module urdhva(

input [5:0] a,

input [5:0] b,

output [10:0] p

);

assign p[0] = a[0] & b[0];

assign x1=a[1]&b[0];

assign x2=a[0]&b[1];

assign x3=a[2]&b[0];

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

assign x4=a[1]&b[1];

assign x5=a[0]&b[2];

assign x6=a[3]&b[0];

assign x7=a[2]&b[1];

assign x8=a[1]&b[2];

assign x9=a[0]&b[3];

assign x10=a[4]&b[0];

assign x11=a[3]&b[1];

assign x12=a[2]&b[2];

assign x13=a[1]&b[3];

assign x14=a[0]&b[4];

assign x15=a[5]&b[0];

assign x16=a[4]&b[1];

assign x17=a[3]&b[2];

assign x18=a[2]&b[3];

assign x19=a[1]&b[4];

assign x20=a[0]&b[5];

assign x21=a[5]&b[1];

assign x22=a[4]&b[2];

assign x23=a[3]&b[3];

assign x24=a[2]&b[4];

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

assign x25=a[1]&b[5];

assign x26=a[5]&b[2];

assign x27=a[4]&b[3];

assign x28=a[3]&b[4];

assign x29=a[2]&b[5];

assign x30=a[5]&b[3];

assign x31=a[4]&b[4];

assign x32=a[3]&b[5];

assign x33=a[5]&b[4];

assign x34=a[4]&b[5];

assign x35=a[5]&b[5];

ha h1(.a(x1),.b(x2),.s(p[1]),.c(c1));

fa f1(.a(x3),.b(x4),.ci(c1),.s(w1),.c0(c2));

ha h2(.a(w1),.b(x5),.s(p[2]),.c(c3));

fa f2(.a(x6),.b(x7),.ci(c2),.s(w2),.c0(c4));

fa f3(.a(w2),.b(x8),.ci(c3),.s(w3),.c0(c5));

ha h3(.a(w3),.b(x9),.s(p[3]),.c(c6));

fa f4(.a(x10),.b(x11),.ci(c4),.s(w4),.c0(c7));

fa f5(.a(w4),.b(x12),.ci(c5),.s(w5),.c0(c8));

fa f6(.a(x13),.b(w5),.ci(c6),.s(w6),.c0(c9));

ha h4(.a(x14),.b(w6),.s(p[4]),.c(c10));

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

fa f7(.a(x15),.b(x16),.ci(c7),.s(w7),.c0(c11));

fa f8(.a(w7),.b(x17),.ci(c8),.s(w8),.c0(c12));

fa f9(.a(w8),.b(x18),.ci(c9),.s(w9),.c0(c13));

fa f10(.a(w9),.b(x19),.ci(c10),.s(w10),.c0(c14));

ha h11(.a(w10),.b(x20),.s(p[5]),.c(c15));

fa f12(.a(x21),.b(x22),.ci(c11),.s(w11),.c0(c16));

fa f13(.a(w11),.b(x23),.ci(c12),.s(w12),.c0(c17));

fa f14(.a(w12),.b(x24),.ci(c13),.s(w13),.c0(c18));

fa f15(.a(w13),.b(x25),.ci(c14),.s(w14),.c0(c19));

ha h5(.a(w14),.b(c15),.s(p[6]),.c(c20));

fa f16(.a(x26),.b(x27),.ci(c16),.s(w15),.c0(c21));

fa f17(.a(w15),.b(x28),.ci(c17),.s(w16),.c0(c22));

fa f18(.a(w16),.b(x29),.ci(c18),.s(w17),.c0(c23));

fa f19(.a(w17),.b(c19),.ci(c20),.s(p[7]),.c0(c24));

fa f20(.a(x30),.b(x31),.ci(c21),.s(w18),.c0(c25));

fa f21(.a(x32),.b(w18),.ci(c22),.s(w19),.c0(c26));

fa f22(.a(c24),.b(w19),.ci(c23),.s(p[8]),.c0(c27));

fa f23(.a(x33),.b(x34),.ci(c25),.s(w21),.c0(c29));

fa f24(.a(w21),.b(c26),.ci(c27),.s(p[9]),.c0(c30));

fa f25(.a(x35),.b(c29),.ci(c30),.s(p[10]),.c0());

endmodule

CMR College of Engineering & Technology Department of ECE

DSP OPERATION USING VEDIC MATHEMATICS

module ha(

input a,b,

output s,c

);

assign s=a^b;

assign c=a&b;

endmodule

module fa(

input a,b,ci,

output s,c0

);

assign s=a^b^ci;

assign c0=(a&b)|(b&ci)|(ci&a);

endmodule

CMR College of Engineering & Technology Department of ECE

Вам также может понравиться

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceОт EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceРейтинг: 4 из 5 звезд4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeОт EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeРейтинг: 4 из 5 звезд4/5 (5794)

- Face Recognition: Lecture Attendance SystemДокумент27 страницFace Recognition: Lecture Attendance Systemdemo testОценок пока нет

- Spintronicsppt 140414113440 Phpapp02Документ17 страницSpintronicsppt 140414113440 Phpapp02demo testОценок пока нет

- HHS En18 Hacking Wireless.v2Документ31 страницаHHS En18 Hacking Wireless.v2demo test100% (1)

- Mr. Richard Morin Joined Pakistan Stock Exchange Limited (PSX) As CeoДокумент1 страницаMr. Richard Morin Joined Pakistan Stock Exchange Limited (PSX) As Ceodemo testОценок пока нет

- The Yellow House: A Memoir (2019 National Book Award Winner)От EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Рейтинг: 4 из 5 звезд4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingОт EverandThe Little Book of Hygge: Danish Secrets to Happy LivingРейтинг: 3.5 из 5 звезд3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItОт EverandNever Split the Difference: Negotiating As If Your Life Depended On ItРейтинг: 4.5 из 5 звезд4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureОт EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureРейтинг: 4.5 из 5 звезд4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryОт EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryРейтинг: 3.5 из 5 звезд3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerОт EverandThe Emperor of All Maladies: A Biography of CancerРейтинг: 4.5 из 5 звезд4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaОт EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaРейтинг: 4.5 из 5 звезд4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersОт EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersРейтинг: 4.5 из 5 звезд4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyОт EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyРейтинг: 3.5 из 5 звезд3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnОт EverandTeam of Rivals: The Political Genius of Abraham LincolnРейтинг: 4.5 из 5 звезд4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaОт EverandThe Unwinding: An Inner History of the New AmericaРейтинг: 4 из 5 звезд4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreОт EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreРейтинг: 4 из 5 звезд4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)От EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Рейтинг: 4.5 из 5 звезд4.5/5 (121)

- Management in English Language Teaching SummaryДокумент2 страницыManagement in English Language Teaching SummaryCarolina Lara50% (2)

- Powerpoint Presentation R.A 7877 - Anti Sexual Harassment ActДокумент14 страницPowerpoint Presentation R.A 7877 - Anti Sexual Harassment ActApple100% (1)

- Acevac Catalogue VCD - R3Документ6 страницAcevac Catalogue VCD - R3Santhosh KumarОценок пока нет

- Bank Statement SampleДокумент6 страницBank Statement SampleRovern Keith Oro CuencaОценок пока нет

- 1grade 9 Daily Lesson Log For Demo 1 4Документ5 страниц1grade 9 Daily Lesson Log For Demo 1 4cristy olivaОценок пока нет

- QuizДокумент11 страницQuizDanica RamosОценок пока нет

- Manuscript - Batallantes &Lalong-Isip (2021) Research (Chapter 1 To Chapter 3)Документ46 страницManuscript - Batallantes &Lalong-Isip (2021) Research (Chapter 1 To Chapter 3)Franzis Jayke BatallantesОценок пока нет

- Floor Paln ModelДокумент15 страницFloor Paln ModelSaurav RanjanОценок пока нет

- Canopy CountersuitДокумент12 страницCanopy CountersuitJohn ArchibaldОценок пока нет

- Scope of Internet As A ICTДокумент10 страницScope of Internet As A ICTJohnОценок пока нет

- Lemon AidДокумент17 страницLemon AidJade Anne Mercado BalmesОценок пока нет

- Binder 1Документ107 страницBinder 1Ana Maria Gálvez Velasquez0% (1)

- Fletcher Theophilus Ato CVДокумент7 страницFletcher Theophilus Ato CVTHEOPHILUS ATO FLETCHERОценок пока нет

- Flow Chart For SiFUS Strata Title ApplicationДокумент5 страницFlow Chart For SiFUS Strata Title ApplicationPhang Han XiangОценок пока нет

- STM Series Solar ControllerДокумент2 страницыSTM Series Solar ControllerFaris KedirОценок пока нет

- Agreement Deed BangladeshДокумент8 страницAgreement Deed BangladeshVabna EnterpriseОценок пока нет

- BreezeAIR 8000 Data SheetДокумент2 страницыBreezeAIR 8000 Data Sheetalfasukarno100% (1)

- Insurance Smart Sampoorna RakshaДокумент10 страницInsurance Smart Sampoorna RakshaRISHAB CHETRIОценок пока нет

- CPE Cisco LTE Datasheet - c78-732744Документ17 страницCPE Cisco LTE Datasheet - c78-732744abds7Оценок пока нет

- ECO 101 Assignment - Introduction To EconomicsДокумент5 страницECO 101 Assignment - Introduction To EconomicsTabitha WatsaiОценок пока нет

- Fracture and FatigueДокумент15 страницFracture and FatigueZou JiaweiОценок пока нет

- Prevalence of Peptic Ulcer in Patients Attending Kampala International University Teaching Hospital in Ishaka Bushenyi Municipality, UgandaДокумент10 страницPrevalence of Peptic Ulcer in Patients Attending Kampala International University Teaching Hospital in Ishaka Bushenyi Municipality, UgandaKIU PUBLICATION AND EXTENSIONОценок пока нет

- Sun Nuclear 3D SCANNERДокумент7 страницSun Nuclear 3D SCANNERFranco OrlandoОценок пока нет

- Practical GAD (1-32) Roll No.20IF227Документ97 страницPractical GAD (1-32) Roll No.20IF22720IF135 Anant PatilОценок пока нет

- VoLTE KPI Performance - E2EДокумент20 страницVoLTE KPI Performance - E2EAnway Mohanty100% (1)

- SMK Techno ProjectДокумент36 страницSMK Techno Projectpraburaj619Оценок пока нет

- Introduction To Wireless and Mobile Systems 4th Edition Agrawal Solutions ManualДокумент12 страницIntroduction To Wireless and Mobile Systems 4th Edition Agrawal Solutions Manualethelbertsangffz100% (34)

- Is.14785.2000 - Coast Down Test PDFДокумент12 страницIs.14785.2000 - Coast Down Test PDFVenkata NarayanaОценок пока нет

- Ssasaaaxaaa11111......... Desingconstructionof33kv11kvlines 150329033645 Conversion Gate01Документ167 страницSsasaaaxaaa11111......... Desingconstructionof33kv11kvlines 150329033645 Conversion Gate01Sunil Singh100% (1)

- Project Job Number EngineerДокумент2 страницыProject Job Number Engineertekno plus banatОценок пока нет